Application Report SLLA296–November 2009

# TLK313x CPRI Multi-hop Performance with the CDCM7005 Clock Jitter Cleaner

Hassan Ali

ICP - High Speed Interface

# ABSTRACT

Laboratory measurements were performed to determine the impact of reference clock phase noise on the performance of the TLK313x serializer/deserializer (SerDes) devices in a CPRI multi-hop configuration. The SerDes jitter-cleaner PLL was turned off, and the recovered clock, RXCLK\_0, was externally jitter-cleaned with the CDCM7005 clock jitter cleaner before it was used to clock the serial transmitter.

The following key measurements were taken for 614.4Mbps, 1.2288Gbps, and 2.4576Gbps serial data rates, with the SerDes setup in the TBID mode (parallel interface clock rate = serial bit-rate/20):

- 1. Serial transmitter eye-pattern at every hop to determine compliance with the CPRI transmitter eye-mask.

- 2. Data continuity status as a function of the number of hops tested with the CRPAT long pattern.

- 3. Accumulated clock phase noise as a function of the number of hops.

- 4. SerDes PLL lock status at every hop.

It was observed that:

- the TLK313x/CDC7005 combination operated error-free in the 7-hop CPRI configuration at all the tested serial data rates with a large operating margin on the transmitter eye-mask. The worst-case total jitter recorded for the SerDes transmitter data after 7 hops was just 0.114UI at the 2.4576Gbps serial data rate, which provides better than 59% margin against the 0.279UI CPRI specification.

- at all the hops, the SerDes PLL remained locked after 24 hours of continuous error-free running.

- the TLK313x/CDCM7005 SerDes/clock combination proved to be capable of supporting more than the required 5 CPRI hops.

The results are applicable to any other non-CPRI multi-hop configurations similar to the one covered in this document.

#### Contents

| 1     | The O | bjectives                                           | 3  |

|-------|-------|-----------------------------------------------------|----|

| 2     | Measu | irement Setup                                       | 4  |

|       |       | urement Results                                     |    |

|       |       | usion                                               |    |

|       |       | Configuration Script for the Lead SerDes Device     |    |

| Appen | dix B | Configuration Script for the Partner SerDes Devices | 19 |

# List of Figures

| 1  | A typical CPRI Multi-hop SerDes/Clock Configuration                             | 3  |

|----|---------------------------------------------------------------------------------|----|

| 2  | Measurement Setup for the Evaluation of CPRI SerDes/Clock Multi-hop Performance | 4  |

| 3  | 614.4Mbps Serial Rate – Hop #1 Performance                                      | 6  |

| 4  | 614.4Mbps Serial Rate – Hop #2 Performance                                      | 7  |

| 5  | 614.4Mbps Serial Rate – Hop #3 Performance                                      | 7  |

| 6  | 614.4Mbps Serial Rate – Hop #4 Performance                                      | 7  |

| 7  | 614.4Mbps Serial Rate – Hop #5 Performance                                      | 8  |

| 8  | 614.4Mbps Serial Rate – Hop #6 Performance                                      | 8  |

| 9  | 614.4Mbps Serial Rate – Hop #7 Performance                                      | 8  |

| 10 | 1.2288Gbps Serial Rate – Hop #1 Performance                                     | 9  |

| 11 | 1.2288Gbps Serial Rate – Hop #2 Performance                                     | 10 |

| 12 | 1.2288Gbps Serial Rate – Hop #3 Performance                                     | 10 |

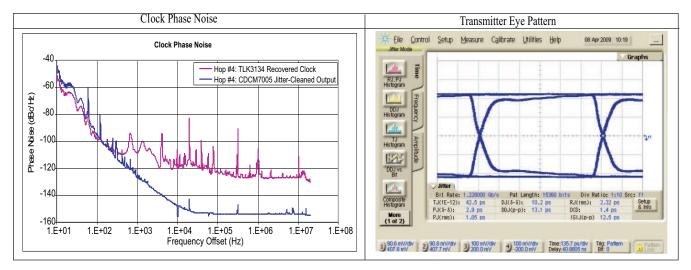

| 13 | 1.2288Gbps Serial Rate – Hop #4 Performance                                     | 10 |

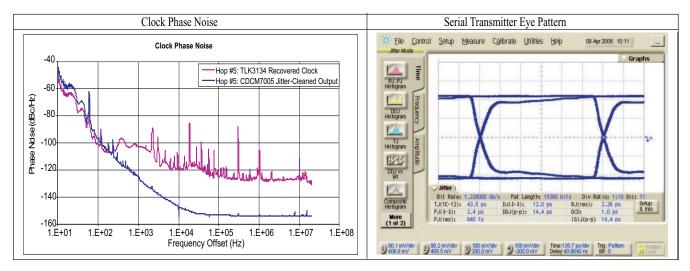

| 14 | 1.2288Gbps Serial Rate – Hop #5 Performance                                     | 11 |

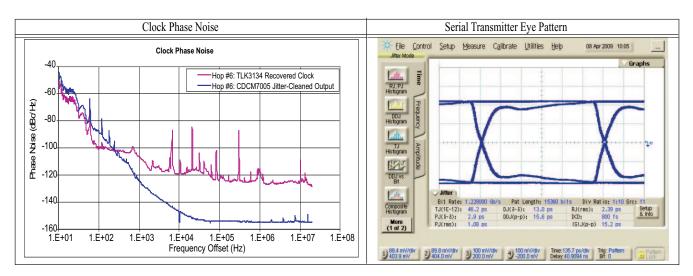

| 15 | 1.2288Gbps Serial Rate – Hop #6 Performance                                     | 11 |

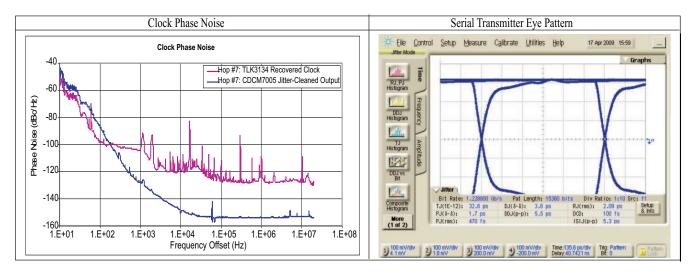

| 16 | 1.2288Gbps Serial Rate – Hop #7 Performance                                     | 11 |

| 17 | 2.4576Gbps Serial Rate – Hop #1 Performance                                     | 12 |

| 18 | 2.4576Gbps Serial Rate – Hop #2 Performance                                     | 13 |

| 19 | 2.4576Gbps Serial Rate – Hop #3 Performance                                     | 13 |

| 20 | 2.4576Gbps Serial Rate – Hop #4 Performance                                     | 13 |

| 21 | 2.4576Gbps Serial Rate – Hop #5 Performance                                     | 14 |

| 22 | 2.4576Gbps Serial Rate – Hop #6 Performance                                     | 14 |

| 23 | 2.4576Gbps Serial Rate – Hop #7 Performance                                     | 14 |

|    |                                                                                 |    |

# List of Tables

| 1 | 614.4Mbps Serial Rate Performance Summary  | 8  |

|---|--------------------------------------------|----|

| 2 | 1.2288Gbps Serial Rate Performance Summary | 11 |

| 3 | 2.4576Gbps Serial Rate Performance Summary | 14 |

# 1 The Objectives

CPRI multi-hop configurations can suffer from performance degradation due to accumulated clock phase noise. The objective of this study is to understand the extent of the performance degradation when the TLK313x family of Texas Instruments SerDes devices is used with the Texas Instruments CDCM7005 clock jitter cleaner.

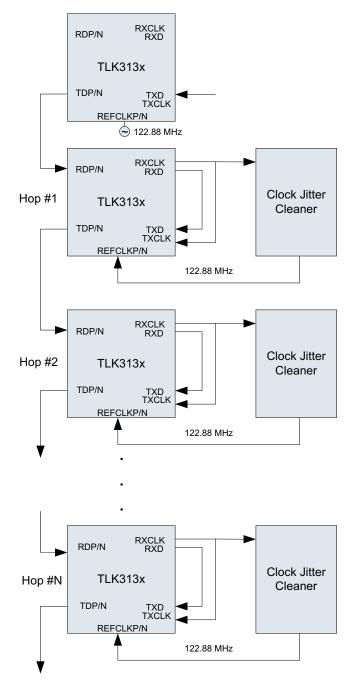

Figure 1. A typical CPRI Multi-hop SerDes/Clock Configuration

A typical CPRI multi-hop configuration using SerDes devices such as Texas Instruments TLK3131, TLK3132, and TLK3134, and clock jitter cleaners such as Texas Instruments CDCM7005, is shown in Figure 1. At every hop the recovered clock, RXCLK, is jitter-cleaned by the clock-jitter cleaner before it's used to clock the outgoing serial data TDP/TDN. This configuration reduces clock phase noise accumulation from hop to hop and hence reduces the transmitted serial data jitter at every hop.

#### Measurement Setup

#### 2 Measurement Setup

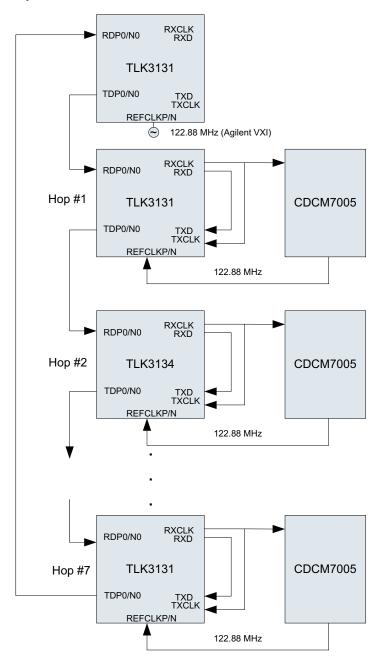

## Figure 2. Measurement Setup for the Evaluation of CPRI SerDes/Clock Multi-hop Performance

The measurement setup used for the evaluation of the CPRI SerDes/clock multi-hop performance is as shown in Figure 2.

The first TLK3131 SerDes device was clocked with an external 122.88MHz clock from Agilent VXI. This device was setup to generate and verify a long continuous random test pattern (CRPAT) composed of 15360 bits. To form the first hop, the TDP0/TDN0 output of the first TLK3131 device was connected to the RDP0/RDN0 input of the second TLK3131 SerDes device which was itself set in the SLOOP mode. Again, the TDP0/TDN0 output of the second TLK3131 device was connected to the RDP0/RDN0 input of a TLK3134 device also set in the SLOOP mode to form the second hop. The process was repeated with four more TLK3134 devices and one TLK3131 device to form a total of seven hops. The TDP0/TDN0 output of the TLK3131 device on the seventh hop was connected back to the RDP0/RDN0 input of the first TLK3131 device for bit-error checking.

The MDIO script provided in Appendix 1 provides an example of how the lead (generator/verifier) TLK3131 device was configured and tested for the 2.4576Gbps serial data rate. The MDIO script provided in Appendix 2 provides more details on how the partner (downstream) TLK313x devices were configured and tested for the 2.4576Gbps serial data rate. The configuration and testing were similar for the other serial data rates.

The recovered clock, RXCLK\_0, outputs of all the SerDes devices, other than the first TLK3131 device, were fed into the respective TXCLK inputs as well as into seven, separate CDCM7005 devices for jitter cleaning and clock multiplication. The jitter-cleaned 122.88MHz clock was tied to the REFCLKP/N input of each respective SerDes device. An external Epson Toyocom 491.52MHz voltage-controlled crystal oscillator (VCXO) was used with every CDCM7005 device to provide a 122.88MHz clock to every SerDes device on power-up. The clock frequency tolerance from this VCXO was ±125ppm.

Using Agilent E5052 Phase Noise Analyzer, the phase noise of the RXCLK\_0 and jitter-cleaned REFCLKP/REFCLKN clocks were measured at every hop. The random jitter in ps-RMS was computed by integrating the phase noise over 10Hz to 20MHz frequency offset range. The random and total jitter of the TDP0/TDN0 output at every hop was measured using the jitter mode of the Agilent DCAj oscilloscope

Measurement Results

# 3 Measurement Results

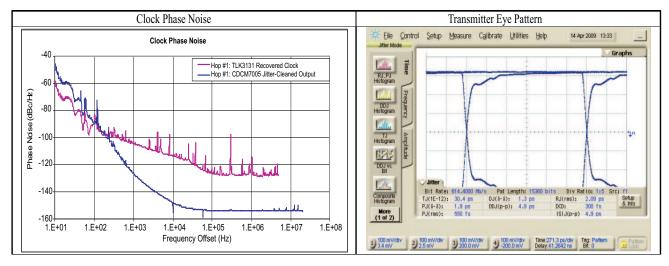

The performance results for the 614.4Mbps serial rate are shown in Figure 3 to Figure 9 and are summarized in Table 1.

Figure 3. 614.4Mbps Serial Rate – Hop #1 Performance

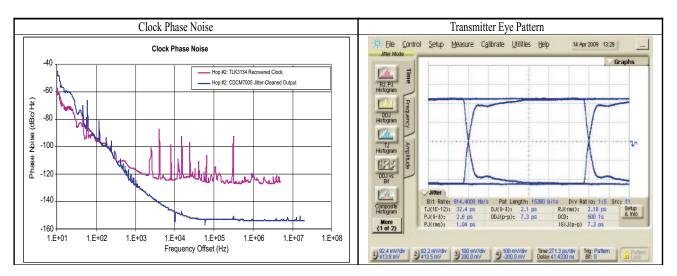

Figure 4. 614.4Mbps Serial Rate – Hop #2 Performance

Figure 5. 614.4Mbps Serial Rate – Hop #3 Performance

Figure 6. 614.4Mbps Serial Rate – Hop #4 Performance

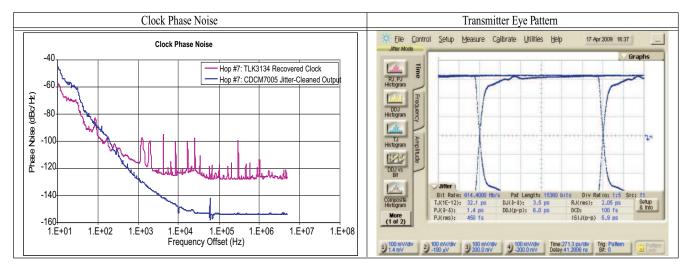

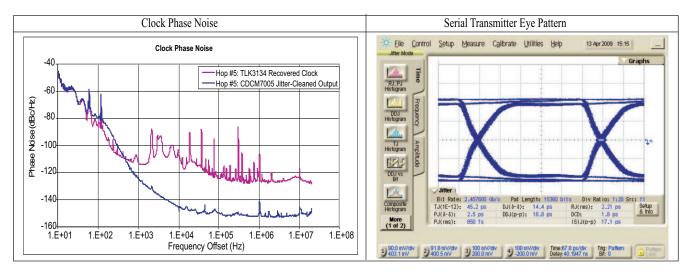

Figure 8. 614.4Mbps Serial Rate – Hop #6 Performance

Figure 9. 614.4Mbps Serial Rate – Hop #7 Performance

| Hop # | 30.72MHz Recovered Clock<br>Jitter (ps RMS) (10Hz to<br>20MHz Offset) | 122.88MHz CDCM7005 Output<br>Clock Jitter (ps RMS)<br>(10Hz to 20MHz Offset) | SerDes Serial Transmit<br>Data Random Jitter<br>(ps RMS) | SerDes Serial Transmit<br>Data Total Jitter<br>(ps pp [UI]) |

|-------|-----------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| 1     | 17.7                                                                  | 12.2                                                                         | 2.09                                                     | 30.4 [0.019]                                                |

| 2     | 20.5                                                                  | 12.0                                                                         | 2.18                                                     | 32.4 [0.020]                                                |

| 3     | 19.6                                                                  | 11.6                                                                         | 2.28                                                     | 35.6 [0.022]                                                |

| 4     | 18.9                                                                  | 12.2                                                                         | 2.33                                                     | 35.9 [0.022]                                                |

| 5     | 19.4                                                                  | 12.3                                                                         | 2.18                                                     | 35.2 [0.022]                                                |

| 6     | 20.4                                                                  | 12.0                                                                         | 2.32                                                     | 35.1 [0.022]                                                |

| 7     | 20.1                                                                  | 15.6                                                                         | 2.05                                                     | 32.1 [0.020]                                                |

| Table 1. 614.4 Mbps Serial Rate Performance Summary |

|-----------------------------------------------------|

|-----------------------------------------------------|

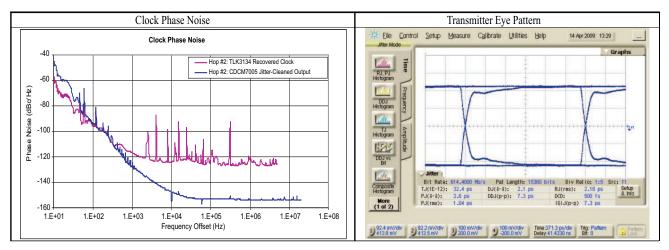

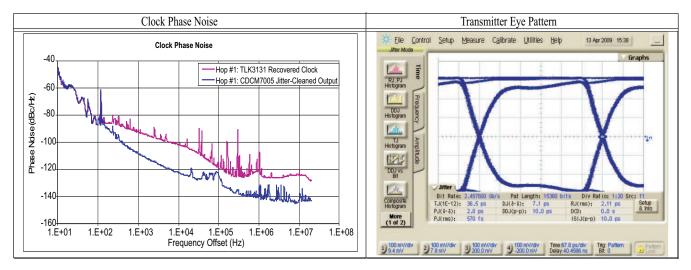

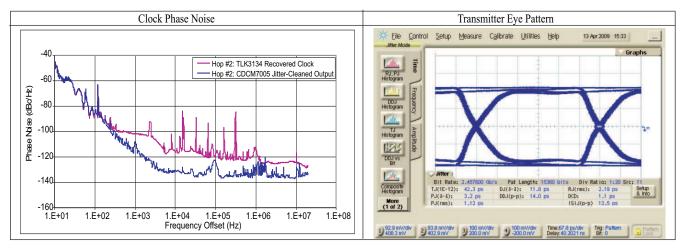

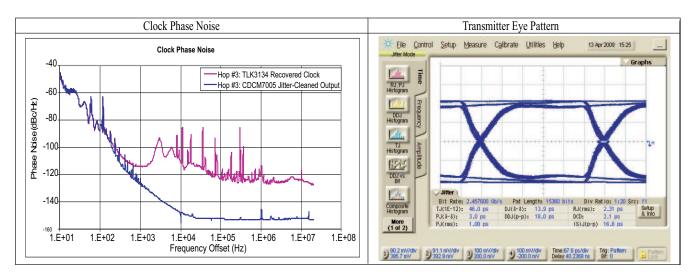

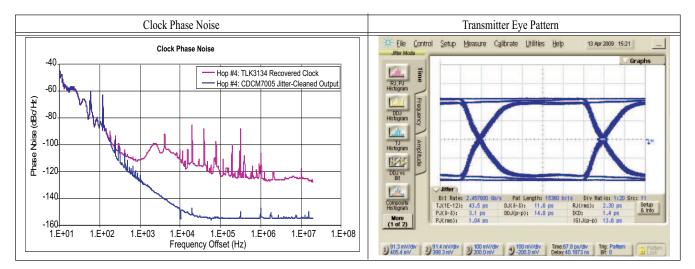

# The performance results for the 1.2288Gbps serial rate are shown in Figure 10 to Figure 16 and are summarized in Table 2.

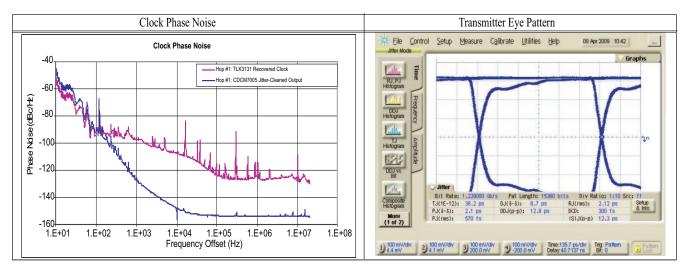

Figure 10. 1.2288Gbps Serial Rate – Hop #1 Performance

Figure 11. 1.2288Gbps Serial Rate – Hop #2 Performance

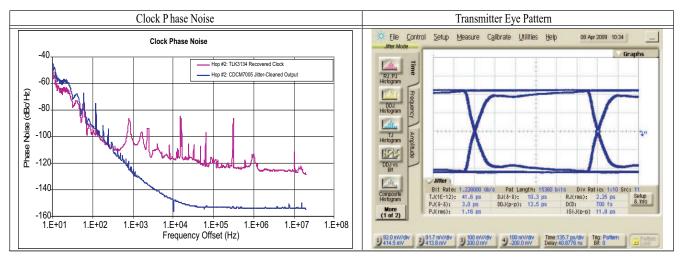

Figure 12. 1.2288Gbps Serial Rate – Hop #3 Performance

Figure 13. 1.2288Gbps Serial Rate – Hop #4 Performance

Figure 14. 1.2288Gbps Serial Rate – Hop #5 Performance

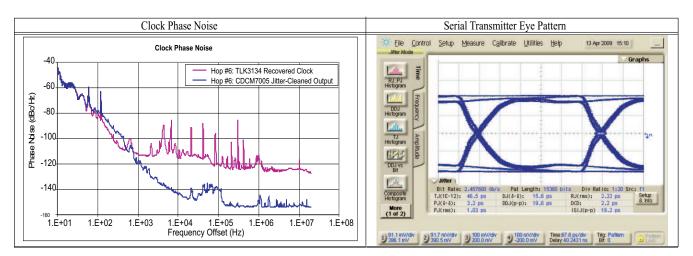

Figure 15. 1.2288Gbps Serial Rate – Hop #6 Performance

Figure 16. 1.2288Gbps Serial Rate – Hop #7 Performance

| Нор # | 61.44MHz Recovered<br>Clock Jitter (ps RMS)<br>(10Hz to 20MHz Offset) | 122.88MHz CDCM7005<br>Output Clock Jitter (ps RMS)<br>(10Hz to 20MHz Offset) | SerDes Serial Transmit<br>Data Random Jitter<br>(ps RMS) | SerDes Serial<br>Transmit Data Total<br>Jitter<br>(ps pp [UI]) |

|-------|-----------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|

| 1     | 19.0                                                                  | 12.6                                                                         | 2.12                                                     | 38.2 [0.047]                                                   |

| 2     | 21.3                                                                  | 12.9                                                                         | 2.25                                                     | 41.6 [0.051]                                                   |

| 3     | 21.2                                                                  | 13.2                                                                         | 2.36                                                     | 44.8 [0.055]                                                   |

| 4     | 20.4                                                                  | 13.8                                                                         | 2.32                                                     | 42.5 [0.052]                                                   |

| 5     | 20.5                                                                  | 14.0                                                                         | 2.26                                                     | 43.5 [0.053]                                                   |

| 6     | 22.0                                                                  | 14.4                                                                         | 2.39                                                     | 46.2 [0.057]                                                   |

| 7     | 20.6                                                                  | 16.1                                                                         | 2.09                                                     | 32.6 [0.040]                                                   |

| Table 2. 1.2 | 2288Gbps | Serial | Rate | Performance | Summary |

|--------------|----------|--------|------|-------------|---------|

|--------------|----------|--------|------|-------------|---------|

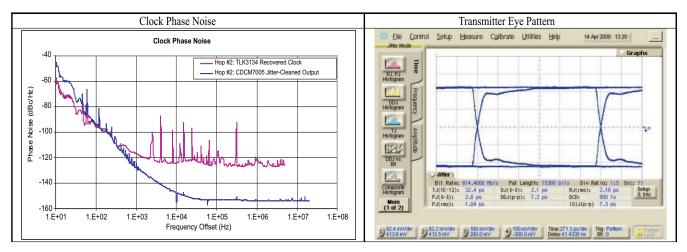

#### Measurement Results

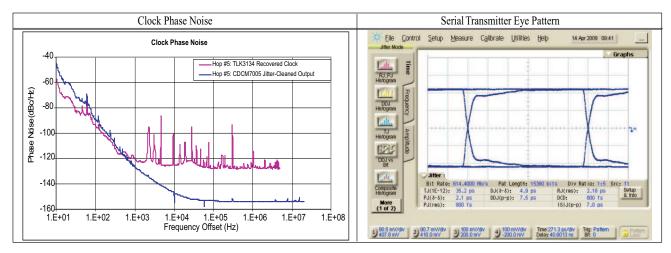

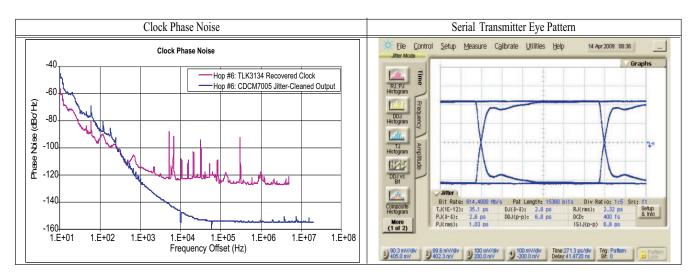

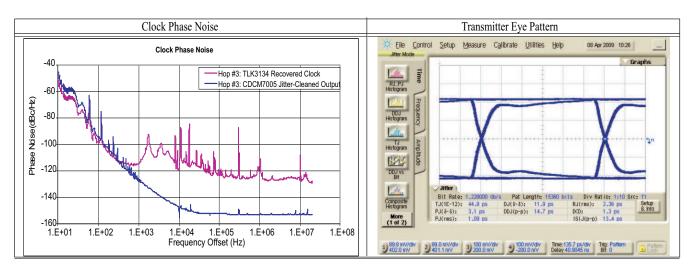

The performance results for the 2.4576Gbps serial rate are shown in Figure 17 to Figure 23 and are summarized in Table 3.

Figure 17. 2.4576Gbps Serial Rate – Hop #1 Performance

Figure 18. 2.4576Gbps Serial Rate – Hop #2 Performance

Figure 19. 2.4576Gbps Serial Rate – Hop #3 Performance

Figure 20. 2.4576Gbps Serial Rate – Hop #4 Performance

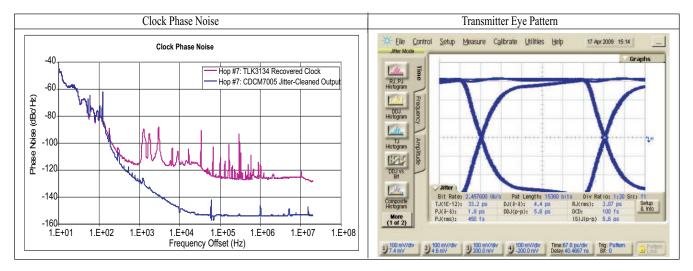

Figure 22. 2.4576Gbps Serial Rate – Hop #6 Performance

Figure 23. 2.4576Gbps Serial Rate – Hop #7 Performance

| Нор # | 122.88MHz Recovered<br>Clock Jitter (ps RMS)<br>(10Hz to 20MHz Offset) | 122.88MHz CDCM7005<br>Output Clock Jitter (ps<br>RMS) (10Hz to 20MHz<br>Offset) | SerDes Serial Transmit<br>Data Random Jitter<br>(ps RMS) | SerDes Serial Transmit<br>Data Total Jitter<br>(ps pp [UI]) |

|-------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| 1     | 14.9                                                                   | 13.1                                                                            | 2.11                                                     | 36.5 [0.090]                                                |

| 2     | 16.6                                                                   | 13.3                                                                            | 2.19                                                     | 42.3 [0.104]                                                |

| 3     | 16.5                                                                   | 13.6                                                                            | 2.31                                                     | 46.0 [0.113]                                                |

| 4     | 16.3                                                                   | 14.0                                                                            | 2.30                                                     | 43.5 [0.107]                                                |

| 5     | 16.6                                                                   | 14.6                                                                            | 2.21                                                     | 45.2 [0.111]                                                |

| 6     | 17.5                                                                   | 15.0                                                                            | 2.22                                                     | 46.5 [0.114]                                                |

| 7     | 16.1                                                                   | 15.3                                                                            | 2.07                                                     | 33.2 [0.082]                                                |

# 4 Conclusion

The TLK313x/CDCM7005 combination operated error-free in the 7-hop CPRI configuration at all the tested serial data rates with a large operating margin on the transmitter eye-mask. The worst-case total jitter recorded for the SerDes transmitter data after 7 hops was just 0.114UI at the 2.4576Gbps serial data rate which provides better than 59% margin against the 0.279UI CPRI specification.

Conclusion

At all the hops, the SerDes PLL remained locked after 24 hours of continuous error-free running.

Based on the above results, the TLK313x/CDCM7005 SerDes/clock combination has proven to be capable of supporting more than the required 5 CPRI hops.

#### Appendix A Configuration Script for the Lead SerDes Device

// TLK3131\_LEAD\_REF122\_FULL\_245G.txt // TLK3131 is provided with 122.88MHz diff reference clock input. // Data rate is 2.4576Gbps. // TLK3131 should be configured in TBID Mode // Parallel I/O Source Centered mode // JADIS TX/RX set at Full Rate with 10x Multiplier for a Line Rate of 2.4576Gbps // JADIS TX and RX gets Diff clock // RCLK is RXBCLK AND RCLK IS 122.88 MHz // Date: 03/12/2009 // Revision: 1.0 START CLAUSE 22 // Device Pin Settings // CODE input pin is LOW // PLOOP input pin is LOW // SLOOP input pin is LOW // SPEED[1:0] input pins are both HIGH (SW select) // ENABLE input pin is HIGH // PRBS\_EN input pin is LOW // PRTAD[4:0] = 5'b00000 //CONFIGURE LEAD TLK3131 (DUT WITH CRPAT GEN AND VERIFIER) //Each TLK3131 has 2 channels but only 1 channel is used. //2nd channel is powered down //Assigning Port Address 0 for Channel 0 //Assigning Port Address 1 for Channel 1 SETPHYADD(00) DISPLAY(Setting LEAD TLK3131) // Software Reset WRITE(00, 8000) // Verify MDIO is functional READ(11, 3590, FFFF) // Power down the unusable channel 1 to save power // RX1 Ch disable WRITE(1E, 9004) WRITE(1F, 0000) // TX1 Ch disable WRITE(1E, 900C) WRITE(1F, 0000) // Channel 1 powerdown SETPHYADD(01) WRITE(00, 0940) // go back to channel 0 SETPHYADD(00) // SERDES\_PLL\_CONFIG: use 10x MPY, same as default WRITE(1E, 9000) WRITE(1F, 1515) // SERDES\_RATE\_CONFIG\_TX\_RX: use FULL rate, same as default WRITE(1E, 9001) WRITE(1F, 0000) // Set the JADIS RX equalizer and AC Coupled RX Term WRITE(1E, 9002) WRITE(1F, 1005) // Set the JADIS TX output swing to 1375mv, // and set common mode bit WRITE(1E, 900A) WRITE(1F, 0F01) // Issue HSTL Retrain WRITE(1E, 9304) WRITE(1F, 0088) WRITE(1E, 9304)

WRITE(1F, 4088) WRITE(1E, 9304) WRITE(1F, 0088) // Poll Serdes PLL Status for Locked State WRITE(1E, 901B) READ(1F) READ(1F, 0011, 0011) READ(1F, 0011, 0011) // Set TBID mode and Enable Pattern Gen/Ver in LEAD TLK3131 // PHY\_CH\_CONTROL\_2: Enable Encoder/Decoder. Set TBID mode. WRITE(11, 3394) // PHY\_CH\_CONTROL\_1: perform datapath reset WRITE(10, 0C00) // PHY\_CH\_CONTROL\_1: select CRPAT Long test pattern WRITE(10, 0403) // PHY\_CH\_CONTROL\_1: enable CRPAT Long test pattern generation WRITE(10, 0413) // PHY\_CRPAT\_PATTERN\_COUNTER\_1: clear it READ(17) // PHY\_CRPAT\_PATTERN\_COUNTER\_2: clear it READ(18) // PHY\_CH\_CONTROL\_1: enable CRPAT Long test pattern verification WRITE(10, 041B) // Devices are programmed. Test pattern should pass DISPLAY(Pattern Verification in LEAD TLK3131) SETPHYADD(00) // PHY\_TEST\_PATTERN\_SYNC\_STATUS: CRPAT Sync READ(15)READ(15, 0001, 0001) READ(15, 0001, 0001) // double check // Now, test pattern generation and verification is in progress. // Verify error-free operation. 11 // PHY\_TEST\_PATTERN\_COUNTER READ(17, 0000, FFFF) READ(18, 0000, FFFF) READ(17, 0000, FFFF) READ(18, 0000, FFFF) // Now, all done. DISPLAY(CRPAT LONG TEST FINISHED) // BELOW REGISTERS TO BE READ AFTER SOME TIME // REGISTERS TO VERIFY TO MAKE SURE SET UP IS RUNNING ERROR FREE // CONTROL REGS //MULT WRITE(1E, 9000) READ(1F, 1515, FFFF) //RATE WRITE(1E, 9001) READ(1F, 0000, FFFF) // CH\_CONTROL\_1 READ(10, 041B, FFFF) // CH\_CONTROL\_2 READ(11, 3394, FFFF) // STATUS REGS // PLL LOCK WRITE(1E, 901B) READ(1F, 0011, 0011) // PHY\_TEST\_PATTERN\_SYNC\_STATUS: CRPAT Sync READ(15, 0001, 0001) // PHY\_TEST\_PATTERN\_COUNTER READ(17, 0000, FFFF) READ(18, 0000, FFFF)

Appendix A

STOP

# Appendix B Configuration Script for the Partner SerDes Devices

```

// TLK3131_PARTNER_REF122_FULL_245G.txt

// TLK3131 is provided with 122.88MHz diff reference clock input.

// Data rate is 2.4576Gbps.

// TLK3131 should be configured in TBID Mode

// Parallel I/O Source Centered mode

// JADIS TX/RX set at Full Rate with 10x Multiplier for a Line Rate of 2.4576Gbps

// JADIS TX and RX gets Diff clock

// RCLK is RXBCLK AND RCLK IS 122.88 MHz

// Date: 03/12/2009

// Revision: 1.0

START

CLAUSE 22

// Device Pin Settings

// CODE input pin is LOW

// PLOOP input pin is LOW

// SLOOP input pin is HIGH

// SPEED[1:0] input pins are both HIGH (SW select)

// ENABLE input pin is HIGH

// PRBS_EN input pin is LOW

// PRTAD[4:0] = 5'b00000

//Each TLK3131 has 2 channels but only 1 channel is used.

//2nd channel is powered down

//Assigning Port Address 0 for Channel 0

//Assigning Port Address 1 for Channel 1

SETPHYADD(00)

DISPLAY(Setting PARTNER TLK3131)

// Software Reset

WRITE(00, 8000)

// Verify MDIO is functional

READ(11, 3590, FFFF)

// Power down the unusable channel 1 to save power

// RX1 Ch disable

WRITE(1E, 9004)

WRITE(1F, 0000)

// TX1 Ch disable

WRITE(1E, 900C)

WRITE(1F, 0000)

// Channel 1 powerdown

SETPHYADD(01)

WRITE(00, 0940)

// go back to channel 0

SETPHYADD(00)

// SERDES_PLL_CONFIG: use 10x MPY, same as default

WRITE(1E, 9000)

WRITE(1F, 1515)

// SERDES_RATE_CONFIG_TX_RX: use FULL rate, same as default

WRITE(1E, 9001)

WRITE(1F, 0000)

// Set the JADIS RX equalizer and AC Coupled RX Term

WRITE(1E, 9002)

WRITE(1F, 1005)

// Set the JADIS TX output swing to 1375mv,

// and set common mode bit

WRITE(1E, 900A)

WRITE(1F, 0F01)

// Issue HSTL Retrain

WRITE(1E, 9304)

WRITE(1F, 0088)

WRITE(1E, 9304)

WRITE(1F, 4088)

```

Appendix B

WRITE(1E, 9304) WRITE(1F, 0088) // Poll Serdes PLL Status for Locked State WRITE(1E, 901B) READ(1F) READ(1F, 0011, 0011) READ(1F, 0011, 0011) // PHY\_CH\_CONTROL\_2: Disable Encoder/Decoder. Set TBID mode. WRITE(11, 3390) // PHY\_CH\_CONTROL\_1: perform datapath reset WRITE(10, 0C00) // Now, all done. DISPLAY(PARTNER TLK3131 PROGRAMMING FINISHED) // BELOW REGISTERS TO BE READ AFTER SOME TIME // REGISTERS TO VERIFY TO MAKE SURE SET UP IS RUNNING ERROR FREE // CONTROL REGS //MULT WRITE(1E, 9000) READ(1F, 1515, FFFF) //RATE WRITE(1E, 9001) READ(1F, 0000, FFFF) // CH\_CONTROL\_1 READ(10, 0400, FFFF) // CH\_CONTROL\_2 READ(11, 3390, FFFF) // STATUS REGS // PLL LOCK WRITE(1E, 901B) READ(1F, 0011, 0011)

STOP

## **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated