# Application Note **Flexible RS-485: A Simplified Multi-System Design for RS-485 Using the THVD1424**

Parker Dodson

#### ABSTRACT

RS-485 is long standing interface that has proliferated industrial based communication applications for almost three decades. Championed for its simplicity and its technical benefits, namely a differential wire communication interface with relatively high data rates and a large common mode range which enables accurate communication across long busses in multi-point networks, has made RS-485 the most used wired communication standard in industrial applications. With a relatively minimal set of requirements, RS-485 systems have much variability and each system, as well as RS-485 transceiver, needs to be carefully designed to best provide the specific application needs. This leads to considerable design effort for each RS-485 system and with many RS-485 transceivers being designed for specific niches within the overarching RS-485 standard which can further compound the complexity of the design and qualification processes. However, with TI's new Flexible RS-485 Transceivers, the THVD1424 and the THVD1454, one IC can now cover a wide array of RS-485 based applications which designers can leverage into multiple systems – removing the need to select and qualify multiple devices for each new design. This application report briefly explain: the RS-485 use case domain to see the vast differences possible between RS-485 systems; a quick look at the traditional RS-485 system design.

# **Table of Contents**

| 1 Use Case Domain of RS-485                                        | 2 |

|--------------------------------------------------------------------|---|

| 1.1 RS-485 Compliant Transmitter                                   | 2 |

| 1.2 RS-485 Compliant Receiver                                      | 2 |

| 1.3 RS-485 Transceiver Use Case Variability                        | 3 |

| 2 Traditional RS-485 Design Process                                |   |

| 2.1 Design Process Overview                                        | 3 |

| 2.2 Requirement Definition                                         |   |

| 2.3 IC Selection, Application Design, and Validation/Qualification | 5 |

| 3 One Multi-System Design: Flexible RS-485 with the THVD1424       | 5 |

| 3.1 Flexible Multi-System Design                                   | 5 |

| 3.2 Simplification of RS-485 Design Process Using THVD1424         | 5 |

| 4 Summary                                                          | 7 |

| 5 References                                                       | 7 |

# List of Figures

| Figure 1-1. Standard Unit Load Chart for RS-485 Compliant Receivers<br>Figure 2-1. Typical RS-485 Cable Length v. Data Rate Performance | 2 |

|-----------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                         |   |

| Figure 3-1. Standard Half Duplex RS-485 IC Package vs. THVD1424 Package                                                                 |   |

# List of Tables

# Trademarks

All trademarks are the property of their respective owners.

# 1 Use Case Domain of RS-485

The RS-485 standard defines a differential, bi-directional, and multipoint wired communication interface. The standard is published jointly by the Telecommunications Industry Association (TIA) and the Electronic Industries Alliance (EIA). It defines the electrical characteristics of the interface circuits, but does not define cabling, connectors, nor data protocol(s) used.

# 1.1 RS-485 Compliant Transmitter

A RS-485 compliant transmitter has a few key requirements to be compliant with the standard – while this is not an exhaustive list – these tend to be the most critical across applications. The first is the output differential voltage magnitude – which is typically denoted  $|V_{OD}|$  - which requires the magnitude of the driver to be a minimum of 1.5 V across a 54  $\Omega$  load – which is intended to show that the transmitter can drive 32 Unit Loads in Parallel with two 120  $\Omega$  termination resistors. It needs to be able to withstand an input common mode range of -7 V to 12 V – but this range can be expanded. In case of bus contention, two transmitters communicating at the same time, or a direct short to a voltage supply from a differential bus pin, or a short between differential bus pins the driver must limit the current magnitude to 250mA – this is typically denoted  $I_{OS}$ . Finally, a more variable requirement, that of maximum differential transition time - which states that the transition time can be no more than a third of the bit time of the incoming signal.

# 1.2 RS-485 Compliant Receiver

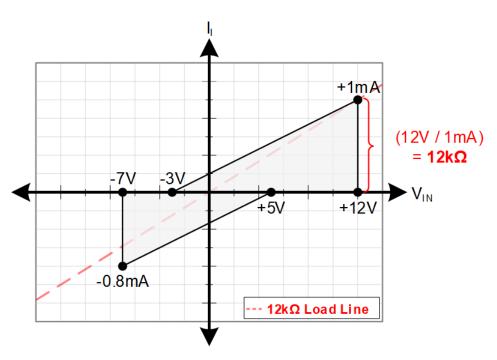

An RS-485 compliant receiver also includes a few key requirements to be compliant with the standard. The first of which is a -7 V to 12 V common mode input voltage range – like the transmitter specification it can be greater than this range but not less. Next, the receiver's sensitivity is defined through the positive going threshold (value to switch from a logic 0 to a logic 1) denoted as  $V_{IT+}$  and the negative going threshold (value to switch from a logic 0) denoted by  $V_{IT-}$ , which require that a logic 1 is guaranteed at a differential input of 200mV and above and a logic 0 is guaranteed at a differential input of -200 mV and below. It should be noted that many different possible combinations can exist for threshold values within the window defined by standard. Finally, we have the bus input current, denoted  $I_b$ , which is used to determine loading of the RS-485 bus; an RS-485 receiver has a maximum loading of 1 Unit load.

Figure 1-1. Standard Unit Load Chart for RS-485 Compliant Receivers

The standard allows 32 unit load devices on one bus – devices can also have fractional unit loads, such as 1/8<sup>th</sup> unit load, to allow for more devices on a bus.

# 1.3 RS-485 Transceiver Use Case Variability

As shown – the RS-485 requirements define a minimal set of requirements that leaves many design questions to be answered by the designer through IC selection and system design. A designer will have to consider, at minimum, the following system and application parameters when selecting an IC: bus side supply voltage, controller voltage, how many communication nodes are present on the bus, how long is the bus going to be, what is the required data-rate, does the bus need to support unterminated and terminated communication nodes, what network topology can the system support, are emissions a concern in the design, is the application full or half duplex, is there a need for protection on the device and if yes how much, is the system design static or dynamic, and finally are there any additional features needed from the RS-485 transceiver?

| System/Application Parameter               | Boundary Conditions in RS-485                                                                                            |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Bus Side Supply Voltage (VCC)              | 3 V to 5.5 V                                                                                                             |

| Controller/Logic Side Supply Voltage (VIO) | 1.65 V to 5.5 V                                                                                                          |

| Number of Nodes Supported                  | Traditionally 32, Some Modern Devices Can Support up to 256                                                              |

| Max Bus Length                             | 1.2 km at 100Kbps – faster speeds can reduce max length                                                                  |

| Data-Rate                                  | Traditionally 0 – 10Mbps, Some Modern Devices Can Support up to 50Mbps                                                   |

| Terminated and Unterminated Nodes          | 2 terminations required – both End Nodes terminated – if > 2 nodes the design requires terminated and unterminated nodes |

| Network Topology                           | Daisy Chain or Spine w/ Junction Box Strongly suggested                                                                  |

#### Table 1-1. RS-485 Boundary Conditions

With the other parameters not having set bounds leaves the designer many unanswered questions that will vary based on the system they are designing in. TI currently has over 250 various RS-485 and related RS-422 transceivers to serve the wide array of niches in the RS-485 bus. This leads to a very involved RS-485 design process that is further complicated by the IC selection process.

# 2 Traditional RS-485 Design Process

# 2.1 Design Process Overview

In general the application design flow of RS-485 systems can be thought of in four discrete steps.

- 1. Requirement Definition

- 2. IC Selection

- 3. Application Design

- 4. Validation and Qualification

While this process can change slightly from system or designer to another these steps can still largely guide RS-485 system design.

# 2.2 Requirement Definition

The first step in the process is understanding what requirements the system needs to meet beyond the standard RS-485 requirements. Well defined requirements are vital for efficient and accurate IC selection. Using the variable considerations from earlier in the note the next step is to take a brief look into how requirements impact system definition. It is also important that the designer maintains which requirements are needs (specification needed for proper system operation) versus what requirements are wants (specification that provides some technical or some other pragmatic benefit but aren't required for proper system operation) as this will help open all possible options.

# 2.2.1 Bus Voltage and Logic Voltage (VCC and VIO):

The RS-485 bus side pins can always require between 3 V to 5.5 V as a supply voltage to meet base RS-485 specifications. A higher supply can lead to a higher differential output voltage which leads to a longer maximum bus length. Depending on the power rails available some applications can only be able to support 3.3 V  $\pm$  10% supply operation. In devices with only one supply pin the logic inputs and outputs, pins that interact with a logic controller, can be related to the supply voltage VCC.

In many applications the devices controller can be operating at a different supply voltage than the bus – in some cases down 1.8 V controllers – this can require either the use of a level translator between the transceiver and controller or a transceiver that allows separate logic supplies – typically denoted on RS-485 parts as VIO.

## 2.2.2 Number of Communication Nodes Supported plus Static vs. Dynamic Systems

A designer must know how many communication nodes will need to be supported in the system – as this will define the minimum unit load fraction of a device. One important caveat for designers to consider is if the system is static or dynamic- meaning is it possible for nodes to be removed or added over the life time of the system's design? Consider an HVAC system the is originally designed for 32 units and the designer selected a 1 Unit Load RS-485 Transceiver for the wired communication in the system. Now imagine the HVAC system needs an update which will require the support of 18 additional units, this would require a redesign as 1 Unit Load devices will not be able to support a bus with 50 devices. So a designer must consider if additional nodes are possible when the original system design is conceived to avoid future redesigns and IC selections. The dynamic system could also change which nodes are terminated in a system so multiple designs may exist for the same use case.

#### 2.2.3 Max Bus Length, Network Topology, Emission Concerns, and Data Rate Required

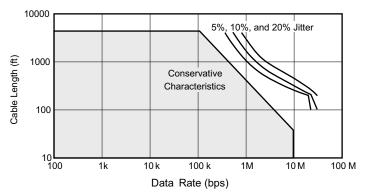

Next a designer must consider the required data rate of the system and how that impacts what the max bus length, network topology selected, and emissions generations. Traditionally RS-485 ran between 0kbps to 10Mbps, but recent developments have some parts push up to 50Mbps. However, there exists a tradeoff between speed and maximum bus length.

Figure 2-1. Typical RS-485 Cable Length v. Data Rate Performance

The designer must determine what is the minimum required speed and whether the bus length will allow for that speed – in certain cases the addition of RS-485 repeaters may be needed to overcome this limitation. To further complicate the trade-off is the question of network topology. In RS-485 only 2 nodes are terminated – so any additional node is connected to the main trunk of the bus via an unterminated stub. These stubs will act as parallel transmission lines to the main bus if they become too long relative to the transition time of the differential signal – where the maximum stub length allowed to mitigate these effects is effected by the rise time of the transceiver and the signal propagation velocity through the transmission medium.

Daisy Chained systems will minimize the stub lengths to avoid these issues and is why it is the preferred method; however, not all applications can support daisy chaining so the unterminated stub length needs to be considered when selecting a topology. In general, the faster the device the shorter the maximum unterminated stub length can be. This also is the time for the designer to consider emissions concerns, while RS-485 is an EMC friendly interface standard due to the balanced signaling, higher speed devices will increase the high frequency energy content of the signal which are more prone to causing emissions and EMI. Some RS-485 designs will need to add additional EMI protections for an added layer of robustness.

#### 2.2.4 Duplex

4

The next decision is that of the duplex of the device. Full duplex systems simultaneous bi-directional data communication therefore increasing their overall throughput, while half duplex systems allow bi-directional data communication a transceiver is either actively driving or in a listen mode. The trade off is that full duplex designs require 4 wires since there are two differential pairs per IC and half duplex only require 2 wires since there is only one differential pair.

#### 2.2.5 Protection Needs

A designer must also consider if there are any additional protection needs that extend above the standard RS-485 interface standard. Common protection needs include ESD protection, Electrical Fast Transient (EFT) protection, surge protection, and fault protection. All these designs can be either integrated within the transceiver themselves or must be added on externally on the differential bus.

#### 2.2.6 Additional Features of RS-485 Bus

Many RS-485 devices will have additional features in addition to meeting the base standard. These include, but are not limited to, auto-direction, input fail-safe protection (keeps 'R' output known during bus open, idle, and short states), polarity correction, integrated termination, flexible power rails, slew rate limiting, and power over data bus to name a few. These niche features can either be realized through selection of IC with needed features or using external circuits to realize the final circuit.

# 2.3 IC Selection, Application Design, and Validation/Qualification

With the requirements of the system defined the next three steps in the process are straight-forward and are largely guided by the first step in the process. The IC selection process will allow for quick disqualifications of parts that don't meet the absolute needs of the use case. With each additional requirement added to the RS-485 system the pool of potential parts will decrease limiting the ability of many parts to be used across varied use cases. With general bus architecture informed by the standard and with system definition finalized the actual application design has largely been tackled throughout the definition and IC selection process. Finally, there is the question of validation and qualification – depending on the end user they may do IC and system level qualification to see if the IC and system are functioning as they should. These two events are typically separate where designers don't usually have to re-qualify the same device over multiple projects so parts that fit multiple niches can be beneficial to the entire process.

With proper requirements defined the last three generalized steps are straight-forward. However, with the large amount of variability of RS-485 implementations even similar use cases could require different IC selections – adding a level of complexity to the design and qualification processes which could lead to multiple designs and additional qualification procedures.

# 3 One Multi-System Design: Flexible RS-485 with the THVD1424

# 3.1 Flexible Multi-System Design

In the first two sections RS-485 and the traditional design process has been discussed. There is ample evidence that with a minimal set of requirements, a large array of use cases, and many varied RS-485 compliant devices the design process of similar systems can require almost complete re-designs when needing to consider slight variations to the use case. This can compound the design effort needed for designers who work with RS-485 interfaces. However, the design and IC selection process can be streamlined if there was a part that could handle multiple use cases over a wide range of use cases– therefore only necessitating minimal IC qualification and minimal design changes across use cases. TI has recently introduced a part that does just that – the THVD1424.

# 3.2 Simplification of RS-485 Design Process Using THVD1424

The THVD1424 is a flexible RS-485 transceiver – which means that its use can span multiple use cases over a range of operational conditions. To highlight this – the THVD1424's specifications will be compared against the RS-485 system definition question list to see how this device will fit into the RS-485 interface.

# 3.2.1 Bus Voltage and Logic Voltage Supplies (VCC and VIO)

The THVD1424 has the option to have two different power supplies – one for the differential bus and one for the logic pins that communicate with a controller for the device. The VCC will accept a voltage of 3 V to 5.5 V for normal operation (this is the entire possible range of RS-485 applications) and its logic supply will accept from 1.65 V to 5.5 V (allowing for 1.8 V controller support). The device can be configured as a standard 3 V to 5.5 V device by shorting VCC and VIO together. So any typical RS-485 interface power supply scheme will work with the THVD1424.

# 3.2.2 Number of Communication Nodes Supported plus Dynamic or Static Systems

The THVD1424 is a 1/8 unit load device which allows up to 256 1/8 unit load devices on one differential bus. This is typically the max bound for RS-485 systems so this device can be fit into any RS-485 bus up to 256 nodes. With the THVD1424 also has a benefit in dynamic systems with its integrated termination resistors. Using the HVAC example from section 2.2 – imagine that the 50-node bus is going to be increased to 51 nodes where the new additional node becomes an end node. In traditional RS-485 systems node 49 (unterminated) has a different design than node 50 (terminated) so that means that node 51 needs to conform to node 50's design while node 50 must be reconfigured to be like node 49. This increases the chances of a technician in the field making a mistake causing a communication failure which could lead to system downtown while the problem is identified. The THVD1424 solves this problem by allowing termination to be controlled by an input on a logic pin – allowing for a simple way to change nodes between unterminated and terminated; which also cuts down on the issue of needing multiple node designs.

### 3.2.3 Max Bus Length, Network Topology, Data Rate, and Emissions Concerns

As discussed previously the max bus length, max unterminated stub length, network topology, and emissions concerns are all dependent on data-rate for the device. In general, faster devices mean shorter effective bus length and shorter unterminated stub lengths with a greater concern for EMI. In traditional design different devices would fit into different speed classifications meaning most speeds had a group of parts that serviced it. The THVD1424 on the other hand handles this issue through an integrated selectable slew rate limit option. This is controlled via 1 logic pin that when held low the device can output up to 20Mbps and when held high the devices data rate will be reduced to a maximum of 500Kbps. This allows the THVD1424 to handle faster RS-485 use cases up to 20Mbps – but in length and/or emissions sensitive systems the THVD1424 can also slow its transition times to increase the maximum stub length in a system, effective bus length, and reduce the amount of higher frequency energy generated therefore helping reduce EMI issues.

### 3.2.4 Duplex

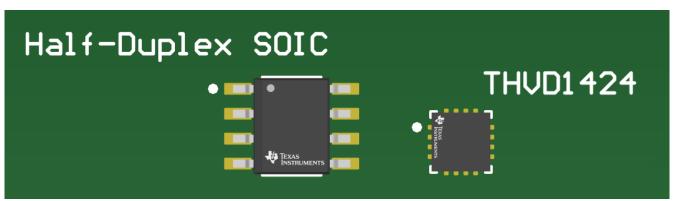

The next issue is that of the duplex of the system. Traditionally the choice is either half or full duplex without additional components. The THVD1424 doesn't have this limitation as through a simple logic pin the device can be configured into a half or full duplex communication mode without the need for additional circuitry. One concern can be: *Half Duplex devices are typically smaller than full-duplex – why would the design include a full-duplex capable part if it only ever needs a half-duplex device?* This is a legitimate concern – however the THVD1424 was designed with this concern in mind by releasing the part in a VQFN package that is only 3 mm x 3 mm compared to a traditional half duplex device in an 8-pin SOIC package which is at 4.9 mm x 6 mm – which is a little over 3x reduction in footprint size.

Figure 3-1. Standard Half Duplex RS-485 IC Package vs. THVD1424 Package

## 3.2.5 Protection Needs

The THVD1424 does also include a base level of additional protection not required by standard which will help reduce the amount of use cases where external protection would be required. For ESD protection it includes  $\pm$  16 kV HBM protection on the differential bus pins,  $\pm$  4 kV HBM on other pins,  $\pm$  1.5 kV CDM spec, IEC 61000-4-2 Contact Discharge (Differential Bus and Ground) value of  $\pm$  8 kV, and Air-Gap discharge of  $\pm$  15 kV. The device also includes  $\pm$  4 kV of EFT protection on the bus terminals as well as voltage protection of  $\pm$  16 V on the bus pins. This device provides a high level of ESD protection and adds additional protection reducing the amount of uses cases that would require external components. External components can still be added to increase the robustness of the design.

#### 3.2.6 Additional Features

As mentioned throughout this section – there are additional features on the THVD1424 which include: integrated termination, integrated ESD protection, integrated EFT protection, slew rate limiting, support of full and half duplex, and separate logic and VCC supplies allowed. These features integrated into once device allow most RS-485 applications within reach of the THVD1424's large group of potential use cases. The THVD1424 still retains the standard RS-485 bus pins so many other features can be easily added onto systems that use the THVD1424 – truly allowing it to be flexible in its use and allowing a much wider array of RS-485 compliant use cases than other RS-485 devices.

# 4 Summary

It is clear that most of the possible variability in the RS-485 design process can be handled by one RS-485 device – the THVD1424. Not only will this process also impact the difference between different application designs (with one only one-part design changes are typically marginal) but also has the potential to save on time spent qualifying devices – as a new device selection isn't needed with each new RS-485 based application.

# 5 References

- Texas Instruments, The RS-485 Design Guide application note.

- Texas Instruments, THVD1424 3-V to 5.5-V RS-485 Transceiver With Slew Rate Control, Integrated 120-Ohm Switchable Termination Resistor and Duplex Switching, data sheet.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated