## **Design Summary Power Block II**

High Volume Analog

#### ABSTRACT

Recent trends in Compact Form Factor Ultra-books and Tablet PCs are driving the electronics industry towards smaller packaging technologies. Texas Instruments (TI) addresses this trend by introducing Power Block II, a family of Synchronous Buck Dual MOSFETs that eliminates molding compound in the package and utilizes industry standard LGA concept in the silicon design. The small footprint, low height, low weight, and higher current capacity of these packages are ideal for a variety of power conversion applications where small-form-factor/space/weight limitations are essential. Power Block II packages are constructed utilizing high performance materials resulting in an ultra thin and thermally efficient packaging solution. Power Block II products reduces source inductance with respect to Industry standard Dual MOSFETs and enable high performance designs with less power dissipation. For more information, visit: www.ti.com

#### Topic

#### Page

| 1 | PCB DESIGN GUIDELINES | 3 |

|---|-----------------------|---|

| 2 | STENCIL VITALS        | 4 |

| 3 | PACKAGE PLACEMENT     | 6 |

| 4 | QUESTIONS & ANSWERS   | 7 |

|   |                       |   |

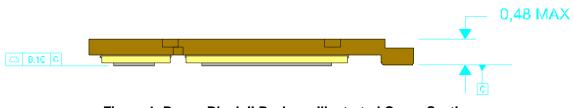

|                                      | Micro | Nano | Pico |

|--------------------------------------|-------|------|------|

| Package<br>Designator                | МРВ   | MPA  | MPC  |

| Package<br><sup>(1)</sup> Width (W)  | 3,5   | 2,5  | 2,5  |

| Package<br><sup>(1)</sup> Length (L) | 5,0   | 5,0  | 3,0  |

| Package<br>Thickness (T)<br>Max      | 0,48  | 0,48 | 0,48 |

<sup>(1)</sup> Nominal Dimensions Shown for Additional Information See Package Designator at www.ti.com

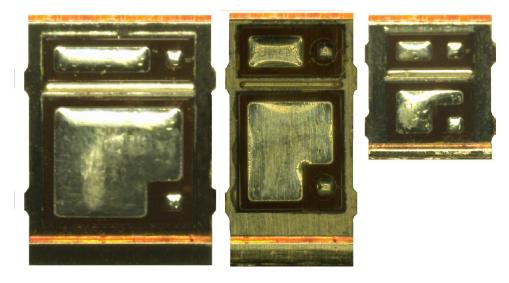

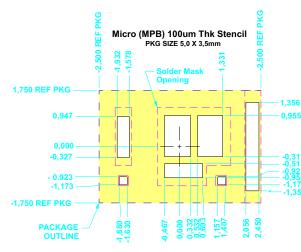

Figure 1. Power Block II Package Illustrated Cross-Section

#### PCB DESIGN GUIDELINES

#### 1 PCB DESIGN GUIDELINES

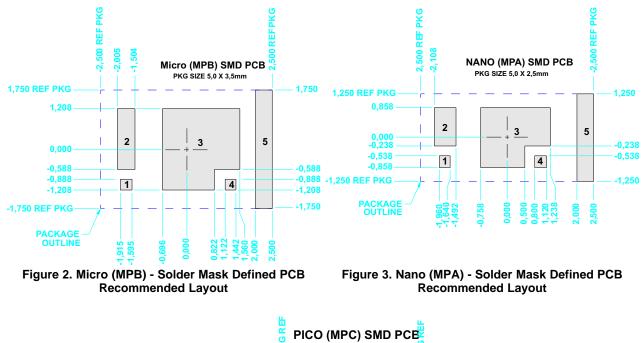

Figure 4. Pico (MPC) - Solder Mask Defined PCB Recommended Layout

#### 2 STENCIL VITALS

TI recommends stencil manufacturing by either; laser cut / electro polished or electroform

#### 2.1 Solder Paste

TI recommends the use of type 3 or finer solder paste when mounting Power Block II family. The use of paste offers the following advantages:

- It acts as a flux to aid wetting of the solder ball to the PCB land.

- The adhesive properties of the paste will hold the component in place during reflow.

- Paste contributes to the final volume of solder in the joint, and thus allows this volume to be varied to give an optimum joint.

- Paste selection is normally driven by overall system assembly requirements. In general, the "no clean" compositions are preferred due to the difficulty in cleaning under the mounted components.

The power block II series packages do not require underfill to be utilized.

TI recommends controlled placement pressure in mounting the power block II series packages. Recommended force should be controlled to 5N maximum for static and 2.5N for impact

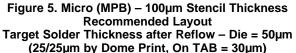

Figure 6. Micro (MPB) – 125µm Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 63µm (25/38µm by Dome Print, On TAB = 43µm)

NANO (MPA) 80um Thk Stencil PKG SIZE 5,0 X 2,5mm 0,743 0,743 0,743 0,743 0,743 0,743 0,758 0,000 0,743 0,758 0,000 0,758 0,000 0,758 0,000 0,758 0,0571 0,758 0,0571 0,0571 0,0571 0,0571 0,0571 0,0571 0,0571 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0582 0,0571 0,0582 0,0571 0,0582 0,0571 0,0582 0,0582 0,0571 0,0582 0,0582 0,0571 0,0582 0,0582 0,0582 0,0582 0,0582 0,0571 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0571 0,0582 0,0582 0,0571 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,0582 0,05

Figure 7. Nano (MPA) – 80µm Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 50µm (25/25µm by Dome Print, On TAB = 30µm)

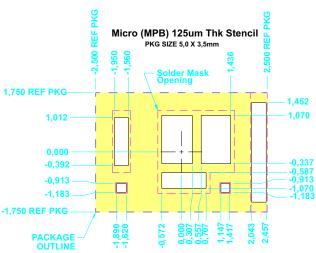

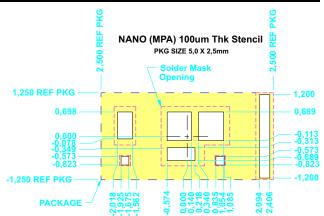

Figure 9. Nano (MPA) –125um Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 63um

(25/38um by Dome Print, On TAB = 43um)

STENCIL VITALS

Figure 8. Nano (MPA) – 80µm Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 50µm (25/25µm by Dome Print, On TAB = 30µm)

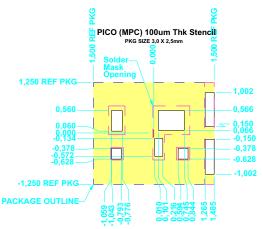

Figure 10. Pico (MPC) –100um Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 50um (25/25um by Dome Print, On TAB = 30um)

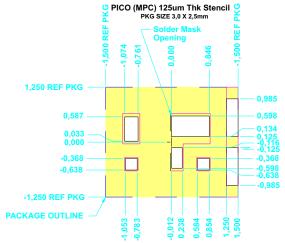

Figure 11. Pico (MPC) –125um Stencil Thickness Recommended Layout Target Solder Thickness after Reflow – Die = 63um (25/38um by Dome Print, On TAB = 43um)

#### 3 PACKAGE PLACEMENT

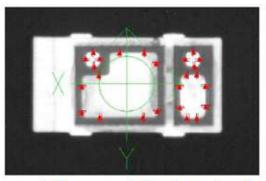

- · Alignment should be done by package outline or terminals

- · Package outline image recognition is recommended because it is more accurate

Support lead

### Alignment by outline

### Alignment by terminal

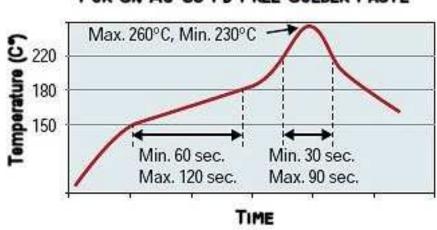

|                            | JEDEC Pb Free Profile Example |  |

|----------------------------|-------------------------------|--|

| Ramp Rate                  | 3°C/sec. Max.                 |  |

| Preheat                    | 150 to 180°C                  |  |

|                            | 60 to 120 sec.                |  |

| Time Above Liquidus        | 220°C                         |  |

|                            | 30 to 90 sec.                 |  |

| Peak Temp.                 | 260°C +0/-5°C                 |  |

| Time Within 5°C Peak Temp. | 10 to 20 sec.                 |  |

| Ramp Down Rate             | 6°C/sec. Max.                 |  |

# Temperature profile above is JEDEC Pb Free reflow compliant and shown as example only,

### RECOMMENDED TEMPERATURE PROFILE FOR SN-AG-CU PB-FREE SOLDER PASTE

#### 4 QUESTIONS & ANSWERS

### Q. Is package rework possible? Are tools available?

A. Yes, rework is possible, and there are several semi-automatic SMT rework machines and profiles available. However, TI does not guarantee the reliability of re-used packages. It is best to discard and replace any package that fails test. Please refer to the repair guideline section of this document for more details.

#### Q. Can the solder come off during shipping?

A. No, this has never been observed. The solder is 100 percent inspected for co-planarity and other physical properties prior to packing for shipment.

### Q. What size land diameter for these packages viashould I design on my board?

A. Land size is the key to board-level reliability, and Texas Instruments strongly recommends following the design rules included within this summary.

### Q. Can customers mount Power Block packages on the bottom side of the PCB board?

A. Yes, they can and the ideal 2nd reflow profile is the same as the 1st.

### Q. Are there pressure requirements for mounting PBII packages?

A. TI recommends controlling the placement pressure in mounting the PBII package. Thus force should be controlled to 5N maximum for static and 2.5N for impact.

# Q. If I want to add a heat sink to the package, what is recommended maximum torque force I can apply?

A. A heat sink can be added to package after its successfully mounted to PCB. A thermal pad is a recommended addition between package and heat sink to insure thermal conductivity. And torque force applying the heat sink should not exceed 2.7 pound-force lbs (12 N).

#### Q. Has TI developed a lead-free version of Power Block II?

A. Yes, Texas Instruments has developed the power block II series as Pb-Free option in order to comply with lead-free environmental policies.

### Q: What routing choices do I have when using Power Block PBII packages?

A: The pad design is wide enough to allow for viain-pad routing techniques to be employed on an economical basis.

### Q. Can the solder joints be inspected after reflow?

A. Many customers are achieving satisfactory results during process setup using X-ray techniques

## Q. Any EMI concerns for traces under the package and how can customers design their board to minimize EMI?

A. EMI can be controlled by minimizing any complex current loops on the PCB trace. Some helpful hints include:

- Solid ground and power planes can be used in the design. Partitioned ground and power planes must be avoided. These ground and power partitions may create complex current loops increasing radiation.

- Avoid right angles or "T" crosses on the trace. Right angles can cause impedance mismatch and increase trace capacitance causing signal degradation.

- Minimize power supply loops by keeping power and ground traces parallel and adjacent to each other. Significant package EMI can be reduced by using this method.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated