## Application Note **Application Design Guidelines for LM324 and LM358 Devices**

Ronald Michallick

Including LM124, LM224, LM2902, LM158, LM258, LM2904, LM321, TS321

#### ABSTRACT

The LM324 and LM358 family of op amps are popular and long-lived general purpose amplifiers due to their flexibility, availability, and cost-effectiveness. Understanding how these op amps are different than most other op amps before using them in your design is important. The information in this application note helps promote first-time design success.

#### **Table of Contents**

| 1 Devices Covered in Application Note                            | 3  |

|------------------------------------------------------------------|----|

| 2 Input Stage Considerations                                     |    |

| 3 Output Stage Considerations                                    |    |

| 4 AC Performance                                                 | 14 |

| 5 Low V <sub>CC</sub> Guidance                                   |    |

| 6 Comparator Usage                                               |    |

| 7 Unused Amp Connections and Inputs Connected Directly to Ground |    |

| 8 Conclusion                                                     |    |

| 9 Revision History                                               |    |

| ,                                                                |    |

## **List of Figures**

| Figure 1-1. Device Schematic from Data Sheet                                                                                                 | 3        |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2-1. Input Stage Schematic with All Current Source Connections                                                                        |          |

| Figure 2-2. Unity Gain Buffer Test Configuration                                                                                             | <b>7</b> |

| Figure 2-3. Input Current vs Input Voltage                                                                                                   | 7        |

| Figure 2-4. Output Voltage vs Input Voltage                                                                                                  | 7        |

| Figure 3-1. Schematic of Output Driver Stage With Highlighted Sink Drivers                                                                   | 9        |

| Figure 3-2. Typical Output Low Voltage vs Output Sinking Current                                                                             |          |

| Figure 3-3. I <sub>OL</sub> vs Non-Inverting Pin Voltage, V <sub>CC</sub> = 5 V, V <sub>OUT</sub> = 2 V, T <sub>J</sub> = 125°C              | 11       |

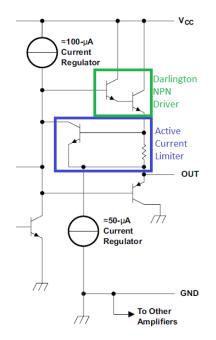

| Figure 3-4. Schematic of Output Driver Stage with Highlighted Source Driver and Current Limiter                                              | 11       |

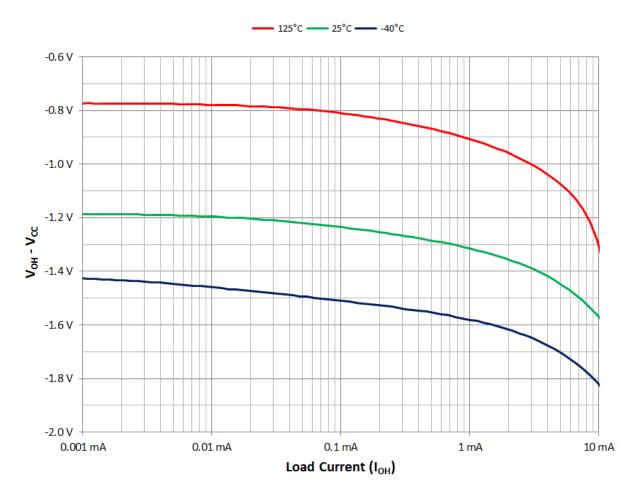

| Figure 3-5. Plot Showing V <sub>OH</sub> Relative to V <sub>CC</sub> (V <sub>OH</sub> - V <sub>CC</sub> ) vs Load Current (I <sub>OH</sub> ) | 12       |

| Figure 3-6. Plot Showing Short Circuit Current vs Junction Temperature                                                                       | 13       |

| Figure 4-1. Schematic With the Following Slew Rate Components Highlighted: Tail Current (Blue), Compensation                                 |          |

| Capacitor (Blue), Collector Current (Green), Collector to Base Capacitance (Red)                                                             |          |

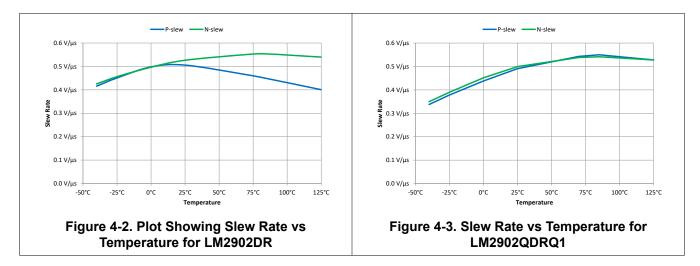

| Figure 4-2. Plot Showing Slew Rate vs Temperature for LM2902DR                                                                               | 15       |

| Figure 4-3. Slew Rate vs Temperature for LM2902QDRQ1                                                                                         | 15       |

| Figure 4-4. Schematic with the Following Time Delay Components Highlighted: Shared Input Node (Green),                                       |          |

| Compensation Capacitor (Red), and Output Transistors (Blue)                                                                                  |          |

| Figure 4-5. Crossover Test Schematic                                                                                                         |          |

| Figure 4-6. LM324 Crossover Test Waveforms                                                                                                   |          |

| Figure 4-7. Second Crossover Test Schematic                                                                                                  | 18       |

| Figure 4-8. LM358 Crossover Test Waveforms                                                                                                   |          |

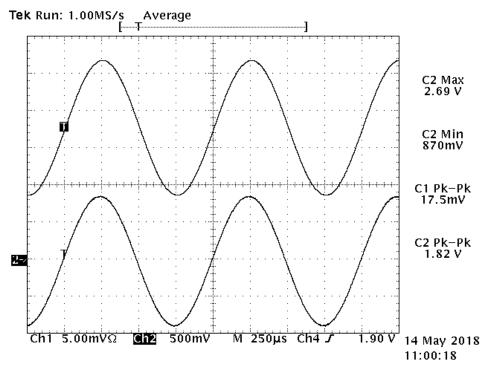

| Figure 5-1. Output Current vs Output Voltage for Pullup Resistor Usage                                                                       |          |

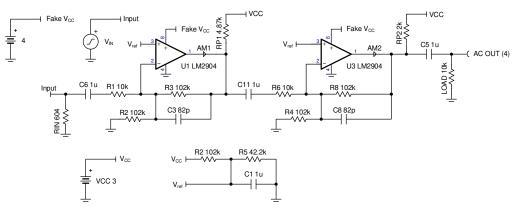

| Figure 5-2. 3-V Audio Bandpass Amplifier Schematic                                                                                           |          |

| Figure 5-3. Simulation of 1-kHz Sine Wave Transient                                                                                          |          |

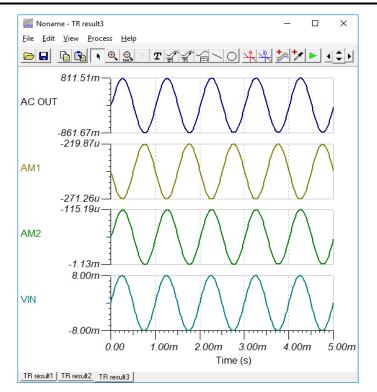

| Figure 5-4. Bench Testing 1-kHz Maximum Amplitude Without Clipping Waveforms                                                                 |          |

| Figure 5-5. Amplifier Voltage Gain vs Frequency                                                                                              |          |

| Figure 6-1. Overload Recovery Time from V <sub>OL</sub> vs V <sub>IN+</sub> , V <sub>ID</sub> = 200 mV, V <sub>CC</sub> = 30 V               |          |

| Figure 6-2. Overload Recovery from V <sub>OL</sub> State                                                                                     | 25       |

| Trademarks |

|------------|

|------------|

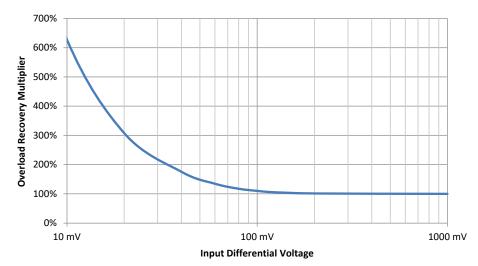

| Figure 6-3. Overload Recovery Multiplier vs Input Differential Voltage (VID)       | 26 |

|------------------------------------------------------------------------------------|----|

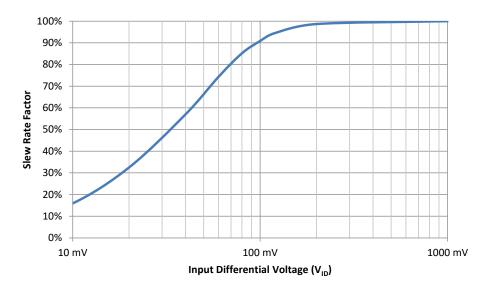

| Figure 6-4. Slew Rate Factor vs Input Differential Voltage (VID)                   | 26 |

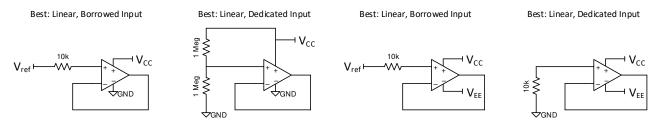

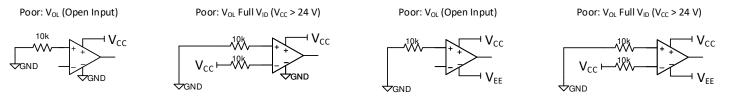

| Figure 7-1. Best Connections Practices for Single and Dual Supplies                |    |

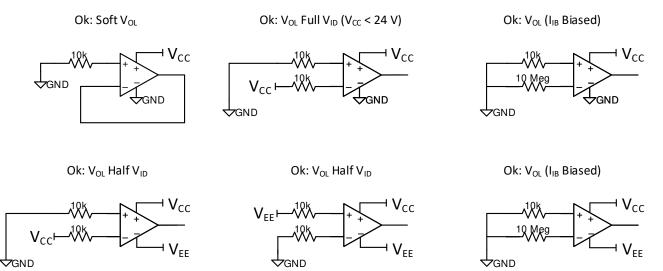

| Figure 7-2. Acceptable Connection Practices for Single and Dual Supplies           |    |

| Figure 7-3. Less Than Acceptable Connection Practices for Single and Dual Supplies |    |

| Figure 7-4. Potentially Harmful Connection Practices for Single and Dual Supplies  |    |

|                                                                                    |    |

## List of Tables

| Table 1-1. Base Part Number, Channel Count, and Temperature Range                                          | 3 |

|------------------------------------------------------------------------------------------------------------|---|

| Table 1-2. Maximum Input Offset Error at 25°C for Each Base Part Number With V <sub>IO</sub> Grade Options |   |

| Table 3-1. Data Sheet V <sub>OL</sub> Parameter Setup Conditions                                           |   |

| Table 3-2. Data Sheet Showing Output Current for 200 mV Output Voltage                                     |   |

| Table 4-1. Typical Slew Rate and Gain Bandwidth                                                            |   |

| ·····                                                                                                      |   |

## Trademarks

All trademarks are the property of their respective owners.

## **1 Devices Covered in Application Note**

## **1.1 Common Schematic**

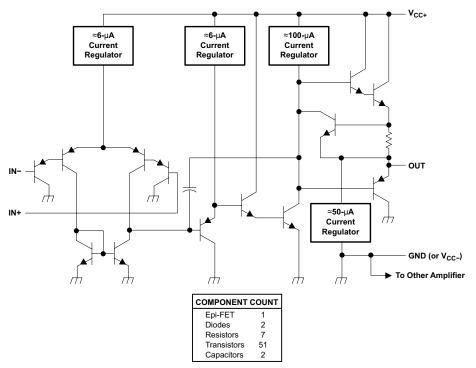

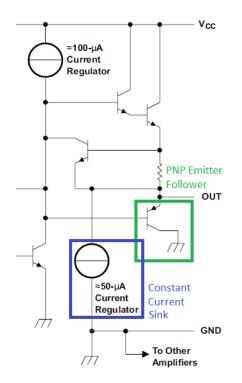

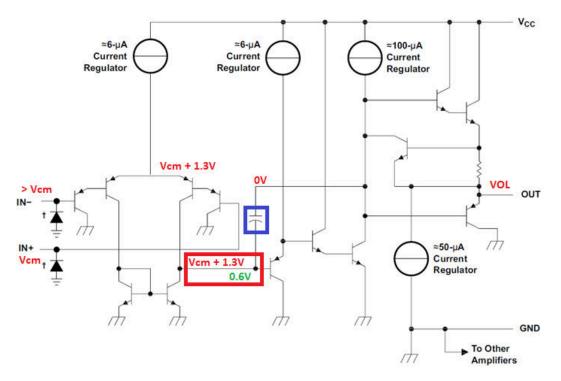

This application note covers all op amps that are based on the simplified schematic in Figure 1-1, which contains a unique output stage that was revolutionary when released. Unlike other op amps of the time, it supports a near ground output voltage useful for single supply designs. The  $\sim$ 50-µA Current Regulator can pull the output close to ground because the other transistor emitters do not have a strong opposing current flow, unlike other op amps of this time period.

Figure 1-1. Device Schematic from Data Sheet

#### 1.2 Base Part Numbers

The temperature range and channel count are used to create the base part number. The "-N" in a part name denotes devices acquired from National Semiconductor that matched an existing Texas Instruments (TI) base part number. There are no orderable part number duplicates because National Semiconductor and TI used different package suffixes. Some base numbers may include an 'A' at the end, but that does not affect the temperature range.

| Temperature Range | Sin   | gle   | Dual   |       |       | Quad     |        |       |       |          |

|-------------------|-------|-------|--------|-------|-------|----------|--------|-------|-------|----------|

| –55°C to 125°C    | —     | —     | LM     | 158   | LM1   | 58-N     | LM     | 124   | LM1   | 24-N     |

| –40°C to 125°C    | TS321 | _     | LM2904 | LM2   | 904B  | LM158-N  | LM2902 | LM2   | 902B  | LM124-N  |

| –40°C to 85°C     | TS321 | LM321 | LM2904 | LM3   | 58B   | LM2904-N | LM2902 | LM3   | 324B  | LM2902-N |

| –25°C to 85°C     | TS321 | LM321 | LM     | 258   | LM2   | 58-N     | LM     | 224   | LM2   | 24-N     |

| 0°C to 70°C       | TS321 | LM321 | LM     | 358   | LM3   | 58-N     | LM     | 324   | LM3   | 24-N     |

| Automotive Q1     | TS32  | 1-Q1  | LM29   | 04-Q1 | LM290 | )4B-Q1   | LM29   | 02-Q1 | LM290 | )2B-Q1   |

Table 1-1. Base Part Number, Channel Count, and Temperature Range

Part numbers in bold have operating temperature regions that match the given temperature range exactly. Part numbers that are not in bold can operate within and beyond the given temperature range. Please note that, counterintuitively, LM2904 is a dual op amp, whereas LM2902 is a quad op amp.

## 1.3 Input Voltage Offset Grades

There are also grade options for  $V_{IO}$  (also known as  $V_{os}$ ) tolerance. An "A" in the part number suffix has better  $V_{IO}$  specifications compared to the same part number without an "A".

| Table 1-2. Maximum Input Offset Error at 25°C for Each Base Part Number With VIO Grade | • Options |

|----------------------------------------------------------------------------------------|-----------|

|----------------------------------------------------------------------------------------|-----------|

| Single      |                          | Du          | ual                      | Quad         |                          |  |

|-------------|--------------------------|-------------|--------------------------|--------------|--------------------------|--|

| Part Number | V <sub>IO</sub> Max 25°C | Part Number | V <sub>IO</sub> Max 25°C | Part Number  | V <sub>IO</sub> Max 25°C |  |

| TS321       | 4 mV                     | LM158A      | 2 mV                     | LM124A       | 2 mV                     |  |

| TS321-Q1    | 4 mV                     | LM158A-N    | 2 mV                     | LM124A-N     | 2 mV                     |  |

| LM321       | 7 mV                     | LM2904AV    | 2 mV                     | LM2902KAV    | 2 mV                     |  |

|             |                          | LM2904AV-Q1 | 2 mV                     | LM2902KAV-Q1 | 2 mV                     |  |

|             |                          | LM358BA     | 2 mV                     | LM324B       | 3 mV                     |  |

|             |                          | LM2904BA    | 2 mV                     | LM2902B      | 3 mV                     |  |

|             |                          | LM2904BA-Q1 | 2 mV                     | LM2902B-Q1   | 3 mV                     |  |

|             |                          | LM258A      | 3 mV                     | LM224A       | 3 mV                     |  |

|             |                          | LM358A      | 3 mV                     | LM324A       | 3 mV                     |  |

|             |                          | LM358A-N    | 3 mV                     | LM324A-N     | 3 mV                     |  |

|             |                          | LM358B      | 3 mV                     | LM124        | 5 mV                     |  |

|             |                          | LM2904B     | 3 mV                     | LM124-N      | 5 mV                     |  |

| _           | _                        | LM2904B-Q1  | 3 mV                     | LM224        | 5 mV                     |  |

|             |                          | LM158       | 5 mV                     | LM224-N      | 5 mV                     |  |

|             |                          | LM158-N     | 5 mV                     | LM2902K      | 7 mV                     |  |

|             |                          | LM258       | 5 mV                     | LM2902       | 7 mV                     |  |

|             |                          | LM258-N     | 5 mV                     | LM2902-Q1    | 7 mV                     |  |

|             |                          | LM2904      | 7 mV                     | LM324        | 7 mV                     |  |

|             |                          | LM2904-N    | 7 mV                     | LM324-N      | 7 mV                     |  |

|             |                          | LM2904-Q1   | 7 mV                     |              |                          |  |

|             |                          | LM358       | 7 mV                     |              | —                        |  |

|             |                          | LM358-N     | 7 mV                     |              |                          |  |

#### 1.4 Maximum Supply Voltage

The default maximum supply voltage is 30 V; however, LM290X devices have a 26-V maximum supply rating. The exceptions are LM2902 and LM2904 devices having a "V" in the suffix, which denotes maximum voltage up to 32 V. Two examples are LM2902KAVQDR and LM2904AVQDR. All devices with a "B" in the suffix have a maximum supply voltage rated at 36 V; examples are LM358BIDR, LM2904BAIDR, LM324BIPWR, and LM2902BIPWR.

#### **1.5 High Reliability Options**

There are many high-reliability options for dual and quad op amps. For more information, please visit both the Dual Hi-Rel, and Quad Hi-Rel op-amp product lists to get the high reliability options on the parametric search.

The qualifications and ratings of these devices are not covered in this application note.

## 1.6 HBM ESD Grade

For ESD purposes, the "K" and "B" suffixes in part names have the same meaning. A "K" or "B" in the suffix of an op amp denotes an HBM ESD rating of 2 kV. For example, LM324K, LM324KA, LM324B, LM2902K, LM2902KA, LM2902B, LM2902KAV, LM2904B and LM358B all have a 2-kV HBM rating.

When greater ESD protection is desired, incorporate system-level ESD solutions into the design.

#### 1.7 LM358B, LM358BA, LM2904B, LM2904BA, LM324B, LM2902B

The "B" suffix is used to denote new device variant releases based on an advanced wafer process that provides many device improvements. Maximum supply voltage is increased to 36 V; EMI filters are added to inputs; input offset voltage is reduced (3 mV or 1.8 mV for parts with an 'A' in their suffix ); tested low V<sub>OL</sub> sink drive current is increased (from 12  $\mu$ A to 50  $\mu$ A) to support lower resistance feedback networks and more load current; I<sub>B</sub> maximum decreased (from –250 nA to –35 nA); 2-kV HBM ESD is standard. Most data sheet specifications use a setup of a load terminated to mid-supply to match modern data sheet test conditions.

## 2 Input Stage Considerations

## 2.1 Input Stage Schematic

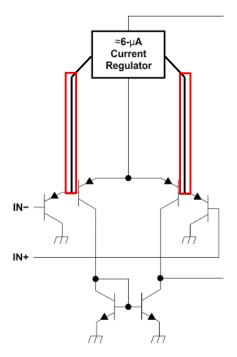

The input stage in Figure 2-1 contains additional current source lines (shown boxed in red) not drawn in the simplified schematic found in the data sheets. All PNP emitters in the Darlington input stage have current source connections. These connections ensure a consistent input bias current that does not vary with the differential input voltage. This consistent current provides a high effective input to input resistance. Without the red box current sources, the input bias current would vary from zero to twice the normal bias current as the differential input voltage is varied. This is common on other bipolar transistor input op amps. TS321 is an exception to this rule because it does not have the additional current sources.

Figure 2-1. Input Stage Schematic with All Current Source Connections

## 2.2 Input Common Mode Range

The recommended common mode range is 0 V (relative to the negative supply) to  $V_{CC} - 2$  V over the full temperature range. However, the actual upper common mode range varies by approximately 4 mV/°C, with cold temperatures reducing the upper limit of the common mode voltage range. For die temperatures above 125°C, offset voltage at  $V_{CM} = 0$  V may be degraded.

Note that when used as a comparator, only one input needs to be within the common mode range. The other input can be above the common mode range or above  $V_{CC}$  and the output will be the expected  $V_{OH}$  level (for  $V_{in}$ + >  $V_{in}$ -) or  $V_{OL}$  level (for  $V_{in}$  - >  $V_{in}$ +). If both inputs exceed the upper common mode range, the output is undefined; it could be either the  $V_{OL}$  or  $V_{OH}$  level and the result may vary part-to-part, lot-to-lot, over process, over temperature, etc. If either input or both inputs are lower than -0.3 V with respect to the negative supply, excessive input current can flow and the output may display phase reversal, also called inversion.

Because the inputs have no internal diodes to  $V_{CC}$ , the input voltage can exceed the  $V_{CC}$  voltage. If this occurs, the input will block current flow due to a reverse biased diode forming in the input PNP transistor. Current flow is blocked even if  $V_{CC}$  equals 0 V. If either input or both inputs exceed maximum the  $V_{CC}$  rating, junction breakdown can occur. This may lead to permanent device damage per the table notes in the respective device's data sheet *Absolute Maximum Ratings* table.

## 2.3 Input Impedance

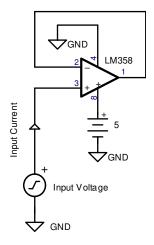

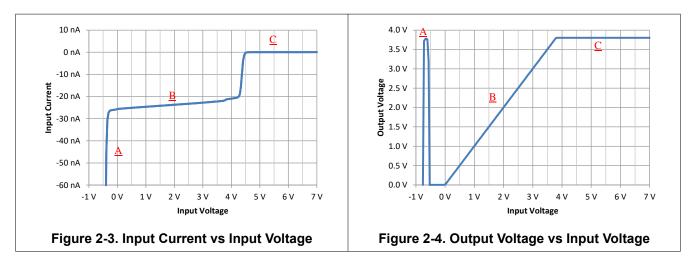

The input stage uses a Darlington PNP configuration with dedicated internal current sources on all of the transistor emitters. Therefore the input appears as a current source to the application. This current is the input PNP transistor's base current whose value is specified in the data sheet as  $I_{IB}$ . This effective input current source has a high impedance of approximately 1 G $\Omega$  and a wide voltage range compliance from 0 V to one diode drop below  $V_{CC}$ , including cases where a large differential input voltage is present (see Figure 2-3 region B). When the input voltage is greater than one diode voltage drop below  $V_{CC}$  or is greater than  $V_{CC}$ , the input becomes high impedance and no current flows other than a reverse diode leakage current (see Figure 2-3 region C). Matching the input resistance can reduce the input offset voltage from  $I_{IB}$ . This can be done by placing matching resistors on the inputs. Note that the consequential increase in resistor thermal noise may be unacceptable.

The input current profile for a unity gain buffer powered by a 5-V supply, shown in Figure 2-2, can be seen in Figure 2-3. Applying a negative input voltage will forward bias a diode formed from the input PNP transistor's base to the die's grounded substrate on the input pin. The result will be high current flow as indicated by the vertical slope near -0.5 V (region A). An input between 0 V and 3.5 V (region B) has a fixed current (I<sub>IB</sub>) with an impedance of approximately 1 G $\Omega$ . Region C spans from 4.5 V to 7 V and beyond, continuing up to a maximum of V<sub>CC</sub> where there is no input current flow.

Figure 2-2. Unity Gain Buffer Test Configuration

## 2.4 Phase Reversal

Under certain conditions, the polarity of the output voltage can become inverted. This scenario, called "phase reversal," occurs when the input of the amplifier violates the common-mode voltage range. Figure 2-4 region 'A' shows output phase reversal from an invalid input voltage. A negative input voltage, relative to a grounded V– pin, may come from unexpected sources, such as switching noise or ground bounce in DC to DC converters. Negative input voltages can also arise when rapid fall times and large capacitors combine to temporarily set a negative voltage at the input. An input voltage of less than -0.3 V can cause parasitic diode conduction that results in the output assuming the minimum  $V_{OL}$  or maximum  $V_{OH}$  level. Operation in this region is not defined in the data sheet as it violates the absolute maximum specification for input voltage. The input current turns on internal parasitic NPN transistors that steal current from other internal nodes causing output phase reversal.

Do not try to determine phase reversal performance empirically as different units may have different performance. Negative inputs must be avoided, assuming a single supply configuration, unless the application can accept either the  $V_{OL}$  or  $V_{OH}$  level during the duration of the negative input. In cases where a negative input voltage cannot be avoided, use a resistor in series with the input to limit the current to -1 mA or less. This amount of input current is unlikely to cause any damage. If both inputs are above the upper common mode range, the output is undefined; it could be either  $V_{OL}$  or  $V_{OH}$ . This affects comparator applications, but normal, negative feedback applications are generally not affected because the upper limit of the input voltage range is the same as output high range ( $V_{OH}$ ).

## **3 Output Stage Considerations**

## 3.1 Output Stage Schematic, $V_{OL}$ and $I_{OL}$

The op amp can provide a low output voltage near the negative rail, provided that the load and load termination voltage are aiding the 'Constant Current Sink' driver shown in Figure 3-1. Table 3-1 states that the output low voltage is less than 20 mV with a 10-k $\Omega$  or less load, assuming the negative supply is at GND. Therefore, if the load resistor is 10 k $\Omega$  or less and is terminated to the negative rail, then the load resistor helps the "Constant Current Sink" provide a very low output voltage.

| Table 3-1. Data Sheet V <sub>OL</sub> | Parameter Setup Conditions |

|---------------------------------------|----------------------------|

|---------------------------------------|----------------------------|

| Parameter                                | Test Conditions        | Typical | Maximum |  |  |

|------------------------------------------|------------------------|---------|---------|--|--|

| V <sub>OL</sub> Low-Level Output Voltage | R <sub>L</sub> ≤ 10 kΩ | 5 mV    | 20 mV   |  |  |

If the op amp load, including the feedback network, is terminated to a positive voltage, then the op amp must sink current when driving the output low. The output stage seen in Figure 3-1 has a weak constant current sink consisting of a current regulator that provides a low output voltage for low levels of sink current. The PNP emitter follower can provide a much higher sink current at a higher output voltage.

The output pin can sink over 12  $\mu$ A and still have a less than 200-mV output low level as seen in Table 3-2. From the electrical characteristics table in the data sheet, the typical output current is 30  $\mu$ A or 40  $\mu$ A. The "~50 $\mu$ A Current Regulator" in the device schematic is called a "constant current sink" driver in this application note because the current value is not necessarily 50  $\mu$ A, as per the electrical characteristics table. Note that the data sheet specification has no maximum limit.

| Table 3-2. Data Sheet Showing Output Current for 200 my Output voltage |                                                 |         |         |  |  |  |

|------------------------------------------------------------------------|-------------------------------------------------|---------|---------|--|--|--|

| Parameter                                                              | Test Conditions                                 | Minimum | Typical |  |  |  |

| I <sub>O</sub> Output Current                                          | V <sub>ID</sub> = 1 V < V <sub>O</sub> = 200 mV | 12 µA   | 40 µA   |  |  |  |

Table 3-2. Data Sheet Showing Output Current for 200 mV Output Voltage

The output low voltage is less than 200 mV when sinking up to 12  $\mu$ A. At higher current levels, the constant current sink is no longer sufficient. So, the PNP emitter follower supplies this current. However, no current is provided by the PNP emitter follower until the output voltage is approximately 600 mV, assuming room

temperature. Note that when the PNP emitter follower is active, the  $V_{OL}$  level has a temperature coefficient of approximately  $-2 \text{ mV/}^{\circ}\text{C}$ . The PNP emitter follower provides a low output impedance and the base current flows to the output load for a higher efficiency.

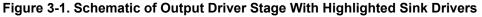

Figure 3-2 plots the low output voltage level vs the sinking current. As can be seen, there is an obvious transition from the constant sink driver (region "A") to the PNP emitter follower (region "B"). Note that the constant sink driver, as its name suggests, is always on.

Figure 3-2. Typical Output Low Voltage vs Output Sinking Current

In Figure 3-2, two example load lines, a 16-k $\Omega$  (solid black line) resistor line and 300-k $\Omega$  (dotted black line) resistor line, are shown terminated to 5 V. The 300-k $\Omega$  load line intersects the device performance curves at a low V<sub>OL</sub> level across supply voltage and temperature. Therefore, a low V<sub>OL</sub> can be expected for this load. The 16-k $\Omega$  load line intersects the device performance curves at a higher V<sub>OL</sub> that varies with temperature, but not with V<sub>CC</sub>. With this load, a V<sub>OL</sub> near the negative supply is not possible. If having a low V<sub>OL</sub> is important, use high resistance loads or loads (including feedback) terminated to the negative supply.

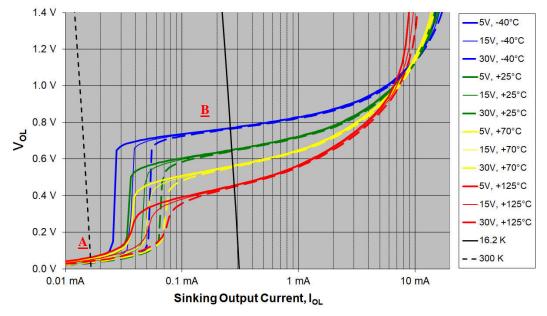

#### 3.2 I<sub>OL</sub> and Common Mode Voltage

When the op amp is used to sink high current, consider making the input common mode greater than 0.8 V. Also, the maximum sink current of the PNP emitter follower can be reduced when the non-inverting input is 0 V and the junction temperature is high. Figure 3-3 shows the relation between the non-inverting input voltage and the sinking current with a 2-V output and a junction temperature of 125°C. Op amps with "B" in the name suffix have  $I_{OL}$  that is less sensitive to the low non-inverting pin voltage.

Figure 3-3.  $I_{OL}$  vs Non-Inverting Pin Voltage,  $V_{CC}$  = 5 V,  $V_{OUT}$  = 2 V,  $T_J$  = 125°C

Shorts to positive voltage may damage the device as stated in the absolute maximum rating table in the data sheets. Damage is more likely if the short voltage is greater than 10 V relative to the GND, or V–, pin.

#### 3.3 Output Stage Schematic, $V_{OH}$ and $I_{OH}$

Unlike most new op amps that have a rail-to-rail output, this family of op amps has a high level output voltage that is significantly lower than the  $V_{CC}$  power rail, regardless of the load sourcing current. Figure 3-4 shows the Darlington NPN transistors that provide sourcing current. An active current limiter helps protect the op amp and load from overcurrent conditions.

#### Figure 3-4. Schematic of Output Driver Stage with Highlighted Source Driver and Current Limiter

The Darlington NPN provides a low output impedance and the base current flows to the output load for higher efficiency. This setup has a high headroom requirement that significantly reduces the V<sub>OH</sub> level. The two base emitter junctions in the Darlington NPN have a combined temperature coefficient of approximately –4 mV/°C. Therefore V<sub>OH</sub> has an equal and opposite temperature coefficient of 4 mV/°C. Per the data sheet *Electrical Characteristics* tables, the V<sub>OH</sub> level is V<sub>CC</sub> – 1.5 V or better with a 2-k $\Omega$  load to ground when V<sub>CC</sub> is 5 V at 25°C;

this is 1.75 mA. The typical V<sub>OH</sub> level varies with load current and also varies with temperature as seen in Figure 3-5. V<sub>OH</sub> performance relative to V<sub>CC</sub> is independent of V<sub>CC</sub>, which means the set of curves in Figure 3-5 apply to the entire operating range of V<sub>CC</sub>.

Figure 3-5. Plot Showing V<sub>OH</sub> Relative to V<sub>CC</sub> (V<sub>OH</sub> - V<sub>CC</sub>) vs Load Current (I<sub>OH</sub>)

#### 3.4 Short Circuit Sourcing Current

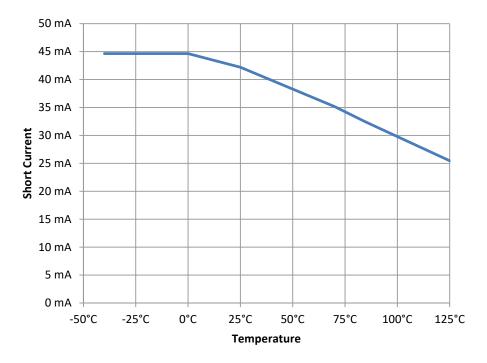

The Darlington NPN driver has a current limiting circuit to protect against shorts to ground. The current limiting feature protects the device from immediate damage. However, device overheating can occur during prolonged shorts especially when the  $V_{CC} - V_{OUT}$  voltage is high. Note that power dissipation in the op amp is (( $V_{CC} - V_{OUT}$ ) ×  $I_{OUT}$ ). The op amp sets  $I_{OUT}$  and the application determines both the  $V_{CC}$  value and the short voltage,  $V_{OUT}$ , affecting the power dissipated. The op amp has no over-temperature shutdown circuitry. Therefore, excessive power dispassion can lead to very high die temperature. The data sheet absolute maximum ratings table only allows shorts to ground for  $V_{CC} \le 15$  V. The current limit magnitude, in Figure 3-6, decreases as die temperature increases.

Figure 3-6. Plot Showing Short Circuit Current vs Junction Temperature

## 3.5 Output Voltage Limitations

Do not pull the output below the GND (V<sub>CC</sub>–) pin or pull the output above the V<sub>CC</sub> (V<sub>CC</sub>+) pin. High output pin current can damage the op amp.

## 4 AC Performance

## 4.1 Slew Rate and Bandwidth

All slew rate and bandwidth specifications are typical and not tested in production. The typical values vary marginally among channel count variants. Op amps with "B" in the name suffix have a typical slew rate of 0.5 V/ $\mu$ s, and bandwidth of 1.2 MHz. Op amps without "B" in the name suffix are listed in Table 4-1.

| Typical   | Single   | Dual     | Quad     |  |  |

|-----------|----------|----------|----------|--|--|

| Slew Rate | 0.4 V/µs | 0.3 V/µs | 0.5 V/µs |  |  |

| Bandwidth | 0.8 MHz  | 0.7 MHz  | 1.2 MHz  |  |  |

#### Table 4-1. Typical Slew Rate and Gain Bandwidth

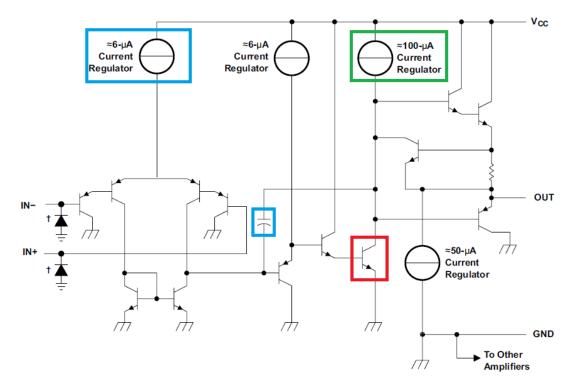

## 4.2 Slew Rate Variability

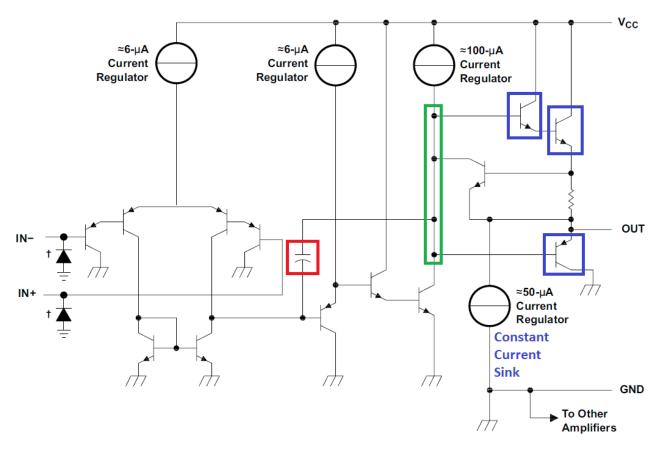

It is best to allow for some margin between the application's slew rate requirement and the typical slew rate of the device used. Normal process variance affects internal bias currents and capacitor oxide thickness, which are two factors that determine slew rate. These components are highlighted in blue in Figure 4-1. There may also be a slight difference between the positive and negative slew rates. The reason for this difference is simple: the transistor in the red box in Figure 4-1 has no turn off drive. The NPN transistor driving the red box transistor can only source current to turn on, but cannot sink current to turn off. The base to collector capacitance of the transistor in the red box in this device family varies among the dies in production. The beta of the NPN transistor is also a factor in determining slew rate. If the natural turn off slew rate of the red boxed transistor

$$SR_{Natural} = \frac{100 \ \mu A}{\beta_{NPN} \times Cap_{CB}}$$

is slower than the slew rate set by the bias and compensation capacitor

$$SR_{Comp} = \frac{6 \ \mu A}{Cap_{Comp}}$$

then the positive slew rate is reduced while the negative slew rate is not affected. Hence, the positive slew rate can be slower than the negative slew rate. LM358B, LM2904B, LM324B, and LM2902B have a discharge path for the base of the red boxed transistor. Therefore, the slew rate is not affected by this highlighted transistor.

# Figure 4-1. Schematic With the Following Slew Rate Components Highlighted: Tail Current (Blue), Compensation Capacitor (Blue), Collector Current (Green), Collector to Base Capacitance (Red)

Only the commercial grade quad op amp with the widest input offset specification has a die with enough base-collector capacitance to typically demonstrate variation in high temperature slew rates. Slew rate differing in all other device variants will be a rare occurrence. The key point is not to depend on matching slew rate. Fortunately, few circuits actually require matching slew rate. For reference, the slew rate curves of two common devices are shown below with the commercial grade in Figure 4-2 and the automotive grade in Figure 4-3. Note that the other die designs typically have matching positive and negative slew rates. A small percentage of samples may exhibit some differences at high temperature.

## 4.3 Output Crossover Time Delay

This op amp family does not provide any static bias for any of the output transistors (Class B type) highlighted in the blue boxes in Figure 4-4. Most other op amp designs provide a small static bias to the output transistors (Class AB type) to make output current transitions seamless. The advantage of having no static bias is allowing

the 'Constant Current Sink' driver to pull the output close to the negative supply voltage. The disadvantage of having no static bias is a time delay when switching between the output source and sink drivers.

# Figure 4-4. Schematic with the Following Time Delay Components Highlighted: Shared Input Node (Green), Compensation Capacitor (Red), and Output Transistors (Blue)

The op amp's Darlington NPN driver and PNP emitter follower output transistors share an input signal highlighted in the green box. The compensation capacitor is also connected to this common node. Therefore, the slew rate of the green node is the same as the output's slew rate, which can be found on the data sheet as a typical value. When the op amp needs to change between the Darlington NPN and PNP emitter follower drivers, there is a time delay of approximately

$$T_{Delay} = -\frac{3 \times V_{BE}}{Slew Rate}$$

Depending on the application, this delay may or may not be significant. The maximum application frequency and load current range are relevant factors in determining whether or not the time delay will be significant.

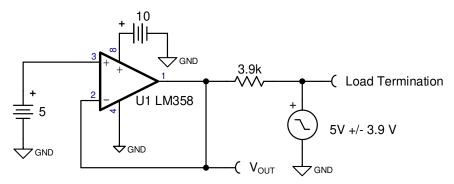

Two test circuits, shown in Figure 4-5 and Figure 4-7, are specifically designed to maximize the visual effect of the crossover time delay. In many applications, the crossover time does not cause any issues. However, extra care should be taken when there are high frequency signals, fast rise or fall times, or when distortion must be minimized. Output pull down or pull up resistors can be added to keep either the output source or sink driver continually active, thereby preventing time delays.

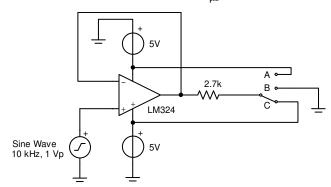

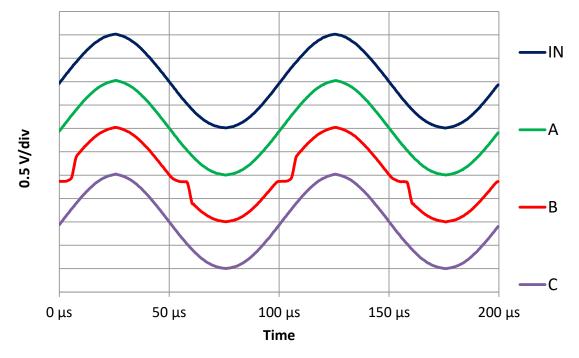

## 4.4 First Crossover Example

The first example test circuit in Figure 4-5 uses the LM324 as a 10-kHz frequency sine wave buffer. The input signal is a  $\pm$ 1-V peak, 10-kHz sine wave. The supply voltage is  $\pm$ 5 V. The load is always 2.7 k $\Omega$ , regardless of the switch position. But, the termination voltage for the resistor can be switched between –5 V, 0 V, and 5 V. Ideally, the op amp output would follow the input voltage sine wave as the load current is small and the output slew rate required is well below the typical slew rate specification.

$SR_{Required} = V_{PP} \times f \times \pi = 2V \times 10 \text{kHz} \times \pi = 0.063 \frac{V}{\text{us}}$

Figure 4-5. Crossover Test Schematic

**Case A:** With the switch in position "A", the load resistor is terminated to -5 V. So, the op amp will always source current. This current will vary from 1.48 mA to 2.22 mA. The output will follow the input as the Darlington NPN driver is always active as seen in the green waveform in Figure 4-6.

**Case B:** With the switch in position "B", the load resistor is terminated to 0 V, or mid-supply. Therefore, the op amp will source and sink current, requiring the output to change drivers. The current will vary from -0.37 mA to 0.37 mA. Since the output driver will switch between PNP and NPN, the green box node voltage in Figure 4-4 has to slew to a voltage of three times V<sub>BE</sub> before the output voltage can change. At 25°C, the time needed to switch current polarity is

$$\frac{3 \times V_{BE}}{\text{Slew Rate}} = \frac{2 V}{0.5 V/\mu s} = 4 \ \mu s \tag{1}$$

The output waveform flattens for 4  $\mu$ s as only the weak constant current sink is active and neither the Darlington NPN driver nor the PNP emitter follower drivers are active during this time. See the red waveform in Figure 4-6. The voltage value of this flat time is 2.7 k $\Omega$ , or the load resistance, multiplied by the constant current sink value. After the delay, the output voltage changes at the device's slew rate limit until it assumes the correct value. This happens each time the op amp switches between the source current and sink current drivers. The constant current sink is always on, but it is insufficient current to drive the 2.7 k $\Omega$  load resistor to -1 V by itself. Only the newest device simulation models dated 2018 or later include this time delay in the model.

**Case C:** With the switch in position "C", the load resistor is terminated to 5 V. Thus, the op amp will always sink current. The current will vary from -1.48 mA to -2.22 mA. The output will follow the input as the PNP emitter follower will always be active. See the purple waveform in Figure 4-6.

Figure 4-6. LM324 Crossover Test Waveforms

## 4.5 Second Crossover Example

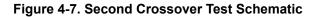

Crossover can also occur when the load current changes from an external source as seen in Figure 4-7. The LM358 is set up as a reference voltage buffer and the load current alternates between 1 mA and –1 mA.

The LM358 load current is stepped ±1 mA using a pulse generator square wave and a series resistor. Ideally, the output voltage should be constant at 5 V. However the output voltage jumps by 2 V, or about  $3 \times V_{BE}$ , before the other output driver can provide current flow. At 25°C, the time needed to correct the output signal back to 5 V is about

$$\frac{2 V}{0.3 V/\mu s} = 6.7 \ \mu s \tag{2}$$

The LM358 has a slower typical slew rate than the LM324. Consequently, the time delay is greater in the LM358. The oscilloscope capture in Figure 4-8 shows as example output waveform in red and a pulse generator output in dotted blue. From this real-world data, we see that output crossover can create output steps and flat waveforms followed by a correction period.

Figure 4-8. LM358 Crossover Test Waveforms

## 5 Low V<sub>CC</sub> Guidance

The minimum  $V_{CC}$  for this device family is 3 V and many applications use a 5-V supply with good results. For lower supply voltages, such as those in the range of 3 V to 3.6 V, pay careful attention to the input and output voltage ranges. Note that these are especially limited at the device's lowest operating temperature. For more information on this topic and device family, please consult the General Purpose Amps at Low Voltage blog.

#### 5.1 Low V<sub>CC</sub> Input Range Supporting –40°C

The input common mode range for the op amp with a 3-V supply at  $-40^{\circ}$ C is 0 V to 1 V, as per the data sheet. This design requirement is easy to meet when the input signal is small. It is also easy to meet when an inverting gain configuration is used because this configuration allows for a fixed common mode voltage to be set between 0 V and 1 V.

## 5.2 Low V<sub>CC</sub> Output Range Supporting –40°C

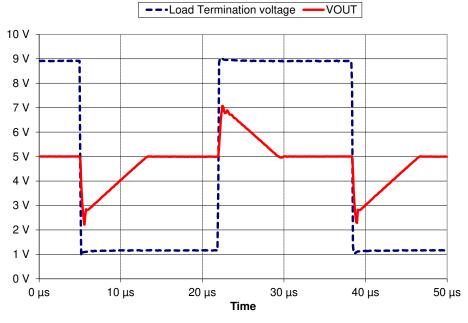

The output range is typically 0.75 V to 1.5 V for a bidirectional load current of 100  $\mu$ A at -40°C. This output range is just 25% of the supply voltage range. The output range can be increased to 0.1 V to 1.5 V with a bidirectional load current of 12  $\mu$ A. If all loads terminate to ground, then the output range is 0 V to 1.4 V for a 1-mA load. The largest output range possible requires using an external pullup resistor. For example, using a 5-k $\Omega$  resistor gives a typical -40°C output range from 0.8 V to 2.7 V.

Lower resistance gives more design margin and a slightly higher, typical range.  $V_{OH}$  improves with lower resistance, but  $V_{OL}$  degrades and power consumption increases. The op amp does not oppose the pullup resistor other than the constant sink driver current that is always on. The high output level is limited by the pullup resistor, feedback, and other loads. The constant sink current driver reduces  $V_{OH}$  as this current flows through the pullup resistor. All of the output ranges in this section are based on the typical  $V_{OH}$  and  $V_{OL}$  curves in this application note. Always add design margin when using typical data.

Figure 5-1 shows typical  $I_{OH}$  vs  $V_{OH}$  curves given  $T_a = 25^{\circ}$ C and  $V_{CC} = 3$  V. The constant current sink driver from Figure 3-1 is responsible for this current flow. This current value can vary from device to device and across temperature. Do not pull up the output to a voltage higher than  $V_{CC}$  unless an external diode to  $V_{CC}$  is used to limit output voltage.

The output V<sub>OH</sub> level is significantly increased by a pullup resistor that provides at least 100  $\mu$ A. In Figure 5-1, output current vs output voltage was measured. Two pullup resistor load lines, 2 k $\Omega$  and 5 k $\Omega$ , are included on

the chart. With no pullup resistor or any other load, the current is zero and V<sub>OH</sub> is 1.8 V. The 5-k $\Omega$  resistor load line intersects the output current curve at V<sub>OH</sub> = 2.73 V and the 2-k $\Omega$  load line intersects the output current curve at V<sub>OH</sub> = 2.88 V. If the output current were 100  $\mu$ A, then V<sub>OH</sub> would be reduced to [2.8 V, 2.5 V] for the [2k, 5k] loads. Note that another advantage of unidirectional current or very low bidirectional current is the lack of time delay that occurs when switching between the NPN Darlington and PNP emitter follower drivers.

In this family of devices, TS321, LM358B, LM2904B, LM324B, and LM2902B typically have higher constant sink currents. Therefore, pulldown resistors are recommended instead of pullup resistors for these parts.

## 5.3 Low $V_{CC}$ Audio Amplifier Example

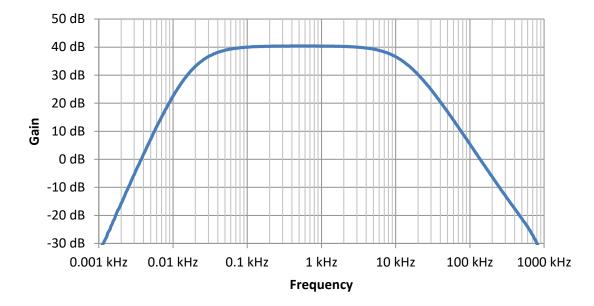

To demonstrate that 3 V is a usable yet challenging supply voltage, an example involving a 3-V audio preamplifier with LM2904DR is considered (see Figure 5-2). This amplifier has a 40-dB bandpass gain and –3-dB corners at 30 Hz and 10 kHz. Pull up resistors (RP1, RP2) were added to increase the output range to 0.9 V to 2.7 V at the worst case temperature of –40°C. For a maximum output swing without clipping, an output bias point of 1.76 V was used, which is halfway between the expected V<sub>OL</sub> and V<sub>OH</sub> values, and the input bias point is was at half of the output, 0.88 V because it is simple and meets the 0-V to 1-V input range. Higher temperature will improve the V<sub>OL</sub> range and a higher V<sub>CC</sub> will improve the V<sub>OH</sub> range. This means there is more design margin against low peak output clipping at warmer temperatures and more design margin against high peak output clipping with a larger V<sub>CC</sub>.

Figure 5-2. 3-V Audio Bandpass Amplifier Schematic

For the resulting simulation to work correctly, a "fake"  $V_{CC}$  set to 4 V was used because the LM2904 model does not support pull up resistors that improve  $V_{OH}$ . The model fights the pull up resistor, but real-world devices will not do so. AM1 and AM2 simulation meters are used to check the output current's magnitude and polarity. Ensure the current meters are more negative than  $-100 \ \mu$ A. The current needs to be greater than a strong constant current sink sample so the PNP emitter follower always conducts some current to prevent crossover time delay. Figure 5-3 is the simulation result for the output voltage and output currents. The minimum negative output current is more negative than  $-100 \ \mu$ A with an 8-mV peak input signal.

Figure 5-3. Simulation of 1-kHz Sine Wave Transient

Figure 5-4 shows the bench test results for  $V_{CC} = 3 \text{ V}$  at  $T_a = -40^{\circ}\text{C}$ . From the resulting plots, the maximum output without clipping was 1.82  $V_{pp}$ . The top waveform is the U3 output and the bottom waveform is the input signal. Figure 5-5 shows the plot of gain vs frequency at  $V_{CC} = 3 \text{ V}$ ,  $T_a = 25^{\circ}\text{C}$ .

From this discussion we can conclude that 3-V supply designs can be used successfully. However, applications using 5-V or higher supply will be easier to design.

Figure 5-4. Bench Testing 1-kHz Maximum Amplitude Without Clipping Waveforms

Figure 5-5. Amplifier Voltage Gain vs Frequency

## 6 Comparator Usage

## 6.1 Op Amp Limitations

Op amps generally do not make good comparators. However, there are reasons to occasionally use an op amp as a comparator. These include having an unused amplifier, having no timing requirements, and having inputs that exceed  $V_{CC}$ .

## 6.2 Input and Output Voltage Ranges

When using an op amp as a comparator, the key DC parameters to consider are input offset voltage, input common mode range, low output voltage ( $V_{OL}$ ) and high output voltage ( $V_{OH}$ ). It is important to maintain a valid input common mode, otherwise phase reversal may occur as discussed earlier in this document. When used in a comparator application, the input common mode voltage of the op amp will be the same as the least positive input voltage. For example, if one input is 2 V and the other input is 3 V, the common mode voltage would be 2 V. The voltage of the other, higher voltage input doesn't affect the input common mode voltage in this device family and many other PNP and PMOS op amp families.

## 6.3 Overload Recovery

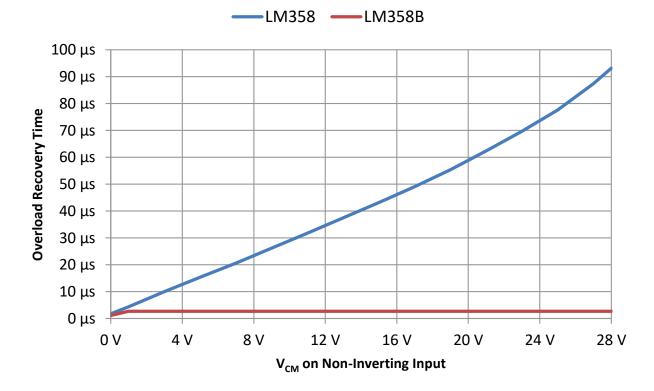

Overload recovery time is analogous to comparator propagation delay. Overload occurs when an op amp's input voltage difference is large enough such that the output reaches either the  $V_{OL}$  or  $V_{OH}$  level and the output no longer changes with variations in the input. Some internal node voltages will continue to change even though the op amp output is not changing. The overload condition ends when the input voltage difference is reduced to a point where the op amp returns to a linear operating region or the input voltage polarity is reversed. After the overload condition is removed, there is a finite time delay before the output can change from the V<sub>OL</sub> or V<sub>OH</sub> level. This delay is the overload recovery time. The data sheet does not specify an overload recovery time parameter. The recovery time when the output is at the V<sub>OH</sub> level is approximately 2  $\mu$ s, regardless of the common mode voltage. The recovery time when the output is at V<sub>OL</sub> varies with the common mode voltage present at the non-inverting input as seen in Figure 6-1.

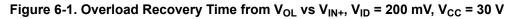

The reason for variable overload recovery time for  $V_{OL}$  is shown in Figure 6-2. The voltage of the difference amplifier stage output (red box node) normally runs near 0.6 V when the op amp is in the linear (normal) operation mode. During a negative ( $V_{ID} < 0$ ) input overload event where the output is at the  $V_{OL}$  level, this node rises to  $V_{CM}$  + 1.3 V while the other side of the capacitor is 0 V. This charges the capacitor to a voltage set by the voltage present on IN+ pin.

LM358B, LM2904B, LM324B, and LM2902B limit the voltage of the red box node to 1.2 V. Consequently, the overload recovery time does not increase with the IN+ voltage. When the input overload is removed, the difference amp output node voltage returns to 0.6 V. The time for this to happen depends on the input voltage difference and internal factors, such as the current of the leftmost 6-µA current regulator and the capacitance of the internal compensation capacitor highlighted in the blue box in Figure 6-2.

Figure 6-2. Overload Recovery from V<sub>OL</sub> State

In addition to the overload recovery time of 2  $\mu$ s from the V<sub>OH</sub> state or the overload recovery time in Figure 6-1 from the V<sub>OL</sub> state, the input voltage difference applied during the input recovery time is also a factor in the actual recovery time. One can multiply the internal factor time (2  $\mu$ s or the time from Figure 6-1) by the scalar value in Figure 6-3 to get the final expected recovery time. V<sub>ID</sub> is the voltage applied while waiting for the recovery time.

Figure 6-3. Overload Recovery Multiplier vs Input Differential Voltage (VID)

For example, assume the LM358 output is in a V<sub>OL</sub> state, the non-inverting input is 10 V, and the inverting input is 10.05 V. If the inverting input suddenly drops to 9.98 V, then the output will start increasing after approximately 90  $\mu$ s. The input common mode was 10 V, which makes the overload recovery time 30  $\mu$ s, per Figure 6-1. The input difference is 10 V – 9.98 V = 20 mV which makes the multiplier 300%, per Figure 6-3. Multiply the two values; 30  $\mu$ s × 300% = 90  $\mu$ s. Later when the inverting input suddenly rises back to 10.05 V, the output will start decreasing after approximately 3  $\mu$ s. The output was V<sub>OH</sub>, so the recovery time is 2  $\mu$ s. The input difference is 10.05 V – 10 V = 50 mV, which makes the multiplier 150%, per Figure 6-3. Multiply the two values; 2  $\mu$ s × 150% = 3  $\mu$ s.

#### 6.4 Slew Rate

Slew rate (SR) limits the output rise and fall times, which are defined as  $(V_{OH} - V_{OL})/SR$ . Slew rate, as specified in the op amp data sheet, is applicable for large differential input voltages. Dedicated comparator parts, on the other hand, may have much smaller differential input voltages. Note that the slew rate is reduced when the input difference voltage is small. Figure 6-3 shows that an input difference of 100 mV provides a slew rate 90% as fast as the data sheet setup result and a 10-mV input difference voltage has a slew rate that is only 16% of the data sheet slew rate.

Figure 6-4. Slew Rate Factor vs Input Differential Voltage (VID)

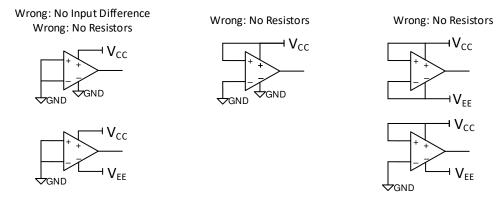

## 7 Unused Amp Connections and Inputs Connected Directly to Ground 7.1 Do Not Connect Inputs Directly to Ground

For both used and unused amplifiers, the inputs must not be connected directly to ground or any other low impedance node. Always add some resistance to limit the current to less than 10 mA, regardless of any possible fault condition. All the input pins have a diode from the input to the device's GND, or V–, pin. In dual supply applications, the GND pin will be negative. However, during power up, power down, or supply faults, the GND pin may become positive. If this occurs then a grounded input pin will have potentially damaging current flow due to the input diode. Even if the GND pin is also grounded, such as in single supply applications, there is a possibility that the input ground will be negative relative to the op amp's internal ground node. Ground differences occur when there is poor layout or high current transients,  $\Delta i/\Delta t$ . Adding 1-k $\Omega$  to 10-k $\Omega$  series resistors to the input pin is acceptable in most applications.

## 7.2 Unused Amplifier Connections

Occasionally applications will not need all the amplifiers in a dual or quad package. The unused op amp should be connected in a way that is safe for the unused amplifier and doesn't affect the used amplifiers. The best connection method puts the op amp into the normal linear operation range and no inputs are connected directly to low impedance nodes. The output of the op amp is not a low impedance node. The output by itself cannot provide a harmful voltage and/or current to the input. Therefore, no series resistor is needed between the input and output pins. Figure 7-1 shows preferred connections for unused amplifiers.

Figure 7-1. Best Connections Practices for Single and Dual Supplies

Alternatively, the device may be connected in certain, non-linear  $V_{OH}$  or  $V_{OL}$  configurations, as shown in Figure 7-2.  $V_{OL}$  is preferred over  $V_{OH}$  because that provides a small reduction in supply current,  $I_{CC}$ . LM358B and LM2904B have slightly lower  $I_{CC}$  in the  $V_{OH}$  configuration. A soft  $V_{OL}$  configuration is sometimes linear if  $V_{IO}$  is more positive than 1 mV, but it usually creates a non-linear  $V_{OL}$  state. Increasing the input resistor to 10 M $\Omega$  would ensure linear operation as the input bias current would raise the non-inverting input voltage beyond the input offset voltage range. " $V_{OL}$  Full  $V_{ID}$ " is better suited for lower voltage applications as there is no reason to apply a large input voltage difference even though the op amp allows it. The " $V_{OL}$  ( $I_{IB}$  Biased)" method uses the input bias current to raise the voltage on the inverting input. If used, place the 10-M $\Omega$  resistor close to the inverting input pin to reduce noise pickup. No inputs may be connected directly to low impedance nodes such as ground,  $V_{CC}$  or  $V_{EE}$ .  $V_{OH}$  alternatives are also acceptable; just swap the input pins. The "soft  $V_{OL}$ " connection cannot be input swapped.

Unused Amp Connections and Inputs Connected Directly to Ground

Figure 7-2. Acceptable Connection Practices for Single and Dual Supplies

The next set of connections in Figure 7-3 is not recommended, but these configurations are not considered harmful methods of terminating unused channels. The  $V_{OH}$  alternatives that swap the inputs are also not recommended methods of terminating unused channels.

Figure 7-3. Less Than Acceptable Connection Practices for Single and Dual Supplies

The last set of connections, seen in Figure 7-4, demonstrates improper setups that could cause output noise chatter or device damage if the GND pin were to ever become positive relative to the input pin.

Figure 7-4. Potentially Harmful Connection Practices for Single and Dual Supplies

## 8 Conclusion

The LM324, LM358 and their variants are among the most popular, cost effective and long-lived general purpose amplifiers. Using this app note to understand their pros, cons and how they differ from more modern op amps will increase the likelihood of a successful design. Although most analog designers will continue to use these devices, improvements in op amp design, process technology and our understanding of op amp applications over the past four decades have led to the development of better and easier to use op amps.

#### **9 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision A (August 2021) to Revision B (July 2023)   | Page |

|---|------------------------------------------------------------------|------|

| • | Application note globally revised to reflect LM324B and LM2902B. | 1    |

| С | hanges from Revision * (January 2019) to Revision A (August 2021)                             | Page |

|---|-----------------------------------------------------------------------------------------------|------|

| • | Updated the numbering format for tables, figures and cross-references throughout the document | 1    |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated