# Achieving the Optimal Thermal Performance for Chip Scale Package

Linhong Qin

### ABSTRACT

The Wafer Chip Scale Package (WCSP) is getting more popular in portable electronics due to its better electrical parameters, smaller size, and lower manufacturing cost. For example, for the same die size power conversion integrated circuit (IC), higher efficiency can be achieved in WCSP than the Quad Flat No-Leads (QFN) package. However, how to dissipate the power loss in a smaller area and keep the IC temperature cool becomes a big challenge, as this is critical for user experience in a power conversion IC. Printed-circuit board (PCB) layout plays a crucial role in achieving the best thermal performance. This application note details an experimental study of several versions of PCB layout and demonstrated techniques in PCB layout that can help improve WCSP thermal performance including power loss reduction, heat dissipation optimization, and other methods to keep temperature cool.

# Trademarks

All trademarks are the property of their respective owners.

# 1 Introduction

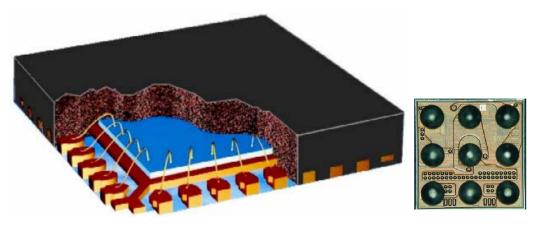

The silicon chip can be packaged with many options. QFN and WCSP are among the most popular options for the power converters. The QFN package fully encloses the silicon die in a plastic casing, making contacts to the circuit board through bond wires and lead frame, while the WCSP package makes direct interconnection from the silicon chip to the PCB through solder balls (shown in Figure 1). This reduces the footprint on the board to the minimum because the footprint is exactly the same size as the die. It also minimizes the parasitic resistance, inductance, and the weight by getting rid of extra bond wires, lead frame, and encapsulation. There is minimum electrical distance between the circuitry on the silicon and PCB. The interconnection is direct and through a very wide channel, namely solder ball array. By completely eliminating the wire bonds as well as any substrate related impedance, WCSP provides excellent electrical performance. It helps to achieve a total solution with better efficiency, less expense, smaller footprint size, lower height, and lighter weight.

Figure 1. Comparison of QFN (Left) and WCSP (Right) Package

#### Power Loss Reduction

These unique features make WCSP very attractive in portable devices, such as smart phones, navigation devices, tablets, and so forth. More and more ICs have adopted this package, including power conversion devices such as a charger. Although the efficiency is higher due to lower resistance, the remaining challenge is how to achieve the best thermal performance. Due to the small size, the WCSP package has higher junction-to-ambient thermal resistance ( $R_{BJA}$ ). For the same IC, QFN  $R_{BJA}$  is about 32.6°C/W while WCSP can go as high as 55.8°C/W. Remaining cool during high power operation, like high current charging, becomes very challenging.

This application note presents the experimental study about how to achieve the best thermal performance by comparing several versions of PCB layout for a high current battery charger. The techniques to help not only reduce power loss, but also facilitate thermal dissipation have been demonstrated with experimental verification of improved WCSP thermal performance.

# 2 Power Loss Reduction

The most popular charger used in high power applications is a switching charger. There are three major components of power losses related to the battery charger IC: conduction loss, switching loss, and gate driver loss.

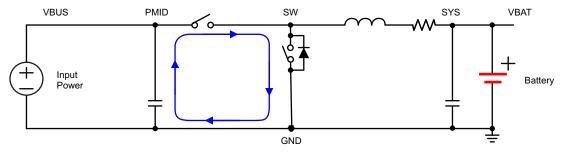

PCB layout plays a very important role in reducing the switching loss and conduction loss. The switching rising and falling time are one of the important factors of the switching loss. For a good layout, it is critical to place all key components in the proper place and to rout them properly so that high-frequency current path loop is minimized and does not have a big impact to the switching time as Figure 1 shows. The layout also helps the reduction of copper conduction loss on the trace. Another benefit of the minimized input current loop also alleviates the electrical and magnetic field radiation and high-frequency resonant problems.

Figure 2. High-Frequency Current Loop in a Switching Charger

When efficiency is in the 90% range, power loss is about 10%. Thus, a 1% addition to a higher efficiency will bring in about a 10% reduction on power loss, and hence a big percentage reduction on temperature increase as a large portion of the lost power is converted into heat.

Due to the smaller size of WCSP, component placement becomes even more critical. For applications with constrained area, there would be not enough space to place all key components in ideal locations. IC pins are crowded into a square or rectangle array and it is difficult to make traces out. Priorities must be taken.

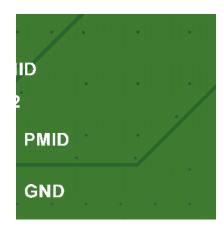

First, decoupling capacitors should be put as close as possible to the converter input (for example, PMID in Figure 2) and output (for example, SYS in Figure 2) pins, traces should be the widest and the shortest. The area enclosed by the high-frequency current loop (be sure to include GND return path) should be kept to a minimum. All duplicate WCSP balls for each power pin should be used and connected. Maximum copper pours should be applied to high-current traces. This will not only reduce the voltage drop on the copper trace, thus generate less heat, but also help dissipate heat from the IC.

Next, inductors and other capacitors should be placed as close as possible to the corresponding IC pins. Place all decoupling capacitors close to their respective IC pins and as close as possible to GND.

Finally, the layout must manage GND appropriately. A dedicated GND plane is highly recommended. Make GND readily accessible to all return paths. Remaining portions of the PCB should be covered by GND with copper pour since copper is a good thermal conductor.

#### www.ti.com

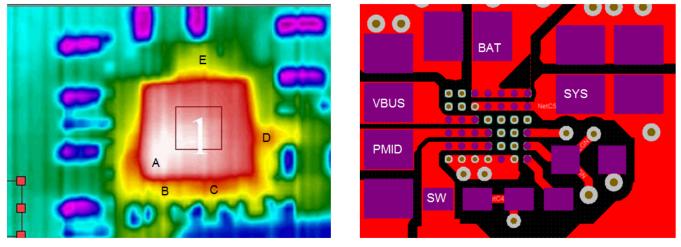

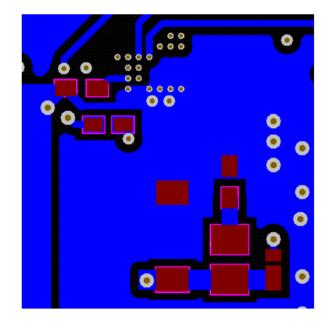

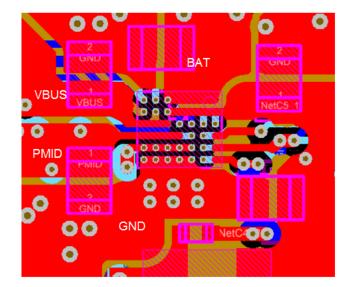

Figure 3 and Figure 4 are example layouts (Design #1), using the bq25898 IC (schematic simplified in Figure 2). All critical components (for example, capacitors of PMID, SYS, VBUS, and BAT) were put close to the die to reduce high-frequency current loop area. Maximum copper pours were used for all power lines. The entire PCB was almost covered by copper. On the right side are the top and bottom layout, on the left are thermal images of the PCB.

Figure 3. Top Layer Layout and Thermal Image of Design #1

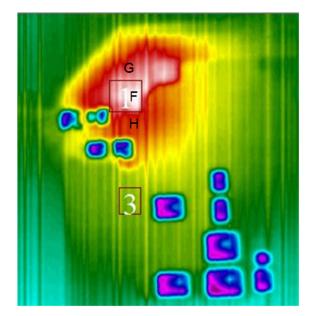

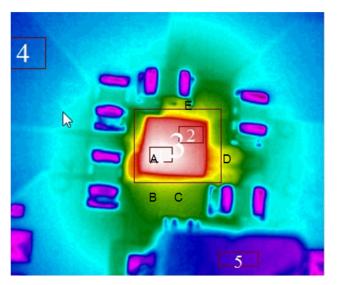

Figure 4. Bottom Layer Layout and Thermal Image Of Design #1

The thermal images were taken when the charger was operated with a 9-V adapter, 3.9-V battery, and 3-A charging current. There are some interesting points as labeled with alphabetic letters in Figure 3 and Figure 4:

- The lower left hand corner area, **A**, is where PMID, SW, and PGND are located. IR and switching losses are concentrated in this corner of the die. It easily becomes the hottest spot of the die.

- **B** and **C** are the PGND copper pour. Ideally this copper should be as big as possible. However, this PGND is trapped inside the SW-SYS-PGND loop. Bigger PGND pour will make the loop area bigger, thus more loss in power.

- C shares the same Cu pour as B, but C has no vias and is running a lot hotter than B. This shows the importance of Vias!

#### Further Improvement With Layout

- Area **D** heat is carried out by short traces, but goes no further, thus it also gets hot.

- Area E is the high current BAT pin. Current flows out of the chip into battery from here. Unlike other power pins PMID or SYS, the BAT pin is at the edge. To take advantage of the multiple solder balls of this pin, copper trace is placed perpendicular to the ball line so that current is flowing at maximum from all balls. The triangle cut in the copper pour is intended to guide the current flow so that it is not overcrowded at the corner ball. However, it seems to block heat dissipation.

- Area F is the hottest area of the back side as multiple vias are concentrated here. Vias help transfer heat from the top to the bottom layer, but they do not seem to dissipate well after that. This is more obvious at G, where no copper is present.

- The copper vacancy in area G traps heat!

- Area H has similar via numbers but a much larger copper pour connected, thus it is cooler than F.

As seen in this analysis, even though there are a lot of considerations in this layout, further optimization is still needed.

#### **Further Improvement With Layout** 3

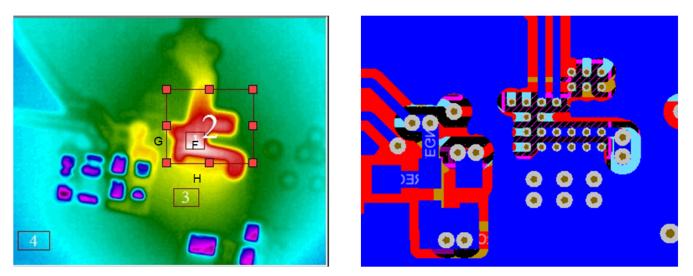

Knowing more optimization is needed, a new layout was implemented to optimize heat dissipation (Design #2). One major change was making the IC PGND a bigger copper pour. This further shortens the return path for PMID cap. Vias now connect SW to the inductor. Observe how the thermal picture changes in Figure 5 and Figure 6.

- As expected, the lower left hand corner, A, is still the hottest part of the die. However, the heat is spread across to the remaining die, rather than being contained within a smaller area.

- B and C are now one big PGND copper pour that serves like a heat sink and makes this edge of IC the coolest.

- C no longer shows any difference from B.

- D does not improve as some signal must be run out.

- With the triangle cut removed, E is sinking heat at full scale.

- **F** remains the hottest on the back side because of heat carried from the top layer by vias and PCB. The hot area has reduced dramatically due to the re-route of several lines.

- **G** is much cooler, due to the large GND copper pour connection.

- **H** is also much cooler, a big GND helps spread out the heat.

With this optimized PCB layout, temperature increase is reduced by 1°C to 3°C, depending on the test environment.

Figure 5. Top Layer Layout and Thermal Image of Design #2

Copyright © 2017, Texas Instruments Incorporated

www.ti.com

Figure 6. Bottom Layer Layout and Thermal Image of Design #2

# 4 Other Considerations

This design uses 1-oz copper. The results of this report show that thicker copper serves as a better heat sink and further improves thermal performance. However, using thicker copper is usually constrained by WCSP ball and pad size, and pitch. TI recommends checking with the PCB manufacturer before increasing the copper thickness.

Dielectric layer thickness is also intentionally reduced in this design. Our study shows thicker dielectric layer makes heat dissipation worse.

Table 1 shows an example of layer stack. Top and bottom layers are used for critical high-current traces.

The second layer is a GND plane. The third layer is for other signals.

| Layer Name     | Туре                 | Material         | Thickness (mil) | Dielectric Material | Dielectric<br>Constant |

|----------------|----------------------|------------------|-----------------|---------------------|------------------------|

| Top overlay    | Overlay              |                  |                 |                     |                        |

| Top solder     | Solder mask/coverlay | Surface material | 0.4             | Solder resist       | 3.5                    |

| Top layer      | Signal               | Copper           | 1.4             |                     |                        |

| Dielectric1    | Dielectric           | Core             | 6.6             | FR-4 High TG        | 4.2                    |

| Signal layer 1 | Signal               | Copper           | 1.4             |                     |                        |

| Dielectric2    | Dielectric           | Prepreg          | 6.6             | FR-4 High TG        | 4.2                    |

| Signal layer 2 | Signal               | Copper           | 1.4             |                     |                        |

| Dielectric3    | Dielectric           | Core             | 6.6             | FR-4 High TG        | 4.2                    |

| Bottom layer   | Signal               | Copper           | 1.4             |                     |                        |

| Bottom solder  | Solder mask/coverlay | Surface material | 0.4             | Solder resist       | 3.5                    |

| Bottom overlay | Overlay              |                  |                 |                     |                        |

### Table 1. Example Layer Stack Structure

Stitching vias are often overlooked but important. In a charger, high current traces may run on two layers to reduce the trace resistance. This is the perfect place to apply stitching vias. It not only helps to reduce connection resistance electrically, but also helps with thermal dissipation. From our experiment, it also significantly reduces electromagnetic interference (EMI). Figure 7 shows an example of stitching vias on PMID and GND copper pours.

www.ti.com

Summary

Figure 7. Stitching Vias on PMID and GND Copper Pours Example

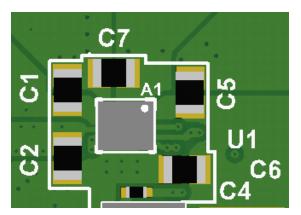

Using proper soldering techniques when soldering the WCSP IC onto the PCB ensures good electrical and thermal contact between the IC and PCB. A guide box (white square box in Figure 8) is usual helpful for manual soldering.

Figure 8. Die-Size Guide Box With Pin 1 Position Example

# 5 Summary

This application note studied and experimented with several versions of PCB layout for a high-current battery charger. The demonstrated techniques can help reduce power loss and facilitate thermal dissipation. With an optimized PCB layout, temperature increase can be reduced by 1°C to 3°C, depending on the test environment. If used together with system-level optimization (such as heat sink, heat block, and better air flow, and so forth), the results can be even better.

# 6 References

- 1. Sreenivasan Koduri et al. Proceedings of the 17th International Symposium on Power Semiconductor Devices and IC's (2005), Santa Barbara, CA.

- 2. Frank Mortan and Lance Wright, Quad Flatpack No-Lead Logic Packages (SCBA017)

- 3. bq25898, bq25898D I<sup>2</sup>C Controlled Single Cell 4-A Fast Charger with MaxCharge™Technology for High Input Voltage and Adjustable Voltage USB On-the-Go Boost Mode (SLUSCI7)

- 4. bq2426x 3-A, 30-V, Host-Controlled Single-Input, Single-Cell Switched-Mode Li-Ion Battery Charger With Power-Path Management and USB-OTG Support (SLUSBU4)

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated