# Application Note **Stability Analysis and Design of Internally-Compensated Peak Current Mode TPS62933 - Part II: How to Select the Feedforward Capacitor**

# **TEXAS INSTRUMENTS**

Andrew Xiong, Zhao Ma, Qi Yang, Chris Peng

#### ABSTRACT

This application note is part two of a two-part series: *Stability Analysis and Design of Internally Compensated Peak Current Mode TPS62933.* In *Part I: How to Select the Output Capacitor*, the output capacitor selection method is proposed to ensure the stability of the TPS62933, an internally-compensated, peak current-mode, buck converter. On this basis, the method to select a feedforward capacitor (C<sub>ff</sub>) is further introduced in this application note. First, the necessity to add C<sub>ff</sub> for high output voltage applications is introduced. Next, the impacts of C<sub>ff</sub> on converter phase margin improvement is analyzed. Combined with the loop feature of TPS62933, a method for stability enhancement with C<sub>ff</sub> is then proposed. Compared with conventional C<sub>ff</sub> selection method, the bode plot without C<sub>ff</sub> is not needed for the design, which makes it more applicable for the overall system design. Finally, an application design example is given to verify the effectiveness of the proposed method.

### **Table of Contents**

| 1 Introduction                                                                     | 2 |

|------------------------------------------------------------------------------------|---|

| 2 C <sub>ff</sub> in High-Output Voltage Internally Compensated PCM Buck Converter | 2 |

| B Effects of C <sub>ff</sub> on the Loop                                           |   |

| 4 Method for Selecting C <sub>ff</sub>                                             |   |

| 5 Experimental Verification for TPS62933                                           |   |

| 5 Summary                                                                          | 8 |

| 7 References                                                                       |   |

| A Validation Results for the Proposed Method                                       | 9 |

### **List of Figures**

| Figure 2-1. Bode Plot of PCM Buck Converter Open Loop Response                                                                                          | 2              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 2-2. Loop Gain of TPS62933 With Fixed Load Resistance R <sub>O</sub> (a) Low V <sub>O</sub> With –20 dB/dec Crossing (b) High V <sub>o</sub>     |                |

| With –40 dB/dec Crossing                                                                                                                                | 3              |

| Figure 2-3. Loop Gain of TPS62933 With Constant Output Current I <sub>out</sub> (a) Low V <sub>o</sub> With –20 dB/dec Crossing (b) High V <sub>o</sub> |                |

| With –40 dB/dec Crossing                                                                                                                                | 3              |

| Figure 3-1. Scheme of Feedback Divider Including Feedforward Capacitor                                                                                  | 4              |

| Figure 3-2. Bode Plot of Feedback Divider Transfer Function Including Cff                                                                               | 4              |

| Figure 4-1. Correct Method to use Cff by Only Adding Cff Zero Inside Bandwidth                                                                          | 5              |

| Figure 4-2. Correct Method to use C <sub>ff</sub> by Adding Both the C <sub>ff</sub> Zero and Pole Inside Bandwidth                                     | 5              |

| Figure 4-3. Incorrect Method to use C <sub>ff</sub> by Adding Both the C <sub>ff</sub> Zero and Pole Inside Bandwidth                                   | 6              |

| Figure 5-1. Bode Plot With the Selected Feedforward Capacitor                                                                                           | <mark>8</mark> |

| -                                                                                                                                                       |                |

### List of Tables

### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

Peak current mode (PCM) control is widely used in buck converters due to the advantages such as good dynamic performance and easy compensation. By using internal compensation with PCM control, the TPS62933 device further reduces the customer-application BOM, which helps to reduce the solution size and design complexity. For common applications, components are selected based on the recommended table and design applications are quickly implemented<sup>(1)</sup>. Methods for choosing output capacitors in applications with *large* output capacitors are detailed in *Stability Analysis and Design of Internally-Compensated Peak Current Mode TPS62933 - Part I: How to Select the Output Capacitor*.

However, from the results derived in *Part I: How to Select the Output Capacitor*, the maximum output capacitance value under the stability constraint is inversely proportional to the output voltage, which makes it difficult to select a large capacitance in high output voltage applications. This difficulty leads to the contradiction between voltage ripple, voltage noise, and a stable design. This document first explains the root cause of the contradiction based on theoretical analysis. Then the effects of feedforward capacitor C<sub>ff</sub> on the loop are introduced. With a pair of introduced zero and pole in the loop, the phase margin can be improved for stability, which enlarges the range of output capacitance selection in high output voltage applications.

## 2 C<sub>ff</sub> in High-Output Voltage Internally Compensated PCM Buck Converter

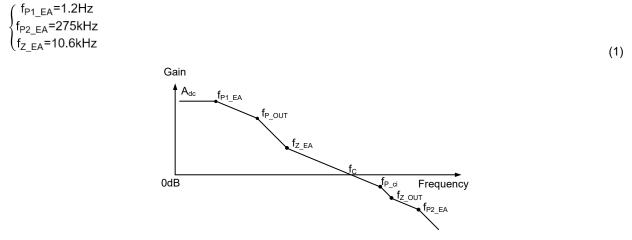

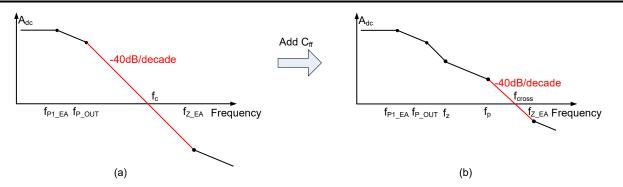

*Loop Response Considerations in Peak Current Mode Buck Converter Design* introduces the loop response model of PCM mode buck converters, as shown in Figure 2-1. The initial loop gain slope of the PCM converter is 0, it changes from 0 to -20 dB/dec at the initial pole frequency  $f_{P1\_EA}$ . At pole  $f_{P\_OUT}$ , the loop gain slope changes to -40 dB/dec. With the compensation of zero  $f_{Z\_EA}$ , the gain slope becomes -20 dB/dec, and the gain curve crosses 0 dB with a -20-dB/dec slope. That slope can normally bring sufficient phase margin for the converter.

The TPS62933 has internal compensation, the  $f_{P1\_EA}$ ,  $f_{Z\_EA}$ , and  $f_{P2\_EA}$  are the frequencies of poles and zero generated by the internal compensation and fixed as Equation 1:

The DC gain  $A_{dc}$  is related with output current. The  $A_{dc}$  of TPS62933 can be expressed as:

$$A_{dc} = \frac{352000}{I_{out}}$$

(2)

$f_{P_{OUT}}$  is the frequency of the pole formed with the output capacitance and loading, which can be expressed as:

$$f_{P_{OUT}} = \frac{1}{2\pi(R_{ESR} + R_0)C_0}$$

(3)

The expressions of A<sub>dc</sub> and f<sub>P OUT</sub> include the output current I<sub>out</sub> and the load resistance R<sub>O</sub>, respectively.

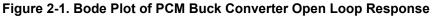

For the application with a fixed load resistance  $R_O$ , when output voltage increases, output current increases and the DC gain  $A_{dc}$  decreases. As Figure 2-2 illustrates, this causes the bandwidth decrease. If the zero  $f_{Z\_EA}$  becomes out of bandwidth, the –40 dB/decade gain slope occurs at gain crossover frequency and could cause insufficient phase margin.

# Figure 2-2. Loop Gain of TPS62933 With Fixed Load Resistance $R_0$ (a) Low $V_0$ With –20 dB/dec Crossing (b) High $V_0$ With –40 dB/dec Crossing

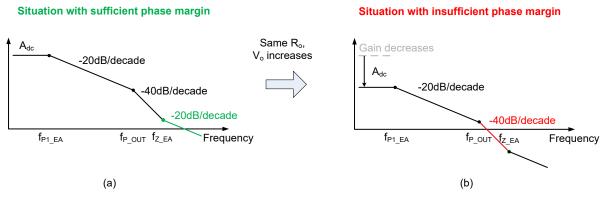

For converters with fixed output current  $I_{out}$ , the equivalent output resistance  $R_O$  increases with increasing output voltage, which makes the frequency  $f_{P_OUT}$  in Equation 3 decrease. As Figure 2-3 shows, that results in bandwidth decrease and could also cause the compensated zero  $f_{Z_EA}$  to become out of bandwidth. The -40 dB/decade gain slope also occurs at gain crossover frequency and could cause insufficient phase margin.

# Figure 2-3. Loop Gain of TPS62933 With Constant Output Current I<sub>out</sub> (a) Low V<sub>o</sub> With –20 dB/dec Crossing (b) High V<sub>o</sub> With –40 dB/dec Crossing

Above all, increasing output voltage tends to cause the internal peak-current-mode converter to be unstable, which makes it hard to design an application with high output voltage.

Since the pole frequency  $f_{P_OUT}$  is inversely proportional to the output capacitance  $C_o$ , reducing  $C_o$  can help to increase the frequency  $f_{P_OUT}$ , making the zero  $f_{Z_EA}$  inside bandwidth again and bringing enough phase margin. Just as the derived output capacitance range with Equation 4 in *Part I*, the maximum output capacitance is reduced by increasing the output voltage  $V_O$  for stability. But reducing output capacitance has many side effects, such as poor transient performance, larger ripple, and larger noise.

$$C_{o} < \frac{5.98 \times 10^{-4}}{I_{out}R_{ESR} + V_{O}}$$

(4)

This analysis proves that in high-voltage applications, there is a contradiction between performance and stability in an internally-compensated PCM buck converter. Adding a feedforward capacitor  $C_{\rm ff}$  can help solve the issue at this condition.

# 3 Effects of C<sub>ff</sub> on the Loop

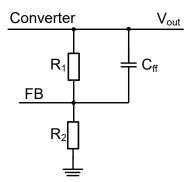

The Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor application report details the effects of adding a feedforward capacitor in the feedback divider. Figure 3-1 shows feedback divider including C<sub>ff</sub>.

Figure 3-1. Scheme of Feedback Divider Including Feedforward Capacitor

C<sub>ff</sub> introduces a pair of zero and pole in the converter loop. The frequency of the introduced zero and pole are:

$$f_{z} = \frac{1}{2\pi R_{1}C_{ff}}$$

(5)

$$f_{p} = \frac{1}{2\pi C_{ff}} \left(\frac{1}{R_{1}} + \frac{1}{R_{2}}\right)$$

(6)

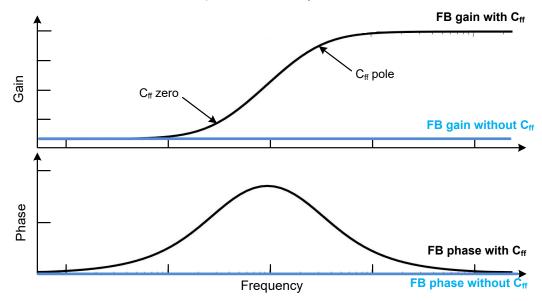

#### Figure 3-2 shows the effects of the zero and pole introduced by Cff.

Figure 3-2. Bode Plot of Feedback Divider Transfer Function Including C<sub>ff</sub>

C<sub>ff</sub> has both effects on the loop gain and phase. The loop gain is increased to enlarge bandwidth which benefits transient response, and the phase is also boosted to increase the phase margin for system stability.

In application notes such as *Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor*, some methods have been proposed to use  $C_{\rm ff}$  for phase margin enhancement. But in those methods, the bode plot results without  $C_{\rm ff}$  are always needed to get the recommended  $C_{\rm ff}$  value. The  $C_{\rm ff}$  selecting method is more applicable in the solution validation process but not in the application design process.

A new method to choose  $C_{\rm ff}$  is proposed in this application report. The bode plot results without  $C_{\rm ff}$  are not needed to get the recommended  $C_{\rm ff}$  value in this method, which makes it more applicable in TPS62933 application design.

# 4 Method for Selecting C<sub>ff</sub>

This method is implemented by letting the loop gain cross 0 dB with -20 dB/dec slope. To be noted, -20 dB/dec gain at 0 dB is not a necessary condition for stability. So this method just provides an allowable range for C<sub>ff</sub> and it does not mean the converter will be unstable if C<sub>ff</sub> exceeds this range.

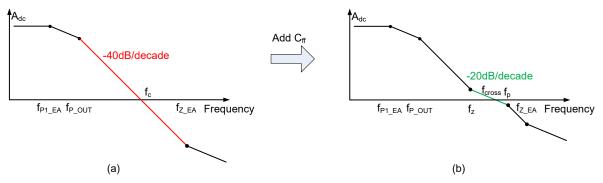

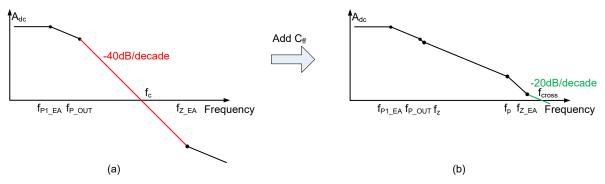

For the case as Figure 4-1(a) shows, when the EA zero frequency  $f_{Z\_EA}$  is larger than bandwidth, the C<sub>ff</sub> zero  $f_z$  can be added inside bandwidth, then the loop gain *can* cross 0 dB with -20 dB/dec, as Figure 4-1(b) shows.

Figure 4-1. Correct Method to use C<sub>ff</sub> by Only Adding C<sub>ff</sub> Zero Inside Bandwidth

As the case in Figure 4-2 shows, the zero and pole introduced by  $C_{ff}$  are both added inside bandwidth and the system stability can still be ensured. Although the slope of loop gain becomes –40 dB/dec again after the pole  $f_p$ , the increase in loop gain with  $C_{ff}$  makes the bandwidth increase and the  $f_{Z_{EA}}$  becomes smaller than the bandwidth. A –20-dB/dec crossing is achieved and the system has enough phase margin.

Figure 4-2. Correct Method to use C<sub>ff</sub> by Adding Both the C<sub>ff</sub> Zero and Pole Inside Bandwidth

As the case in Figure 4-3 shows, both the zero and pole introduced by  $C_{ff}$  are inside bandwidth, but the EA zero frequency  $f_{Z\_EA}$  is still larger than the bandwidth. At this condition, the loop gain will still cross 0 dB with -40 dB/dec, which cannot ensure the system phase margin.

Figure 4-3. Incorrect Method to use  $C_{\rm ff}$  by Adding Both the  $C_{\rm ff}$  Zero and Pole Inside Bandwidth

Therefore, the two restrictions deduced to achieve a stable state with -20 dB/dec crossing after adding feedforward capacitor are (1)  $f_z < f_c$ , and (2) avoiding the condition as exhibited in Figure 4-3.  $f_c$  is the gain crossover frequency when not adding  $C_{\text{ff}}$ .

The expression of f<sub>c</sub> has already been derived in *Part I*, as shown in Equation 7.

$$f_{c} = f_{P_{OUT}} \sqrt{A_{P_{OUT}}} = \sqrt{A_{dc} f_{P_{OUT}} f_{P1_{EA}}}$$

(7)

With the restriction  $f_z < f_c$ , the low limit of  $C_{ff}$  is obtained based on Equation 5 and Equation 7:

$$C_{\rm ff} > \frac{\sqrt{C_{\rm O}(V_{\rm O} + I_{\rm out}R_{\rm ESR})}}{1629R_1}$$

(8)

This equation corresponds to the limit for restriction 1. Since Equation 9 corresponds to the condition as Figure 4-3(b), restriction 2 to avoid that condition corresponds to Equation 10.

$$20lg(A_p)>0dB$$

and  $f_{Z_EA}>f_{cross}$  (9)

$$20lg(A_p) \le 0dB$$

or  $f_{Z_EA} \le f_{cross}$  (10)

where  $A_{p}$  is the amplitude of gain at  $f_{p}. \label{eq:constraint}$

To get the expressions of  $A_p$  and  $f_{cross}$ , first determine the relation between gain and frequency as Equation 11, Equation 12, and Equation 13.

$$\frac{20 \lg(A_{P_OUT}) - 20 \lg(A_z)}{\lg(f_{P_OUT}) - \lg(f_z)} = -40 dB/decade$$

(11)

$$\frac{20 \lg(A_z) - 20 \lg(A_p)}{\lg(f_z)} = -20 dB/decade$$

$$(12)$$

$$\frac{20 \lg(A_p) - 0}{\lg(f_p) - \lg(f_{cross})} = -40 dB/decade$$

(13)

Next, the expressions of A<sub>p</sub> and f<sub>cross</sub> as Equation 14 and Equation 15 are determined.

$$A_{p} = \frac{A_{P}_{OUT} f_{P}_{OUT}^{2}}{f_{z} f_{p}}$$

(14)

$$f_{cross} = f_p \sqrt{A_p}$$

(15)

Substituting expressions for  $A_{P_OUT}$ ,  $f_{P_OUT}$ ,  $f_z$ , and  $f_p$  into Equation 14 and Equation 15, then Equation 16 is calculated as the equation for restriction 2 based on Equation 10, Equation 14, and Equation 15.

$$C_{\rm ff} \leq \sqrt{\frac{C_{\rm O}(R_1 + R_2)(V_{\rm O} + I_{\rm out}R_{\rm ESR})}{844800\pi R_1^2 R_2}} \quad \text{or} \quad C_{\rm O} \leq \frac{R_1 + R_2}{1670(V_{\rm O} + I_{\rm out}R_{\rm ESR})R_2}$$

(16)

Combining Equation 8 for restriction 1 and Equation 16 for restriction 2, Equation 17 and Equation 18 are the limits for  $C_{\rm ff}$ .

$$C_{\rm ff} > \frac{\sqrt{C_{\rm O}(V_{\rm O} + I_{\rm out}R_{\rm ESR})}}{1629R_1} , \quad \text{if } C_{\rm O} \le \frac{R_1 + R_2}{1670(V_{\rm O} + I_{\rm out}R_{\rm ESR})R_2}$$

(17)

$$\frac{\sqrt{C_{\rm O}(V_{\rm O}+I_{\rm out}R_{\rm ESR})}}{1629R_{\rm 1}} < C_{\rm ff} \le \sqrt{\frac{C_{\rm O}(R_{\rm 1}+R_{\rm 2})(V_{\rm O}+I_{\rm out}R_{\rm ESR})}{844800\pi R_{\rm 1}^{2}R_{\rm 2}}} , \text{ if } C_{\rm O} > \frac{R_{\rm 1}+R_{\rm 2}}{1670(V_{\rm O}+I_{\rm out}R_{\rm ESR})R_{\rm 2}}$$

$$(18)$$

### **5 Experimental Verification for TPS62933**

Using the typical application as an example,  $V_{in}$  = 24 V,  $V_{out}$  = 5 V,  $I_{out}$  = 3 A,  $f_{sw}$  = 500 kHz, L = 6.8 µH. For the voltage divider resistance,  $R_1$  = 52.5 k $\Omega$  and  $R_2$  = 10 k $\Omega$ .

With the method demonstrated in *Part I*, the calculated output capacitance upper limit is 106  $\mu$ F without feedforward capacitor. Here 20 × C3216X5R1V226M160AC capacitors are selected for lower voltage ripple and better transient performance, which equals to about 264- $\mu$ F C<sub>o</sub> effective value, which is much higher than the 106  $\mu$ F upper limit without C<sub>ff</sub>.

This example has been validated on the TPS62933EVM. C3216X5R1V226M160AC (22  $\mu$ F) and CGA5L1X7R1H106K160AC (10  $\mu$ F) are selected as C<sub>o</sub>, the effective value of C3216X5R1V226M160AC is about 13.2  $\mu$ F when biased at 5 V, the effective value of CGA5L1X7R1H106K160AC is about 9.4  $\mu$ F.

Since 20 × parallel capacitors are used, the ESR of output capacitors can be ignored. With Equation 17 and Equation 18, the range of  $C_{\rm ff}$  as  $C_{\rm ff}$  > 425 pF, is calculated. So, 470 pF  $C_{\rm ff}$  is selected for the application.

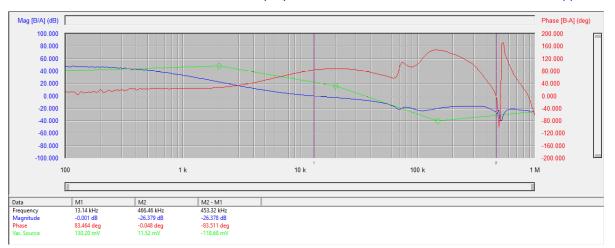

Figure 5-1 shows the bode plot test results with added 470 pF  $C_{\rm ff}$ . The phase margin is boosted to 83.464 degrees, which validates the effectiveness of the proposed method. See more validation results in Appendix A.

Figure 5-1. Bode Plot With the Selected Feedforward Capacitor

### 6 Summary

A selection method for feedforward capacitors is proposed in this application note for TPS62933, based on loop stability analysis. First, the necessity of adding  $C_{\rm ff}$  in an application with high output voltage is analyzed. Then the impacts of the  $C_{\rm ff}$  on the converter loop is introduced and a method to choose  $C_{\rm ff}$  for stability is proposed by ensuring –20 dB/dec gain slope at gain crossover frequency. Compared with previous methods, the bode plot test results without  $C_{\rm ff}$  are not needed to get recommended  $C_{\rm ff}$  value, which makes the method more applicable in application design. The proposed methods expressed in this application note are verified by experiment.

### 7 References

- 1. Texas Instruments, *TPS62933 3.8-V to 30-V, 3-A Synchronous Buck Converter in SOT583 Package* Data Sheet

- 2. Texas Instruments, *Loop Response Considerations in Peak Current Mode Buck Converter Design* Application Report

- 3. Texas Instruments, *Optimizing Transient Response of Internally Compensated dc-dc Converters With Feedforward Capacitor* Application Report.

# A Validation Results for the Proposed Method

Table A-1 details the validation of feedforward capacitance.

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | f <sub>SW</sub> (kHz) | L <sub>choose</sub> (µH) | High Limit<br>C <sub>O</sub> (μF)<br>Without Cff | C <sub>choose</sub> (μF)                         | C <sub>ff</sub> limit    | C <sub>ff</sub> choose (pF) | PM <sub>bench</sub> (deg) |  |  |  |  |

|---------------------|----------------------|-----------------------|--------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------|-----------------------------|---------------------------|--|--|--|--|

| 24                  | 5                    | 500                   | 6.8                      | 106                                              | 20 × 22 μF<br>(C <sub>effective</sub> : 264 μF)  | C <sub>ff</sub> > 425 pF | 470 pF                      | 83.464                    |  |  |  |  |

| 24                  | 5                    | 1200                  | 3.3                      | 119.6                                            | 20 × 22 μF<br>(C <sub>effective</sub> : 264 μF)  | C <sub>ff</sub> > 425 pF | 470 pF                      | 86.143                    |  |  |  |  |

| 24                  | 12                   | 500                   | 12                       | 40.7                                             | 20 × 22 μF<br>(C <sub>effective</sub> : 98.5 μF) | C <sub>ff</sub> > 402 pF | 470 pF                      | 102.6                     |  |  |  |  |

### Table A-1. Validation Results

For 5 V V<sub>out</sub>, R<sub>upper</sub> (R<sub>1</sub>) is 52.5 k $\Omega$  and R<sub>lower</sub> (R<sub>2</sub>) is 10 k $\Omega$ .

For 12 V V<sub>out</sub>, R<sub>upper</sub> (R<sub>1</sub>) is 52.5 k $\Omega$  and R<sub>lower</sub> (R<sub>2</sub>) is 3.75 k $\Omega$ .

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated