DV2003S1

# **Fast Charge Development System**

#### **Features**

- bq2003 fast-charge control evaluation and development

- Charge current sourced from an on-board switch-mode regulator (up to 3.0 A)

- ► Fast charge of 2 to 16 NiCd or NiMH cells

- Fast-charge termination by delta temperature/delta time (ΔT/Δt), negative delta voltage (-ΔV), maximum temperature, maximum time, and maximum voltage

- $\blacktriangleright$   $\Delta V$  enable, hold-off, top-off, maximum time, and number of cells are jumper-configurable

- Charging status displayed on charge and temperature LEDs

- Discharge-before-charge control with push-button switch

- ▶ Inhibit fast charge by external logic-level input

### **General Description**

The DV2003S1 Development System provides a development environment for the bq2003 Fast-Charge IC. The DV2003S1 incorporates a bq2003 and a buck-type switch-mode regulator to provide fast charge control for 2 to 16 NiCd or NiMH cells.

Review the bq2003 data sheet and the application note, "Using the bq2003 to Control Fast Charge," before using the DV2003S1 board.

The fast charge is terminated by any of the following:  $\Delta T/\Delta t$ ,  $-\Delta V$ , maximum temperature, maximum time, maximum voltage, or an external inhibit command. Jumper settings select the  $-\Delta V$  enabled state, and the hold-off, top-off, and maximum time limits.

The user provides a power supply and batteries. The user configures the DV2003S1 for the number of cells,  $-\Delta V$  charge termination and maximum charge time (with or without top-off), and commands the discharge-before-charge option with the push-button switch S1.

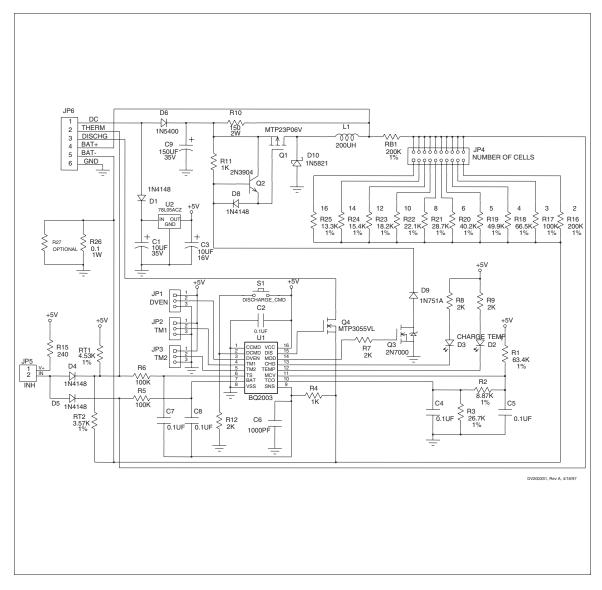

#### Control of On-Board P-FET Switch-Mode Regulator

### **Connection Descriptions**

#### J6

|     | DC+   | DC input from charger supply                              |  |  |

|-----|-------|-----------------------------------------------------------|--|--|

|     | THERM | Thermistor connection                                     |  |  |

|     | DSCHG | Low side of discharge load                                |  |  |

|     | BAT+  | Positive battery terminal and high side of discharge load |  |  |

|     | BAT-  | Negative battery terminal and thermistor connection       |  |  |

|     | GND   | Ground from charger supply                                |  |  |

| J2  |       |                                                           |  |  |

|     | +V    | Voltage source for inhibit input                          |  |  |

|     | IN    | Inhibit input to prevent bq2003 activity                  |  |  |

| JP1 | DVEN  | Negative voltage termination enable                       |  |  |

| JP2 | TM1   | TM1 setting                                               |  |  |

| JP3 | TM2   | TM2 setting                                               |  |  |

| JP4 | NOC   | Select number of cells                                    |  |  |

Rev. A Board

3/98

#### **Fixed Configuration**

The DV2003S1 board has the following fixed characteristics :

$V_{CC} \ (4.75 - 5.25V)$  is regulated on-board from the supply at connector JP6 DC+.

LEDs indicate charge status and temperature fault status.

Pin CCMD is grounded, providing charge initiation on the later application of the battery or DC+, which provides  $V_{CC}$  to the bq2003.

Pin DCMD is pulled to ground through R12. A toggle of switch S1 momentarily pulls DCMD high and initiates a discharge-before-charge. The bq2003 output activates FET Q4, allowing current to flow through an external current-limiting load between BAT+ and DSCHG on connector JP6.

Trickle current is limited by a  $150\Omega/2W$  resistor R10 between DC+ and BAT+ (maximum potential across R10 = 17.3V). Note that too large a voltage between DC+ and BAT+ may exceed the wattage rating of resistor R10.

As shipped from Benchmarq, the DV2003S1 buck-type switch-mode regulator is configured to a charging current of 2.35A. This current level is controlled by the value of sense resistor R26 by the relationship:

$$I_{CHG} = \frac{0.235V}{R26}$$

The value of R26 at shipment is  $0.100\Omega$ . This resistor can be changed depending on the application.

The suggested maximum ICHG for the DV2003S1 board is 3A. A location for a second sense resistor (R27) is provided on the DV2003S1 Board. R27 is electrically in parallel with R26, which assists in user modification of  $I_{CHG}$ , if needed.

Charge current can be halted at any time via external stimulus. Connector JP5 provides a +5V DC source (+V) and an inhibit input (IN) node for this function. To inhibit charge current, the JP5 inhibit in;put (IN) is driven by +5V DC. To reinitiate charge, remove the voltage source from the inhibit input.

The maximum cell voltage (MCV) setting is 1.8V.

Zener diode D( is used to limit Q1 VGS per a given DC+ voltage. Benchmarq ships a 1N751A (5.1V Zener) at location D9. This voltage value was selected as an appropriate value for most development work. The user can modify this Zener diode for the application. Refer to Table 1 for suggested D9 values for DC+ voltages.

| Table 1. Lookup Table for D9 Selection | Table 1. | Lookup | Table for | D9 | Selection |

|----------------------------------------|----------|--------|-----------|----|-----------|

|----------------------------------------|----------|--------|-----------|----|-----------|

| +VDC Input<br>(Volts) | Motorola<br>Part No. | Nominal Zener<br>Voltage |  |  |

|-----------------------|----------------------|--------------------------|--|--|

| Below 15              | Shorted              | 0                        |  |  |

| 15–18                 | 1N749                | 4.3                      |  |  |

| 18-21                 | 1N755                | 7.5                      |  |  |

| 21-24                 | 1N758                | 10                       |  |  |

| 24-27                 | 1N964A               | 13                       |  |  |

| 27-30                 | 1N966A               | 16                       |  |  |

| 30-32                 | 1N967A               | 18                       |  |  |

| 32-35                 | 1N968A               | 20                       |  |  |

With the provided NTC thermistor connected between THERM and BAT–, values are: LTF = 10°C, HTF = 45°C, and TCO = 50°C. The  $\Delta$ T/ $\Delta$ t settings at 30°C (T $\Delta$ T) are: minimum = 0.82°C/minute, typical = 1.10°C/minute.

The thermistor is identified by the serial number suffix as follows:

| Identifier | r Thermistor                   |  |  |

|------------|--------------------------------|--|--|

| K1         | Keystone RL0703-5744-103-S1    |  |  |

| (blank)    | Philips 2322-640-63103         |  |  |

| F1         | Fenwal Type 16, 197-103LA6-A01 |  |  |

#### Jumper-Selectable Configuration

The DV2003L1 must be configured as described below.

DVEN (JP1): Enables/disables -  $\Delta V$  termination (see bq2003 data sheet).

| Jumper Setting | Pin State      |  |  |

|----------------|----------------|--|--|

| [12]3          | Enabled (high) |  |  |

| 1 [ 2 3 ]      | Disabled (low) |  |  |

TM1 and TM2 (JP2 and JP3): Select fast charge safety time/hold-off/top-off (see bq2003 data sheet).

| Jumper Setting | Pin State |  |  |

|----------------|-----------|--|--|

| [12]3          | High      |  |  |

| 1 [ 2 3 ]      | Low       |  |  |

| 123            | Float     |  |  |

Number of Cells (JP4): A resistor-divider network is provided to select 2 to 16 cells (the resulting resistor value equals N - 1 cells). RB1 is a 200K $\Omega$  resistor, and RB2 (R16–R22) is jumper-selected.

| Closed Jumper | Number of Cells |  |  |

|---------------|-----------------|--|--|

| R22           | 14              |  |  |

| R21           | 12              |  |  |

| R20           | 10              |  |  |

| R19           | 8               |  |  |

| R18           | 6               |  |  |

| R17           | 5               |  |  |

| R16           | 4               |  |  |

Temperature Disable: Connecting a  $10K\Omega$  resistor between THERM and BAT– disables temperature control.

#### **Setup Procedure**

- 1. Configure DVEN, TM1, TM2, and number-of-cells (NOC) jumpers.

- 2. Connect the provided thermistor or a  $10 \text{K}\Omega$  resistor between THERM and BAT-.

**Note:** RT1 and RT2 match the thermistor provided and must be changed if a different thermistor type is used (see Appendix A in the application note, "Using the bq2003 to Control Fast Charge").

- 3. If using the discharge-before-charge option, connect a current-limiting discharge load between BAT+ and DSCHG.

- 4. If using the INHIBIT function, connect a switch across JP5 (IN to +V) or connect IN to the controlling signal source (3–5V).

- 5. Attach the battery pack to BAT+ and BAT-. For temperature control, the thermistor must contact the cwlls.

- 6. Attach DC current source to DC+ (+) and GND (-) connections in JP6.

#### **Recommended DC Operating Conditions**

| Symbol            | Description            | Minimum                                                                    | Typical | Maximum                         | Unit | Notes  |

|-------------------|------------------------|----------------------------------------------------------------------------|---------|---------------------------------|------|--------|

| $I_{DC+}$         | Maximum input current  | -                                                                          | -       | 2.4                             | Α    |        |

| V <sub>DC</sub>   | Maximum input voltage  | $\begin{array}{c} 2.0 + \mathrm{V_{BAT+}} \\ \mathrm{or} \ 15 \end{array}$ | -       | 18 + V <sub>BAT+</sub><br>or 35 | v    | Note 1 |

| V <sub>BAT+</sub> | BAT+ input voltage     | -                                                                          | -       | 30                              | V    |        |

| VTHERM            | THERM input signal     | 0                                                                          | -       | 5                               | V    |        |

| IDSCHG            | Discharge load current | -                                                                          | -       | 2                               | Α    |        |

Note: 1. The  $V_{DC+}$  limits consider the 5.1V Zener diode at D9. The voltage at D9 is application-specific and limits the  $V_{GS}$  of Q1 to a safe enhancement value during Q1 conduction. See Table 1 for recommended D9 selections per  $V_{DC+}$ .

## **DV2003L1 Board Schematic**

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated