# Application Note BQ78350-R1 TRM Addendum for the BQ78350-R3 Device

#### ABSTRACT

This document is an addendum to the *BQ78350-R1 Technical Reference Manual* and discusses modifications relating to the BQ78350-R3 device. Items not discussed in this addendum have not changed.

#### **Table of Contents**

| 1 General Description        | 2 |

|------------------------------|---|

| 2 Production Plans           | 2 |

| 3 Added Features             |   |

| 3.1 Cell Balancing at Rest   | 2 |

| 3.1.1 Cell Balancing DF Bits |   |

| 3.1.2 0xB1 CB_REST_Enable()  |   |

| 4 Revision History           |   |

1

# **1** General Description

The BQ78350-R3 device is a modified version of the catalog BQ78350-R1 device that has modified selected functionality, as well as new features. This document details the changes regarding the BQ78350-R3 device with respect to the BQ78350-R1 device.

## **2 Production Plans**

To use the BQ78350-R3 device, order the catalog BQ78350-R1 device from TI.com and program the device with the TI provided BQ78350-R3 firmware. The package and pinout remain the same as the BQ78350-R1 device, with the exception of some modified functionality associated with the GPIO\_B pin.

### **3 Added Features**

#### 3.1 Cell Balancing at Rest

A new feature is added to BQ78350-R3 to activate the cell balancing operation when the device is at REST. Writing to the 0xB1 *CB\_REST\_Enable()* command enables or disables this feature. The **Balancing Configuration[CB\_REST]** DF bits sets the default enable/disable configuration of this feature upon device POR. If this feature is enabled when **[CB]** = 1, and the voltage level of the lowest cell is above the voltage level programmed in the **Cell Balance Threshold** register, cell balancing operation will be activated when the device enters REST mode. In the same way as normal cell balancing during CHARGE mode, only the non-adjacent cells will be balanced at the same time during REST mode.

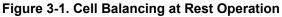

When cell balancing operation is activated in REST mode, the dynamic cell balance threhold will automatically be set to the voltage level which is *Cell Balance Min* above the lowest cell voltage, without *Cell Balance Window* adjustment, and continue to decrease as the cell voltages decrease over time due to leakag while remaining above the *Cell Balance Threshold* voltage level. This ensures the cell balancing operation continues to operate in REST if the maximum difference in cell voltages exceeds the value programmed in *Cell Balance Threshold* is significantly lower than the lowest cell voltage. Figure 3-1 shows how the cell balancing operates in REST mode when this feature is activated.

Cell balancing at REST will complete when the maximum difference in cell voltages is less than the value programmed in *Cell Balance Min*. Upon completion while the lowest cell voltage is still above the voltage level programmed in *Cell Balance Threshold*, if a fast leaking cell causes the maximum difference in cell voltages

to widen again beyond *Cell Balance Min*, the cell balancing at REST will re-activate. When the device exits REST mode or when any of the cell voltage falls below the programmed value of *Cell Balance Threshold*, cell balancing at REST will stop even before the balancing operation is completed.

#### 3.1.1 Cell Balancing DF Bits

The **[CB\_REST]** bit is added to the BQ78350-R3 in the following data flash location. Upon device POR, this bit is used to enable or disable the cell balance at rest/relax feature by default.

| Class    | Subclas   | ss Nam                  | Name |     | Size in Bytes | Min  | Мах  | Default | Unit |

|----------|-----------|-------------------------|------|-----|---------------|------|------|---------|------|

| Settings | Configura | tion Balanc<br>Configur | •    | Hex | 1             | 0x00 | 0xFF | 0x01    | Hex  |

| 7        | 6         | 5                       |      | 4   | 3             | 2    |      | 1       | 0    |

| RSVD     | RSVD      | RSVD                    | RSVD |     | RSVD          | RSVD | CB   | REST    | СВ   |

RSVD (Bits 7-2): Reserved. Do not use.

CB\_REST (Bit 1): Cell balancing operation at rest (without charge current detection) default configuration when cell balancing is enabled.

- 1 = Enabled

- 0 = Disabled (default)

CB (Bit 0): Cell balancing

- 1 = Enabled (default)

- 0 = Disabled in all cases

#### 3.1.2 0xB1 CB\_REST\_Enable()

This read/write command enables or disables the cell balancing operation in REST mode without modifying the value of **[CB\_REST]** DF bit.

When cell balancing is enabled by **[CB]** = 1, writing 0x1 to this command enables the cell balancing operation in REST mode, while writing 0x0 to this command disables the operation.

This command can also be used to read back the status of the cell balancing operation in REST mode. The command returns 0x1 to indicate the operation is enabled, and 0x0 to indicate the operation is disabled.

This command is not functional when cell balancing is disabled.

| - | SBS  | Name             | Access |     |     | Protocol | Type | Min    | Мах    | Default | Unit |

|---|------|------------------|--------|-----|-----|----------|------|--------|--------|---------|------|

|   | Cmd  |                  | SE     | US  | FA  | FIOLOCOI | Туре |        | WICA   | Delault | Onit |

|   | 0xB1 | CB_REST_Enable() | R/W    | R/W | R/W | Word     | Hex  | 0x0000 | 0x0001 | 0x0000  | -    |

3

### **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision * (February 2022) to Revision A (November 2022)                 | Page |

|---|--------------------------------------------------------------------------------------|------|

| • | Added Cell Balancing at Rest feature description                                     | 2    |

| • | Updated discription of the [CB_REST] DF bit                                          | 3    |

| • | Added the 0xB1 CB_REST_Enable() R/W command to enable or disable the CB_REST feature | 3    |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated