# Tech Note How to Implement Multi-level Dynamic Voltage Scaling with TPS63900

# Julian Hagedorn

The TPS63900 is a high-efficient synchronous buckboost converter with an extremely low quiescent current (75 nA typical). The 2-level dynamic voltagescaling feature lets applications switch between two output voltages during operation; for example, to save power by using a lower system supply voltage during standby operation. Some applications, for example, a headphone amplifier, might need additional voltage levels to finely adjust the amplifier output power for different headphone loads.

This application note describes options to implement multi-level digital voltage scaling with TPS63900.

#### CFG pin interface

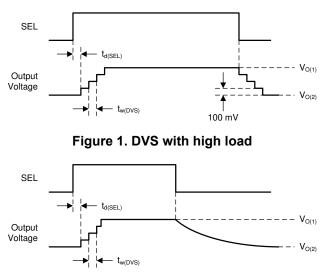

The device has a three configuration pins (CFGx) with a resistor to digital (R2D) interface. One of 16 different resistor values select the settings on each CFGx pin (see data sheet for programming options). The three CFGx pins allow the user to program an optional input current limit and two output voltages ( $V_{O(1)}$  and  $V_{O(2)}$ ), that are selectable via the SEL pin. The output voltage changes between the two targets with a slew rate of 100 mV in 125 µs or 0.8 V/ms (see Figure 1).

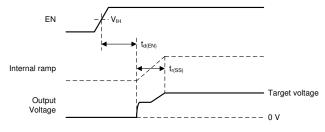

The device does not actively discharge the output capacitor, when the output voltage ramps from a high to a lower output voltage. This leads to a longer output voltage settling time when light load is applied (see Figure 2). The settling time can be calculated with Equation 1.

$$t_{\text{settle}} = C_{\text{O}} \times \frac{V_{\text{O(HIGH)}} - V_{\text{O(LOW)}}}{I_{\text{O}}}$$

(1)

#### where

- t<sub>settle</sub> is the capacitor discharge time

- V<sub>O(HIGH)</sub> is the higher output voltage

- V<sub>O(LOW)</sub> is the lower output voltage

- I<sub>O</sub> is the average output current

- C<sub>O</sub> is the effective output capacitance

**TEXAS INSTRUMENTS**

Figure 2. DVS with light load

#### Start-up behavior

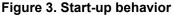

During normal operation of the converter the R2D interface is disabled to save power and increase efficiency. The device evaluates the CFG pins only at startup after the EN pin toggles from low to high with Vin already applied (see Figure 3). The enable time from the EN low to high transition until the device starts operating is specified with maximum  $t_{d(EN)} = 1.5$  ms. After this, the soft-start feature ramps up the output voltage (see data sheet for further details). The typical output voltage ramp time can be calculated with Equation 2.

1

www.ti.com

$$t_{r(SS)} = V_0 \times 1.25 \left[\frac{ms}{V}\right] - 1.75 \left[ms\right]$$

(2)

where

$t_{r(SS)}$  is the rise time of the output voltage in ms

The total start-up time from the EN low to high transition until a settled output voltage is the sum of  $t_{d(EN)}$  and  $t_{r(SS)}$ .

The device can start-up, when the output voltage is not zero. This is beneficial, if the application requires an output voltage, when changing the CFG pin setting. However, in this case the output capacitor needs to be sized accordingly that it can supply the system during the  $t_{d(EN)}$  time. Equation 3 can be used to calculate the output capacitor size ( $C_{\Omega}$ ).

$$C_{O} = t_{d(EN)} \times \frac{I_{O}}{V_{O(HIGH)} - V_{O(LOW)}}$$

(3)

#### where

- $V_{O(HIGH)}$  is the output voltage before the change

- V<sub>O(LOW)</sub> is the allowed minimum voltage

# **Re-read of CFG pins**

One option is to change the resistor value on a CFG pin. A change of the resistor value on a CFG pin only changes the configuration after toggling the EN pin from high to low to high.

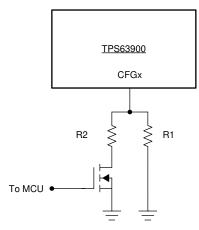

Figure 4. Multi resistor configuration

Figure 4 shows a simple implementation to switch between 2 resistor values. R1 will be selected when the transistor is open. When the transistor is closed, the parallel resistance of both resistors determines the new value (Rtotal). R2 is the parallel resistor that can be calculated with Equation 4.

$$R2 = \frac{R1 \times R_{total}}{R1 - R_{total}}$$

(4)

where

R<sub>total</sub> is the needed parallel resistance of R1 and R2 for the new setting

For example, if CFG3 setting should be changed between 2.1 V and 3.3 V, R1 has to be 16.2 k $\Omega$ . With R2 = 1.24 k $\Omega$ , R<sub>total</sub> calculates to 1.152 k $\Omega$ .

#### Using a reference voltage

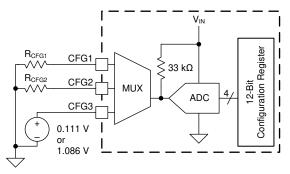

Instead of switching resistors, a voltage can be applied to the CFG pin. Figure 5 shows the internal structure of the R2D interface. At start-up the ADC reads the voltage across the external resistor. Therefore one can apply a voltage (V<sub>CFG</sub>) with a DAC to the CFG pin during start-up. After start-up the DAC can be disabled.

Note, the needed voltage depends on the input voltage (V<sub>IN</sub>) and the external resistor. The voltage can be calculated with Equation 5.

$$V_{CFG} = \frac{R_{ext}}{R_{ext} + R_{int}} \times V_{IN}$$

(5)

where

- $R_{int}$  = 33 k $\Omega$

- Rext is the desired configuration value

# Figure 5. Internal structure of CFG pin interface

For example, if CFG3 setting should be changed between 2.1 V and 3.3 V setting at  $V_{IN}$  = 3.3 V,  $V_{CFG}$ is 111 mV or 1.086 V.

# References

# TPS63900 data sheet

How to Implement Multi-level Dynamic Voltage Scaling with TPS63900

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated