# Technical White Paper **Powering a New Era of High-Performance Space-Grade Xilinx FPGAs**

# TEXAS INSTRUMENTS

Javier Valle, Adrian Helwig, Daniel Hartung, and Kurt Eckles. Written in collaboration with Xilinx and Alpha Data.

#### ABSTRACT

Today's space industry is undergoing an unprecedented expansion across numerous dimensions. There is a rapid increase in the number of spacecraft deployed either in low-earth orbit, mid-earth orbit or geosynchronous orbit. An ever-expanding number of spacecraft includes advanced architectures that deliver a plethora of new scientific instruments.

For many systems, power is now the No. 1 design constraint, as the migration to higher levels of performance and smaller form factors make designing within the same or even lower power budgets more challenging.

Xilinx's 20-nm Kintex UltraScale<sup>™</sup> XQRKU060 radiation-tolerant field-programmable gate arrays (FPGAs) are powerful enough to enable entirely new system architectures. The XQRKU060's ability to support in-flight reprogrammable systems gives satellite operators the ability to potentially reconfigure the basic functionality of the satellite, which is not possible in today's fixed-function implementations. Beyond adding a new level of flexibility, the XQRKU060 enables increased data throughput, which helps reduce the costs of transporting data. These new architectures are also capable of supporting artificial intelligence applications, enabling the satellite to locally process an image or radar data without the normal requirement of ground-based review, thus improving mission responsiveness and real-time processing.

#### **Table of Contents**

| 1 Powering the XQRKU060: Key Challenges |

|-----------------------------------------|

|                                         |

| 3 AC Regulation                         |

| 4 Radiation Effects                     |

| 5 ADA-SDEV-KIT2 Platform                |

| 6 Conclusion                            |

| 7 Key Contributors                      |

#### List of Figures

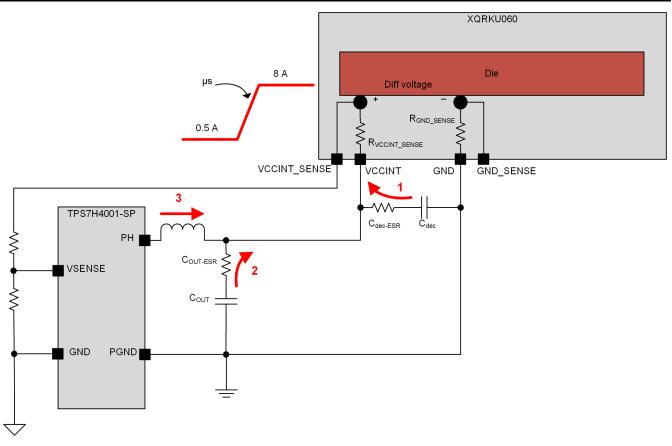

| Figure 2-1. XQRKU060 Sensing Connections to the TPS7H4001-SP                                                                                                                                                                                                                                                                                                     | 3   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2-2. Voltages at the XQRKU060 Pins as a Result of Sensing Pins                                                                                                                                                                                                                                                                                            | 3   |

| Figure 2-3. Differential Voltage Across the XQRKU060 for Two Different R <sub>GND SENSE</sub> Values                                                                                                                                                                                                                                                             | . 4 |

| Figure 3-1. AC Regulation Response Due to Load Transients                                                                                                                                                                                                                                                                                                        |     |

| Figure 5-1. The ADA-SDEV-KIT2 Platform for the KU060                                                                                                                                                                                                                                                                                                             | 6   |

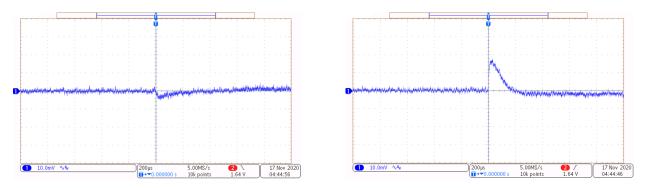

| Figure 5-2. VCCINT transient response with respect to GND using bitstream No. 1 in the ADA-SDEV-KIT2. The<br>response on the left represents the increasing load step and the response on the right represents the decreasing load<br>step                                                                                                                       | 7   |

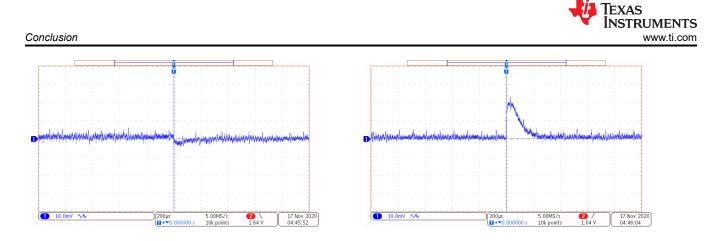

| Figure 5-3. VCCINT_SENSE transient response with respect to GND_SENSE using bitstream No. 1 in the ADA-SDEV-<br>KIT2. The response on the left represents the increasing load step and the response on the right represents the<br>decreasing load step                                                                                                          |     |

| response on the left represents the increasing load step and the response on the right represents the decreasing load<br>step<br>Figure 5-3. VCCINT_SENSE transient response with respect to GND_SENSE using bitstream No. 1 in the ADA-SDEV-<br>KIT2. The response on the left represents the increasing load step and the response on the right represents the |     |

#### List of Tables

| Table 5-1 | . Bitstreams Used to Evaluate the XQRKU060 in the ADA-SDEV-KIT2 | 6 |

|-----------|-----------------------------------------------------------------|---|

| Table 5-2 | . VCCINT Decoupling Capacitors Used in the ADA-SDEV-KIT2        | 7 |

# Trademarks

Texas Instruments www.ti.com

UltraScale<sup>™</sup> is a trademark of UltraScale. All trademarks are the property of their respective owners.

# 1 Powering the XQRKU060: Key Challenges

As a result of its high performance, depending on its programmed capabilities (clock frequency, logic usage), the total on-chip power required for an FPGA could be as high as 30 W. The core voltage of the chip, VCCINT, needs a large percentage of this power. At about 0.95-V nominal (see the XQRKU060 data sheet and Xilinx Power Estimator [XPE] for exact values), depending on the bitstream deployed, this power could translate to more than 25 A of current. Additionally, because of the advanced XQRKU060 process-node technology, the VCCINT voltage electrical tolerance requirements are tight; this tolerance includes electrical performance as well as radiation effects. Therefore, powering up devices like the XQRKU060 requires a different approach to meet the tolerances for successful operation of the device. Let's separate these challenges into DC and AC regulation.

## 2 DC Regulation

One obvious factor related to DC regulation is the DC setpoint accuracy of the converter supplying VCCINT. This DC accuracy depends on factors such as the accuracy of the converter's internal reference, the passives used with the converter (such as feedback resistors) and the layout of the printed circuit board (such as ohmic drops). From these factors, the internal reference of the converter represents a large percentage of the voltage accuracy specified by the FPGA manufacturer. However, you should calculate the accuracy of the internal reference in a way that is representative of the application.

As an example, temperature heavily influences the voltage drift of a reference; thus, you should calculate the accuracy for the temperature range to which the devices will be exposed during the mission. Typically, this range is from  $-40^{\circ}$ C to  $+90^{\circ}$ C, which is smaller than the standard military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C used to characterize space-rated devices. The TPS7H4001-SP from Texas Instruments has an internal reference with  $\pm 1.5\%$  accuracy across electrical and radiation conditions for the entire military temperature range. A simple calculation of the temperature coefficient (0.1 mV/°C) reveals that in the actual application ( $-40^{\circ}$ C to  $+90^{\circ}$ C), the accuracy of the internal reference is about  $\pm 1.1\%$ . You must also take into account radiation effects that could potentially affect DC regulation.

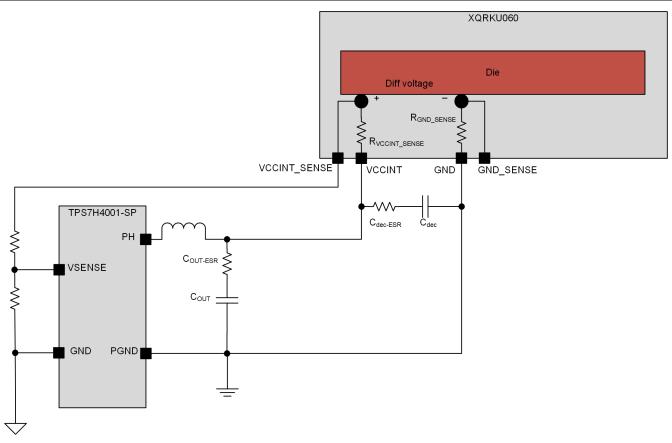

DC regulation typically refers only to the DC setpoint accuracy of the converter supplying VCCINT. The XQRKU060, as well as the converters that provide its power, is offered in a ceramic package because of its use in space applications. While ceramic packages offer hermeticity, they also present unique challenges not encountered in commercial-rated devices, including a larger footprint and larger resistance given the materials used in the package. In the case of the XQRKU060, the effect of ceramic package resistance in DC regulation is larger as the current increases, and the current will depend on the bitstream used. To mitigate this larger resistance, the XQRKU060 offers two pins, VCCINT\_SENSE and GND\_SENSE. Figure 2-1shows the connections needed between the TPS7H4001-SP and the XQRKU060 sensing pins, as well as a simple representation of the internal package resistance for VCCINT and GND.

Because the TPS7H4001-SP does not offer a GND sensing pin, using only the VCCINT\_SENSE pin in the XQRKU060 for the feedback signal (VSENSE) compensates for the voltage drop created by the package resistance RVCCINT\_SENSE, as shown in Figure 2-1. If you don't use the GNDSENSE pin for regulation, there is a small resistance that you need to account for. XPE provides the exact value for VCCINT to account for this small resistance. If not used, you can route the GNDSENSE pin to an optional test point or leave it floating, as indicated in the XQRKU060 data sheet.

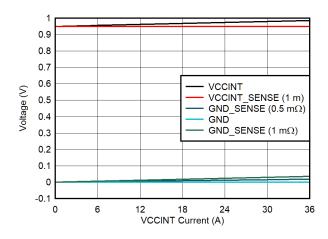

As the current supplied by the TPS7H4001-SP increases, the internal differential voltage across the XQRKU060 die might decrease, depending on the internal RGND\_SENSE resistance. Figure 2-2 shows the relationship between VCCINT current and the different pin voltages for two different assumed values of internal package resistance. Both cases assume a nominal VCCINT voltage of 0.95 V.

The first scenario in Figure 2-2 assumes the same resistance value of 1 m $\Omega$  for both R<sub>VCCINT\_SENSE</sub> and R<sub>GND\_SENSE</sub>. In this case, you can see how the VCCINT\_SENSE voltage remains constant at 0.95 V (dotted red line), while the GND\_SENSE voltage (dotted black line) increases as the VCCINT current increases.

GND signals and planes are typically the least resistive in ceramic packages given the large number of pins and planes used. Therefore, Figure 2-2 also shows an example where  $R_{VCCINT\_SENSE} = 1 \text{ m}\Omega$  but  $R_{GND\_SENSE} = 0.5 \text{ m}\Omega$ . In this particular case, the increase in the GND\_SENSE voltage (dotted blue line) as the VCCINT current increases is much less than when  $R_{GND\_SENSE} = 1 \text{ m}\Omega$ . It is important to reemphasize that when using XPE, even this low  $R_{GND\_SENSE}$  value is compensated in the exact VCCINT value indicated.

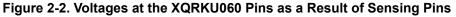

Figure 2-3 shows the impact of these two scenarios in the differential voltage across the XQRKU060 die. You can see that when  $R_{VCCINT\_SENSE} = R_{GND\_SENSE} = 1 \text{ m}\Omega$ , the differential voltage across the XQRKU060 die decreases to 0.914 V as the VCCINT current reaches 36 A. When  $R_{VCCINT\_SENSE} = 1 \text{ m}\Omega$  but  $R_{GND\_SENSE} = 0.5 \text{ m}\Omega$ , however, the differential voltage only decreases to 0.932 V as the VCCINT current reaches 36 A. While the 18-mV difference between these two scenarios might seem low, this translates to a 3.7% (VCCINTdiff = 0.914 V) vs. a 1.9% (VCCINTdiff = 0.932 V) DC-regulation tolerance (from 0.95-V nominal), which is significant in the context of VCCINT voltage tolerance requirements.

Figure 2-3. Differential Voltage Across the XQRKU060 for Two Different R<sub>GND SENSE</sub> Values

## 3 AC Regulation

AC regulation is associated with load transients in the VCCINT rail. These load transients depend heavily on the programming code used in the FPGA. Consequently, we recommending writing the code in a way that avoids severe transients as much as possible – in other words, avoid enabling a large amount of logic in the FPGA at once. Load transients are always present, however, you need to properly address them to meet the regulation requirements.

Given the nature of some of these transients (some with high slew rates in the ampere-per-nanosecond range), the converter might not respond to the voltage drop caused by the transient quickly enough. This is where the decoupling capacitors recommended by Xilinx become critical (see the XQRKU060 data sheet for detailed information regarding decoupling capacitors for different transient scenarios). These decoupling capacitors are in addition to any internal decoupling capacitors typically included in FPGA packages. Figure 3-1 shows an example of an approximately 7-A load transient in the microseconds range.

4

Initially, the internal and external decoupling capacitors will respond to the current increase. The external decoupling capacitors are sized to match the worst-case expected transient based on the XQRKU060 data sheet recommendation and, as a result, they will handle the transient properly. In case the FPGA still requires additional current after the depletion of the decoupling capacitors, the output capacitors of the converter will supply current until the converter is able to respond. You must choose the crossover frequency of the converter and the respective feedback compensation accordingly for every application.

# **4 Radiation Effects**

Along with DC and AC regulation, we recommend you consider any radiation effects introduced by the converter to meet the tolerance requirements from the XQRKU060. These radiation effects include total ionizing dose (TID) and single-event transients (SETs).

TID could introduce drift in the internal reference of the converter that could affect DC regulation. The TPS7H4001-SP is rated up to 100 krad(Si), and Texas Instruments tests every specification to meet the data sheet limits after exposure to 100 krad(Si). The internal reference of the TPS7H4001-SP shows very little sensitivity to TID, with a maximum drift of 2 mV (~0.3%) at 100 krad(Si).

Transients induced by heavy ions (SETs) are not as predictable as TID and could have a very negative effect on regulation. A converter sensitive to transients that shuts down the output of the converter or exceeds the maximum regulation requirements of the XQRKU060 could severely compromise the performance of the FPGA. Additionally, large and positive transients could potentially damage the FPGA.

The TPS7H4001-SP is fully characterized for SETs up to a linear energy transfer (LET) equal to 75 MeV-cm2/mg and shows resilient performance with a low number of SETs (<10 at PVIN = 5 V, VIN = 5 V) when the output voltage exceeds  $\pm 3\%$  at a fluency of 10 million ions/cm2 (see the Single Events Effects Test Report of the TPS7H4001-SP for details). This translates to a very low SET cross-section of 2.18 × 10-7 cm2/device (PVIN = 5 V, VIN = 5 V). This SET performance, along with its TID rating of 100 krad(Si), makes the TPS7H4001-SP a reliable converter to power up the XQRKU060.

# 5 ADA-SDEV-KIT2 Platform

With the ADA-SDEV-KIT2 platform from Alpha Data Parallel Systems, you can evaluate the KU060 (the commercial package) alongside a space-rated power solution from Texas Instruments. The platform also allows you to test the interaction of the KU060 with other devices (such as high-speed analog-to-digital converters) through its FPGA mezzanine card connectors. Figure 5-1 shows a picture of the ADA-SDEV-KIT2.

Figure 5-1. The ADA-SDEV-KIT2 Platform for the KU060

To test the performance of the TI-based power supply on the ADA-SDEV-KIT2 platform, Texas Instruments and Alpha Data Parallel Systems performed a large amount of testing using a modified version of the ADA-SDEV-KIT2 kit that used the XQRKU060 (ceramic package) instead of the KU060 (commercial package).

The testing focused on two aspects:

- Assessing the behavior of the XQRKU060 ceramic package and correlating it to the expectations of the GND pins resistance discussed in this paper.

- Validating the approach shown in Table 5-1 (nonuse of the GND\_SENSE pin) in DC and AC conditions.

To validate the first aspect, the testing focused on measuring the GND\_SENSE pin voltage using two different bitstreams to calculate RGND\_SENSE. The bitstreams were generated in a way that the FPGA would require a current from the VCCINT rail large enough to generate a voltage at the GND\_SENSE pin. Table 5-1 lists the main features for these two bitstreams. All of the measurements were in DC conditions.

|                                  |                        | Bitstream No. 1 | Bitstream No. 2 |

|----------------------------------|------------------------|-----------------|-----------------|

| Clock rate                       |                        | 13%, 150 MHz    | 7%, 200 MHz     |

| Logic usage                      |                        | 81%             | 24%             |

| Block random access memory usage |                        | 0               | 47%             |

| Digital signal processor usag    | je                     | 0               | 19%             |

| Gigabit transceiver usage        |                        | 0               | 0%              |

| Peak VCCINT core current         |                        | ≅9 A            | ≅25 A           |

| XPE VCCINT voltages              | CCINT voltages Minimum |                 | 0.922 V         |

|                                  | Maximum                | 0.993 V         | 0.998 V         |

|                                  |                        |                 |                 |

| Table 5 1  | Ritetroame | llead to E | Evaluato th |               | a tha A | DA-SDEV-KIT2 |

|------------|------------|------------|-------------|---------------|---------|--------------|

| Table 5-1. | Bitstreams | Usea to E  | zvaluate th | E XQKKUU6U II | n the A | DA-SDEV-KIIZ |

For the resistance calculations, the COMP pin voltage in the TPS7H4001-SP approximated the current corresponding to each bitstream shown in Table 5-1, approximately 9 A and 25 A. The COMP pin voltage correlates to the peak output current from the power stage of the device. These current approximations

6

were also very closely aligned with the VCCINT and VCCINT\_IO currents obtained from XPE (VCCINT and VCCINT\_IO are internally connected in the XQRKU060, as indicated in the data sheet).

The data after this testing resulted in RGND\_SENSE values of 0.25 m $\Omega$  and 0.36 m $\Omega$  for the approximately 9-A and 25-A bitstreams, respectively. This agrees with the expectations that GND signals and planes are typically the least resistive in ceramic packages given the large number of pins and planes used.

All tested cases met the DC regulation requirements for the VCCINT in the XQRKU060, as validated by XPE and Vivado software.

Writing bitstream No. 1 into the external configuration flash memory of the ADA-SDEV-KIT2 validated the AC regulation. The FPGA was cleared and then configured from the flash memory in a constant loop. The DONE signal from the FPGA connected to a diode was used as a trigger to capture the AC transients.

The signals captured were VCCINT, GND, VCCINT\_SENSE and GND\_SENSE. The first two signals were captured across a decoupling capacitor under the FPGA. The SENSE signals were captured using  $0-\Omega$  resistor footprints (not populated for the ceramic package version of the KU060) under the FPGA that provided connection to the VCCINT\_SENSE and GND\_SENSE pins. For reference, Table 5-2 lists the VCCINT decoupling capacitors used in the ADA-SDEV-KIT2. This capacitance does not include the decoupling capacitors used for the TPS7H4001-SP.

| Capacitor value (µF) | Quantity |

|----------------------|----------|

| 680                  | 3        |

| 100                  | 5        |

| 47                   | 13       |

| 4.7                  | 10       |

| 1                    | 16       |

| 0.22                 | 55       |

Table 5-2. VCCINT Decoupling Capacitors Used in the ADA-SDEV-KIT2

While in the unprogrammed state, the VCCINT rail in the ADA-SDEV-KIT2 FPGA consumes approximately 0.5 A. This means that each time the FPGA was either configured or cleared, approximately a 8.5-A transient would occur.

Figure 5-2 shows scope shots of the VCCINT response with respect to GND, while Figure 5-3 shows scope shots of the VCCINT\_SENSE response with respect to GND\_SENSE. In both cases, the load-step responses meet the  $\pm$ 38-mV regulation requirement from XPE as shown in Table 5-1 (0.917 V-0.993 V).

Figure 5-2. VCCINT transient response with respect to GND using bitstream No. 1 in the ADA-SDEV-KIT2. The response on the left represents the increasing load step and the response on the right represents the decreasing load step.

7

# Figure 5-3. VCCINT\_SENSE transient response with respect to GND\_SENSE using bitstream No. 1 in the ADA-SDEV-KIT2. The response on the left represents the increasing load step and the response on the right represents the decreasing load step.

## 6 Conclusion

The XQRKU060 is a high-performance FPGA for space applications that is enabling new system architectures in a rapidly evolving market. Given its advanced computing capability, powering up the XQRKU060 requires considering multiple scenarios and constraints in order to meet its voltage regulation requirements. These scenarios include DC and AC regulation as well as radiation effects. By configuring the output voltage of the TPS7H4001-SP to the specific voltage indicated by XPE, along with the VCCINT\_SENSE pin connection, you can be confident in obtaining a robust and validated radiation-hardened power supply.

# 7 Key Contributors

#### **Texas Instruments (TI):**

- Javier Valle, Systems Manager, Space Power Products

- Adrian Helwig, Principal Field Applications Engineer

- Daniel Hartung, Applications Engineer, Space Power Products

- Kurt Eckles, Product Marketing Engineer, Space Power Products

#### Xilinx:

- John Heslip, Staff Technical Marketing Engineer

- Troy Jones, Space Systems Architect

#### Alpha Data Parallel Systems:

• Stephen McKeown, Sr. Design Engineer

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated