**High-Performance Analog Products**

# Analog Applications Journal

Second Quarter, 2009

© Copyright 2009 Texas Instruments

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products<br>Amplifiers<br>Data Converters<br>DLP® Products<br>DSP<br>Clocks and Timers<br>Interface<br>Logic<br>Power Mgmt<br>Microcontrollers<br>RFID<br>RF/IF and ZigBee®<br>Solutions | amplifier.ti.com<br>dataconverter.ti.com<br>www.dlp.com<br>dsp.ti.com<br>www.ti.com/clocks<br>interface.ti.com<br>logic.ti.com<br>power.ti.com<br>microcontroller.ti.com<br>www.ti-rfid.com<br>www.ti.com/lprf | Applications<br>Audio<br>Automotive<br>Broadband<br>Digital Control<br>Medical<br>Military<br>Optical Networking<br>Security<br>Telephony<br>Video & Imaging<br>Wireless | www.ti.com/audio<br>www.ti.com/automotive<br>www.ti.com/broadband<br>www.ti.com/digitalcontrol<br>www.ti.com/medical<br>www.ti.com/military<br>www.ti.com/opticalnetwork<br>www.ti.com/security<br>www.ti.com/telephony<br>www.ti.com/video<br>www.ti.com/wireless |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                          | Mailing Address:                                                                                                                                                                                               | Texas Instruments<br>Post Office Box 655303                                                                                                                              |                                                                                                                                                                                                                                                                    |

www.ti.com/aaj

Dallas, Texas 75265

# Contents

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Data Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| How the voltage reference affects ADC performance, Part 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5          |

| Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

| <b>Taming linear-regulator inrush currents</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .9         |

| Designing a linear Li-Ion battery charger with power-path control1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2          |

| Power-path control in a charger is a fairly simple design concept, but there is more to a good design than the basic topology. This article presents an analysis of the power-path capabilities and safety features of the bq2407x family. These fully integrated chargers manage loading, give priority to the system, increase reliability, allow less expensive adapters to be used, and include many safety features at a lower total system cost.                                                                                                                                                                       |            |

| Selecting the right charge-management solution1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8          |

| Designers of portable devices must choose from a large assortment of battery chemistries, charger topologies, and charge-management solutions. The objective is to strike a balance between performance, cost, form factor, and other key requirements. This article provides an overview of several portable-power solutions.                                                                                                                                                                                                                                                                                               |            |

| Interface (Data Transmission)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| <b>Designing with digital isolators</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>'</u> 1 |

| Amplifiers: Op Amps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

| Using fully differential op amps as attenuators, Part 1: Differential bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| input signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3          |

| An ADC's requirement for a low-level differential input can be a problem when the input signal is at a high level such as ±10 V. This article presents the use of a fully differential operational amplifier (FDA) to match a balanced, differential bipolar input signal to the ADC input requirements. Circuit analysis is performed to aid understanding of the key design points, and a design methodology is presented for calculating the required component values. Spreadsheet calculation tools are provided along with example TINA-TI <sup>TM</sup> SPICE models to show how to implement the design methodology. |            |

| Index of Articles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ;7         |

| TI Worldwide Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .2         |

| 11 Wondwide Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | : <b>Z</b> |

### To view past issues of the Analog Applications Journal, visit the Web site www.ti.com/aaj

# Introduction

Analog Applications Journal is a collection of analog application articles designed to give readers a basic understanding of TI products and to provide simple but practical examples for typical applications. Written not only for design engineers but also for engineering managers, technicians, system designers and marketing and sales personnel, the book emphasizes general application concepts over lengthy mathematical analyses.

These applications are not intended as "how-to" instructions for specific circuits but as examples of how devices could be used to solve specific design requirements. Readers will find tutorial information as well as practical engineering solutions on components from the following categories:

- Data Acquisition

- Power Management

- Interface (Data Transmission)

- Amplifiers: Op Amps

Where applicable, readers will also find software routines and program structures. Finally, *Analog Applications Journal* includes helpful hints and rules of thumb to guide readers in preparing for their design.

# How the voltage reference affects **ADC performance, Part 1**

By Bonnie Baker, Senior Applications Engineer, and Miro Oljaca, Senior Applications Engineer

### Introduction

When designing a mixed-signal system, many designers have a tendency to examine and optimize each component separately. This myopic approach can go only so far if the goal is to have a working design at the end of the day. Given the array of different components in a system. designers must have a complete understanding of not only the individual components but also their impact on the overall system performance. When a design has an analogto-digital converter (ADC), it is critical to understand how this device interacts with the voltage reference and voltagereference buffer.

This article is the first of a three-part series. Parts 2 and 3 will appear in future issues of the Analog Applications Journal. Part 1 looks at the fundamental operation of an ADC independently, exactly as many designers do, and then at the performance characteristics that have an impact on the accuracy and repeatability of the system. Part 2 will delve into the voltage-reference device, once again examining its fundamental operation and then the details of its impact on the performance of the ADC. Part 3 will investigate the impact of the voltage-reference buffer and the capacitors that follow it, and will discuss how to ensure that the amplifier is stable. Assumptions and conclusions will be compared to measurement results. The interplay between the driving amplifier, voltage reference, and converter will be briefly analyzed, followed by an investigation of the sources of error in the ADC's conversion results.

### The fundamentals of ADCs

Figure 1 shows the voltage-reference system for the successive-approximation-register (SAR) ADC that will be examined in this three-part series. As the name suggests, the ADC converts an analog voltage to a digital code. The overall system accuracy and repeatability depend on how effectively the converter executes this process. The accuracy of this conversion can be defined with static specifications, and the repeatability with dynamic specifications. Generally, the ADC static specifications are offset-voltage error, gain error, and transition noise. The ADC dynamic specifications are signal-to-noise ratio (SNR), total harmonic distortion (THD), and spurious-free dynamic range (SFDR).

### **Static performance**

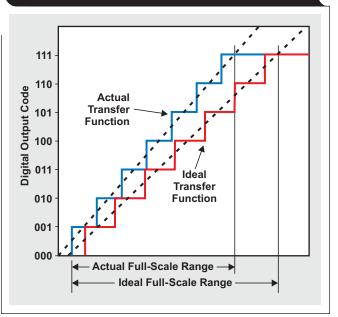

Figure 2 shows an ideal and an actual (or non-ideal) transfer function of a 3-bit ADC. The actual transfer function has an offset-voltage error and a gain error. In the example application circuit, only the ADC gain error, transition noise, and SNR are of concern.

Voltage Reference ESR CL2 VREF D<sub>OUT</sub> V<sub>IN</sub> ADC

Figure 1. Voltage-reference system for SAR ADC

### Figure 2. Ideal and actual ADC transfer functions with offset and gain errors

Equation 1 describes the typical transfer function of the ideal (error-free) ADC:

$$Code = V_{IN} \times \frac{2^{n}}{V_{REF}},$$

(1)

where "Code" is the ADC output code in decimal form,  $V_{IN}$  is the analog input voltage (in volts), n is the resolution of the ADC (or number of output-code bits), and  $V_{REF}$  is the analog value of the voltage reference (in volts). This equation demonstrates that the ADC output code is directly proportional to the analog input voltage and inversely proportional to the voltage reference. Equation 1 also shows that the output code depends on the number of bits (the converter resolution).

The DC errors of non-ideal ADCs are offset-voltage error and gain error. If the offset-voltage error is introduced into the transfer function, Equation 1 can be rewritten as

$$Code = (V_{IN} - V_{OS_ADC}) \times \frac{2^{n}}{V_{REF}},$$

(2)

where  $V_{\rm OS\_ADC}$  is the input offset voltage of the ADC. Gain error is equal to the difference between the ideal slope from zero to full scale and the actual slope from zero to full scale. The notation for gain error is a decimal or percentage. If the impact of only the gain error (no offset-voltage error) on an ADC is considered, Equation 1 can be rewritten as

$$Code = V_{IN} \times \frac{2^{II}}{V_{REF} (1 - GE_{ADC})},$$

(3)

where  $GE_{ADC}$  is the gain error in decimal form, expressed as

## $GE_{ADC} = \frac{Actual Gain - Ideal Gain}{Actual Gain}$

From Equation 3 it can be seen that the gain-error factor adds to the initial accuracy of  $V_{REF}$ . The output code is inversely proportional to the combination of the voltage reference plus the gain error. The DC error caused by noise from the voltage-reference chip inversely impacts the gain accuracy of the ADC. Part 2 of this series will specifically show the impact of the voltage reference's errors.

Equations 2 and 3 can be combined to show the final transfer function:

$$Code = (V_{IN} - V_{OS_ADC}) \times \frac{2^{n}}{V_{REF} (1 - GE_{ADC})}$$

(4)

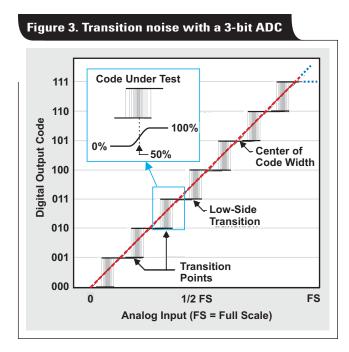

To analyze ADC transition noise, the code transition points in the ADC's transfer curve can be examined. These are the points where the digital output switches from one code to the next as a result of a changing analog input voltage. The transition point from code to code is not a single threshold but a small region of uncertainty. Figure 3 shows the uncertainty at these transitions that results from internal converter noise. The region of uncertainty is defined by measuring repetitive code transitions from code to code.

An ADC's transition noise has a direct effect on the signal-to-noise ratio (SNR) of the converter. Since it is important to understand this phenomenon, Part 2 of this series will look more closely at voltage-reference noise characteristics.

### **Dynamic performance**

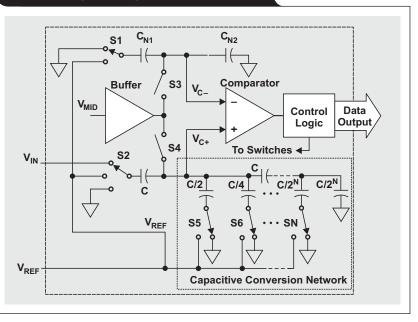

The total system noise from the circuit in Figure 1 is a combination of the inherent ADC noise, the noise from the analog inputbuffer circuitry, and the reference inputvoltage noise. Figure 4 shows a simplified internal circuit of a SAR ADC.

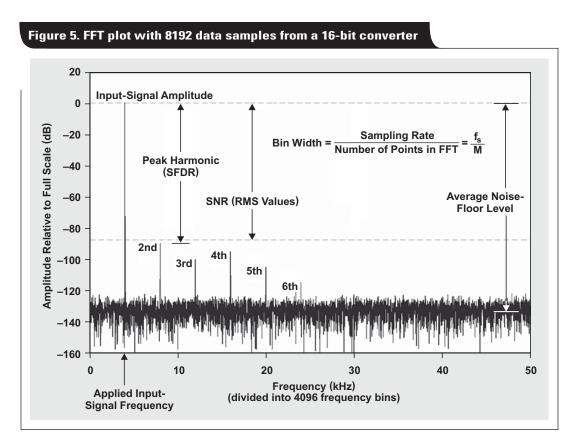

To determine the dynamic performance of an ADC, a fast Fourier transform (FFT) plot of the converter's output data can be used. An FFT plot can be calculated from a consistent clocked series of converter outputs. The FFT plot provides the SNR, the noisefloor level, and the spurious-free dynamic range (SFDR). In the example application circuit, only the SNR specification is of interest. Figure 5 provides an FFT plot of these specifications.

A useful way of determining noise in an ADC circuit is to examine the SNR (see Figure 5). The SNR is the ratio of the root mean square (RMS) of the signal power to the RMS of the noise power. The SNR of the

FFT calculation is a combination of several noise sources, which may include the ADC quantization error and the ADC internal noise. Externally, the voltage reference and the reference driving amplifier contribute to the overall system noise. The theoretical limit of the SNR is equal to 6.02n + 1.76 dB, where n is the number of ADC bits.

### Figure 4. Simplified topology of a SAR ADC

The total harmonic distortion (THD) quantifies the amount of distortion in the system. THD is the ratio of the root sum square (RSS) of the powers of the harmonic components (spurs) to the input-signal power. For example, in Figure 5, the harmonic components are labeled "2nd" through "6th." An RSS calculation is also known as the

TI Lit. #

square root of the sum of the squares of several values. Spurs resulting from the nonlinearity of the ADC appear at whole-number multiples of the input signal's frequency (the fundamental frequency). Most manufacturers use the first six to nine harmonic components in their THD calculations.

If the ADC creates spikes in the FFT plot, it is probable that the converter has some integral nonlinearity errors. Additionally, spurs can come from the input signal through the signal source or from the reference driving amplifier. If the driving amplifier is the culprit, the amplifier may have crossover distortion; or it may be marginally stable, slewrate-limited, bandwidth-limited, or unable to drive the ADC. Injected noise from other places in the circuit, such as digital-clock sources or the frequency of the mains, can also contribute spurs to the FFT result.

The combination of the converter's SNR and THD can be used to determine the signal to noise and distortion (SINAD) of the device. Many engineers refer to SINAD as "THD plus noise" or "total distortion." SINAD is an RSS calculation of the SNR and THD; i.e., it is the ratio of the fundamental input signal's RMS amplitude to the RMS sum of all other spectral components below half the sampling frequency (excluding DC). While the SAR converter's theoretical minimum for SINAD is equal to the ideal SNR, or 6.02n + 1.76 dB, the working SINAD is

SINAD (dB) =

$$-20 \log \sqrt{10^{-\text{SNR}/10} + 10^{\text{THD}/10}}$$

. (5)

SINAD is an important figure of merit because it provides the effective number of bits (ENOB) with a simple calculation:

$$ENOB = \frac{SINAD - 1.76 \text{ dB}}{6.02}$$

(6)

In an FFT representation of converter data, the average noise floor (see Figure 5) is an RSS combination of all the bins within the FFT plot, excluding the input signal and signal harmonics. The number of samples versus the number of ADC bits can be chosen so that the noise floor is below any spurs of interest. With these considerations, the theoretical average FFT noise floor (in decibels) is

FFT Noise Floor =

$$6.02n + 10 \log \left(\frac{3M}{\pi \times \text{ENBW}}\right)$$

where M is the number of data points in the FFT, and ENBW is the equivalent noise bandwidth of the FFT window function. A reasonable number of samples for the FFT of a 12-bit converter is 4096, which will result in a theoretical noise floor of -107 dB.

### Conclusion

The ADC specifications that impact the application circuit in Figure 1 are gain error, transition noise, and SNR. Part 2 will examine the voltage reference's DC accuracy and noise contribution to the system performance.

### References

For more information related to this article, you can download an Acrobat<sup>®</sup> Reader<sup>®</sup> file at www-s.ti.com/sc/techlit/ *litnumber* and replace "*litnumber*" with the **TI Lit. #** for the materials listed below.

### Document Title

- 1. Bonnie Baker, "A Glossary of Analog-to-Digital Specifications and Performance Characteristics," Application Report ...... sbaa147

- 3. Rick Downs and Miro Oljaca. Designing SAR ADC drive circuitry, Parts I – III. *EN-Genius Network: analogZONE: acquisitionZONE* [Online]. Available: http://www.analogzone.com/ acqt0000.pdf (Replace "0000" with "0221" for Part I, "1003" for Part II, or "0312" for Part III.) —

- 4. Tim Green. Operational amplifier stability, Parts 3, 6, and 7. *EN-Genius Network: analogZONE: acquisitionZONE* [Online]. Available: http://www.analogzone.com/ acqt0000.pdf (Replace "0000" with "0307" for Part 3, "0704" for Part 6, or "0529" for Part 7.)

- 5. Bonnie C. Baker and Miro Oljaca. (2007, June 7). External components improve SAR-ADC accuracy. *EDN* [Online]. Available: http://www.edn.com/contents/images/ 6447231.pdf

- Wm. P. (Bill) Klein, Miro Oljaca, and Pete Goad. (2007). Improved voltage reference circuits maximize converter performance. Analog e-Lab<sup>™</sup> Webinar [Online]. Available: http://dataconverter.ti.com (Scroll down to "Videos" under "Analog eLab<sup>™</sup> Design Support" and select webinar title.)

- 7. Art Kay. Analysis and measurement of intrinsic noise in op amp circuits, Part I. *EN-Genius Network: analogZONE: audiovideoZONE* [Online]. Available: http://www.en-genius.net/includes/files/ avt\_090406.pdf

### Related Web site

# **Taming linear-regulator inrush currents**

### **By Jeff Falin**

### Senior Applications Engineer

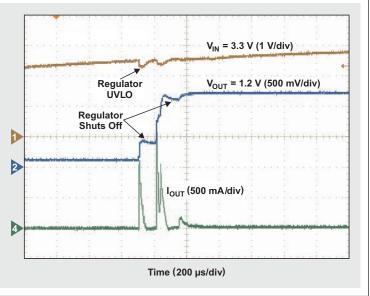

Many older linear regulators and some regulators specifically designed for fast start-up require significant inrush current at start-up to charge their output capacitors and to provide current to their resistive loads. The relationship  $\mathrm{I}_{\mathrm{Inrush}} = \mathrm{C}_{\mathrm{OUT}} \times$  $V_{OUT}/t_{Rise}\ predicts the regulator's required input$ current at start-up for a given rise time,  $t_{Rise}$ , where  $C_{OUT}$  is the regulator's output capacitance. With no inrush-control (commonly called "soft-start") circuitry,  $I_{Inrush}$  is clamped to the regulator's current limit, which is typically significantly higher than the regulator's rated current. If the input power supply is current-limited or connected by long inductive traces, the voltage at the regulator's input will droop, possibly below that of the regulator's undervoltage lockout (UVLO) circuit. Figure 1 illustrates how this causes the regulator to "stair step" or ratchet its way up to regulation, shutting down momentarily while the input capacitor recharges, then starting up again.

In the past, start-up problems were common for linear regulators and can still occur when the output capacitance seen by the regulator is large. Endequipment designers need to take into account how linear regulators handle inrush current, especially if the selected regulator has no inrush-current control other than clamping to its current limit.

Additional circuitry can be configured to manage inrush current for any regulator or converter. Simply by adding a FET and some passive elements following the regulator's or converter's output voltage, the designer can shape the FET's turn-on characteristic and the output-voltage waveform. For example, a designer has minimal control over

Figure 1. Older regulator with 2.5-V UVLO ratcheting up to regulation with no load

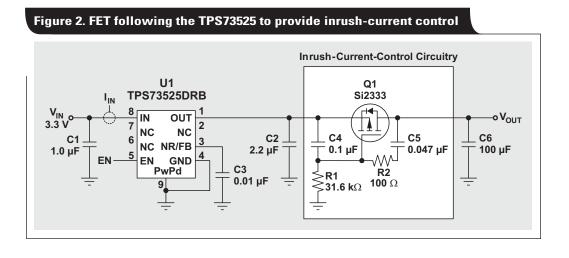

the inrush current of linear regulators designed for fast start-up, like the Texas Instruments (TI) TPS734xx/5xx, which have a high power-supply ripple rejection (PSRR), low noise, and an ultralow  $I_q$ . Figure 2 shows how adding a FET and some passive circuitry to the TPS73525 provides greater control over the inrush current.  $I_{IN}$  is measured between the regulator input pin and the input capacitor because both the capacitor and the input power supply will supply the inrush current.

009

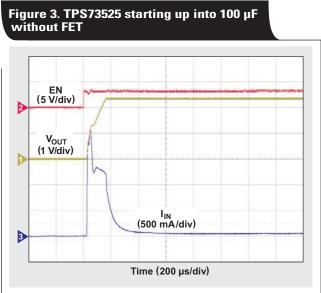

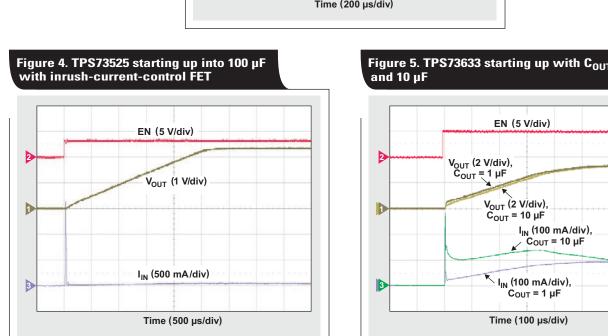

Note that in Figure 3 the amplitude and duration of the initial current spike are significantly reduced compared to those in Figure 4 because the output sees only the 2.2-µF capacitor instead of the 100-µF capacitor. Surprisingly, capacitor C5, providing additional FET gate-to-drain capacitance, and resistor R1 set the soft-start time. Reference 1 explains in detail how the additional circuit works, how to choose the FET, and how to size the passive elements.

Some regulators use a topology that has inherent inrushcurrent control. For example, the TI TPS732xx/4xx/6xx family of linear regulators has an internal charge pump that is needed to drive the gate of the n-channel pass element. At start-up, the charge pump needs a finite amount of time-several hundred microseconds-to charge the internal servo capacitor, which in turn charges the n-FET's gate capacitance. Figure 5 shows the TPS73633 output

voltage and inrush current at start-up with  $C_{OUT} = 1 \ \mu F$ and 10 µF.

Even though these linear regulators have an 800-mA maximum current limit, the inrush current never exceeds 150 mA, after a brief spike to 300 mA, even with a 10-µF output capacitor.

From the relationship  $I_{Inrush}$  =  $C_{OUT} \times V_{OUT}/t_{Rise},$  and by comparing the output voltage rise times in Figures 4 and 5, one can see that there is an inverse relationship between the output-voltage ramp time and the inrush current. Therefore, in recent years, IC manufacturers have developed linear regulators with user-controllable V<sub>OUT</sub> ramp time (soft start), not only to manage inrush current but also to meet the power-rail ramp-time requirements of certain DSPs and FPGAs. The simplest integrated soft-start method, used by the TI TPS74x01 family of regulators, is

# Figure 5. TPS73633 starting up with $C_{OUT} = 1 \mu F$

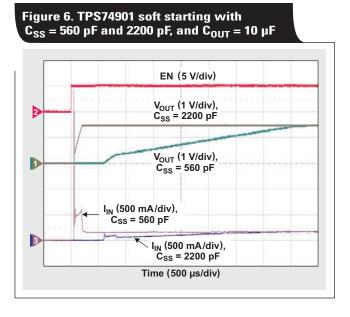

to slowly ramp the error amplifier's internal reference voltage following an enable signal. The IC uses an external capacitor ( $C_{SS}$ ) on the soft-start pin and an internal constant-current source ( $I_{SS}$ ) to linearly charge this capacitor, which is initially tied to the regulator's error amplifier. Once the capacitor is charged to the same value as the internal reference voltage,  $V_{REF}$ , the IC switches the error-amplifier connection to the internal reference. Therefore, without affecting regulation, the designer can set the soft-start time as predicted by a simple equation,  $t_{SS} = V_{REF} \times C_{SS}/I_{SS}$ , by adjusting the capacitor value. Figure 6 shows the TPS74901 output voltage and current at start-up, with two different soft-start capacitors and  $C_{OUT} = 10 \ \mu\text{F}$ .

This soft-start method is very common and works as predicted for start-up loads that are primarily capacitive and not resistive. When the start-up load has resistive loading, the method still works, but the ramp (soft-start) time is a bit longer than predicted by the  $t_{SS}$  equation.

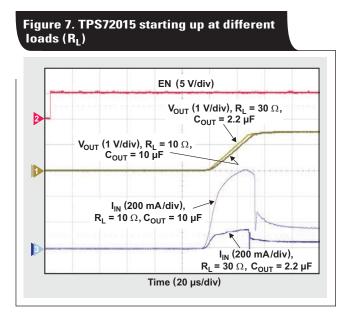

TI's low- $I_q$ , dual-rail, 350-mA TPS720xx linear regulator addresses simultaneous capacitive and resistive loads with a novel, internal architecture that limits inrush current. Instead of being clamped to an overcurrent-limit value as with older regulators, the current drawn from the input to the output is limited to a lower value,

$I_{Inrush\_Limit} = I_{R_1} + C_{OUT} (\mu F) \times 0.0455 (V/\mu s),$

where  $I_{R_L}$  is the start-up resistive loading. Figure 7 shows the TPS72015 starting up at different fixed resistive loads with  $C_{OUT}$  = 2.2  $\mu F$  and 10  $\mu F$ . The soft-start circuitry scales the soft-start current proportionally with  $C_{OUT}$  so that the start-up time is virtually independent of  $C_{OUT}$ .

### Conclusion

Historically, design engineers chose linear regulators for their low cost, simplicity, low noise, and high PSRR. Rarely did engineers consider a regulator's ability to control inrush current at start-up until after the choice was made. This oversight sometimes rendered the input power supply unable to supply enough start-up current, especially if the regulator had a large output capacitance. To continue going forward, designers had to use external circuitry to provide inrush-current control. Today, however, they can choose from a new generation of linear regulators with integrated soft start/inrush-current control. Taking soft start into consideration early in the design phase provides a problem-free system with controlled, predictable inrush current at start-up.

### References

For more information related to this article, you can download an Acrobat<sup>®</sup> Reader<sup>®</sup> file at www-s.ti.com/sc/techlit/ *litnumber* and replace "*litnumber*" with the **TI Lit. #** for the materials listed below.

### **Document Title**

TI Lit. #

11

### **Related Web sites**

power.ti.com

www.ti.com/sc/device/partnumber Replace partnumber with TPS72015, TPS73525,

TPS73633, or TPS74901

# Designing a linear Li-lon battery charger with power-path control

### **By Charles Mauney**

### Senior Systems/Applications Engineer, Battery Management and Charging Solutions

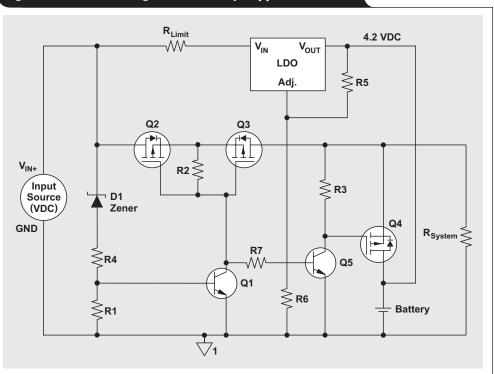

In theory, a linear battery charger with a separate power path for the system is a fairly simple design concept and can be built with an LDO adjusted to 4.2 V; a current-limit resistor; three p-channel FETs to switch the system load between the input power and the battery source; and some bias parts. In reality, there is much more to a good design than the basic topology. This article will discuss dynamic power-path management (DPPM) and explore safety features that turn a basic topology into a complete design.

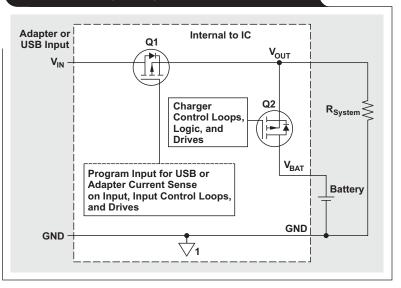

The DPPM topology is shown in Figure 1 and has two power-source pins,  $V_{IN}$  and  $V_{BAT}$ . The charger can be programmed for either a USB input or an adapter input. The design concept is to always power the system if power is available, either from  $V_{IN}$  or  $V_{BAT}$ , unless the system is programmed to shut down. The input FET regulates the output voltage and will also limit the input current to the programmed level if the load is excessive. The battery FET has control loops

associated with charging the battery and allowing the battery to power the system. The input controls and battery controls act independently and are discussed in more detail later.

Figure 2 shows a charger solution with a discrete power path. The LDO provides the regulated output voltage, and the inputcurrent-limit resistor limits the maximum current that can be delivered to the battery. D1, R1, R4, and Q1 monitor the input voltage and turn on Q2 and Q3 if input source power is present, connecting the input to the system load. If input source power is not present, Q5 and Q4 are biased on so the battery will provide power to the system load. This state will hereinafter be referred to as "battery-supplement mode."

### Figure 1. Power-path topology of battery charger

### Figure 2. Discrete charger with battery-supplement mode

This charger solution is simple and discrete but has many limitations and few safety features. Adding any safety feature will quickly drive up the solution cost but often may offset the liability cost of an unprotected design. LDOs are typically not highly accurate regulators, especially with external programmable resistors. If the regulation was set lower to ensure that the maximum battery voltage was not exceeded, the typical voltage and capacity would be lower. The crude current-limit resistor would allow more current at lower battery voltages and would not provide a conditioning current to help recover depleted cells or to prevent cell damage from excessive charging.

### **Typical integrated application**

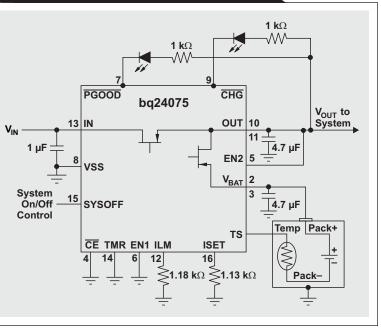

Figure 3 shows the Texas Instruments (TI) bq24075, a charger with a highly integrated power path in a  $3 \times 3$ -mm, 16-pin QFN package. The only external components required are two external programming resistors and three capacitors for the power sources.

### **Programmed input-source protection**

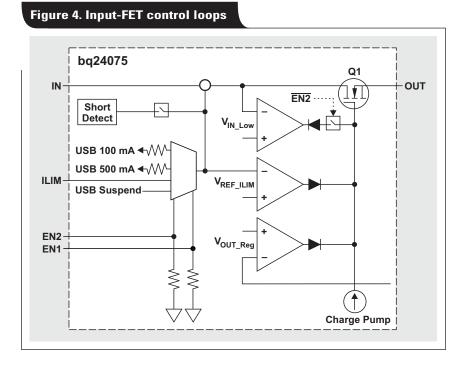

The input-current limit is programmed with the EN1/2 pins to one of four states: 100 mA, 500 mA, ILIM, or Suspend, as shown in Figure 4. A resistor can be used to program ILIM at any level up to the device's maximum input current. When current-limited, the input FET restricts the current to the OUT pin, causing the system voltage to drop to the DPPM threshold or to the battery voltage where the charge current will be reduced. Assuming that the protection was designed for the applied

# Figure 3. Typical integrated application with bq24075 charger

source, this feature solves the problem of the system overloading the adapter or the USB source, which could potentially damage the source or device. More powermanagement details are presented later under "DPPM protection of output voltage."

If a current-limited source such as a weak or wrong adapter or USB is used, the adapter and system voltages

will drop, causing the IC to enter DPPM mode or batterysupplement mode. Basing DPPM on the output voltage solves most loading issues by reducing the charge current, giving priority to the system load, and allowing operation with a weak power source or minor AC brownouts. Other input-current-management solutions without DPPM would not detect the weak source or reduce the charging current, and the system would crash.

The V<sub>IN Low</sub> input loop provides additional protection for a weak source when in USB 100/500-mA mode. This loop monitors the voltage on the USB input pin; and, if it drops to ~4.5 V, Q2 enters its linear range to keep the USB input voltage from dropping any further, as shown in Figure 5. This voltage loop is independent of the input-current-limit loop. This feature adds protection for the USB host in the event that it cannot deliver the load current because of a weak source or failed communication. In Figure 5, IOUT starts with no load and, at ~250 mA, the current limit of the weak source causes the source voltage to fall to 4.5 V, where the  $V_{IN\ Low}$  loop kicks in and the system output voltage drops about 100 mV to the DPPM threshold. The charge current is reduced as the load is increased to maintain the input at 4.5 V. As the load is reduced, the system returns to normal operation.

#### **DPPM** protection of output voltage

The output voltage powering the system will drop if the system load current and the battery charge current exceed the available input current. The input current can

### Figure 5. V<sub>IN\_Low</sub> USB protection with sourcecurrent limit at 250 mA

be restricted by the source, the  $V_{\rm IN\_Low}$  loop, or the inputcurrent-limit setting of the IC. If the output voltage drops to the DPPM threshold, the charge current will be reduced to keep the voltage from further decay. This allows the use of a less expensive adapter because the charging current is reduced during peak loads.

If the system current exceeds the available input current, the output voltage will drop to the battery voltage and enter battery-supplement mode, in which the battery FET turns on and supplements the input current going to the system. This allows use of the battery to supplement large current pulses to the system, which the charger is not capable of supplying. Figures 6 through 8 show the waveforms of the TI bq24072/3/4/5 where the output voltage drops first into DPPM mode and then into battery-supplement mode.

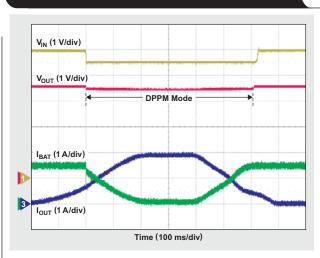

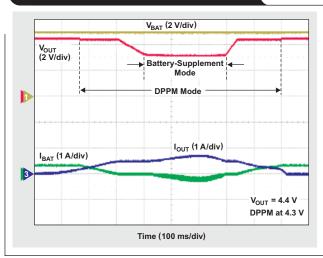

Figure 6 shows the waveforms of the bq24072 with  $V_{OUT}$  initially regulated to about 225 mV above the battery voltage. Upon reaching the input-current limit after the first load step, the IC enters DPPM mode, which reduces the charge current to keep the output voltage from dropping below the DPPM threshold. After the second load step, the system load is greater than the input limit. The output voltage drops to just below the battery voltage, and the battery FET turns on and supplements the input current to the system load. Note that the voltage transitions between modes are very small and are best for applications that are sensitive to voltage changes.

### Figure 6. bq24072 DPPM and battery- supplement modes with $V_{BAT}\approx 3.1~V$

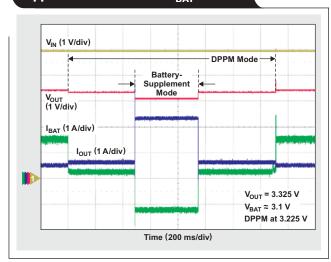

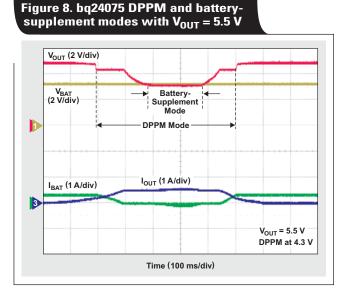

The waveforms of the bq24073/4 in Figure 7 were generated under the same conditions as for the bq24072 in Figure 6, except that the bq24073/4 regulates  $V_{OUT}$  at 4.4 V and the DPPM threshold at 4.3 V. Upon entering battery-supplement mode, the output voltage drops to just below the battery voltage; so the lower the battery voltage is, the larger the drop. For an application sensitive to system voltage drops, the system load should not exceed the available input current in order to stay out of battery-supplement mode. An alternative is to use the bq24072.

The bq24075 waveforms in Figure 8 were generated under the same conditions as for the bq24072 in Figure 6, except that the bq24075 regulates  $V_{OUT}$  at 5.5 V and the DPPM threshold at 4.3 V. The transition between modes is larger and dependent on the input voltage and battery voltage. If the input voltage is less than 5.5 V, then the regulator is switched fully on to deliver what voltage is available.

### Protection from shorting system V<sub>OUT</sub>

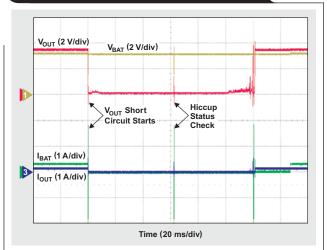

Shorting the  $V_{\rm OUT}$  pin can cause excessive current from the battery or the  $V_{\rm IN}$  power source. Battery short-circuit protection disables the battery FET if the voltage drop from  $V_{\rm BAT}$  to  $V_{\rm OUT}$  is greater than 250 mV for a duration longer than the specified deglitch time. The battery FET is turned on periodically to check whether the short is still present, and this hiccup mode will continue until the short is removed. This prevents damage to the IC and solves reliability issues.

For  $V_{\rm IN}$  protection, the input FET limits the input current to 100 mA when the output voltage is less than 1 V. Once the excessive load is removed, the output will charge above 1 V and start delivering the programmed input current. This feature reduces the power dissipation during the output short, which also improves reliability. Figure 9 shows the waveforms of an output short and the IC's recovery.

Figure 9 shows the waveforms that occur when the bq24072's output is shorted, causing the battery FET and input FET to turn off. The input source supplies about

### Figure 7. bq24073/4 DPPM and batterysupplement modes with V<sub>OUT</sub> = 4.4 V

90 mA to the output via the input control loop; and, approximately every 64 ms, the battery FET is turned on for 250 µs to check whether the short is still present.

### Picking the right charger IC

The bq24072/3/4/5 ICs all charge a single-cell Li-Ion battery properly, but they have various values for the overvoltage-protection (OVP) threshold, the V<sub>OUT</sub> regulation, and the DPPM threshold (see Table 1). Each IC also has an

### Table 1. Differences between bq24072/3/4/5 ICs

| DEVICE  | V <sub>OVP</sub> | V <sub>OUT</sub>          | V <sub>DPPM</sub>            | OPTIONAL<br>FUNCTION |

|---------|------------------|---------------------------|------------------------------|----------------------|

| bq24072 | 6.6 V            | V <sub>BAT</sub> + 225 mV | V <sub>0(REG)</sub> – 100 mV | TD                   |

| bq24073 | 6.6 V            | 4.4 V                     | V <sub>0(REG)</sub> – 100 mV | TD                   |

| bq24074 | 10.5 V           | 4.4 V                     | V <sub>0(REG)</sub> – 100 mV | ITERM                |

| bq24075 | 6.6 V            | 5.5 V                     | 4.3 V                        | SYSOFF               |

### Figure 9. Output short-circuit protection

optional control function such as termination disable (TD), programmable termination current (ITERM), or system off (SYSOFF). The 10.5-V OVP is for a nonregulated 5-V adapter where the unloaded source is above 6.6 V. To minimize power dissipation, during fast charge the optimum input voltage should be between 4.5 and 5.5 V.

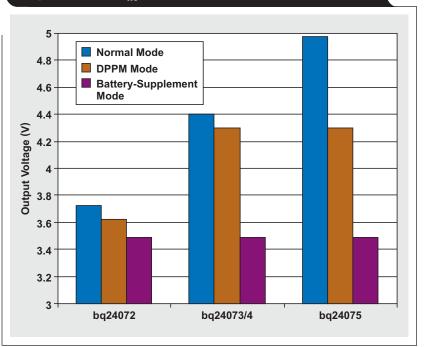

The bar chart in Figure 10 shows graphically how the charger output voltage changes from one operational mode to another for each charger. If the system is sensitive to changes in the output voltage and the peak system load exceeds the input current, the bq24072 minimizes these changes since it regulates the output voltage to within 225 mV of the battery voltage. The bq24073/4 regulates the output voltage to 4.4 V and the DPPM threshold to 4.3 V. Depending on the battery voltage, the voltage drop can be large when the charger enters battery-supplement mode. The bg24075 regulates the output voltage to 5.5 V for inputs greater than 5.5 V and passes through lower voltages. If the charger output current plus the charge current exceed the input current, the output voltage will drop much more than 100 mV, as shown in Figure 10. A further increase in output current may put the device in battery-supplement mode, where another large drop will occur.

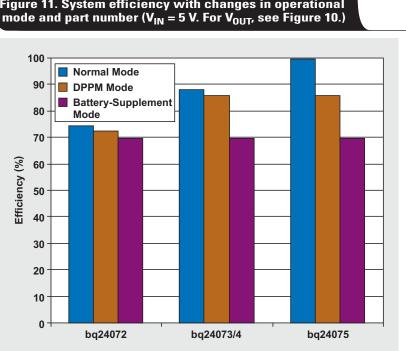

Figure 11 shows the efficiency of the power topology. Efficiency for a linear topology is

$$\eta = \frac{V_{IN} - V_{OUT}}{V_{IN}} \times 100.$$

Each charger mode has an efficiency factor. For the bq24072/3/4/5, the efficiency during battery-supplement mode is the same given the same input voltage and battery voltage.

The bg24072 has the least change in output voltage between modes, but the efficiency drops as the battery discharges. The bg24073/4 is more efficient in normal and DPPM modes but may have a larger internal voltage drop upon entering batterysupplement mode. The bq24075 has high efficiency in normal mode and good efficiency in DPPM mode, but it may have a large change in output voltage after switching from normal to DPPM to batterysupplement mode.

The decision for the designer is whether the charger should be sensitive to system voltage changes, have lower efficiency, or both. If the charger is sensitive to voltage changes, will the system operations cause changes between

### Figure 10. Output voltage with changes in operational mode and part number (V<sub>IN</sub> = 5 V)

Figure 11. System efficiency with changes in operational

the modes with large voltage steps? Because of the low power drain from the adapter or USB source, efficiency is not typically a cost concern, but it can be a heat-dissipation issue in the device.

### Simple, single-cell, integrated Li-lon chargers

For designs where power-path control is not necessary, the TI bq2401x, bq2402x, and bq2406x families of singlecell Li-Ion chargers perform complete charging with all the necessary safety features.

The bg2406x family incorporates many of the same features found in the bq24072/3/4/5 family, but without the power-path management. The bq2406x performs standard three-phase charging-battery conditioning, constant current, and voltage regulation-followed by termination. The safety features include input OVP, a precharge safety timer, a fast-charge safety timer, and IC thermal regulation. The OVP circuit disables the input pass FET if the input voltage exceeds the OVP threshold. This helps to protect against wrong or damaged power sources. The safety timers, once expired, will disable charging. Typically, if the design is done properly, a good battery will exit precharge or reach termination long before the safety timers declare a fault. Typically intended for operation in extremely hot environments where the IC junction temperature reaches 125°C, the thermal-regulation loop reduces the charge level to prevent further heating of the charger IC. Further details on these features can be found in the data sheet.

### Conclusion

An inexpensive discrete charger can be implemented that performs the charging and manages basic power-path connections but does not address any of the safety and reliability issues that may occur. A brief description has been given of the safety features of a simple charger, followed by a more detailed description of DPPM. The bq24072/3/4/5 chargers provide three levels of input-current-limiting protection that can be programmed to protect the specified source. The USB  $V_{IN\_Low}$  loop provides additional protection by detecting weak USB sources and restricting the input current. The output DPPM loop reduces the charging current at the first sign of a drop in the system voltage and enters battery-supplement mode if the system load exceeds what the adapter can handle. This article has also discussed how the IC protects against a system short circuit and then recovers. Finally, for each part number in the bq24072/3/4/5 family, changes in output voltage and efficiency that occur with changes in operational mode were compared.

The bq24072/3/4/5 family of Li-Ion battery chargers is a fully integrated solution that performs Li-Ion charging and DPPM and reduces application size. It solves many issues with power sources by allowing use of less expensive adapters, managing loading, giving priority to the system, increasing reliability, and incorporating many safety features for a lower total system price.

### **Related Web sites**

### power.ti.com

**www.ti.com/sc/device/***partnumber* Replace *partnumber* with bq24010, bq24020, bq24060, bq24072, bq24073, bq24074, or bq24075

# Selecting the right chargemanagement solution

### **By Masoud Beheshti**

Director/Product Line Manager

### Introduction

Today's designers of portable devices have choices of many types of battery chemistries, charger topologies, and charge-management solutions. Selecting the right solution should be simple, but in most cases it is a bit complicated. The designer needs to strike a balance between performance, cost, form factor, and other key requirements. This article provides an overview of several portable-power solutions.

### The three C's of charge management

Charge management is a critical function in any portable design utilizing rechargeable batteries. Sound design techniques ensure that requirements for the following three considerations are met (see Table 1):

- 1. Cell safety—This is not limited to a simple requirement like, for example, meeting the voltage-regulation tolerance of  $\pm 1\%$  during the final phase of charge for a Li-Ion battery. Safety functions also include safety timers, celltemperature monitoring, and a preconditioning mode to safely handle deeply discharged cells.

- 2. *Cell capacity*—Any charge-management solution needs to ensure that the batteries are charged to full capacity in every cycle. Early charge termination results in reduced run time and is not desirable in today's power-hungry portable devices.

- 3. *Cell cycle life*—Adhering to the recommended charge algorithm is an important step towards ensuring that the end user gets the maximum number of charge cycles from each pack. Qualifying each charge with the cell temperature and voltage, preconditioning deeply discharged cells, and avoiding late or improper charge termination are some of the steps necessary for maximizing cycle life.

### Managing battery-chemistry requirements

System designers today have the option to select from a variety of battery chemistries. The selection is typically based on a number of criteria, including energy density; size and form factor; cost; and usage pattern and cycle life. Although there has been a strong trend towards Li-Ion and Li-Pol chemistries in recent years, the NiCd and NiMH chemistries are still viable options for a variety of consumer applications.

### Table 1. The three C's of charge management

| CHARGE FEATURE                                 | CELL<br>SAFETY | CELL<br>CAPACITY      | CELL<br>CYCLE LIFE |

|------------------------------------------------|----------------|-----------------------|--------------------|

| Accurate voltage and/or<br>current regulation  | ~              | ~                     |                    |

| Charge qualification (voltage and temperature) | ~              |                       | ~                  |

| Temperature monitoring                         | ~              | <ul> <li>✓</li> </ul> | ~                  |

| Preconditioning                                | ~              | <b>v</b>              | ~                  |

| End-of-charge termination                      | ~              | <b>v</b>              | ~                  |

| Charge timer                                   | ~              |                       |                    |

| Charge-status reporting                        | ~              | ~                     |                    |

| Detection of battery insertion and removal     | ~              |                       |                    |

| Minimal battery drainage                       |                | <ul> <li>✓</li> </ul> |                    |

| Short-circuit current limit                    | ~              |                       |                    |

| Automatic recharge                             |                | ~                     |                    |

Regardless of the choice of chemistry, it is critical to adhere to the appropriate charge-management techniques for each chemistry. These techniques ensure that batteries are charged to their maximum capacities in every cycle without compromising safety or cycle life.

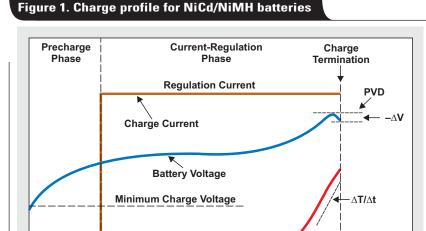

### NiCd/NiMH

Before a fast-charge cycle starts, NiCd and NiMH batteries must be qualified and possibly conditioned. Fast charge is prohibited if the battery voltage or temperature is outside the allowed limits. For safety, any charging of a "hot" battery (typically above 45°C) is suspended until the battery cools to the normal operating-temperature range. To condition a "cold" battery (typically below 10°C) or an overdischarged battery (typically below 1 V per cell), a gentle trickle current is applied.

Fast charge begins when the battery temperature and voltage are valid. NiMH batteries are typically charged with a constant current of 1C or less. Certain NiCd batteries can be charged at rates of up to 4C. Proper charge termination is required to prevent harmful overcharge.

For nickel-based rechargeable batteries, fast-charge termination can be based on either voltage or temperature.

As shown in Figure 1, a typical voltagetermination method is peak-voltage detection (PVD), where fast charging is terminated within a range of 0 to -4 mV per cell of the peak cell voltage. The temperature method monitors the rate of battery temperature rise,  $\Delta T/\Delta t$ , to detect full charge. The typical  $\Delta T/\Delta t$  rate is 1°C/minute.

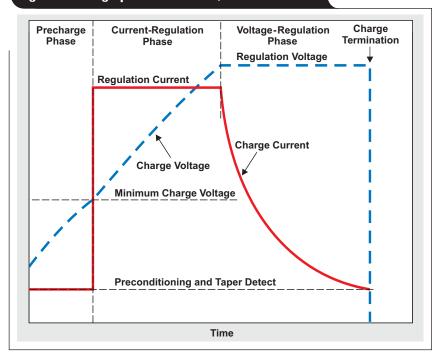

### Li-Ion/Li-Pol

Similar to NiCd and NiMH batteries, Li-Ion and Li-Pol batteries must be qualified and possibly conditioned before fast charge. A qualification and conditioning method similar to the one described earlier is used.

As shown in Figure 2, following qualification and preconditioning, a lithium-based battery is first charged with a current of 1C or less until it reaches its charge-voltage limit. This stage of charge typically replenishes up to 70% of the capacity. The battery is then charged with a constant voltage of typically 4.2 V. To maximize safety and the available capacity, the charge voltage must be regulated to at least  $\pm 1$ %. During this stage of charge, the charging current drawn by the battery tapers down. The charge is typically terminated once the current level falls below 10 to 15% of the initial charging current at a 1C charging rate.

# Linear versus switch-mode charging topology

Linear and switch-mode topologies are commonly used for controlling the charging current and voltage in applications using rechargeable batteries. Each topology provides unique advantages for its intended applications.

The linear topology is well suited for low cell counts and charging currents. It offers the designer several advantages: low implementation cost, design simplicity, and "quiet" operation due to the absence of high-frequency switching. The linear topology also introduces some power dissipation into the system, in this case mostly during the current-regulation phase of the charge cycle. This is a drawback if the designer has no means to manage the thermal issues in the design.

The switch-mode topology is well suited

for higher cell counts and charging currents. Its main advantage is increased efficiency. Unlike linear regulators, the power switch or switches are operated in the saturation region, which substantially reduces the overall losses. The main sources of power loss in a buck converter

**Battery Temperature**

Time

Preconditioning and Taper Detect

### Figure 2. Charge profile for Li-Ion/Li-Pol batteries

include the switching losses (in the power switches) and the DC losses in the filter inductor. Depending on the design parameters, it is not uncommon to see efficiencies of well over 95% in these applications.

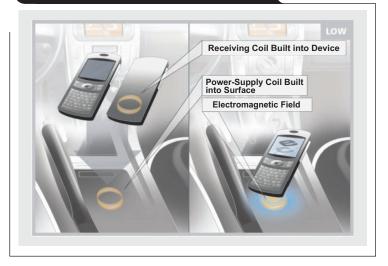

### **Inductive charging**

Inductive (wireless) power has been around for a long time and has found applications in many areas. In the industrial area, for instance, induction heating has provided a practical and efficient way to melt large amounts of metals in a manufacturing environment. In the consumer area, inductive power has been used successfully to charge toothbrushes and other small personal-care products. However, when it comes to charging the new generation of portable appliances such as cellular phones, portable media players, and *Bluetooth*<sup>®</sup> headsets, the use of wireless power is in its infancy.

The wireless chargers commonly used in the consumer market for devices such as toothbrushes are not optimized for efficiency or speed. These chargers "trickle charge" at a low rate, and the form factor is customized to accept only the intended end equipment. However, the demands for portable power are changing; and most consumers now own a multitude of portable devices, each with its own power cable and, in many cases, proprietary connectors. Consumers are beginning to look for the same convenience in charging their portable devices as is offered by wireless data transfer. This concept, although simple, presents a number of barriers for design solution and acceptance:

- Unlike the battery for a toothbrush, batteries for the new portable devices need to be charged at a standard fast-charge rate, reaching 70% of capacity in about an hour. The solution must therefore be very power-efficient.

- The battery for each portable device is a different size and has a different charge rate (i.e., power rating), so the concept of "one size fits all" does not apply. The wireless charger needs to have the intelligence to recognize these variations and adjust itself accordingly.

- Consumer safety is very important, so the wireless charger needs not only to differentiate between a coin and a cell phone but also to make certain that no hazardous situations are created under any operating condition.

- Ultimately, what consumers will pay for is convenience, so the wireless charger needs to be substantially easier to use than the easiest corded charger available.

There are a variety of solutions being developed to address these concerns. A great example is eCoupled<sup>TM</sup> technology developed by Fulton Innovation. This technology includes an inductively coupled power-supply circuit that dynamically seeks resonance, adapting its operation to match the needs of each device it supplies (see Figure 3). By communicating with each device individually in real time, eCoupled technology not only determines power needs but also takes into account the age of a battery or device and its charging life cycles. This supplies the optimal

### Figure 3. Concept of inductively coupled power supply

| Battery Chargers Selection Tool                             | Make Your                                                                                |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Choose the battery chemistry you are interested in          | Select Newton Screens Ier<br>1. Choose the battery<br>chemistry one are<br>interested in |

| Select one of the following (USB) (Comparison) (Comparison) |                                                                                          |

| a. Li-Ion, Li-Pol                                           |                                                                                          |

| b, NMI, NCD<br>c, Lead-Acid                                 |                                                                                          |

|                                                             |                                                                                          |

amount of power to the device and keeps it operating at peak efficiency.

### Selecting the charger

Texas Instruments offers a variety of tools to make the process of selecting the right charger easier for designers. Figure 4 shows the "Battery Chargers Quick Search" tool available at power.ti.com (Scroll down to "Analog eLab<sup>TM</sup> Design Support" to view links under "Design, Simulation, and Selection Tools.")

### Related Web site power.ti.com

power.ti.com

# **Designing with digital isolators**

### **By Thomas Kugelstadt**

Senior Applications Engineer

### Introduction

The purpose of this article is to help engineers use the Texas Instruments (TI) ISO72xx family of digital isolators to design galvanically isolated systems in the shortest time possible. The article explains the basic operating principle of the TI isolator, suggests where to place it within a system design, and recommends guidelines for an electromagneticcompatible (EMC) circuit-board design.

### **Operating principle**

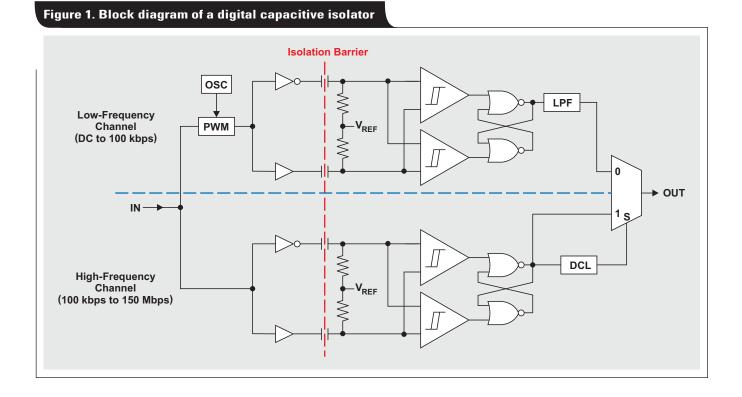

The isolator in Figure 1 is based on a capacitive-isolationbarrier technique. The device consists of two data channels —a high-frequency channel with a bandwidth ranging from 100 kbps up to 150 Mbps, and a low-frequency channel covering the range from 100 kbps down to DC.

In principle, a single-ended input signal entering the high-frequency channel is split into a differential signal via the inverter gate at the input. The subsequent capacitorresistor networks differentiate the signal into transients, which are then converted into differential pulses by two comparators. The comparator outputs drive a NOR-gate flip-flop whose output feeds an output multiplexer. A decision logic (DCL) at the driving output of the flip-flop measures the durations between signal transients. If the duration between two consecutive transients exceeds a certain time limit, as in the case of a low-frequency signal, the DCL forces the output multiplexer to switch from the high- to the low-frequency channel.

Because low-frequency input signals require the internal capacitors to assume prohibitively large values, a pulsewidth modulator (PWM) is used to modulate these signals with the carrier frequency of an internal oscillator (OSC), thus creating a frequency high enough to pass the capacitive barrier. As the input is modulated, a low-pass filter (LPF) is needed to remove the high-frequency carrier from the actual data before it is passed on to the output multiplexer.

### Analog Applications Journal 20 2009

### **High-frequency-channel operation**

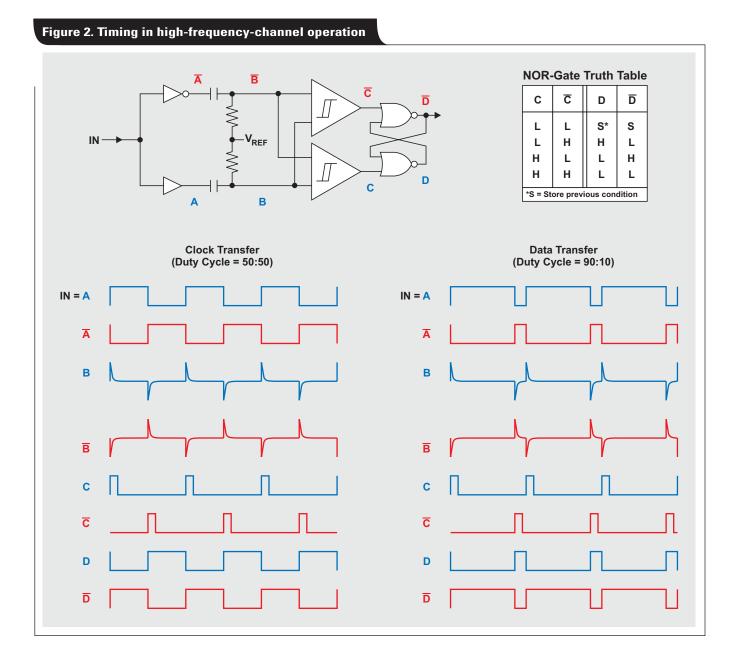

Figure 2 presents the high-frequency channel and the waveforms at specific points of the signal chain. The single-ended input signal is split into the differential signal components, A and  $\overline{A}$ . Each signal component is then differentiated into the transients, B and  $\overline{B}$ . The subsequent comparators compare the differential transients to one another. As long as the positive input of a comparator has a higher potential than its negative input, the comparator output will present a logical high, thus converting an input transient into a short output pulse.

The output pulses set and reset a NOR-gate flip-flop. From the "NOR-Gate Truth Table" in Figure 2 we see that the NOR-gate configuration presents an inverting flip-flop, meaning that a high at input C sets output  $\overline{D}$  to high, and a high at  $\overline{C}$  sets D to high. Because the comparator output pulses are of short duration, there will be times when both outputs are low. During this time the flip-flop stores its previous output condition. Since the signal at  $\overline{D}$  is identical to the input signal in shape and phase,  $\overline{D}$  becomes the output of the high-frequency channel and is connected to the output multiplexer.

While input signals with symmetrical duty cycles cause equidistant pulses at the comparator outputs, asymmetrical signals (shown in the "Data Transfer" timing diagram in Figure 2) move the comparator pulses closer to each other to maintain the shape and phase relationships of the input signal.

### Low-frequency-channel operation

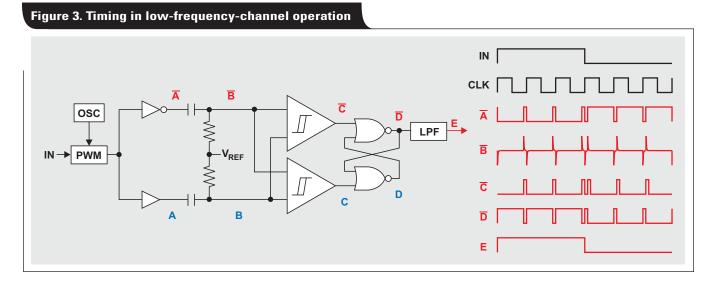

As shown in Figure 3, a PWM modulates slow input signals with a high-frequency carrier such that, at location A, a high-level input yields a 90:10 duty cycle, and a low-level input yields a 10:90 duty cycle. From there on, signal processing is identical to the asymmetrical signal processing in the high-frequency channel. The only exception is that the high-frequency content of  $\overline{D}$ , the low-frequency channel, is filtered by an R-C LPF before being passed on to the output multiplexer, E.

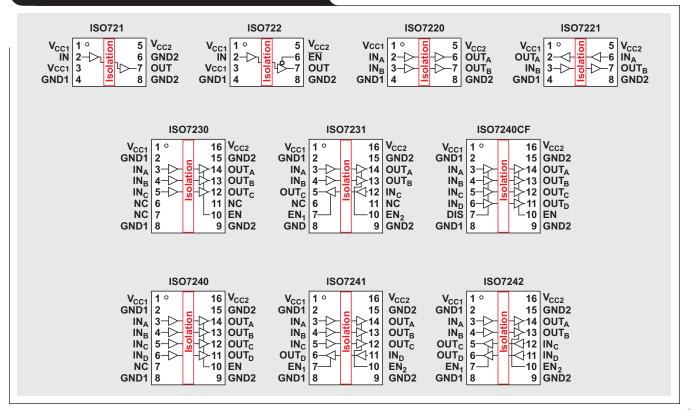

### Isolator technology and requirements

The successful proof of the single isolator's ability to transmit wideband data (from DC to above 150 Mbps) inspired TI to fabricate unidirectional and bidirectional devices in dual-, triple-, and quad-channel versions that accommodate the most common digital interfaces encountered in industrial applications (see Figure 4). All TI digital isolators utilize single-ended, 3-V/5-V CMOS-logic switching technology. Their nominal supply-voltage range is specified

### Figure 4. TI family of stand-alone digital isolators

from 3.3 V to 5 V for both supplies,  $V_{\rm CC1}$  and  $V_{\rm CC2},$  and allows any combination of these values.

It is important for the designer to keep in mind that digital isolators, due to their single-ended design structure, do not conform to any specific interface standard and are intended only for isolating singleended, 3-V/5-V digital signal lines.

Figures 5 to 7 give examples of isolated interfaces for SPI, RS-232, and RS-485 applications. Note that the isolator is always placed between the data controller (i.e., the microcontroller or UART) and a data converter or line transceiver, regardless of the interface type or standard.

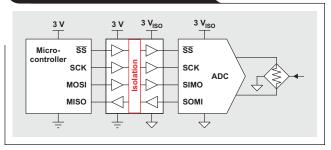

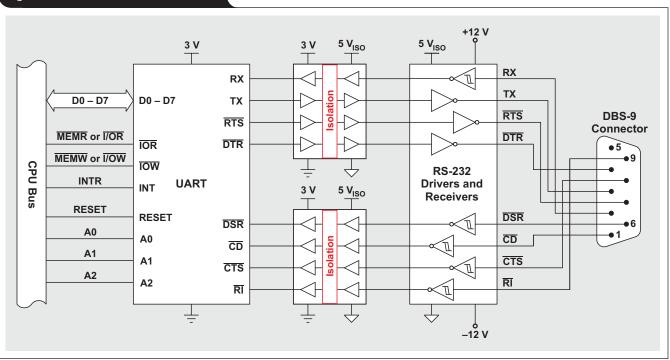

Figure 5 presents the simplest isolator application. Here the entire circuit constitutes a single-ended, low-voltage system in which a digital isolator connects the SPI interface of a controller with the SPI interface of a data converter. The most commonly applied TI isolators in SPI interfaces are ISO7231 and ISO7241, often designated as 3- and 4-channel SPI isolators. The full-blown, isolated RS-232 interface in Figure 6 requires two quad isolators because six control signals are required in addition to the actual data lines, RX and TX. Although the entire system is single-ended, the high-voltage requirements of the symmetrical,  $\pm 13$ -V bus supply make it necessary to galvanically isolate the data link between the UART and the low-voltage side of the bus transceiver.

### Figure 5. Isolated SPI interface

### Figure 6. Isolated RS-232 interface

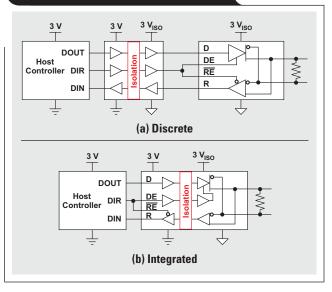

As in the previous example, the isolation of the RS-485 interface in Figure 7a occurs between the controller and the bus transceiver. Despite the entire interface circuit being a low-voltage system, the differential nature of the transmission bus requires prior isolation on the single-ended side. Due to the simplicity of this interface, it was possible to integrate the isolator function into the RS-485 transceiver circuit as shown in Figure 7b, thus providing an application-specific isolator device featuring low cost and a low component count.

To simplify the selection of an appropriate isolator for a specific application, Table 1 provides a comprehensive overview of TI digital isolators. Of the five different speed grades for isolators—A, B, C, CF, and M—all but the M version possess internal low-pass noise filters at the data inputs and are therefore recommended for use in noisy environments. The high-speed version, M, requires external input filtering when used in noisy environments. This is accomplished by connecting a filter capacitor from an

### Figure 7. Isolated RS-485 interface

| ISOLATOR<br>Type        | DEVICE            | SPEED<br>GRADE | INPUT<br>Threshold | MAX.<br>DATA RATE*<br>(Mbps) | MAX.<br>PROP. DELAY*<br>(ns) | MAX. CH/CH<br>OUTPUT SKEW*<br>(ns) | TYPICAL OUTPUT<br>RISE TIME*<br>(ns) |

|-------------------------|-------------------|----------------|--------------------|------------------------------|------------------------------|------------------------------------|--------------------------------------|

| Single                  | IS0721/722        |                | TTL                | 100                          | 24                           | —                                  | 1                                    |

| Single                  | 130721/722        | М              | CMOS               | 150                          | 16                           | —                                  | 1                                    |

|                         |                   | А              |                    | 1                            | 475                          | 15                                 | 1                                    |

| Dual                    | 1007020/7001      | В              | TTL                | 5                            | 70                           | 3                                  | 1                                    |

| Duai                    | IS07220/7221      | С              |                    | 25                           | 42                           | 1                                  | 1                                    |

|                         |                   | М              | CMOS               | 150                          | 16                           | 1                                  | 1                                    |

|                         |                   | А              | TTL                | 1                            | 95                           | 2                                  | 2                                    |

| Triple                  | IS07230/7231      | С              | IIL                | 25                           | 42                           | 2                                  | 2                                    |

|                         |                   | М              | CMOS               | 150                          | 23                           | 1                                  | 2                                    |

| Quad                    | IS07240/7241/7242 | А              | TTL                | 1                            | 95                           | 2                                  | 2                                    |

|                         |                   | С              | IIL                | 25                           | 42                           | 2                                  | 2                                    |

| uuau                    |                   | М              | CMOS               | 150                          | 23                           | 1                                  | 2                                    |

|                         | IS07240           | CF             | TTL                | 25                           | 42                           | 2                                  | 2                                    |

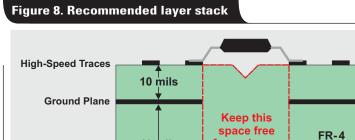

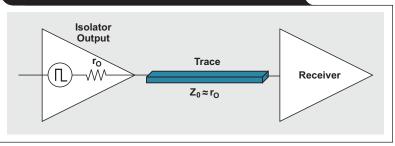

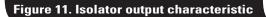

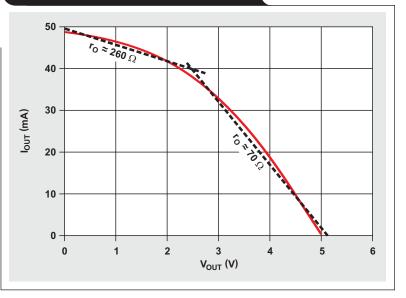

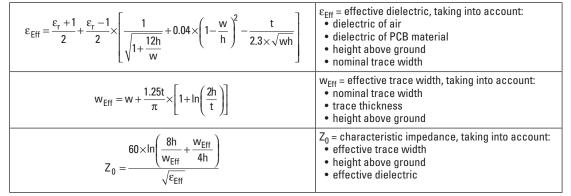

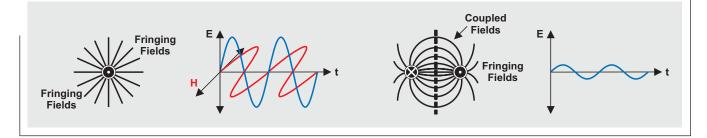

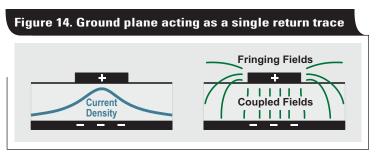

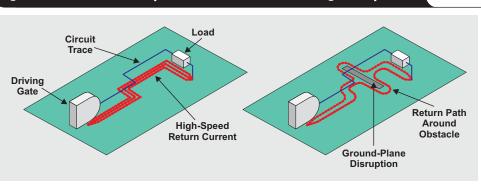

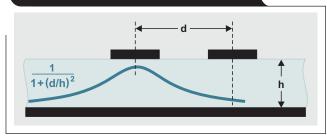

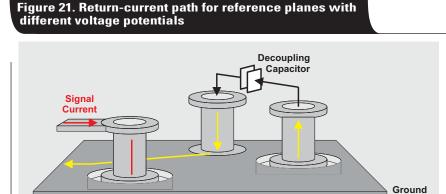

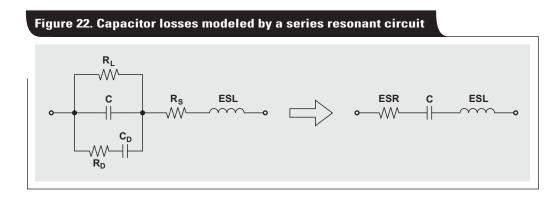

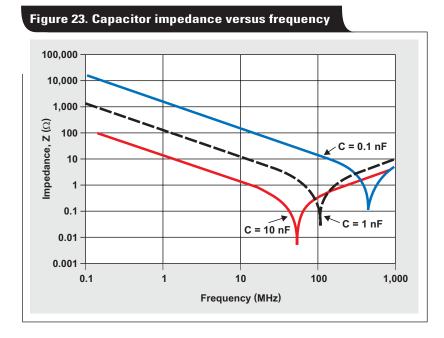

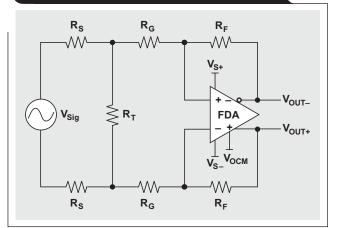

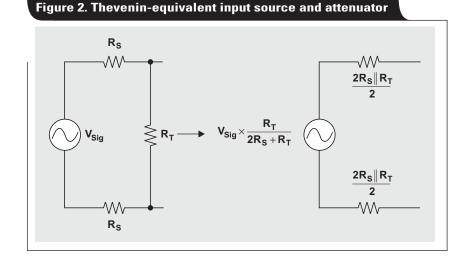

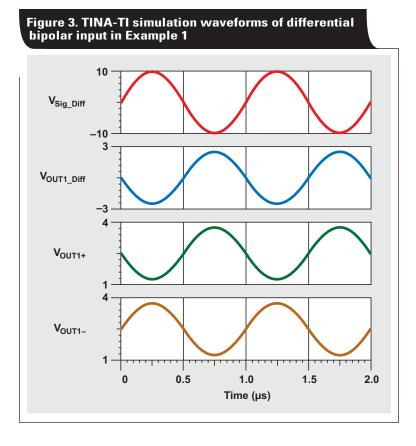

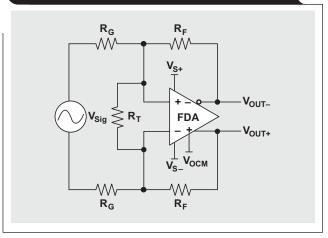

|                         | IS03082           |                | TTL                | 0.2                          | 1.3 (XTR)<br>125 (RCV)       | —                                  | 900 (XTR)<br>1 (RCV)                 |