# How to use isolation to improve ESD, EFT and surge immunity in industrial systems

#### **By Anant Kamath**

Systems Engineer, Isolation, Interface Products

#### Introduction

Industrial equipment is expected to operate reliably in harsh environments. The cables connecting equipment inputs and outputs can pick up voltage and current noise from a variety of disturbances. For example, cables near motors can pick up high-voltage and high-frequency electrical fast transients (EFTs). Lightning strikes (causing surges) can couple inductively to long running cables, or couple indirectly through power supplies. Connectors and exposed parts can be subject to electrostatic discharge (ESD) if they come in contact with a human operator during operation or maintenance. Industrial equipment must withstand these disturbances and continue to function normally.

Achieving good electromagnetic compatibility (EMC) is different for isolated systems when compared to nonisolated systems. This article discusses how to use isolation to improve ESD, EFT and surge immunity. Improvements in performance and reduced system cost are possible through careful design.

#### Voltages and currents during EMC testing: Non-isolated systems

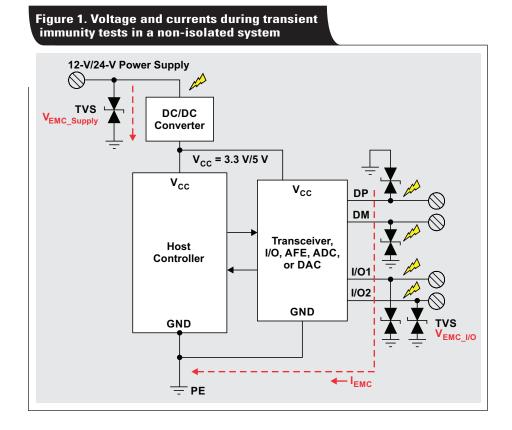

Reference 1 provides details of the voltage and current profiles of noise pulses and timing sequences associated with the International Electrotechnical Commission (IEC) for ESD, EFT and surge tests. Figure 1 shows a block diagram of a non-isolated system, and indicates the voltages and currents that are created due to an ESD, EFT or surge transient. In a non-isolated system, all circuitry, including any transient protection devices, connect to protective earth (PE). Modern transient voltage suppressors (TVSs) are the preferred protection components for high-speed data transmission because of their low capacitance, which enables them to be designed into every node of a multi-node network without requiring a reduction in data rate.

With response times of a few picoseconds and power ratings up to several kilowatts, TVS diodes present the most effective protection against ESD, burst EFT and surge transients. Transient protection devices conduct the

large currents induced during transient events to the PE. You must design transient protection such that the voltages on the supply and I/O pins are clamped below the maximum voltage ratings of the circuits connected to those terminals. For example, a TVS diode that clamps to 50 V for a 1-kV surge transient can protect transceivers and I/O circuits that can tolerate peak voltages up to 50 V. You may require additional components, such as ballasting resistors, to help protect the I/O circuitry if the clamping voltage of the TVS is much higher than the safe operating voltage of the transceiver circuits. Reference 1 discusses protection circuits for non-isolated RS-485 transceivers.

During a transient event on the transceiver and I/O pins, the transient protection devices clamp to a certain clamping voltage, V<sub>C</sub>. This clamping causes a loss of regular signaling on the communication channel, drowned out by the energy of the transient pulse and potentially causing glitches or error pulses in the communication link. The error pulses are at least as wide as the transient-noise pulses (100 ns for ESD and EFT and 100 µs for surge) and repeat according to the test-repetition patterns. In order to meet Criterion A (no performance degradation during the application of noise transients), you must filter out these error pulses with resistor-capacitor filters, digital filters in the host controller, or through error detection and retransmission. However, these methods reduce the throughput of the communication channel, add cost and put an additional computational load on the host controller.

#### Voltages and currents during EMC testing: Isolated systems

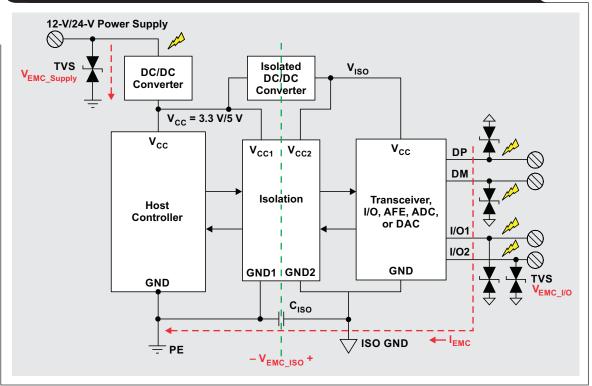

Figure 2 shows a block diagram of an isolated system, and indicates the voltages and currents that are created due to an ESD, EFT or surge event. In this example, the transceivers and other I/O ports are isolated from the host controller using a digital isolator. The host controller is referenced to PE. The interface side (or hot side) of the system, including transient protection devices, is referenced to a "floating" isolated ground (ISO GND). An isolated DC/DC converter generates the power supply for the hot side. Between the ISO GND and the PE is a parasitic capacitor,  $C_{\rm ISO}$ .  $C_{\rm ISO}$  is the sum of the isolation/barrier capacitances of all of the isolation elements used (isolators, optocouplers, transformers) and any capacitance introduced by the printed circuit board.

You can create electrical models of the different transient events using the voltage and current profiles defined in the standards, with the defined output impedances of the generators and clamping circuits. The block diagram in Figure 2 simulates the impact of transient events.

#### Voltage across the isolation barrier

During a transient event on the interface pins, the transient protection devices turn on with a relatively low voltage drop across them. This causes the entire opencircuit voltage of the transient pulse to appear across the isolation barrier. For example, an 8-kV ESD strike on the

interface pins will cause an 8-kV stress on the isolation barrier (between ISO GND and PE).

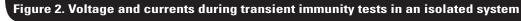

You can reduce the voltage stress across the isolation barrier by using additional safety certified capacitors (extra components) across the barrier, increasing the effective value of  $C_{\rm ISO}$ . Short-duration ESD and EFT pulses are easier to filter than a surge.

Simulation results in Figure 3a show the filtering of an 8-kV ESD strike to less than 5 kV, with  $C_{ISO}$  equal to 100 pF. Figure 3b shows the attenuation of a 4-kV EFT pulse to less than 2 kV, with  $C_{ISO} = 1$  nF.

Only a few signal-isolation technologies available in the market today (Texas Instruments reinforced isolators included) can handle 8-kV ESD and 4-kV EFT events across the barrier. The others would need an additional safety certified capacitor to reduce the barrier stress to acceptable levels. While the obvious disadvantage of an extra safety certified capacitor is an increase in system cost, there are other disadvantages as discussed in the next section.

Surge pulses are wider and thus more difficult to filter with a reasonable  $C_{\rm ISO}$  value. At the same time, most isolation barriers are able to handle the 1-kV to 2-kV surge levels required for industrial systems, thus needing no additional filtering.

References 2 and 3 discuss the insulation specifications and transient voltage tolerance of TI reinforced isolators.

#### **Current through transient protection devices**

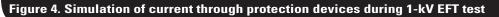

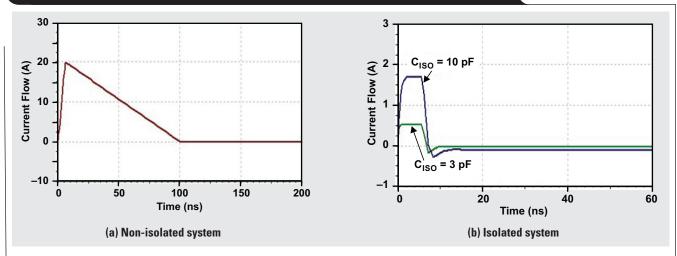

For the isolated system shown in Figure 2, the current loop for a transient event on the interface pin is completed through  $C_{\rm ISO}$ . If you carefully design  $C_{\rm ISO}$  to be low, it can present significant impedance to the transient event and drastically cut down the peak current through the transient protection devices. Slower transients like a surge see a higher impedance. As Figure 4 shows, with  $C_{\rm ISO} = 10$  pF, the peak current through the protection devices in an EFT event drops from 20 A in a non-isolated system to 1.8 A in an isolated system—an attenuation of 10x. The current

duration also reduces more than 10x, from 100 ns to less than 10 ns. Similarly, as Figure 5 shows, the peak current through the protection devices in a surge event drops more than 40x and the duration of the current is 100x smaller.

The reduction in amplitude and pulse width reduces the peak-current and peak-power requirements on external TVS protection, making them smaller and less costly. The peak power for surge events reduces from a few kilowatts to tens of a milliwatt, a very useful reduction. If  $C_{\rm ISO}$  is low enough, and with reasonable on-chip transient protection on the transceivers, you can completely eliminate external transient protection.

#### **Meeting Criterion A for EFT and surge**

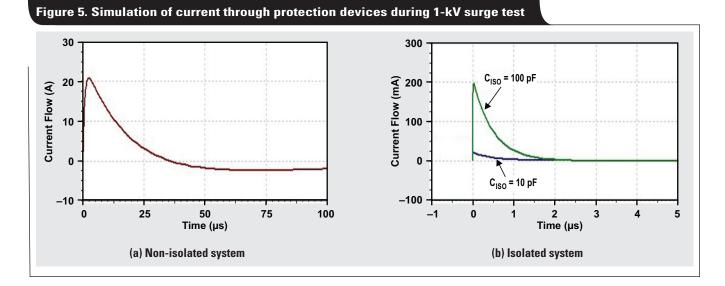

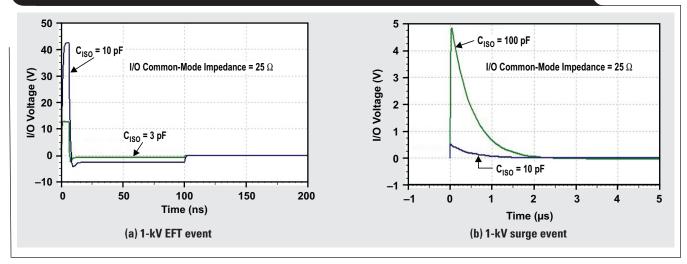

As discussed earlier, in a non-isolated system, the signal on the interface pins is drowned for the entire duration of the transient event: roughly 100 ns for an EFT event and 100 µs for a surge event. You must filter out the subsequent error pulses in the communication channel, resulting in extra cost, latency and reduction in data throughput. In an isolated system, since the current through transient protection devices lasts for a much smaller duration, the error pulses generated are narrower. As Figure 6 shows, the common-mode voltage excursions on a 25- $\Omega$  commonmode impedance transceiver or I/O can last for only 6 ns for an EFT event and 2 µs for a surge event. Such narrow error pulses are filtered more easily, and without much impact on throughput. The voltage excursions are contained to a few volts, which might enable the transceiver to function normally without any filtering at all. Thus, isolation can enable systems to meet Criterion A without trading off throughput or latency.

, Figure 6. Simulation of voltage developed on an I/O with a 25- $\Omega$  common-mode impedance

|             | Non-Isolated System |                                               |                                                        | Isolated System with $C_{ISO} = 10 \text{ pF}$ |                                               |                                                        |

|-------------|---------------------|-----------------------------------------------|--------------------------------------------------------|------------------------------------------------|-----------------------------------------------|--------------------------------------------------------|

| Event       | Peak Current        | Common-Mode<br>Voltage Excursion <sup>1</sup> | Duration of Current-<br>Pulse/Common-Mode<br>Excursion | Peak Current                                   | Common-Mode<br>Voltage Excursion <sup>1</sup> | Duration of Current-<br>Pulse/Common-Mode<br>Excursion |

| EFT: 1 kV   | 20 A                | V <sub>C</sub> <sup>2</sup>                   | 100 ns                                                 | 1.8 A                                          | 44 V                                          | 6 ns                                                   |

| Surge: 1 kV | 20 A                | V <sub>C</sub> <sup>2</sup>                   | 100 µs                                                 | 20 mA                                          | 0.5 V                                         | 2 µs                                                   |

#### Table 1. Reduction of peak current and duration of current pulse through isolation

<sup>1</sup>Transceiver with 25- $\Omega$  common-mode impedance

$^{2}V_{C}$  is the clamping voltage of the external transient protection

Table 1 summarizes the reduction in current peaks and duration of peaks through isolation, reducing or eliminating the need for transient protection. For example, you can reduce the peak power during a surge event from 1.2 kW to 10 mW. The reduction in common-mode excursions during transient events also enables easier compliance with Criterion A.

#### Conclusion

The considerations for achieving good EMC performance in isolated systems and non-isolated systems differ. The open-circuit voltage applied during ESD, EFT and surge tests can appear as voltage stress across the isolation barrier. The isolators used in the system must be capable of handling these high-voltage fast transients.

The current loop for a transient event on the interface pins in an isolated system is completed through the total isolation barrier capacitance. Through careful design, keeping the value of the isolation-barrier capacitance low, you can present significant impedance to the transient event and drastically cut down the peak current passing through transient protection devices, thus eliminating the need for high-power transient protection devices and reducing system cost. Isolation also reduces the duration for which the protection devices clamp the I/O pins by an order of magnitude. This reduces the width of error pulses in the communication channel during EMC tests, and enables systems to meet Criterion A much more easily when compared to non-isolated systems.

#### References

- 1. Thomas Kugelstadt, "Protecting RS-485 Interfaces Against Lethal Electrical Transients," Texas Instruments application note (SLLA292A), March 2011.

- 2. Anant Kamath and Kannan Soundarapandian, "Highvoltage reinforced isolation: Definitions and test methodologies," Texas Instruments white paper (SLYY063), November 2014.

- 3. Sarangan Valavan, "Understanding electromagnetic compliance tests in digital isolators," Texas Instruments white paper (SLYY064), November 2014.

#### **Related Web sites**

Product information: ISOW7841 ISO7741 ISO1212 ISO1211 ISO7821LLS ISO7841

## TI Worldwide Technical Support

## TI Support

Thank you for your business. Find the answer to your support need or get in touch with our support center at

www.ti.com/support

- China: http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp

- Japan: http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp

### Technical support forums

Search through millions of technical questions and answers at TI's E2E™ Community (engineer-to-engineer) at

e2e.ti.com China: http://www.deyisupport.com/ Japan: http://e2e.ti.com/group/jp/

## TI Training

From technology fundamentals to advanced implementation, we offer on-demand and live training to help bring your next-generation designs to life. Get started now at

#### training.ti.com

- China: http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

- Japan: https://training.ti.com/jp

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

A011617

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

© 2017 Texas Instruments Incorporated. All rights reserved.

SLYTxxx

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated