# Application Brief **Replace External Memory for Module Identification With TMP1826 Embedded EEPROM**

## Amit Ashara

Memory in systems plays an important role of storing software code, data, and information required for acquiring data from sensors and initiating proper control to keep process parameters within acceptable bounds. Additionally, the memory is also required for storing temperature sensor calibration information. With the increasing complexity in systems, the design modular (sub-systems) must be made so that system components can be easily upgraded, replaced, or updated. This brings about the challenges of adding memory in the sub-system, that can be used to store necessary information about the characteristics, so that the main controller can query and identify the module and the necessary control parameters. To address these challenges, TI developed the TMP1827 and TMP1826, 1-Wire<sup>®</sup> based temperature sensor with 2048 bits of non-volatile EEPROM which features:

- NIST traceable factory-programmed non-erasable 64-bit identification number for device addressing

- Write operation in block size of 64 bits

- Continuous read mode

- Read with write protection with page size of 256

bits

- Authenticated write protection mode with page size of 256 bits (only available on TMP1827)

## **Simplified Connectivity**

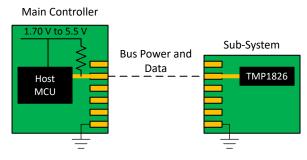

System designers often require that before the subsystem is powered up, the required information is available to the main controller. This requirement results in dedicating a set of pins for the onboard memory of the sub-system to have a dedicated supply and communication bus. Most memory devices require I<sup>2</sup>C or SPIs that have 2 or 3 wires respectively for the communication interface. As Figure 1 shows, the TMP182x devices feature bus-powered, 1-Wire interface which greatly simplifies the backplane connector requirement as only one-pin and PCB trace is required for both powering and communicating with the device.

### Temperature and Humidity Sensing

Figure 1. TMP1826 Backplane Connectivity

#### Identification and Configuration

The 2048 bits of EEPROM on the TMP182x is organized as 8 pages of 256 bits. Each page has 4 blocks of 64 bits each. The basic EEPROM write is done at the block level. Additionally, a page can be protected by changing the page attribute to read-only, applicable on TMP1826 and TMP1827, or authenticated-write that is applicable only on the TMP1827.

As a result, a system designer can now partition the memory to store information such as the board manufacturing date, revision of the sub-system, and so forth, and make the memory read-only to prevent accidental overwrite. On the TMP1827, reprogrammable information such as periodic calibration information, counters, and so forth, can be stored in a page marked with authenticated-write, which allows for regular read, but an update only when the host authenticates the transfer, giving the system an extra level of security. Finally, any page marked as writeread (factory default), can be used as a temporary storage for periodic information.

The availability of non-volatile memory with the previously-mentioned page attributes, provides the system designer greater flexibility and efficiency in partitioning the system memory. A mechanism to store sub-system information is often required for identification and configuration of the sub-system in terms of power sequencing, access sequences, and calibration of other components like analog sensors.

1

# **Memory Scalability**

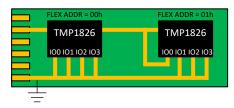

In applications that require larger memory size or distributed memories, the TMP182x provides a unique capability to expand addressing space using the flexible address scheme using the IO. Figure 2 illustrates two TMP1826 connected on the subsystem, one with all IO0-3 strapped to GND (flexible address = 0h) and another with IO0 strapped to SDQ and IO1-3 strapped to GND (flexible address = 1h).

# Figure 2. Scaling Memory Using IO

Together the two devices provide 4096 bits of EEPROM. As shown in Table 1, when accessing the devices, the upper byte of the address space forms the flexible address and lower byte of the address space maps to the address byte LSB. The address byte MSB remains 00h for all access. Due to the 2.5 mm × 2.5 mm NGR package, multiple TMP182x devices can be placed without taking up area on the board, and scalability is easily achieved in software without having to develop software to qualify a new device, as up to 64 devices can be strung together on the same bus, if necessary.

| Address<br>Space | Flex Address | Address Byte<br>MSB | Address Byte<br>(LSB) |

|------------------|--------------|---------------------|-----------------------|

| 0000h - 00FFh    | 00h          | 00h                 | 00h - FFh             |

| 0100h - 01FFh    | 01h          | 00h                 | 00h - FFh             |

## Summary

The high-accuracy TMP1826 and TMP1827 temperature sensors with integrated 2048 bits of EEPROM and multilevel memory protection provides modular applications with the capability to identify and configure onboard sensors and devices, with the right level of scalability. The unique interface and memory scaling features of the TMP182x family of devices, facilitates ease of redesign, mixing and matching memory devices with and without authentication, an increase in memory size or distributed memories, and also eliminates the need for unnecessary system changes for manufacturability and fast time-to-market.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated