# AN-643 EMI/RFI Board Design

### ABSTRACT

The control and minimization of Electro-Magnetic Interference (EMI) is a technology that is, out of necessity, growing rapidly. EMI will be defined shortly but, for now, you might be more familiar with the terms Radio Noise, Electrical Noise, or Radio Frequency Interference (RFI). The technology's explorations include a wide frequency spectrum, from dc to 40 GHz. It also deals with susceptibility to EMI as well as the emissions of EMI by equipment or components. Emission corresponds to that potential EMI which comes out of a piece of equipment or component. Susceptibility, on the other hand, is that which couples from the outside to the inside.

|    | Contents                                      |    |  |  |

|----|-----------------------------------------------|----|--|--|

| 1  | INTRODUCTION                                  | 3  |  |  |

| 2  | DESCRIPTION OF NOISE                          | 3  |  |  |

|    | 2.1 ElectroMagnetic Interference              | 3  |  |  |

|    | 2.2 ElectroMagnetic Compatibility             | 4  |  |  |

|    | 2.3 Inter-System EMI                          | 4  |  |  |

|    | 2.4 Coupling Paths                            | 5  |  |  |

|    | 2.5 Conducted Interference                    | 5  |  |  |

|    | 2.6 Radiated Interference                     | 6  |  |  |

| 3  | NOISE SOURCES                                 | 7  |  |  |

| 4  | Cables and Connectors                         | 7  |  |  |

| 5  | Components                                    | 8  |  |  |

| 6  | Power Supply Noise                            | 8  |  |  |

| 7  | High-Speed CMOS Logic Switching               | 11 |  |  |

| 8  | Signal Crosstalk                              | 12 |  |  |

| 9  | Signal Interconnects                          | 13 |  |  |

| 10 | Ground Bounce                                 |    |  |  |

| 11 | NOISE SUPPRESSION TECHNIQUES                  | 14 |  |  |

| 12 | Intra-System EMI-Control Techniques           |    |  |  |

|    | 12.1 Shielding                                | 15 |  |  |

|    | 12.2 Filtering                                |    |  |  |

|    | 12.3 Wiring                                   |    |  |  |

|    | 12.4 Inter-System EMI Control Techniques      |    |  |  |

| 13 | DESIGN GUIDELINES                             |    |  |  |

| 14 | Logic Selection                               |    |  |  |

| 15 | Component Layout                              |    |  |  |

| 16 | Power Supply Bussing                          |    |  |  |

| 17 | Decoupling                                    |    |  |  |

| 18 | Proper Signal Trace Layout                    |    |  |  |

| 19 | Ground Bounce                                 | -  |  |  |

| 20 | Components                                    |    |  |  |

| 21 | Cables and Connectors                         |    |  |  |

| 22 | Special Considerations with Development Tools |    |  |  |

| 23 | NOISE MEASUREMENT                             |    |  |  |

| 24 | Environment                                   |    |  |  |

| 25 | Instrumentation                               | 29 |  |  |

All trademarks are the property of their respective owners.

# TEXAS INSTRUMENTS

| www.ti.com |

|------------|

|            |

| 26 | Cost       | 29 |

|----|------------|----|

| 27 | SUMMARY    | 30 |

| 28 | REFERENCES | 30 |

### List of Figures

| 1  | ElectroMagnetic Interference Situation                                                                                              | 4  |

|----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | Intra-System EMI Manifestations                                                                                                     | 4  |

| 3  | Simple Circuit Consisting of a Signal Source, $V_{\scriptscriptstyle S}$ , and a Load, $R_{\scriptscriptstyle L}$                   | 5  |

| 4  | Differential-Mode Interference                                                                                                      | 5  |

| 5  | Common-Mode Interference                                                                                                            | 6  |

| 6  | Field-to-Cable Coupling                                                                                                             | 6  |

| 7  | Cable-to-Cable Coupling                                                                                                             | 7  |

| 8  | Common-Mode Impedance Coupling                                                                                                      | 7  |

| 9  | Cables and Connectors                                                                                                               | 8  |

| 10 | Diode Recovery Periods and Spikes                                                                                                   | 8  |

| 11 |                                                                                                                                     | 9  |

| 12 | Switching Transients                                                                                                                | 9  |

| 13 | Switching Transients When the Load Capacitance, $C_{\scriptscriptstyle L}$ , is 15 pF                                               | 9  |

| 14 | Switching Transients When the Load Capacitance, $C_{\scriptscriptstyle L}$ , is 50 pF                                               |    |

| 15 | Switching Transients When the Load Capacitance, $C_{\scriptscriptstyle L}$ , is 100 pF                                              | 10 |

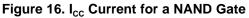

| 16 |                                                                                                                                     | 10 |

| 17 | Top Trace Shows Noise Induced on the High Logic Level Signal and the Bottom Trace Shows Noise Induced on the Low Logic Level Signal | 11 |

| 18 | Illustrates How Noise Affects a 74HC74's Clock Input                                                                                |    |

| 19 | Crosstalk.                                                                                                                          |    |

| 20 |                                                                                                                                     | 14 |

| 21 |                                                                                                                                     | 15 |

| 22 | -                                                                                                                                   | 16 |

| 23 | Board Layout                                                                                                                        | -  |

| 24 |                                                                                                                                     |    |

| 25 |                                                                                                                                     |    |

| 26 |                                                                                                                                     |    |

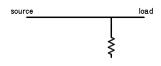

| 27 | Series Termination                                                                                                                  |    |

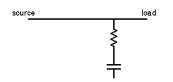

| 28 | Parallel Termination                                                                                                                |    |

| 29 | AC Parallel Termination                                                                                                             |    |

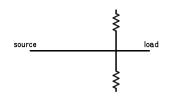

| 30 | Thevenin Termination                                                                                                                |    |

| 31 | Connectors                                                                                                                          |    |

| 32 | Alternating Signal Returns Minimizes Radiation                                                                                      |    |

| 33 | Single Signal Return Maximizes Radiation                                                                                            |    |

|    |                                                                                                                                     |    |

### List of Tables

| 1 | Logic Family Comparisions                   | 11 |

|---|---------------------------------------------|----|

| 2 |                                             | 16 |

| 3 | Electromagnetic Interference Coupling Paths | 18 |

| 4 |                                             | 22 |

### 1 INTRODUCTION

The control and minimization of Electro-Magnetic Interference (EMI) is a technology that is, out of necessity, growing rapidly. EMI will be defined shortly but, for now, you might be more familiar with the terms Radio Noise, Electrical Noise, or Radio Frequency Interference (RFI). The technology's explorations include a wide frequency spectrum, from dc to 40 GHz. It also deals with susceptibility to EMI as well as the emissions of EMI by equipment or components. Emission corresponds to that potential EMI which comes out of a piece of equipment or component. Susceptibility, on the other hand, is that which couples from the outside to the inside.

In HPC designs to date, we have looked at noise situations ranging from 2 MHz to 102 MHz. EMI, in some cases, can affect radio reception, TV reception, accuracy of navigation equipment, etc. In severe cases, EMI might even affect medical equipment, radar equipment, and automotive systems.

This Application Note will define ElectroMagnetic Interference and describe how it relates to the performance of a system. We will look at examples of Inter-system noise and Intra-system noise and present techniques that can be used to ensure ElectroMagnetic Compatibility throughout a system and between systems.

We will investigate and study the sources of noise between systems through wire-harness and backplane cables and connectors. Active circuit components can be contributors of noise and be susceptible to it. The fast switching times of CMOS devices fabricated in today's technology can cause incredible noise in a system. This noise typically is made up of crosstalk, power supply spiking, transient noise, and ground bounce.

The minimization and suppression of EMI can be obtained by utilizing proper control techniques. Intrasystem noise, noise within a single module, sometimes can be controlled with methods such as filtering, shielding, careful selection of components, and following good wiring and grounding procedures. Controlling noise between systems, Inter-system noise, uses subtler techniques such as frequency management and time management, etc.

Appropriate time and resources should be spent during the design of a system or systems to insure that no problems will be encountered due to effects of EMI. Design guidelines will be presented that can be used to increase ElectroMagnetic Compatibility between systems by reducing the effects of noise between them. Above all, don't forget that the development tools used are also systems and are important to consider in your planning.

A brief look will be taken at the environment and tools required for different levels of noise testing. Relative risk-costs between preparing for EMC or excluding EMI concerns from the project will be listed.

# 2 DESCRIPTION OF NOISE

# 2.1 ElectroMagnetic Interference

EMI is a form of electrical-noise pollution. Think of the time when an electric drill or some other power tool jammed a nearby radio with buzzing or crackling noises. Sometimes it got so bad that it prevented you from listening to the radio while the tool was in use. Or the ignition of an automobile idling outside your house caused interference to your TV picture making lines across the screen or even losing sync altogether making the picture flip. These examples are quite annoying but not catastrophic.

More serious, how about a sudden loss in telephone communication caused by electrical interference or noise while you are negotiating an important business deal? Now EMI can be economically damaging.

The results of EMI incidences can be even farther reaching than these examples. Aircraft navigation errors resulting from EMI or interruption of air traffic controller service and maybe even computer memory loss due to noise could cause two aircraft to collide resulting in the loss of lives and property.

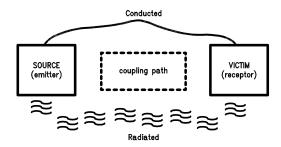

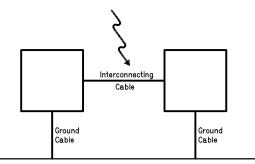

These were just a few examples to help you identify the results of EMI in a familiar context. To help understand an ElectroMagnetic Interference situation, the problem can be divided into three categories. They are the source, the victim, and the coupling path. Secondary categories involve the coupling path itself. It the source and victim are separated by space with no hard wire connection, then the coupling path is a radiated path and we are dealing with radiated noise. If the source and victim are connected together through wires, cables, or connectors, then the coupling path is a conducted path and we are dealing with conducted noise. Incidentally, both types of noise can exist at the same time.

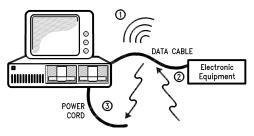

Figure 1. ElectroMagnetic Interference Situation

# 2.2 ElectroMagnetic Compatibility

If you think about the examples given, one can understand that EMI or electrical noise is of national concern. The Government and certain industry bodies have issued specifications with which all electrical, electromechanical, and electronic equipment must comply. These specifications and limitations are an attempt to ensure that proper EMC techniques are followed by manufactures during the design and fabrication of their products. When these techniques are properly applied, the product can then operate and perform with other equipment in a common environment such that no degradation of performance exists due to internally or externally conducted or radiated electromagnetic emissions. This is defined as ElectroMagnetic Compatibility or EMC.

# 2.3 Inter-System EMI

For the purpose of this Application Note, when the source of noise is a module, board, or system and the victim is a different and separate module, board, or system under the control of a different user, that is considered to be an inter-system interference situation. Examples of inter-system interference situations could be a Personal Computer interfereing with the operation of a TV or an anti-lock brake module in a car causing interference in the radio. This type of interference is more difficult to contain because, as mentioned earlier, the systems are generally not under the control of a single user. However, design methods and control techniques used to contain the intra-system form of EMI, which are almost always under the control of a single user, will inherently help reduce the inter-system noise.

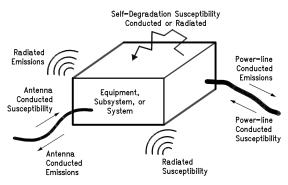

Figure 2. Intra-System EMI Manifestations

This Application Note will address problems and solutions in the area of intra-system noise. Intra-system interference situations are when the sources, victims, and coupling paths are entirely within one system or module or PC board. Systems may provide emissions that are conducted out power lines or be susceptible to emissions conducted in through them. Systems may radiate emissions through space as well as be susceptible to radiated noise. Noise conducted out antenna leads turns into radiated noise. By the same token, radiated noise picked up by the antenna is turned into conducted noise within the system. A perfect example is ground loops on a printed circuit board. These loops make excellent antennas. The system itself is capable of degrading performance due to its own internal generation of conducted and radiated noise and its susceptibility to it.

Some results of EMI within a system: Noise on power line causing false triggering of logic circuits, rapidly changing signals causing "glitches" on adjacent steady state signal lines (crosstalk) causing erratic operation, mutiple simultaneously switching logic outputs propagating ground bounce noise throughout system, etc.

# 2.4 Coupling Paths

The modes of coupling an emitter source to a receptor victim can become very complicated. Remember, each EMI situation can be classified into two categories of coupling, conducted and radiated. Coupling can also result from a combination of paths. Noise can be conducted from an emitter to a point of radiation at the source antenna, then picked up at the receptor antenna by induction, and re-conducted to the victim. A further complication that multiple coupling paths presents is that it makes it difficult to determine if eliminating a suspected path has actually done any good. If two or more paths contribute equally to the problem, eliminating only one path may provide little apparent improvement.

# 2.5 Conducted Interference

In order to discuss the various ways in which EMI can couple from one system to another, it is necessary to define a few terms. When dealing with conducted interference, there are two varieties that we are concerned with. The first variety is differential-mode interference. That is an interference signal that appears between the input terminals of a circuit. The other variety of conducted interference is called common-mode interference. A common-mode interference signal appears between each input terminal and a third point; that third point is called the common-mode reference. That reference may be the equipment chassis, an earth ground, or some other point.

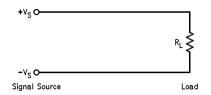

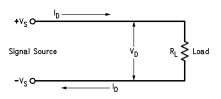

Let's look at each type of interference individually. In Figure 3 we show a simple circuit consisting of a signal source,  $V_s$ , and a load,  $R_L$ . In Figure 4 we show what happens when differential-mode interference is introduced into the circuit by an outside source. As is shown, an interference voltage,  $V_D$ , appears between the two input terminals, and an interference current,  $I_D$ , flows in the circuit. The result is noise at the load. If, for instance, the load is a logic gate in a computer, and the amplitude of  $V_D$  is sufficiently high, it is possible for the gate to incorrectly change states.

Figure 3. Simple Circuit Consisting of a Signal Source,  $V_s$ , and a Load,  $R_L$

Figure 4. Differential-Mode Interference

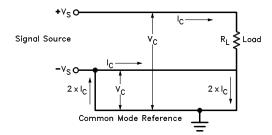

Figure 5 shows what happens when a ground loop is added to our circuit. Ground loops, which are undesirable current paths through a grounded body (such as a chassis), are usually caused by poor design or by the failure of some component. In the presence of an interference source, common-mode currents,  $I_c$ , and a common-mode voltage,  $V_c$ , can develop, with the ground loop acting as the common-mode reference. The common-mode current flows on both input lines, and has the same instantaneous polarity and direction (the current and voltage are in phase), and returns through the common-mode reference. The common-mode voltage between each input and the common-mode reference is identical.

Figure 5. Common-Mode Interference

Figure 6. Field-to-Cable Coupling

### 2.6 Radiated Interference

Radiated coupling itself can take place in one of several ways. Some of those include field-to-cable coupling, cable-to-cable coupling, and common-mode impedance coupling. Let's look at those types of coupling one at a time.

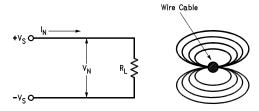

The principle behind field-to-cable coupling is the same as that behind the receiving antenna. That is, when a conductor is placed in a time-varying electromagnetic field, a current is induced in that conductor. That is shown in Figure 6. In this figure, we see a signal source,  $V_s$ , driving a load,  $R_L$ . Nearby there is a current carrying wire (or other conductor). Surrounding the wire is an electromagnetic field induced by the current flowing in the wire. The circuit acts like a loop antenna in the presence of this field. As such, an interference current,  $I_N$ , and an interference voltage,  $V_N$ , are induced in the circuit. The magnitude of the induced interference signal is roughly proportional to the frequency of the incoming field, the size of the loop, and the total impedance of the loop.

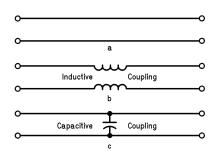

Cable-to-cable coupling occurs when two wires or cables are run close to one another. Figure 7 shows how cable-to-cable coupling works. Figure 7*a* shows two lengths of cable (or other conductors) that are running side-by-side. Because any two conducting bodies have capacitance between them, called stray capacitance, a time-varying signal in one wire can couple via that capacitance into the other wire. That is referred to as capacitive coupling. This stray capacitance, as shown in Figure 7*c* makes the two cables behave as if there were a coupling capacitor between them. Another mechanism of cable-to-cable coupling is mutual inductance. Any wire carrying a time-varying current will develop a magnetic field around it. If a second conductor. That type of coupling is called inductive coupling. Mutual inductance, as shown in Figure 7*b*, makes the cables behave as if a poorly wound transformer were connected between them. In cable-to-cable coupling, either or both of those mechanisms may be responsible for the existance of an interference condition. Though there is no physical connection between the two cables, the properties we have just described make it possible for the signal on one cable to be coupled to the other.

Figure 7. Cable-to-Cable Coupling

Either or both of the above-mentioned properties cause the cables to be electromagnetically coupled such that a time-varying signal present on one will cause a portion of that signal to appear on the other. The "efficiency" of the coupling increases with frequency and inversely with the distance between the two cables. One example of cable-to-cable coupling is telephone "crosstalk", in which several phone conversations can be overheard at once. The term crosstalk is now commonly used to describe all types of cable-to-cable coupling.

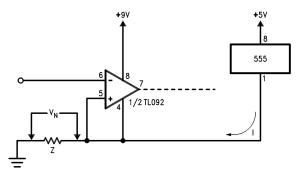

Common-mode impedance coupling occurs when two circuits share a common bus or wire. In Figure 8 we show a circuit that is susceptible to that type of coupling. In that figure a TL092 op-amp and a 555 timer share a common return or ground. Since any conductor (including a printed circuit board trace) is not ideal, that ground will have a non-zero impedance, Z. Because of that, the current, I, from pin 1 of the 555 will cause a noise voltage,  $V_N$ , to develop; that voltage is equal to I × Z. That noise voltage will appear in series with the input to the op-amp. If that voltage is of sufficient amplitude, a noise condition will result.

While not all inclusive, these coupling paths account for, perhaps, 98% of all intra-system EMI situations.

Figure 8. Common-Mode Impedance Coupling

# 3 NOISE SOURCES

In this Application Note, we will look at sources of EMI which involve components that may conduct or radiate electromagnetic energy. These sources, component emitters, are different from the equipment and subsystems we have been talking about. Component emitters are sources of EMI which emanate from a single element rather than a combination of components such as was previously described. Actually, these component emitters require energy and connecting wires from other sources to function. Therefore, they are not true sources of EMI, but are EMI Transducers. They convert electrical energy to electrical noise.

# 4 Cables and Connectors

The three main concerns regarding the EMI role of cables are conceptualized in Figure 9. They act as (1) radiated emission antennas, (2) radiated susceptibility antennas, and (3) cable-to-cable or crosstalk couplers. Usually, whatever is done to harden a cable against radiated emission will also work in reverse for controlling EMI radiated susceptibility. The reason for the word usually, is that when differential-mode radiated emission or susceptibility is the failure mode, twisting leads and shielding cables reduces EMI. If the failure mechanism is due to common-mode currents circulating in the cable, twisting leads has

Components

www.ti.com

essentially no effect on the relationship between each conductor and the common-mode reference. Also cable shields may help or aggravate EMI depending upon the value of the transfer impedance of the cable shield. Transfer impedance is a figure of merit of the quality of cable shield performance defined as the ratio of coupled voltage to surface current in ohms/meter. A good cable shield will have a low transfer impedance. The effectiveness of the shield also depends on whether or not the shield is terminated and, if so, how it is terminated.

**Figure 9. Cables and Connectors**

Connectors usually are needed to terminate cables. When no cable shields or connector filters or absorbers are used, connectors play essentially no role in controlling EMI. The influence of connector types, however, can play a major role in the control of EMI above a few MHz. This applies especially when connectors must terminate a cable shield and/or contain lossy ferrites or filter-pins.

Connectors and cables should be viewed as a system to cost-effectively control EMI rather than to consider the role of each separately, even though each offers specific interference control opportunities.

# 5 Components

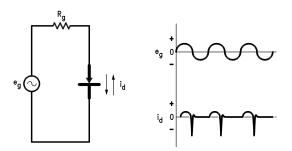

Under conditions of forward bias, a semiconductor stores a certain amount of charge in the depletion region. If the diode is then reverse-biased, it conducts heavily in the reverse direction until all of the stored charge has been removed as shown in Figure 10. The duration, amplitude, and configuration of the recovery-time pulse (also called switching time or period) is a function of the diode characteristics and circuit parameters. These current spikes generate a broad spectrum of conducted transient emissions. Diodes with mechanical imperfections may generate noise when physically agitated. Such diodes may not cause trouble if used in a vibration-free environment.

Figure 10. Diode Recovery Periods and Spikes

# 6 Power Supply Noise

Power-supply spiking is perhaps the most important contributor to system noise. When any element switches logic states, it generates a current spike that produces a voltage transient. It these transients become too large, they can cause logic errors because the supply voltage drop upsets internal logic, or because a supply spike on one circuit's output feeds an extraneous noise voltage into the next device's input.

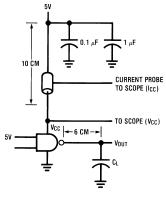

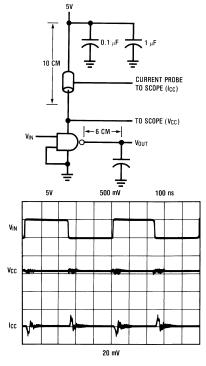

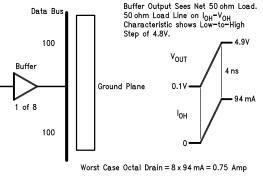

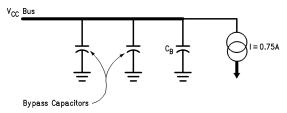

With CMOS logic in its quiescent state, essentially no current flows between  $V_{CC}$  and ground. But when an internal gate or an output buffer switches state, a momentary current flows from  $V_{CC}$  to ground. The switching transient caused by an unloaded output changing state typically equals 20 mA peak. Using the circuit shown in Figure 11, you can measure and display these switching transients under different load conditions.

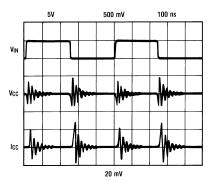

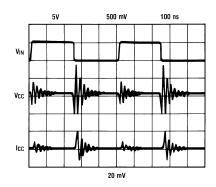

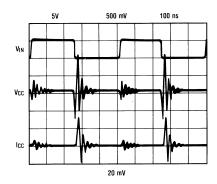

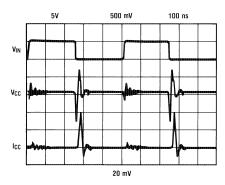

Figure 12 shows the current and voltage spikes resulting from switching a single unloaded ( $C_L = 0$  in Figure 11) NAND gate. These current spikes, seen at the switching edges of the signal on V<sub>IN</sub>, increase when the output is loaded. Figure 13, Figure 14, and Figure 15 show the switching transients when the load capacitance,  $C_L$ , is 15 pF, 50 pF, and 100 pF, respectively. The large amount of ringing results from the test circuit's transmission line effects. This ringing occurs partly because the CMOS gate switches from a very high impedance to a very low one and back again. Even for medium-size loads, load capacitance current becomes a major current contributor.

Figure 12. Switching Transients

Figure 13. Switching Transients When the Load Capacitance,  $C_L$ , is 15 pF

Figure 14. Switching Transients When the Load Capacitance,  $C_L$ , is 50 pF

Figure 15. Switching Transients When the Load Capacitance,  $C_L$ , is 100 pF

Although internal logic generates current spikes when switching, the bulk of a spike's current comes from output circuit transitions. Figure 16 shows the  $I_{cc}$  current for a NAND gate, as shown in the test circuit, with one input switching and the other at ground resulting in no output transitions. Note the very small power-supply glitches provoked by the input-circuit transitions.

# 7 High-Speed CMOS Logic Switching

The magnitude of noise which can be tolerated in a system relates directly to the worst case noise immunity specified for the logic family. Noise immunity can be described as a device's ability to prevent noise on its input from being transferred to its output. It is the difference between the worst case output levels ( $V_{OH}$  and  $V_{OL}$ ) of the driving circuit and the worst case input voltage requirements ( $V_{IH}$  and  $V_{IL}$ , respectively) of the receiving circuit.

Using Table 1 as a guide, it can be seen that for TTL (LS or ALS) devices the worst case noise immunity is typically 700 mV for the high logic level and 300 mV for the low logic level. For HCMOS devices the worst case noise immunity is typically 1.75V for high logic levels and 800 mV for low logic levels. AC high speed CMOS logic families have noise immunity of 1.75V for high logic levels and 1.25V for low logic levels. ACT CMOS logic families have noise immunity of 2.9V for high logic levels and 700 mV for low logic levels.

| Characteristic | Symbol                | LS/ALS TTL | HCMOS                | AC                   | ACT                  |

|----------------|-----------------------|------------|----------------------|----------------------|----------------------|

| Input Voltage  | V <sub>IH</sub> (Min) | 2.0V       | 3.15V                | 3.15V                | 2.0V                 |

| (Limits)       | V <sub>IL</sub> (Max) | 0.8V       | 0.9V                 | 1.35V                | 0.8V                 |

| Output Voltage | V <sub>OH</sub> (Min) | 2.7V       | V <sub>cc</sub> -0.1 | V <sub>cc</sub> -0.1 | V <sub>cc</sub> -0.1 |

| (Limits)       | V <sub>OL</sub> (Max) | 0.5V       | 0.1V                 | 0.1V                 | 0.1V                 |

# **Table 1. Logic Family Comparisions**

To illustrate noise margin and immunity, Figure 17 shows the output that results when you apply several types of simulated noise to a 74HC00's input. Typically, even 2V or more input noise produces little change in the output. The top trace shows noise induced on the high logic level signal and the bottom trace shows noise induced on the low logic level signal.

### Figure 17. Top Trace Shows Noise Induced on the High Logic Level Signal and the Bottom Trace Shows Noise Induced on the Low Logic Level Signal

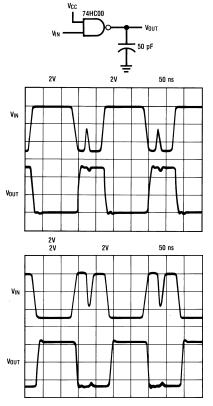

Figure 18 shows how noise affects a 74HC74's clock input. Again, no logic errors occur with 2V or more of noise on the clock input.

When using high speed CMOS, even with its greater noise immunity, crosstalk, induced supply noise and noise transients become factors. Higher speeds allow the device to respond more quickly to externally induced noise transients and accentuate the parasitic interconnection inductances and capacitances that increase self-induced noise and crosstalk.

Figure 18. Illustrates How Noise Affects a 74HC74's Clock Input

# 8 Signal Crosstalk

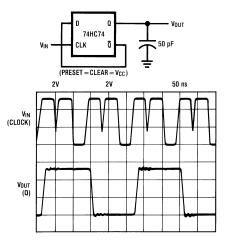

The problem of crosstalk and how to deal with it is becoming more important as system performance and board densities increase. Our discussion on cable-to-cable coupling described crosstalk as appearing due to the distributed capacitive coupling and the distributed inductive coupling between two signal lines. When crosstalk is measured on an undriven sense line next to a driven line (both terminated at their characteristic impedances), the near end crosstalk and the far end crosstalk have quite distinct features, as shown in Figure 19. It should be noted that the near end component reduces to zero at the far end and vice versa. At any point in between, the crosstalk is a fractional sum of the near and far end crosstalk waveforms as shown in the figure. It also can be noted that the far end crosstalk can have either polarity whereas the near end crosstalk always has the same polarity as the signal causing it.

The amplitude of the noise generated on the undriven sense line is directly related to the edge rates of the signal on the driven line. The amplitude is also directly related to the proximity of the two lines. This is factored into the coupling constants  $K_{NE}$  and  $K_{FE}$  by terms that include the distributed capacitance per unit length, the distributed inductance per unit length, and the length of the line. The lead-to-lead capacitance and mutual inductance thus created causes "noise" voltages to appear when adjacent signal paths switch.

Figure 19. Crosstalk

Several useful observations that apply to a general case can then be made:

- The crosstalk always scales with the signal amplitude V<sub>1</sub>.

- Absolute crosstalk amplitude is proportional to slew rate V <sub>1</sub>/t<sub>r</sub>, not just 1/t<sub>r</sub>.

- Far end crosstalk width is always t<sub>r</sub>.

- For t<sub>r</sub> < 2 T<sub>L</sub>, where t<sub>r</sub> is the transition time of the signal on the driven line and T<sub>L</sub> is the propagation or bus delay down the line, the near end crosstalk amplitude V<sub>NE</sub> expressed as a fraction of signal amplitude V<sub>I</sub> is K<sub>NE</sub> which is a function of physical layout only.

- The higher the value of "t<sub>r</sub>" (slower transition times) the lower the percentage of crosstalk (relative to signal amplitude).

Although all circuit conductors have transmission line properties, these characteristics become significant when the edge rates of the drivers are equal to or less than about three times the propagation delay of the line. Significant transmission line properties may be exhibited, for example, where devices having edge rates of 3 ns are used to drive traces of 8 inches or greater, assuming propagation delays of 1.7 ns/ft for an unloaded printed circuit trace.

# 9 Signal Interconnects

Of the many properties of transmission lines, two are of major interest to the system designer:  $Z_{oe}$ , the effective equivalent impedance of the line, and  $t_{pde}$ , the effective propagation delay down the line. It should be noted that the intrinsic values of line impedance and propagation delay,  $Z_o$  and  $t_{pd}$ , are geometry-dependent. Once the intrinsic values are known, the effects of gate loading can be calculated. The loaded values for  $Z_{oe}$  and  $t_{pde}$  can be calculated with:

$$Z_{oe} = Z_o / (1 + C_t / C_i)^{**} 0.5$$

$$t_{ode} = t_{od}^{*} (1 + C_t / C_i)^{**} 0.5$$

(1)

(2)

where  $C_i$  = intrinsic line capacitance

$C_t$  = additional capacitance due to gate loading.

These formulas indicate that the loading of lines *decreases* the effective impedance of the line and *increases* the propagation delay. As was mentioned earlier, lines that have a propagation delay greater than one third the rise time of the signal driver should be evaluated for transmission line effects. When performing transmission line analysis on a bus, only the longest, most heavily loaded and the shortest, least loaded lines need to be analyzed. All lines in a bus should be terminated equally; if one line requires termination, all lines in the bus should be terminated. This will ensure similar signals on all of the lines.

# 10 Ground Bounce

Ground bounce occurs as a result of the intrinsic characteristics of the leadframes and bondwires of the packages used to house CMOS devices. As edge rates and drive capability increase in advanced logic families, the effects of these intrinsic electrical characteristics become more pronounced. One of these parasitic electrical characteristics is the inductance found in all leadframe materials.

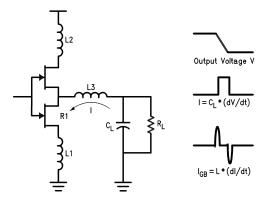

Figure 20 shows a simple circuit model for a CMOS device in a leadframe driving a standard test load. The inductor L1 represents the parasitic inductance in the ground lead of the package; inductor L2 represents the parasitic inductance in the power lead of the package; inductor L3 represents the parasitic inductance in the power lead of the package; inductor L3 represents the parasitic inductance in the output lead of the package; the resistor R1 represents the output impedance of the device output, and the capacitor and resistor  $C_L$  and  $R_L$  represent the standard test load on the output of the device.

Figure 20. Ground Bounce

The three waveforms shown represent how ground bounce is generated. The top waveform shows the voltage (V) across the load as it is switched from a logic HIGH to a logic LOW. The output slew rate is dependent upon the characteristics of the output transistor, and the inductors L1 and L3, and C<sub>L</sub>, the load capacitance. In order to change the output from a HIGH to a LOW, current must flow to discharge the load capacitance. The second waveform shows the current that is generated as the capacitor discharges [I =  $-C_{L} * (dV/dt)$ ]. This current, as it changes, causes a voltage to be generated across the inductances in the circuit. The formula for the voltage across an inductor is V = L(dI/dt). The third waveform shows the voltage that is induced across the inductance in the ground lead due to the changing currents [V<sub>GB</sub> = L1 \* (dI/dt)]. This induced voltage creates what is known as ground bounce.

Because the inductor is between the external system ground and the internal device ground, the induced voltage causes the internal ground to be at a different potential than the external ground. This shift in potential causes the device inputs and outputs to behave differently than expected because they are referenced to the internal device ground, while the devices which are either driving into the inputs or being driven by the outputs are referenced to the external system ground. External to the device, ground bounce causes input thresholds to shift and output levels to change.

Although this discussion is limited to ground bounce generated during HIGH-to-LOW transitions, it should be noted that the ground bounce is also generated during LOW-to-HIGH transitions. This ground bounce though, has a much smaller amplitude and therefore does not present the same concern.

There are many factors which affect the amplitude of the ground bounce. Included are:

- Number of outputs switching simultaneously: more outputs results in more ground bounce.

- Type of output load: capacitive loads generate two to three times more ground bounce than typical system traces. Increasing the capacitive load to approximately 60–70 pF, increases ground bounce. Beyond 70 pF, ground bounce drops off due to the filtering effect of the load itself. Moving the load away from the output also reduces the ground bounce.

- Location of the output pin: outputs closer to the ground pin exhibit less ground bounce than those further away due to effectively lower L1 and L3.

- Voltage: lowering V<sub>cc</sub> reduces ground bounce.

Ground bounce produces several symptoms:

- Altered device states.

- Propagation delay degradation.

- Undershoot on active outputs. The worst-case undershoot will be approximately equal to the worstcase quiet output noise.

# 11 NOISE SUPPRESSION TECHNIQUES

EMI control techniques involve both hardware implementations and methods and procedures. They may also be divided into intra-system and inter-system EMI control. Our major concern in this Application Note is intra-system EMI control, however, an overview of each may be appropriate at this time.

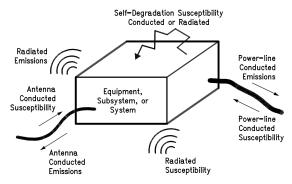

Figure 21 illustrates the basic elements of concern in an intra-system EMI problem. The test specimen may be a single box, an equipment, subsystem, or system (an ensemble of boxes with interconnecting cables). From a strictly near-sighted or selfish point-of-view, the only EMI concern would appear to be degradation of performance due to self jamming such as suggested at the top of the figure. While this might be the primary emphasis, the potential problems associated with either (1) susceptibility to outside conducted and/or radiated emissions or (2) tendency to pollute the outside world from its own undesired emissions, come under the primary classification of intra-system EMI. Corresponding EMI-control techniques, however, address themselves to both self-jamming and emission/susceptibility in accordance with applicable EMI specifications. The techniques that will be discussed include filtering, shielding, wiring, and grounding.

Inter-system EMI distinguishes itself by interference between two or more discrete and separate systems or platforms which are frequently under independent user control. Culprit emissions and/or susceptibility situations are divided into two classes: (1) antenna entry/exit and (2) back-door entry/exit. More than 95% of inter-system EMI problems involve the antenna entry/exit route of EMI. We can group inter-system EMI-control techniques by four fundamental categories: frequency management, time management, location management, and direction management.

Figure 21. Intra-System EMI Manifestations

The first step in locating a solution is to identify the problem as either an inter-system or intra-system EMI situation. Generally, if the specimen has an antenna and the problem develops from what exits or enters the antenna from another specimen or ambient, then the problem is identified as an inter-system EMI one. Otherwise, it is an intra-system EMI situation which we will discuss now.

# 12 Intra-System EMI-Control Techniques

# 12.1 Shielding

Shielding is used to reduce the amount of electromagnetic radiation reaching a sensitive victim circuit. Shields are made of metal and work on the principle that electromagnetic fields are reflected and/or attenuated by a metal surface. Different types of shielding are needed for different types of fields. Thus, the type of metal used in the shield and the shield's construction must be considered carefully if the shield is to function properly. The ideal shield has no holes or voids, and, in order to accommodate cooling vents, buttons, lamps, and access panels, special meshes and "EMI-hardened" components are needed.

Once a printed-circuit board design has been optimized for minimal EMI, residual interference can be further reduced if the board is placed in a shielded enclosure. A box's shielding effectiveness in decibels depends on three main factors: its skin, the control of radiation leakage through the box's apertures or open areas (like cooling holes), and the use of filters or shields at entry or exit spots of cables.

A box skin is typically fabricated from sheet metal or metallized plastic. Normally sheet metal skin that is 1 mm thick is more than adequate; it has a shielding effectiveness of more than 100 dB throughout the high-frequency spectrum from 1 MHz to 20 GHz. Conductive coatings on plastic boxes are another matter. Table 2 shows that at 10 MHz the shielding effectiveness can be as low as 27 dB if a carbon composite is used, or it can run as high as 106 dB for zinc sprayed on plastic by an electric arc process. Plastic filled materials or composites having either conductive powder, flakes, or filament are also used in box shielding; they have an effectiveness similar to that of metallized plastics.

#### Intra-System EMI-Control Techniques

| Table 2.           |                                     |                             |            |          |  |  |

|--------------------|-------------------------------------|-----------------------------|------------|----------|--|--|

|                    | Surface Resistance <sup>(1)</sup> , | Shielding Effectiveness, dB |            |          |  |  |

| Shielding Material | Ohms/Square                         | At 10 MHz                   | At 100 MHz | At 1 GHz |  |  |

| Silver Acrylic     | 0.004                               | 67                          | 93         | 97       |  |  |

| Paint              |                                     |                             |            |          |  |  |

| Silver Epoxy       | 0.1                                 | 59                          | 81         | 87       |  |  |

| Paint              |                                     |                             |            |          |  |  |

| Silver             | 0.05                                | 57                          | 82         | 89       |  |  |

| Deposition         |                                     |                             |            |          |  |  |

| Nickel             | 3.0                                 | 35                          | 47         | 57       |  |  |

| Composite          |                                     |                             |            |          |  |  |

| Carbon             | 10.0                                | 27                          | 35         | 41       |  |  |

| Composite          |                                     |                             |            |          |  |  |

| Arc-Sprayed        | 0.002                               | 106                         | 92         | 98       |  |  |

| Zinc               |                                     |                             |            |          |  |  |

| Wire Screen        | N.A.                                | 86                          | 66         | 48       |  |  |

| (0.64 mm Grid)     |                                     |                             |            |          |  |  |

| (                  |                                     |                             |            |          |  |  |

Table 2

<sup>(1)</sup> Effectiveness of shielding materials with 25-µm thickness and for frequencies for which the largest dimension of the shielding plate is less than a quarter of a wavelength.

In many cases shielding effectiveness of at least 40 dB is required of plastic housings for microcontrollerbased equipment to reduce printed-circuit board radiation to a level that meets FCC regulations in the United States or those of the VDE in Europe. Such skin shielding is easy to achieve. The problem is aperture leakage. The larger the aperture, the greater its radiation leakage because the shield's natural attenuation has been reduced. On the other hand, multiple small holes matching the same area as the single large aperture can attain the same amount of cooling with little or no loss of attenuation properties.

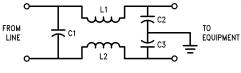

# 12.2 Filtering

Filters are used to eliminate conducted interference on cables and wires, and can be installed at either the source or the victim. Figure 22 shows an AC power-line filter. The values of the components are not critical; as a guide, the capacitors can be between 0.01 and 0.001  $\mu$ F, and the inductors are nominally 6.3  $\mu$ H. Capacitor C1 is designed to shunt any high-frequency differential-mode currents before they can enter the equipment to be protected. Capacitors C2 and C3 are included to shunt any common-mode currents to ground. The inductors, L1 and L2, are called common-mode chokes, and are placed in the circuit to impede any common-mode currents.

Figure 22. Filtering

# 12.3 Wiring

Now that the equipment in each box can be successfully designed to combat EMI emission and susceptibility separately, the boxes may be connected together to form a system. Here the input and output cables and, to a lesser extent, the power cable form an "antenna farm" that greatly threatens the overall electromagnetic compatibility of the system. Most field remedies for EMI problems focus on the coupling paths created by the wiring that interconnects systems. By this time most changes to the individual equipment circuits are out of the question.

Let us address five coupling paths that are encountered in typical systems comprised of two or more pieces of equipment connected by cables. These should adequately cover most EMI susceptibility problems. They are:

- A common ground impedance coupling—a conducting path in which a common impedance is shared between an undesired emission source and the receptor.

- A common-mode, radiated field-to-cable coupling, in which electromagnetic fields penetrate a loop formed by two pieces of equipment, a cable connecting them, and a ground plane.

- A differential-mode, radiated field-to-cable coupling, in which the electromagnetic fields penetrate a loop formed by two pieces of equipment and an interconnecting transmission line or cable.

- A crosstalk coupling, in which signals in one transmission line or cable are capacitively or inductively coupled into another transmission line.

- A conductive paththrough power lines feeding the equipment.

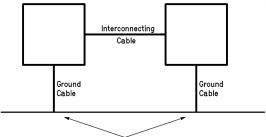

The first coupling path is formed when two pieces of equipment are connected to the same ground conductor at different points, an arrangement that normally produces a voltage difference between the two points. If possible, connecting both pieces of equipment to a single-point ground eliminates this voltage. Another remedy is to increase the impedance along a loop that includes the path between the ground connections of the two boxes. Examples include the isolation of printed-circuit boards from their cabinet or case, the use of a shielded isolation transformer in the signal path, or the insertion of an inductor between one or both boxes and the ground conductor. The use of balanced circuits, differential line drivers and receivers, and absorbing ferrite beads and rods on the interconnecting cable can further reduce currents produced by this undesirable coupling path.

possible voltage differential

#### Common Ground Impedance Coupling

A balanced circuit is configured so its two output signal leads are electrically symmetrical with respect to ground, as the signal increases on one output the signal on the other decreases. Differential line drivers produce a signal that is electrically symmetrical with respect to ground from a single-ended circuit in which only one lead is changing with respect to ground. Ferrite beads, threaded over electrical conductors, substantially attentuate electromagnetic interference by turning radio-frequency energy into heat, which is dissipated in them.

In the second coupling path, a radiated electromagnetic field is converted into a common-mode voltage in the ground plane loop containing the interconnect cable and both boxes. This voltage may be reduced if the loop area is trimmed.

Common-Mode, Radiated Field-to-Cable Coupling

The third coupling path produces a differential-mode voltage that appears across the input terminals of the EMI receptor. One way of controlling this is to cancel or block the pickup of differential-mode radiation. In a balanced transmission line, this is done by use of twisted-wire pairs and a shielded cable.

#### Intra-System EMI-Control Techniques

As for crosstalk, the fourth coupling path—the reduction of capacitive coupling can be achieved by the implementation of at least one of these steps:

- Reducing the spacing between wire pairs in either or both of the transmission lines.

- Increasing the separation between the two transmission lines.

- · Reducing the frequency of operation of the source, if possible.

- Adding a cable shield over either or both transmission lines.

- · Twisting the source's or receptor's wire pairs.

- Twisting both wire pairs in opposite directions.

The fifth coupling path conductively produces both common-mode and differential-mode noise pollution on the power mains. Among several remedies that can suppress the EMI here are the filters and isolation transformers.

There are only about 50 common practical remedies that can be used in most EMI situations. Of these, about 10 suffice in 80 percent of the situations. Most engineers are aware of at least some of these remedies—for example, twisting wires to reduce radiation pickup.

In order to attack the EMI problem, one can make use of the information contained in Table 3. First, decide what coupling path has the worst EMI interference problem. From the 11 most common coupling paths listed at the top of the table, find the problem coupling path. Using the numbers found in that table entry, locate the recommended remedy or remedies from the 12 common EMI fixes identified at the bottom of the table. This procedure should be repeated until all significant coupling paths have been properly controlled and the design goal has been met.

### 12.4 Inter-System EMI Control Techniques

There are many EMI controls that may be carried out to enhance the chances of inter-system EMC. They can be grouped into four categories which we will discuss briefly. The following discussion is not intended to be complete but merely provide an overview of some EMI control techniques available to the intersystem designer and user.

Frequency management suggests both transmitter emission control and improvement of receptors against spurious responses. The object is to design and operationally maintain transmitters so that they occupy the least frequency spectrum possible in order to help control electromagnetic pollution. For example, this implies that long pulse rise and fall times should be used. Quite often one of the most convenient, economic and rapid solutions to an EMI problem in the field, is to change frequency of either the victim receiver or the culprit source.

In those applications where information is passed between systems, a possible time management technique could be utilized where the amount of information transferred is kept to a minimum. This should reduce the amount of time that the receptor is susceptible to any EMI. In communication protocols, for example, essential data could be transmitted in short bursts or control information could be encoded into fewer bits.

Location management refers to EMI control by the selection of location of the potential victim receptor with respect to all other emitters in the environment. In this regard, separation distance between transmitters and receivers is one of the most significant forms of control since interfering source emissions are reduced greatly with the distance between them. The relative position of potentially interfering transmitters to the victim receiver are also significant. If the emitting source and victim receiver are shielded by obstacles, the degree of interference would be substantially reduced.

Direction management refers to the technique of EMI control by gainfully using the direction and attitude of arrival of electromagnetic signals with respect to the potential victim's receiving antenna.

| Radiated Field to Interconnecting Cable | 2, 7, 8, 9, 11 | Radiated Field to Box | 12, 13 |

|-----------------------------------------|----------------|-----------------------|--------|

| (Common-Mode)                           |                |                       |        |

| Radiated Field to Interconnecting Cable | 2, 5, 6        | Box to Radiated Field | 12, 13 |

| (Differential-Mode)                     |                |                       |        |

| Interconnecting Cable to Radiated Field | 1, 3, 9, 11    | Box-to-Box Radiation  | 12, 13 |

### Table 3. Electromagnetic Interference Coupling Paths

|  | Table 3. | Electromagnet | ic Interference |  | Paths | (continued) |

|--|----------|---------------|-----------------|--|-------|-------------|

|--|----------|---------------|-----------------|--|-------|-------------|

| (Common-Mode)                           |                          |                               |               |

|-----------------------------------------|--------------------------|-------------------------------|---------------|

| Interconnecting Cable to Radiated Field | 1, 3, 5, 6, 7            | Box-to-Box Conduction         | 1, 2, 7, 8, 9 |

| (Differential-Mode)                     |                          |                               |               |

| Cable-to-Cable Crosstalk                | 1, 2, 3, 4, 5, 6, 10, 11 | Power Mains to Box Conduction | 4, 11         |

|                                         |                          | Box to Power Mains Conduction | 4             |

Electromagnetic Interference Fixes

- 1. Insert Filter In Signal Source

- 2. Insert Filter in Signal Receptor

- 3. Insert Filter in Power Source

- 4. Insert Filter in Power Receptor

- 5. Twist Wire Pair

- 6. Shield Cable

- 7. Use Balanced Circuits

- 8. Install Differential Line Drivers and Receivers

- 9. Float Printed Circuit Board(s)

- 10. Separate Wire Pair

- 11. Use Ferrite Beads

- 12. Use a Multilayer Instead of a Single-Layer Printed Circuit Boards

### 13 DESIGN GUIDELINES

The growth of concern over electromagnetic compatibility (EMC) in electronic systems continues to rise in the years since the FCC proclaimed that there shall be no more pollution of the electromagnetic spectrum. Still, designers have not yet fully come to grips with a major source and victim of electromagnetic interference—the printed circuit board. The most critical stage for addressing EMI is during the circuit board design. Numerous tales of woe can be recounted about the eleventh hour attempt at solving an EMI problem by retrofit because EMC was given no attention during design. This retrofit ultimately costs much more than design stage EMC, holds up production, and generally makes managers unhappy. With these facts in mind, let's address electromagnetic compatibility considerations in printed circuit board design.

# 14 Logic Selection

Logic selection can ultimately dictate how much attention must be given to EMC in the total circuit design. The first guideline should be: use the slowest speed logic that will do the job. Logic speed refers to transition times of output signals and gate responses to input signals. Many emissions and susceptibility problems can be minimized if a slow speed logic is used. For example, a square wave clock or signal pulse with a 3 ns rise time generates radio frequency (100 MHz and higher) energy that is gated about on the PC board. It also means that the logic can respond to comparable radio frequency energy if it gets onto the boards.

The type of logic to be used is normally an early design decision, so that control of edge speeds and, hence, emissions and susceptibility is practical early. Of course, other factors such as required system performance, speed, and timing considerations must enter into this decision. If possible, design the circuit with a slow speed logic. The use of slow speed logic, however, does not guarantee that EMC will exist when the circuit is built; so proper EMC techniques should still be implemented consistently during the remainder of the circuit design.

### 15 Component Layout

Component layout is the second stage in PC board design. Schematics tell little or nothing about how systems will perform once the board is etched, stuffed, and powered. A circuit schematic is useful to the design engineer, but an experienced EMC engineer refers to the PC board when troubleshooting. By controlling the board layout in the design stage, the designer realizes two benefits: (1) a decrease in EMI problems when the circuit or system is sent for EMI or quality assurance testing; and (2) the number of EMI coupling paths is reduced, saving troubleshooting time and effort later on.

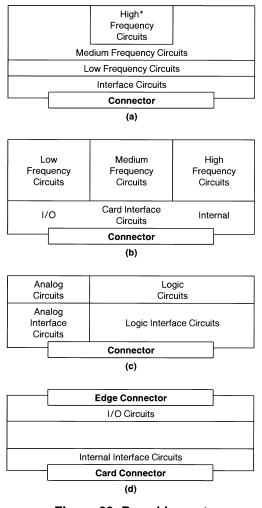

Some layout guidelines for arranging components according to logic speed, frequency, and function are shown in Figure 23. These guidelines are very general. A particular circuit is likely to require a combination and/or tradeoffs of the above arrangements. Isolation of the I/O from digital circuitry is important where emissions or susceptibility may be a problem. For the case of emissions, a frequently encountered coupling path involves a digital energy coupling through I/O circuitry and signal traces onto I/O cables and wires, where the latter subsequently radiate. When susceptibility is a problem, it is common for the EMI energy to couple from I/O circuits onto sensitive digital lines, even though the I/O lines may be "opto-coupled" or otherwise supposedly isolated. In both situations, the solution often lies in the proper electrical and physical isolation of analog and low speed digital lines from high speed circuits. When high speed signals are designed to leave the board, the reduction of EMI is usually performed via shielding of I/O cables and is not considered here.

Therefore, a major guideline in laying out boards is to isolate the I/O circuitry from the high speed logic. This method applied even if the logic is being clocked at "only" a few MHz. Often, the fundamental frequency is of marginal interest, with the harmonics generated from switching edges of the clock being the biggest emission culprits. Internal system input/output PCB circuity should be mounted as close to the edge connector as possible and capacitive filtering of these lines may be necessary to reduce EMI on the lines.

High speed logic components should be grouped together. Digital interface circuitry and I/O circuitry should be physically isolated from each other and routed on separate connectors, if possible as shown in Figure 23*d*.

• No High Frequency Signals to the Backplane

Figure 23. Board Layout

# 16 Power Supply Bussing

Power supply bussing is the next major concern in the design phase. Isolated digital and analog power supplies must be used when mixing analog and digital circuitry on a board. The design preferably should provide for separate power supply distribution for both the analog and digital circuitry. Single point common grounding of analog and digital power supplies should be performed at one point and one point only—usually at the motherboard power supply input for multi-card designs, or at the power supply input edge connector on a single card system. The fundamental feature of good power supply bussing, however, is low impedance and good decoupling over a large range of frequencies. A low impedance distribution system requires two design features: (1) proper power supply and return trace layout and (2) proper use of decoupling capacitors.

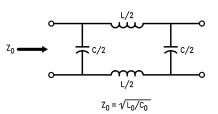

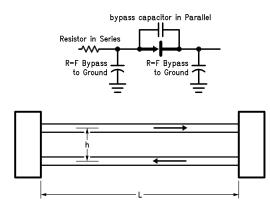

At high frequencies, PCB traces and the power supply busses ( $+V_{cc}$  and 0V) are viewed as transmission lines with associated characteristic impedance,  $Z_0$ , as modeled in Figure 24. The goal of the designer is to maximize the capacitance between the lines and minimize the self-inductance, thus creating a low  $Z_0$ . Table 4 shows the characteristic impedance of various two-trace configurations as a function of trace width, W, and trace separation, h.

Table 4. (1)

| <b>1</b> #1 | ı #2                                                                                                                                                                                                                                                                                                                             | <b>I</b> #3                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|             | w                                                                                                                                                                                                                                                                                                                                | D                                                      |

|             | Z <sub>02</sub> <u>-h</u> -                                                                                                                                                                                                                                                                                                      |                                                        |

|             |                                                                                                                                                                                                                                                                                                                                  |                                                        |

|             | Strip Over Ground Plane*                                                                                                                                                                                                                                                                                                         | Strips Side by Side **                                 |

| 377         | 377                                                                                                                                                                                                                                                                                                                              | NA                                                     |

| 281         | 281                                                                                                                                                                                                                                                                                                                              | NA<br>NA                                               |

| 241         | 241                                                                                                                                                                                                                                                                                                                              | NA<br>NA                                               |

| 187         | 187                                                                                                                                                                                                                                                                                                                              | NA<br>NA                                               |

|             | 107                                                                                                                                                                                                                                                                                                                              | 100                                                    |

| 169         | 169                                                                                                                                                                                                                                                                                                                              | 0                                                      |

| 153         | 153                                                                                                                                                                                                                                                                                                                              | 25                                                     |

| 140         | 140                                                                                                                                                                                                                                                                                                                              | 0<br>25<br>34<br>53<br>62<br>73                        |

| 99          | 99                                                                                                                                                                                                                                                                                                                               | 62                                                     |

| 84          | 84                                                                                                                                                                                                                                                                                                                               | 73                                                     |

|             |                                                                                                                                                                                                                                                                                                                                  |                                                        |

| 67          | 67                                                                                                                                                                                                                                                                                                                               | 87<br>98<br>107<br>114                                 |

| 56          | 56                                                                                                                                                                                                                                                                                                                               | 98                                                     |

| 48          | 48                                                                                                                                                                                                                                                                                                                               | 107                                                    |

| 34          | 34                                                                                                                                                                                                                                                                                                                               | 127                                                    |

|             |                                                                                                                                                                                                                                                                                                                                  |                                                        |

| 28          | 28                                                                                                                                                                                                                                                                                                                               | 137                                                    |

| 24          | 24                                                                                                                                                                                                                                                                                                                               | 146                                                    |

| 19          | 21                                                                                                                                                                                                                                                                                                                               | 153                                                    |

| 17          | 17                                                                                                                                                                                                                                                                                                                               | 160<br>166                                             |

|             |                                                                                                                                                                                                                                                                                                                                  |                                                        |

| 14          | 14                                                                                                                                                                                                                                                                                                                               | 176                                                    |

|             | 11.2                                                                                                                                                                                                                                                                                                                             | 188                                                    |

| 8.4<br>6.7  | 0.4<br>6.7                                                                                                                                                                                                                                                                                                                       | 204<br>217                                             |

| 5.6         | 5.6                                                                                                                                                                                                                                                                                                                              | 227                                                    |

| 4.2         | 4.2                                                                                                                                                                                                                                                                                                                              | 243<br>255                                             |

| 1 74        | 7 4                                                                                                                                                                                                                                                                                                                              | 055                                                    |

|             | $\begin{array}{c} t = & \begin{array}{c} \#1 \\ \hline Z_{01} & \hline \\ & W \end{array} \\ \hline Parallel Strips * \\ \hline 377 \\ 281 \\ 241 \\ 211 \\ 187 \\ \hline 169 \\ 153 \\ 140 \\ 112 \\ 99 \\ 84 \\ 67 \\ 56 \\ 48 \\ 24 \\ 21 \\ 19 \\ 17 \\ \hline 14 \\ 11.2 \\ 8.4 \\ 6.7 \\ 5.6 \\ 4.2 \\ 3.4 \\ \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

<sup>1)</sup> \*Mylar dielectric assumed: DC = 5.0; D≫ nearby ground plane \*\*Paper base phenolic or glass epoxy assumed: DC = 4.7

Z01 =  $(377/\sqrt{DC}) \times (h/W)$ , for W > 3h and h > 3t

$Z02 = (377/\sqrt{DC}) \times (h/W)$ , for W > 3h

$Z03 = (120/\sqrt{DC}) \ln (D/W + \sqrt{D/W^2 - 1})$  for  $W \gg t$

where  $L_{0}$  and  $C_{0}$  are, respectively, the distributed inductance and capacitance per unit length of the line

Figure 24.

Any one of the three configurations may be viewed as a possible method of routing power supply (or signal) traces. The most important feature of Table 4 is the noticeable difference in impedance between the parallel strips and strip over ground plane compared with the side-by-side configurations.

As an example of the amount of voltage that can be generated across the impedance of a power bus, consider TTL logic which pulls a current of approximately 16 mA from a supply that has a  $25\Omega$  bus impedance (this assumes no decoupling present). The transient voltage is approximately  $dV = 0.016 \times 25\Omega = 400 \text{ mV}$ , which is equal to the noise immunity level of the TTL logic. A  $25\Omega$  (or higher) impedance is not uncommon in many designs where the supply and return traces are routed on the same side of the board in a side-by-side fashion. In fact, it is not uncommon to find situations where the power supply and return traces are routed quite a distance from each other, thereby increasing the overall impedance of the distribution system. This is obviously a poor layout.

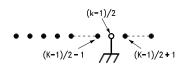

Power and ground planes offer the least overall impedance. The use of these planes leads the designer closer to a multi-layer board. At the very least, it is recommended that all open areas on the PC board be "landfilled" with a 0V reference plane so that ground impedance is minimized.