# DP83815,DP83816

AN-1323 Updating DP83815 MacPHYTER Hardware Designs to DP83816 MacPHYTER-II

Literature Number: SNLA063

# Updating DP83815 Mac-PHYTER<sup>™</sup> Hardware Designs to DP83816 MacPHYTER-II

## 1.0 Scope

This application note is provided to allow a DP83815 based design to be updated to DP83816 efficiently. It details the differences in pin connections and functionality between DP83816 MacPHYTER-II and DP83815 MacPHYTER.

## 2.0 General Information

- 1. The **DP83816** is only available in 144-LQFP package as used on the **DP83815**.

- 2. The **DP83816** uses  $0.18 \mu m$  CMOS technology compared to the **DP83815** which uses  $0.35 \mu m$  CMOS technology.

- 3. NSC provided drivers are compatible on both the **DP83816** and the **DP83815**.

- To allow differentiation between the DP83816 and the DP83815, the Silicon Revision Register (SRR - offset 58h) has been updated to 0505h for the DP83816.

# 3.0 Pin Change Information

Pin changes on the **DP83816** are divided into three categories. Required connection changes, must be observed for proper operation (see Table 1). Optional connection changes, pin can be left connected as it was on the **DP83815** with no adverse effects, although it has a different function on the **DP83816** (see Table 2). Informational changes, pins that have kept the same connections but changed names (see Table 3).

Table 4 shows all pins of both devices for easy comparison.

## 3.1 REQUIRED PIN CONNECTION CHANGES

Required pin connection changes must be done for proper operation of the device. Note that although pin 48 has nothing connected to it on both devices, its functionality on the **DP83816** has changed. The reason for not connecting it has changed and is explained below.

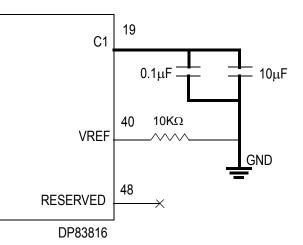

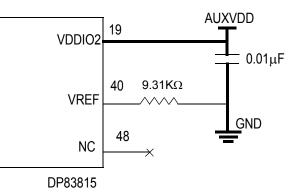

- For **DP83816**, pin 19 should be connected to GND through  $10\mu$ F and  $0.1\mu$ F parallel caps, as shown in Figure 1. For **DP83815**, pin 19 is connected to the 3.3V AUX supply and to a  $0.01\mu$ F cap, as shown in Figure 2.

- For **DP83816**, pin 40 is connected to GND via a  $10K\Omega$  resistor, as shown in Figure 1. For **DP83815**, pin 40 is connected to GND via a  $9.31K\Omega$  resistor, as shown in Figure 2.

National Semiconductor<sup>®</sup> Application Note 1323 March 2004

For DP83816, pin 48 is Reserved and cannot be connected to any external logic or net, as shown in Figure 1.

For **DP83815**, pin 48 is a No Connect, as shown in Figure 2.

Table 1 compares these pins on both devices.

## Figure 1. DP83816 pin connections Block Diagram

## Figure 2. DP83815 pin connections Block Diagram

## 3.2 OPTIONAL PIN CONNECTION CHANGES

These pins have functionally changed, however previous connections would have no adverse effects.

Table 2 compares these pins on both devices.

## 3.3 INFORMATIONAL PIN CHANGES

These are pin name changes only, functionality remains the same.

Table 3 compares these pins on both devices.

National Semiconductor is a registered trademark of National Semiconductor Corporation. MacPHYTER is a trademark of National Semiconductor Corporation. AN-1323

### Table 1. DP83816 required pin connection changes

| DP83815 | DP83816  | LQFP Pin<br>No(s) | Description                                                                                                                                                 |

|---------|----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDIO2  | C1       | 19                | On DP83815: Connect to Aux 3.3V supply VDD                                                                                                                  |

|         |          |                   | On DP83816: Connect to GND through 10uF and 0.1uF external parallel capacitors                                                                              |

| VREF    | VREF     | 40                | Bandgap Reference: External current reference resistor for internal Phy bandgap circuitry.                                                                  |

|         |          |                   | For the DP83815: The value of this resistor is 9.31 K $\Omega$ 1% metal film (100 ppm/ <sup>o</sup> C) which must be connected from the VREF pin to ground. |

|         |          |                   | For the DP83816: The value of this resistor is 10 K $\Omega$ 1% metal film (100 ppm/ <sup>o</sup> C) which must be connected from the VREF pin to ground    |

| NC      | RESERVED | 48                | On DP83815: No Connect                                                                                                                                      |

|         |          |                   | On DP83816: Reserved and cannot be connected to any external logic or net.                                                                                  |

### Table 2. DP83816 optional pin connection changes

| DP83815  | DP83816 | LQFP Pin<br>No(s) | Description                                                                           |

|----------|---------|-------------------|---------------------------------------------------------------------------------------|

| FXVDD,   | NC      | 36,               | On DP83815: Connect pins 36, 37, 84, 85, 124, 125 and 126 to isolated Aux 3.3V supply |

| SUBGND1, |         | 37,               | VDD, GND, GND, Aux 3.3V supply VDD, GND, Aux 3.3V supply VDD, and GND                 |

| VSSIO4,  |         | 84,               | respectively.                                                                         |

| VDDIO4,  |         | 85,               | On DP83816: These pins, that were previously supply pins on the DP83815, are now No   |

| MACVSS2, |         | 124,              | Connects, and thus having them connected as they were previously on the DP 83815 has  |

| MACVDD2, |         | 125,              | no adverse effects.                                                                   |

| SUBGND3  |         | 126               |                                                                                       |

### Table 3. DP83816 pin name changes

| DP83815                                                                                                                                                                          | DP83816 | LQFP Pin<br>No(s)                                                                        | Description                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------|---------------------------------------|

| VDDIO1, PHYVDD1, VDDIO3, PHYVDD2,<br>TXDVDD, MACVDD1, VDDIO5                                                                                                                     | AUXVDD  | 9, 21, 27, 33,<br>56, 58, 137                                                            | Connect to Aux 3.3V supply VDD        |

| PCIVDD1, PCIVDD2, PCIVDD3, PCIVDD4,<br>PCIVDD5                                                                                                                                   | PCIVDD  | 69, 80, 94, 107,<br>117                                                                  | PCI VDD - connect to PCI bus 3.3V VDD |

| VSSIO1, VSSIO2, VSSIO3, PHYVSS1,<br>PHYVSS2, FXVSS, RXAVSS1, RXAVSS2,<br>SUBGND2, TXDVSS, TXIOVSS1, TXIOVSS2,<br>MACVSS1, PCIVSS1, PCIVSS2, PCIVSS3,<br>PCIVSS4, PCIVSS5, VSSIO5 | VSS     | 8, 16, 20, 26,<br>32, 35, 38, 44,<br>49, 51, 52, 55,<br>57, 65, 77, 90,<br>103, 114, 136 | VSS                                   |

| DP83815       | DP83816   | LQFP Pin<br>No(s)                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Bus Inter | face      |                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AD[31-0]      | AD[31-0]  | 66, 67,<br>68, 70,<br>71, 72,<br>73, 74,<br>78, 79,<br>81, 82,<br>83, 86,<br>87, 88,<br>101, 102,<br>104, 105,<br>106, 108,<br>109, 110,<br>112, 113,<br>115, 116,<br>118, 119,<br>120, 121 | Address and Data: Multiplexed address and data bus. As a bus master,<br>the DP83815/16 will drive address during the first bus phase. During<br>subsequent phases, the DP83815/16 will either read or write data<br>expecting the target to increment its address pointer. As a bus target, the<br>DP83815/16 will decode each address on the bus and respond if it is the<br>target being addressed.                                                                                                                                                                      |

| CBEN[3-0]     | CBEN[3-0] | 75,<br>89,<br>100,<br>111                                                                                                                                                                   | <b>Bus Command/Byte Enable:</b> During the address phase these signals define the "bus command" or the type of bus transaction that will take place. During the data phase these pins indicate which byte lanes contain valid data. CBEN[0] applies to byte 0 (bits 7-0) and CBEN[3] applies to byte 3 (bits 31-24) in the Little Endian Mode. In Big Endian Mode, CBEN[3] applies to byte 0 (bits 31-24) and CBEN[0] applies to byte 3 (bits 7-0). Big Endian mode only applies to PCI master operations; the byte ordering does not change for target register accesses. |

| PCICLK        | PCICLK    | 60                                                                                                                                                                                          | <b>Clock:</b> This PCI Bus clock provides timing for all bus phases. The rising edge defines the start of each phase. The clock frequency ranges from 0 to 33 MHz.                                                                                                                                                                                                                                                                                                                                                                                                         |

| DEVSELN       | DEVSELN   | 95                                                                                                                                                                                          | <b>Device Select:</b> As a bus master, the DP83815/16 samples this signal to insure that the destination address for the data transfer is recognized by a PCI target. As a target, the DP83815/16 asserts this signal low when it recognizes its address after FRAMEN is asserted.                                                                                                                                                                                                                                                                                         |

| FRAMEN        | FRAMEN    | 91                                                                                                                                                                                          | <b>Frame:</b> As a bus master, this signal is asserted low to indicate the beginning and duration of a bus transaction. Data transfer takes place when this signal is asserted. It is de-asserted before the transaction is in its final phase. As a target, the device monitors this signal before decoding the address to check if the current transaction is addressed to it.                                                                                                                                                                                           |

| GNTN          | GNTN      | 63                                                                                                                                                                                          | <b>Grant:</b> This signal is asserted low to indicate to the DP83815/16 that it has been granted ownership of the bus by the central arbiter. This input is used when the DP83815/16 is acting as a bus master.                                                                                                                                                                                                                                                                                                                                                            |

| IDSEL         | IDSEL     | 76                                                                                                                                                                                          | <b>Initialization Device Select:</b> This pin is sampled by the DP83815/16 to identify when configuration read and write accesses are intended for it.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INTAN         | INTAN     | 61                                                                                                                                                                                          | Interrupt A: This signal is asserted low when an interrupt condition occurs<br>as defined in the Interrupt Status Register, Interrupt Mask, and Interrupt<br>Enable registers.                                                                                                                                                                                                                                                                                                                                                                                             |

| IRDYN         | IRDYN     | 92                                                                                                                                                                                          | <b>Initiator Ready:</b> As a bus master, this signal will be asserted low when the DP83815/16 is ready to complete the current data phase transaction. This signal is used in conjunction with the TRYDN signal. Data transaction takes place at the rising edge of PCICLK when both IRDYN and TRDYN are asserted low. As a target, this signal indicates that the master has put the data on the bus.                                                                                                                                                                     |

| PAR           | PAR       | 99                                                                                                                                                                                          | <b>Parity:</b> This signal indicates even parity across AD[31-0] and CBEN[3-0] including the PAR pin. As a master, PAR is asserted during address and write data phases. As a target, PAR is asserted during read data phases.                                                                                                                                                                                                                                                                                                                                             |

AN-1323

| 323 |  |

|-----|--|

| Ξ   |  |

| A   |  |

| DP83815          | DP83816            | LQFP Pin<br>No(s) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERRN            | PERRN              | 97                | <b>Parity Error:</b> The DP83815/16 as a master or target will assert this signal low to indicate a parity error on any incoming data (except for special cycles). As a bus master, it will monitor this signal on all write operations (except for special cycles).                                                                                                                                                                                                         |

| REQN             | REQN               | 64                | <b>Request:</b> The DP83815/16 will assert this signal low to request ownership of the bus from the central arbiter.                                                                                                                                                                                                                                                                                                                                                         |

| RSTN             | RSTN               | 62                | <b>Reset:</b> When this signal is asserted all outputs of DP83815/16 will be tri-<br>stated and the device will be put into a known state.                                                                                                                                                                                                                                                                                                                                   |

| SERRN            | SERRN              | 98                | System Error: This signal is asserted low by DP83815/16 during address parity errors and system errors if enabled.                                                                                                                                                                                                                                                                                                                                                           |

| STOPN            | STOPN              | 96                | Stop: This signal is asserted low by the target device to request the master device to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                         |

| TRDYN            | TRDYN              | 93                | <b>Target Ready:</b> As a master, this signal indicates that the target is ready for<br>the data during write operation and with the data during read operation. As<br>a target, this signal will be asserted low when the (target) device is ready to<br>complete the current data phase transaction. This signal is used in<br>conjunction with the IRDYN signal. Data transaction takes place at the<br>rising edge of PCICLK when both IRDYN and TRDYN are asserted low. |

| PMEN/<br>CLKRUNN | PMEN/<br>CLKRUNN   | 59                | <b>Power Management Event/Clock Run Function:</b> This pin is a dual function pin. The function of this pin is determined by the CLKRUN_EN bir 0 of the CLKRUN Control and Status register (CCSR). Default operation o this pin is PMEN.                                                                                                                                                                                                                                     |

|                  |                    |                   | <b>Power Management Event:</b> This signal is asserted low by DP83815/16 to indicate that a power management event has occurred. For pin connection please refer to Section 6.7.                                                                                                                                                                                                                                                                                             |

|                  |                    |                   | <b>Clock Run Function:</b> In this mode, this pin is used to indicate when the PCICLK will be stopped.                                                                                                                                                                                                                                                                                                                                                                       |

| 3VAUX            | 3VAUX              | 122               | <b>PCI Auxiliary Voltage Sense:</b> This pin is used to sense the presence of a 3.3V auxiliary supply in order to define the PME Support available. For pir connection please refer to Section 6.7.                                                                                                                                                                                                                                                                          |

|                  |                    |                   | This pin has an internal weak pull down.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PWRGOOD          | PWRGOOD            | 123               | <b>PCI bus power good:</b> Connected to PCI bus 3.3V power, this pin is used to sense the presence of PCI bus power during the D3 power managemen state.                                                                                                                                                                                                                                                                                                                     |

|                  |                    |                   | This pin has an internal weak pull down.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Media Indepe     | endent Interface ( | (MII)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| COL              | COL                | 28                | <b>Collision Detect:</b> The COL signal is asserted high asynchronously by the external PMD upon detection of a collision on the medium. It will remain asserted as long as the collision condition persists.                                                                                                                                                                                                                                                                |

| CRS              | CRS                | 29                | <b>Carrier Sense:</b> This signal is asserted high asynchronously by the externa PMD upon detection of a non-idle medium.                                                                                                                                                                                                                                                                                                                                                    |

| MDC              | MDC                | 5                 | Management Data Clock: Clock signal with a maximum rate of 2.5 MHz used to transfer management data for the external PMD on the MDIO pin.                                                                                                                                                                                                                                                                                                                                    |

| MDIO             | MDIO               | 4                 | <b>Management Data I/O:</b> Bidirectional signal used to transfer management information for the external PMD. (See Section 3.12.4 for details on connections when MII is used.)                                                                                                                                                                                                                                                                                             |

| RXCLK            | RXCLK              | 6                 | <b>Receive Clock:</b> A continuous clock, sourced by an external PMD device, that is recovered from the incoming data. During 100 Mb/s operation RXCLK is 25 MHz and during 10 Mb/s this is 2.5 MHz.                                                                                                                                                                                                                                                                         |

| DP83815                                | DP83816                                | LQFP Pin<br>No(s) | Description                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------|----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD3/MA9,<br>RXD2/MA8,<br>RXD1/MA7,    | RXD3/MA9,<br>RXD2/MA8,<br>RXD1/MA7,    | 12,<br>11,<br>10, | <b>Receive Data</b> : Sourced from an external PMD, that contains data aligned<br>on nibble boundaries and are driven synchronous to RXCLK. RXD[3] is the<br>most significant bit and RXD[0] is the least significant bit.                                                                                                                 |

| RXD0/MA6                               | RXD0/MA6                               | 7                 | <b>BIOS ROM Address:</b> During external BIOS ROM access, these signals become part of the ROM address.                                                                                                                                                                                                                                    |

| RXDV/MA11                              | RXDV/MA11                              | 15                | <b>Receive Data Valid:</b> Indicates that the external PMD is presenting recovered and decoded nibbles on the RXD signals, and that RXCLK is synchronous to the recovered data in 100 Mb/s operation. This signal will encompass the frame, starting with the Start-of-Frame delimiter (JK) and excluding any End-of-Frame delimiter (TR). |

|                                        |                                        |                   | <b>BIOS ROM Address:</b> During external BIOS ROM access, this signal becomes part of the ROM address.                                                                                                                                                                                                                                     |

| RXER/MA10                              | RXER/MA10                              | 14                | <b>Receive Error:</b> Asserted high synchronously by the external PMD whenever it detects a media error and RXDV is asserted in 100 Mb/s operation.                                                                                                                                                                                        |

|                                        |                                        |                   | <b>BIOS ROM Address:</b> During external BIOS ROM access, this signal becomes part of the ROM address.                                                                                                                                                                                                                                     |

| RXOE                                   | RXOE                                   | 13                | Receive Output Enable: Used to disable an external PMD while the BIOS ROM is being accessed.                                                                                                                                                                                                                                               |

| TXCLK                                  | TXCLK                                  | 31                | <b>Transmit Clock:</b> A continuous clock that is sourced by the external PMD.<br>During 100 Mb/s operation this is 25 MHz +/- 100 ppm. During 10 Mb/s<br>operation this clock is 2.5 MHz +/- 100 ppm.                                                                                                                                     |

| TXD3/MA15,<br>TXD2/MA14,<br>TXD1/MA13, | TXD3/MA15,<br>TXD2/MA14,<br>TXD1/MA13, | 25,<br>24,<br>23, | <b>Transmit Data:</b> Signals which are driven synchronous to the TXCLK for transmission to the external PMD. TXD[3] is the most significant bit and TXD[0] is the least significant bit.                                                                                                                                                  |

| TXD0/MA12                              | TXD0/MA12                              | 22                | <b>BIOS ROM Address:</b> During external BIOS ROM access, these signals become part of the ROM address.                                                                                                                                                                                                                                    |

| TXEN                                   | TXEN                                   | 30                | <b>Transmit Enable:</b> This signal is synchronous to TXCLK and provides precise framing for data carried on TXD[3-0] for the external PMD. It is asserted when TXD[3-0] contains valid data to be transmitted.                                                                                                                            |

| 100BASE-TX/                            | 10BASE-T Interf                        | ace               |                                                                                                                                                                                                                                                                                                                                            |

| TPTDP,<br>TPTDM                        | TPTDP,<br>TPTDM                        | 54,<br>53         | <b>Transmit Data:</b> Differential common output driver. This differential common output is configurable to either 10BASE-T or 100BASE-TX signaling:                                                                                                                                                                                       |

|                                        |                                        |                   | 10BASE-T: Transmission of Manchester encoded 10BASE-T packet data as well as Link Pulses (including Fast Link Pulses for Auto-Negotiation purposes).                                                                                                                                                                                       |

|                                        |                                        |                   | 100BASE-TX: Transmission of ANSI X3T12 compliant MLT-3 data.                                                                                                                                                                                                                                                                               |

|                                        |                                        |                   | The DP83815/16 will automatically configure this common output driver fo<br>the proper signal type as a result of either forced configuration or Auto-<br>Negotiation.                                                                                                                                                                     |

| TPRDP,<br>TPRDM                        | TPRDP,<br>TPRDM                        | 46,<br>45         | <b>Receive Data:</b> Differential common input buffer. This differential common input can be configured to accept either 100BASE-TX or 10BASE-T signaling:                                                                                                                                                                                 |

|                                        |                                        |                   | 10BASE-T: Reception of Manchester encoded 10BASE-T packet data as well as normal Link Pulses and Fast Link Pulses for Auto-Negotiation purposes.                                                                                                                                                                                           |

|                                        |                                        |                   | 100BASE-TX: Reception of ANSI X3T12 compliant scrambled MLT-3 data                                                                                                                                                                                                                                                                         |

|                                        |                                        |                   | The DP83815/16 will automatically configure this common input buffer to accept the proper signal type as a result of either forced configuration or Auto-Negotiation.                                                                                                                                                                      |

| 3                       |

|-------------------------|

| 2                       |

| က                       |

| $\overline{\mathbf{x}}$ |

| ÷                       |

| 4                       |

| ◄                       |

|                         |

| DP83815                                                                            | DP83816                                                                            | LQFP Pin<br>No(s)                                           | Description                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIOS ROM/Fla                                                                       | ish Interface                                                                      | <u></u>                                                     | <u>.</u>                                                                                                                                                                                                                                                                                                                                    |

| MCSN                                                                               | MCSN                                                                               | 129                                                         | BIOS ROM/Flash Chip Select: During a BIOS ROM/Flash access, this signal is used to select the ROM device.                                                                                                                                                                                                                                   |

| MD7,<br>MD6,<br>MD5,<br>MD4/EEDO,<br>MD3,<br>MD2,<br>MD1/CFGDISN,<br>MD0           | MD7,<br>MD6,<br>MD5,<br>MD4/EEDO,<br>MD3,<br>MD2,<br>MD1/CFGDISN,<br>MD0           | 141,<br>140,<br>139,<br>138,<br>135,<br>134,<br>133,<br>132 | <b>BIOS ROM/Flash Data Bus:</b> During a BIOS ROM/Flash access these signals are used to transfer data to or from the ROM/Flash device.<br>MD[5:0] pins have internal weak pull ups.<br>MD6 and MD7 pins have internal weak pull downs.                                                                                                     |

| MA5, MA4/<br>EECLK, MA3/<br>EEDI, MA2/<br>LED100K, MA1/<br>LED10N, MA0/<br>LEDACTN | MA5, MA4/<br>EECLK, MA3/<br>EEDI, MA2/<br>LED100K, MA1/<br>LED10N, MA0/<br>LEDACTN | 3,<br>2,<br>1,<br>144,<br>143,<br>142                       | <b>BIOS ROM/Flash Address:</b> During a BIOS ROM/Flash access, these signals are used to drive the ROM/Flash address.                                                                                                                                                                                                                       |

| MWRN                                                                               | MWRN                                                                               | 131                                                         | <b>BIOS ROM/Flash Write:</b> During a BIOS ROM/Flash access, this signal is used to enable data to be written to the Flash device.                                                                                                                                                                                                          |

| MRDN                                                                               | MRDN                                                                               | 130                                                         | <b>BIOS ROM/Flash Read:</b> During a BIOS ROM/Flash access, this signal is used to enable data to be read from the Flash device.                                                                                                                                                                                                            |

| Clock Interfac                                                                     | e                                                                                  | <u> </u>                                                    | <u>.</u>                                                                                                                                                                                                                                                                                                                                    |

| X1                                                                                 | X1                                                                                 | 17                                                          | <b>Crystal/Oscillator Input:</b> This pin is the primary clock reference input for the DP83815/16 and must be connected to a 25 MHz 0.005% (50ppm) clock source. The DP83815/16 device supports either an external crystal resonator connected across pins X1 and X2, or an external CMOS-level oscillator source connected to pin X1 only. |

| X2                                                                                 | X2                                                                                 | 18                                                          | <b>Crystal Output:</b> This pin is used in conjunction with the X1 pin to connect to an external 25 MHz crystal resonator device. This pin must be left unconnected if an external CMOS oscillator clock source is utilized. For more information see the definition for pin X1.                                                            |

| LED Interface                                                                      |                                                                                    |                                                             |                                                                                                                                                                                                                                                                                                                                             |

| LEDACTN/MA0                                                                        | LEDACTN/MA0                                                                        | 142                                                         | <b>TX/RX Activity:</b> This pin is an output indicating transmit/receive activity. This pin is driven low to indicate active transmission or reception, and can be used to drive a low current LED (<6 mA). The activity event is stretched to a min duration of approximately 50 ms.                                                       |

| LED100N/MA2                                                                        | LED100N/MA2                                                                        | 144                                                         | <b>100 Mb/s Link:</b> This pin is an output indicating the 100 Mb/s Link status. This pin is driven low to indicate Good Link status for 100 Mb/s operation, and can be used to drive a low current LED (<6 mA).                                                                                                                            |

| LED10N/MA1                                                                         | LED10N/MA1                                                                         | 143                                                         | <b>10 Mb/s Link:</b> This pin is an output indicating the 10 Mb/s Link status. This pin is driven low to indicate Good Link status for 10 Mb/s operation, and can be used to drive a low current LED (<6 mA).                                                                                                                               |

| Serial EEPRO                                                                       | M Interface                                                                        |                                                             |                                                                                                                                                                                                                                                                                                                                             |

| EESEL                                                                              | EESEL                                                                              | 128                                                         | <b>EEPROM Chip Select:</b> This signal is used to enable an external EEPROM device.                                                                                                                                                                                                                                                         |

| EECLK/MA4                                                                          | EECLK/MA4                                                                          | 2                                                           | <b>EEPROM Clock:</b> During an EEPROM access (EESEL asserted), this pin is an output used to drive the serial clock to an external EEPROM device.                                                                                                                                                                                           |

| EEDI/MA3                                                                           | EEDI/MA3                                                                           | 1                                                           | <b>EEPROM Data In:</b> During an EEPROM access (EESEL asserted), this pin is an output used to drive opcode, address, and data to an external serial EEPROM device.                                                                                                                                                                         |

| DP83815                                                                     | DP83816          | LQFP Pin<br>No(s)                               | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------|------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEDO/MD4                                                                    | EEDO/MD4         | 138                                             | <b>EEPROM Data Out:</b> During an EEPROM access (EESEL asserted), this pin is an input used to retrieve EEPROM serial read data.                                                                                                                                                                                                                                                                   |

|                                                                             |                  |                                                 | This pin has an internal weak pull up.                                                                                                                                                                                                                                                                                                                                                             |

| MD1/CFGDISN                                                                 | MD1/CFGDISN      | 133                                             | <b>Configuration Disable:</b> When pulled low at power-on time, disables load of configuration data from the EEPROM. Use 1 K $\Omega$ to ground to disable configuration load.                                                                                                                                                                                                                     |

| External Refe                                                               | erence Interface | ·                                               |                                                                                                                                                                                                                                                                                                                                                                                                    |

| VREF                                                                        | VREF             | 40                                              | Bandgap Reference: External current reference resistor for internal Phy bandgap circuitry.                                                                                                                                                                                                                                                                                                         |

|                                                                             |                  |                                                 | For the DP83815: The value of this resistor is 9.31 K $\Omega$ 1% metal film (100 ppm/ <sup>o</sup> C) which must be connected from the VREF pin to ground.                                                                                                                                                                                                                                        |

|                                                                             |                  |                                                 | For the DP83816: The value of this resistor is 10 K $\Omega$ 1% metal film (100 ppm/ <sup>o</sup> C) which must be connected from the VREF pin to ground                                                                                                                                                                                                                                           |

| No Connects                                                                 | and Reserved     |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    |

| NC                                                                          | NC               | 34, 42, 43                                      | No Connect                                                                                                                                                                                                                                                                                                                                                                                         |

| FXVDD,<br>SUBGND1,<br>VSSIO4,<br>VDDIO4,<br>MACVSS2,<br>MACVDD2,<br>SUBGND3 | NC               | 36,<br>37,<br>84,<br>85,<br>124,<br>125,<br>126 | <ul> <li>On DP83815: Connect pins 36, 37, 84, 85, 124, 125 and 126 to isolated Aux 3.3V supply VDD, GND, GND, Aux 3.3V supply VDD, GND, Aux 3.3V supply VDD, and GND respectively.</li> <li>On DP83816: These pins, that were previously supply pins on the DP83815, are now No Connects, and thus having them connected as they were previously on the DP83815 has no adverse effects.</li> </ul> |

| NC                                                                          | RESERVED         | 48                                              | On DP83815: No Connect                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             |                  |                                                 | <b>On DP83816:</b> Reserved and cannot be connected to any external logic or net.                                                                                                                                                                                                                                                                                                                  |

| RESERVED                                                                    | RESERVED         | 41, 50,<br>127                                  | Reserved and cannot be connected to any external logic or net.                                                                                                                                                                                                                                                                                                                                     |

| Supply Pins                                                                 |                  |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDIO2                                                                      | C1               | 19                                              | On DP83815: Connect to Aux 3.3V supply VDD                                                                                                                                                                                                                                                                                                                                                         |

|                                                                             |                  |                                                 | <b>On DP83816:</b> Connect to GND through 10uF and 0.1uF external parallel capacitors                                                                                                                                                                                                                                                                                                              |

| RXAVDD1,<br>RXAVDD2                                                         | IAUXVDD          | 39,<br>47                                       | Connect to isolated Aux 3.3V supply VDD                                                                                                                                                                                                                                                                                                                                                            |

| VDDIO1,<br>PHYVDD1,<br>VDDIO3,<br>PHYVDD2,<br>TXDVDD,<br>MACVDD1,<br>VDDIO5 | AUXVDD           | 9,<br>21,<br>27,<br>33,<br>56,<br>58,<br>137    | Connect to Aux 3.3V supply VDD                                                                                                                                                                                                                                                                                                                                                                     |

| PCIVDD1,<br>PCIVDD2,<br>PCIVDD3,<br>PCIVDD4,<br>PCIVDD5                     | PCIVDD           | 69,<br>80,<br>94,<br>107,<br>117                | PCI VDD - connect to PCI bus 3.3V VDD                                                                                                                                                                                                                                                                                                                                                              |

| DP83815   | DP83816 | LQFP Pin<br>No(s) | Description |

|-----------|---------|-------------------|-------------|

| VSSIO1,   | VSS     | 8,                | VSS         |

| VSSIO2,   |         | 16,               |             |

| VSSIO3,   |         | 20,               |             |

| PHYVSS1,  |         | 26,               |             |

| PHYVSS2,  |         | 32,               |             |

| FXVSS,    |         | 35,               |             |

| RXAVSS1,  |         | 38,               |             |

| RXAVSS2,  |         | 44,               |             |

| SUBGND2,  |         | 49,               |             |

| TXDVSS,   |         | 51,               |             |

| TXIOVSS1, |         | 52,               |             |

| TXIOVSS2, |         | 55,               |             |

| MACVSS1,  |         | 57,               |             |

| PCIVSS1,  |         | 65,               |             |

| PCIVSS2,  |         | 77,               |             |

| PCIVSS3,  |         | 90,               |             |

| PCIVSS4,  |         | 103,              |             |

| PCIVSS5,  |         | 114,              |             |

| VSSI05    |         | 136               |             |

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Č.

AN-1323

| 0       | National Semiconductor<br>Americas Customer<br>Support Center<br>Email: new.feedback@nsc.com<br>Tel: 1-800-272-9959 |

|---------|---------------------------------------------------------------------------------------------------------------------|

| www.nat | tional.com                                                                                                          |

- National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email:

europe.support@nsc.com

Deutsch

Tel:

+49 (0) 69 9508 6208

English

Tel:

+44 (0) 870 24 0 2171

Français

Tel:

+33 (0) 141 91 8790

- National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jon.feedback@nsc.com Tel: 81-3-5639-7560

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated