# DS91D176

## **Multipoint-LVDS (M-LVDS) Transceiver**

# **Evaluation Kit User Manual**

## Overview

The purpose of this document is to familiarize you with the DS91D176 evaluation board, suggest the test setup procedures and instrumentation, and to guide you through some typical measurements that will demonstrate the performance of the device.

The primary function of the board is to assist a system designer in development and analysis of an M-LVDS clock distribution network in an ATCA backplane. The board also enables the user to examine performance and all functions of the DS91D176 as a standalone device. As a side feature, one can utilize the board to access switch fabric interface of an ATCA backplane.

The DS91D176 is a high-speed M-LVDS differential transceiver designed for multipoint applications with multiple drivers or receivers. The device conforms to TIA/EIA-899 standard. It utilizes M-LVDS technology for low power, high-speed and superior noise immunity.

### Description

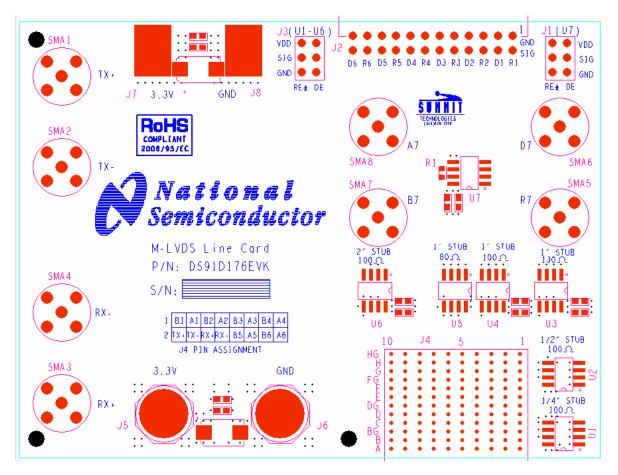

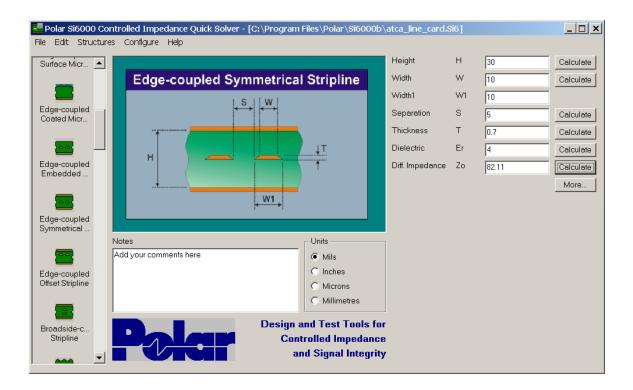

Figure 1 below represents the top layer drawing of the board with the silkscreen annotations. It is a 6 x 4 inch 10 layer printed circuit board (PCB) that features seven DS91D176 (U1-U7) devices.

Figure 1: DS91D176 Evaluation Board - Top View

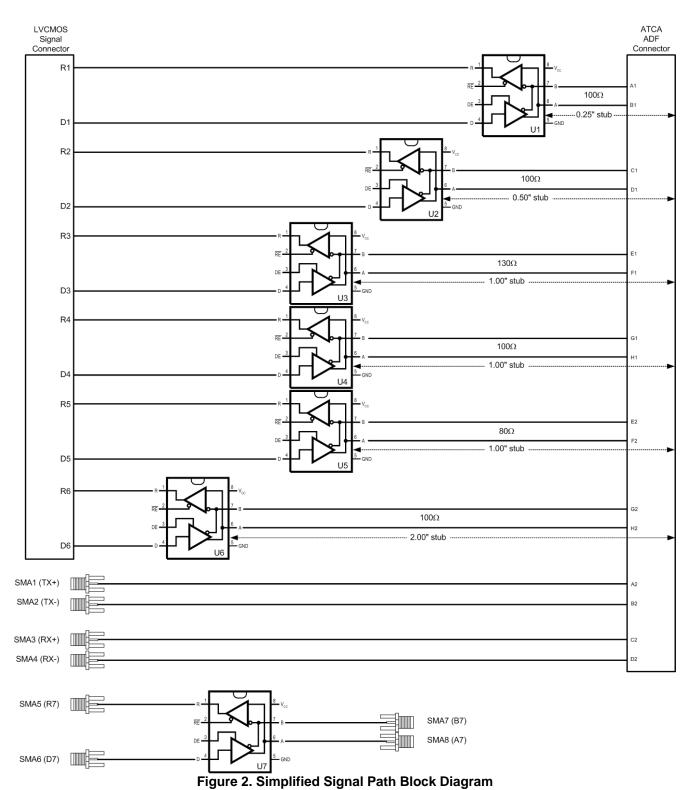

Devices U1 through U6 can serve as building blocks for M-LVDS clock distribution networks in ATCA backplanes. Their M-LVDS I/O pins directly connect to the first two row pins of J4, which is an ADF (Advanced Differential Fabric) connector. When J4 is inserted into any ATCA backplane slot (location J20/P20 for those of you familiar with ATCA backplanes), the M-LVDS I/O pins of each device electrically connect to one of the clock busses (there are six clock busses in an ATCA backplane – See Figure 3). The PCB traces that connect device M-LVDS pins with the J4 connector pins have different characteristics for each device. These traces are also

### DS91D176 Evaluation Board User Manual

called stubs. Table 1 provides characteristic of each stub, M-LVDS pins to J4 pin mapping and LVCMOS pins to J2 pins mapping.

| Device | M-LVDS Pins | J4 Pins | Stub Length | ZSTUB | LVCMOS Pins | J2 Pins |

|--------|-------------|---------|-------------|-------|-------------|---------|

| U1     | A1          | B1      | 0.25"       | 100 Ω | R1          | 2       |

|        | B1          | A1      |             |       | D1          | 4       |

| U2     | A2          | D1      | 0.50"       | 100 Ω | R1          | 6       |

|        | B2          | C1      |             |       | D1          | 8       |

| U3     | A3          | F1      | 1.00"       | 130 Ω | R1          | 10      |

|        | B3          | E1      |             |       | D1          | 12      |

| U4     | A4          | H1      | 1.00"       | 100 Ω | R1          | 14      |

|        | B4          | G1      |             |       | D1          | 16      |

| U5     | A5          | D2      | 1.00"       | 80 Ω  | R1          | 18      |

|        | B5          | C2      |             |       | D1          | 20      |

| U6     | A6          | B2      | 2.00"       | 100 Ω | R1          | 22      |

|        | B6          | A2      |             |       | D1          | 24      |

### Table 1: U1-U6 Stub Characteristics and Pin Mapping

J1 configures U1 through U6 as either driver or receiver.

J7 and J8 are power and ground banana plug receptacles. J5 and J6 are redundant power and ground connections.

U7 is for a standalone evaluation. Its I/O pins (both, M-LVDS and LVCMOS) connect to SMA connectors (SMA5-SMA8) for easy interface with instrumentation. J3 configures U7 as either driver or receiver. There is a provision to terminate M-LVDS inputs of the U7 with a SM0603 sized resistor.

Connectors, SMA1, SMA2, SMA3 and SMA4 connect to J4 pins H2, G2, F2 and E2 respectively. If the board is plugged in an ATCA backplane, locations J21/P21, J22/P22, J23/P23 and J24/P24 in any slot, fabric interface is accessed with these connectors.

Figure 2 provides a simplified block diagram view of the signal paths between the connecters and IC's.

### DS91D176 Evaluation Board User Manual

# Building an Evaluation M-LVDS Clock Distribution Network in an ATCA Backplane

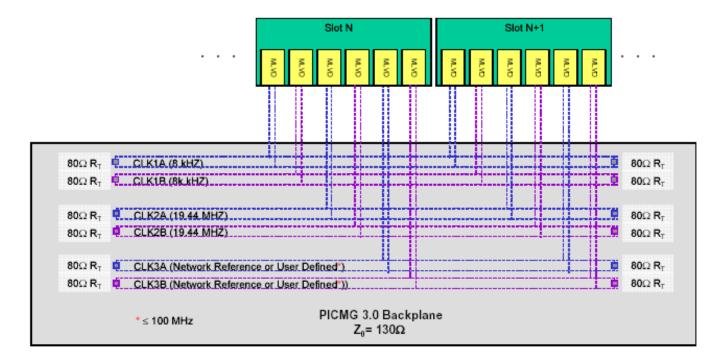

The following is a recommended procedure for building an evaluation M-LVDS clock distribution network with DS91D176 evaluation boards. The assumption is that the user already has an ATCA backplane. Figure 3 depicts configuration of a generic M-LVDS clock network in an ATCA backplane.

- 1. Use two or more DS91D176 evaluation boards and install them at backplane location J20/P20, in the desired slots.

- 2. Apply the power to the boards (3.3 V typical) between J7 and J8 banana plug receptacles, observe the value of I<sub>CC</sub>, and compare it with the expected value (refer to the datasheet) to ensure that the devices are functional.

- 3. Select the board you want to configure as a clock driver/distributor. This is accomplished by setting DE and RE\* pins to VDD (J1). Connect a clock generator to one of the driver inputs (J2).

- 4. Configure the remaining boards as clock receivers. This is accomplished by setting DE and RE\* pins to GND (J1).

- 5. Observe clock waveforms by either connecting receiver LVCMOS output pins (J1) directly to an oscilloscope or by probing receiver M-LVDS input pins with a differential probe.

### Figure 3. M-LVDS Clock Distribution Network in an ATCA Backplane

The above block diagram details the clock channels. They are all 130-ohm differential and doubly terminated with 80 ohms at either end of the backplane. The parallel combination of 80-ohm resistors means that the MLVDS devices will be driving a 40-ohm load termination. The maximum stub length from the backplane is defined in the ATCA standard as 1 inch or 2.5 cm.

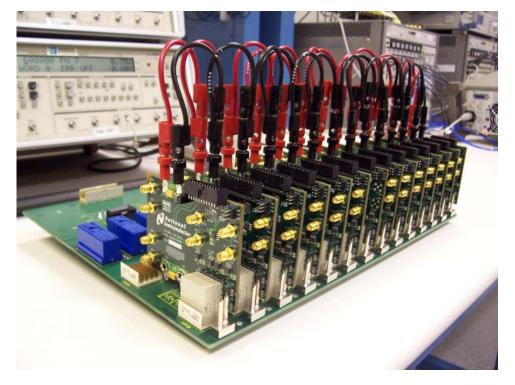

Figure 4 shows a picture of a 14-slot ATCA backplane fully populated with DS91D176 evaluation boards.

Figure 4. DS91D176 Evaluation Boards in an ATCA Backplane

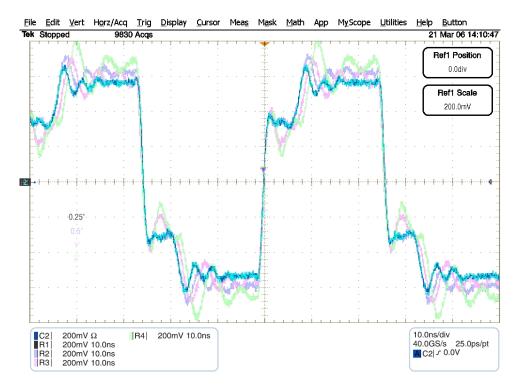

Figure 5 shows 19.44 MHz clock waveforms obtained with a differential probe, Tektronix P6330, on the M-LVDS input pins of U1, U2, U4 and U6 devices of the receiver board in slot #8. The14-Slot backplane was fully populated. The clock driver/distributor board was in slot #7.

Figure 5. 19.44 MHz Clock Waveforms Show Stub Length Effects on Signal Integrity

### **Building an Evaluation Point-Point Link with DS91D176 Evaluation Boards**

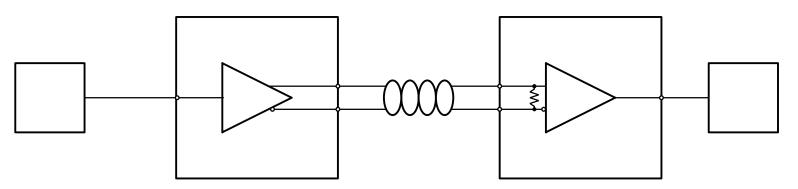

The following is a recommended procedure for building an evaluation M-LVDS point-point network with DS91D176 evaluation boards. Figure 6 depicts a typical setup and instrumentation used for evaluation of a point-to-point link.

- 1. Use two DS91D176 evaluation boards

- Apply the power to the boards (3.3 V typical) between J7 and J8 banana plug receptacles, observe the value of I<sub>CC</sub>, and compare it with the expected value (refer to the datasheet) to ensure that the devices are functional.

- 3. Configure U7 on one board as a driver. This is accomplished by setting DE and RE\* pins to VDD (J3). Connect a signal generator to the driver inputs (SMA6).

- 4. Configure U7 on the other board as a receiver. This is accomplished by setting DE and RE\* pins to GND (J3).

- 5. Select a differential interconnect with balanced 100-ohm differential impedance (i.e. UTP cable) and connect the M-LVDS pins of both devices with it.

- 6. Terminate the interconnect with a matching resistor on the inputs of U7 on the receiver board (R1).

- 7. Observe waveforms by either connecting the receiver LVCMOS output pins (SMA5) directly to an oscilloscope or by probing receiver M-LVDS input pins with a differential probe.

Figure 6. M-LVDS Point to Point Link with DS91D176 Boards and UTP Cable

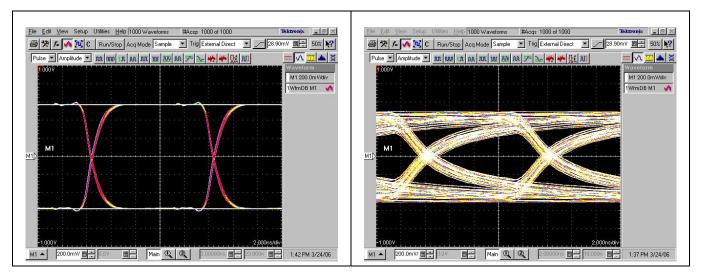

Figure 7 shows eye diagrams acquired at the output of the DS91D176 driver loaded with a 100-ohm resistor and after 50 m Cat5e cable terminated with a 100-ohm resistor. The generator connected to the driver input simulated a 100 Mb/s PRBS-7 NRZ.

Figure 7: Eye Diagram Before and After 50 m of Cat5e

## **Microstrip and Stripline Geometries Used**

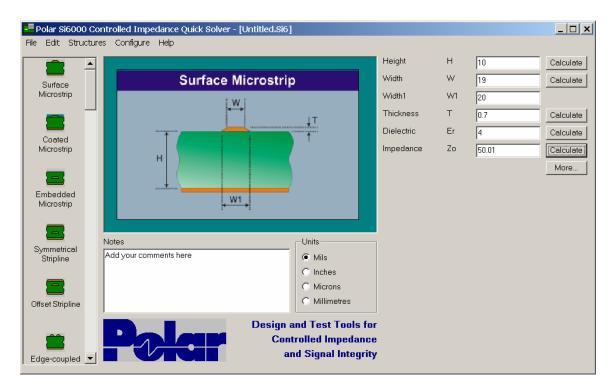

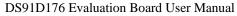

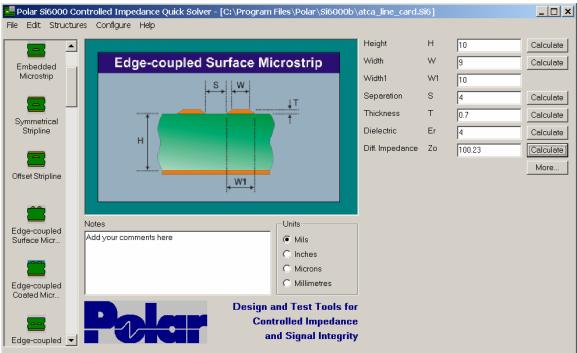

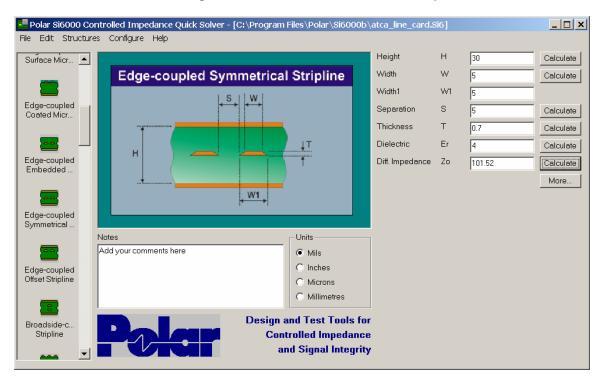

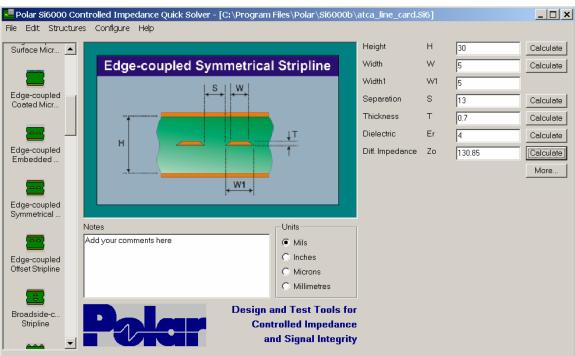

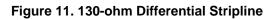

Figures 8 to 12 show trace geometries used in the board design. Table 2 provides trace type to electrical net cross-reference.

| Trace Type / Figure                        | DS91D176 Evaluation Board Nets |  |

|--------------------------------------------|--------------------------------|--|

| 50-ohm Single-ended Microstrip / Figure 8  | All LVCMOS nets                |  |

| 100-ohm Differential Microstrip / Figure 9 | U7 M-LVDS nets, SMA1-SMA4 nets |  |

| 100-ohm Differential Stripline / Figure 10 | U1, U2, U4, U6 M-LVDS nets     |  |

| 130-ohm Differential Stripline / Figure 11 | U3 M-LVDS nets                 |  |

| 80-ohm Differential Stripline / Figure 12  | U5 M-LVDS nets                 |  |

Table 2: Trace Type to Electrical Net Cross-reference.

Figure 8. 50-ohm Single-ended Microstrip

Figure 10. 100-ohm Differential Stripline

Figure 12. 80-ohm Differential Stripline

## Layer Stack Up:

| 1/2 oz   |          | SIG1   |

|----------|----------|--------|

|          | 10 mills |        |

| 1/2 oz   |          | -GND   |

|          | 15 mills |        |

| 1/2 oz   |          | SIG2   |

|          | 15 mills | 0. V.D |

| 1/2 oz   |          | -GND   |

| 1/2      | 3 mills  |        |

| 1/2 02   | 3 mills  |        |

| 1/2 07   |          | PWR    |

| ., _ 02. | 3 mills  |        |

| 1/2 oz   |          | -GND   |

|          | 15 mills |        |

| 1/2 oz   |          | SIG3   |

|          | 15 mills |        |

| 1/2 oz   |          | GND    |

|          | 10 mills |        |

| 1/2 oz   |          | SIG4   |

## **Bill Of Materials**

| Item | Quant | ity Reference                                 | Part                             |

|------|-------|-----------------------------------------------|----------------------------------|

|      |       |                                               |                                  |

| 1    | 2     | C18, C1                                       | 22u; SM7343; C1 Not Installed;   |

| 2    | 9     | C2, C4, C5, C6, C7, C8, C9, C10,<br>C19       | 0.1u; SM0603; C2 Not Installed;  |

| 3    | 9     | C3, C11, C12, C13, C14, C15,<br>C16, C17, C20 | 0.01u; SM0603; C3 Not Installed; |

| 4    | 2     | J3, J1                                        | Molex 90131-0123                 |

| 5    | 1     | J2                                            | Molex 90130-3124                 |

| 6    | 1     | J4                                            | Tyco HM-ZD 1469001-1             |

| 7    | 2     | J5, J6                                        | Pomona 3267; Not Installed;      |

| 8    | 1     | J7                                            | Johnson Components 108-0902-001  |

| 9    | 1     | J8                                            | Johnson Components 108-0903-001  |

| 10   | 4     | SMA1, SMA2, SMA3, SMA4,                       | Not Installed;                   |

| 11   | 4     | SMA5, SMA6, SMA7, SMA8                        | Johnson Components 142-0701-231  |

| 11   | 7     | U1, U2, U3, U4, U5, U6, U7                    | DS91D176TMA                      |

| 12   | 1     | R1                                            | 50; SM0603; Not Installed;       |

## **Revision History**

Revision 0.1: Initial draft – dglisic 12Apr2006 Revision 0.2: Minor edits, added simplified block diagram – bstearns 14 April2006

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        | TI 505 0                        |                               |                                   |

**TI E2E Community Home Page**

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated