# AN-1254 DDR-SDRAM Termination Simplified Using a Linear Regulator

#### **ABSTRACT**

This applications report describes the use and benefits of the LP2995 for DDR-DRAM Termination.

|   | Contents                                        |     |

|---|-------------------------------------------------|-----|

| 1 | Stub Series Termination Logic (SSTL)            | . 2 |

| 2 | Synchronous PWM Buck Controller                 | . 3 |

| 3 | LP2995 Typical Application Circuit              | . 4 |

|   | List of Figures                                 |     |

| 1 | Implementation of Stub Series Termination Logic | 2   |

| 2 | Synchronous PWM Switcher Topology               | 3   |

| 3 | LP2995 Typical Application Circuit              | 4   |

## 1 Stub Series Termination Logic (SSTL)

With the advent of DDR-SDRAM as the industry standard for memory in desktop computers, laptops and videocards, power management has become a focal point for system designers. Active termination of bus interconnects has required the use of another regulator, increasing cost and system complexity. To specifically address this issue, Texas Instruments has released the LP2995 DDR Termination Linear Regulator, offering a linear topology in a marketplace dominated by switchers. The implementation of this architecture has been made possible by careful examination of the system requirements.

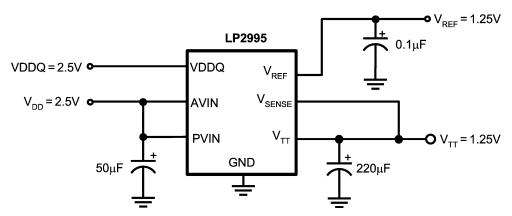

With the memory migration from SDRAM to DDR-SDRAM, higher bus speeds and data transfer rates are attainable. As a consequence of the increased bandwidth, transmission problems have begun to appear. The length of the memory interconnects, coupled with the multiple stubs that are required for supporting DIMMs result in signal reflection causing data corruption. This problem has required more attention as speeds have increased from DDR200 (100MHz clock) to DDR266 (133MHz clock) to the newly released DDR333 (166MHz clock). Concerned with the integrity of the signals at these high frequencies, JEDEC sought to create an industry standard for low voltage, high speed signaling as an improvement over LV<sub>TTL</sub>. The result was an active termination scheme called SSTL (Stub Series Termination Logic), see Figure 1.

The JEDEC definition of SSTL-2 for 2.5V memory called for an active termination using a  $V_{TT}$  output voltage. This voltage is required to track a reference, VREF, which is created by dividing the memory power rail exactly in half. With the JEDEC specification defining the voltage tolerance on the individual rails, power delivery calculations have been left to the system designers. It is easily identifiable that  $V_{TT}$  needs to sink and source current, the problem is determining the magnitude. Historically, numbers were generated based on a macroscopic viewpoint of the system using static worst-case conditions. These approximate calculations defined the solution, by stating the following requirements:

- V<sub>TT</sub> must sink and source current

- Maximum output current is 3A

Figure 1. Implementation of Stub Series Termination Logic

### 2 Synchronous PWM Buck Controller

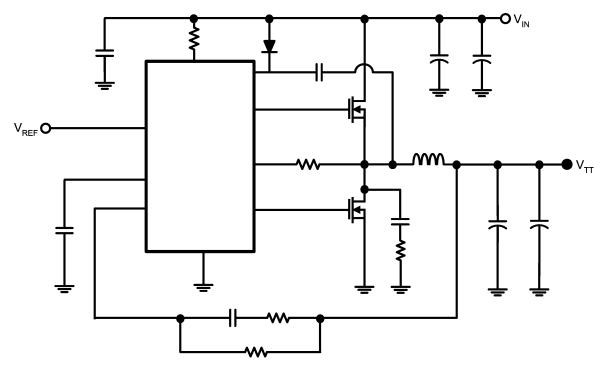

Based on this definition, only one clear choice existed: a synchronous switcher had to be used. To meet these exacting requirements a plethora of switchers were designed to tackle this exact application from various manufacturers. The end solution was typically a synchronous PWM buck controller. A representation of a typical circuit implementing this topology can be seen in Figure 2.

Figure 2. Synchronous PWM Switcher Topology

The synchronous buck switcher, while providing a feasible solution does not present an ideal or even optimal DDR termination regulator. Limitations exist that are inherent with the topology and the practical implementation. Several examples include:

**Board Space:** Due to the complexity of this solution a controller with high pin count is required to drive two external MOSFETs. Coupled with an inductor and the associated capacitors this implementation can occupy a significant amount of board area. This can be extremely critical in laptops and videocards where real estate is at a premium.

Cost: The high component count required for the application translates directly into increased cost.

**Performance** The most fundamental requirement for any DDR termination regulator is performance. While the task of creating a 1.25V reference signal within a +/-200mV window is trivial, the challenge in designing a switching power supply is limiting the switching noise and EMI. Signal interference resulting in data loss is possible if switching harmonics are present on the bus. Though not impossible to limit, it poses an increase in cost and development time to reduce the effects.

The initial assumption that 3A were required for the maximum output current, resulting in the selection of the buck switcher, was actually an oversight. The cause of this problem was that the worst-case conditions were incorrect resulting in over design of the regulator. To counter this problem, Texas Instruments approached the power delivery calculations from a memory architecture and control point of view to define an entirely new solution. From an in-depth analysis of the PC memory it becomes apparent that 3A are not required.

The exact analysis is not included in this application report due to length, however, several of the key points have been highlighted:

- DDR-SDRAM is a dynamic system, static assumptions of a 133MHz clock (266MHz data rate) are not realistic when applied to the regulator requirements.

- Theoretical peak calculations are not obtainable for sustained durations. Data cannot be clocked every

edge indefinitely. Delays such as CAS latencies are an important assessment in every memory

access.

- Significant current cancellation can occur from complementary signals such as data strobes.

- Two line conditions are insufficient for a complete model, tri-stating and transitional periods need to be incorporated.

- · Even periodic refresh affects the average output current required by the regulator.

### 3 LP2995 Typical Application Circuit

Coupled with technical analysis, confirmed by empirical measurements, Texas Instruments found that the average currents required are closer to 200mA. Worse case conditions, simulated by intensive memory burn-in tests, result in little deviation from this figure. This new design target meant that an entirely new topology can be used: LINEAR, bestowing all its advantages.

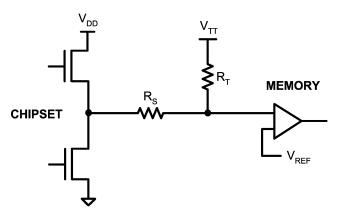

Leveraging the results found from the measurements, Texas Instruments addressed the shortcomings of the switcher topology and created a new standard in DDR bus termination by releasing the LP2995. The LP2995 utilizes an exclusive linear topology to create the  $V_{TT}$  output voltage and the reference output, VREF, for the chipset and DIMMs. A typical application circuit for the LP2995 can be seen in Figure 3.

Figure 3. LP2995 Typical Application Circuit

Re-examining the limitations of the switcher and comparing it to the LP2995, the benefits of a linear topology are immediately recognizable.

**Size:** The external component count has been drastically reduced, permitting the solution to occupy a minimal amount of space. Combined with the LP2995 in an LLP package (Leadless Leadframe Package) an optimal solution can be obtained.

Cost: Removal of the external components creates an instant system cost reduction by 60%.

**Performance:** By its nature as a linear topology, there is no internal oscillator or switching noise to take into consideration. This results in increased performance, as data integrity can be improved with the absence of switching noise on  $V_{TT}$ .

Through careful analysis of the actual memory requirements Texas Instruments was able to provide the optimal solution for DDR termination, the LP2995. Designed with consideration of the end user it offers the highest level of integration while increasing the system performance and lowering the total system cost. The LP2995 offers the perfect solution for any DDR-SDRAM application where space, performance and cost are critical constraints.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### **Products Applications**

power.ti.com

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

**RFID** www.ti-rfid.com

Power Mgmt

**OMAP Applications Processors** www.ti.com/omap **TI E2E Community** e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity