# AN-1413 LM3205 Evaluation Board

#### 1 Introduction

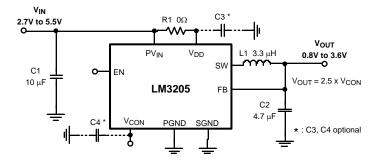

The LM3205 evaluation board is a working demonstration of a step down DC-DC converter. This document contains information about the evaluation board and board layout considerations. For further information on buck converter topology, device electrical characteristics, and component selection, see the *LM3205 650mA Miniature, Adjustable, Step-Down DC-DC Converter for RF Power Amplifiers Data Sheet* (SNVS388).

#### 2 General Description

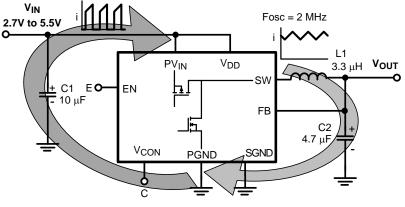

The LM3205 is a DC-DC converter optimized for powering RF power amplifiers (RFPAs) from a single Lithium-Ion cell, however, the device may be used in many other applications. The LM3205 steps down an input voltage range from 2.7 V to 5.5 V to a variable output voltage range from 0.8 V to 3.6 V. Output voltage is set using a  $V_{CON}$  analog input for controlling power levels and efficiency of the RFPA.

The LM3205 offers superior performance for mobile phones and similar RFPA applications. Fixed-frequency pulse width modulation (PWM) operation minimizes RF interference. Shutdown function turns the device off and reduces battery consumption to 0.01 µA (typ).

The LM3205 is available in a 8-pin lead free DSBGA package. A high switching frequency (2 MHz) allows use of tiny surface-mount components. Only three small external components are required: an inductor and two ceramic capacitors.

## 3 Operating Conditions

- $V_{IN}$  range: 2.7 V  $\leq V_{IN} \leq 5.5$  V

- $V_{CON}$  range: 0.32 V  $\leq V_{CON} \leq 1.44$  V

- $V_{OUT}$  equation:  $V_{OUT} = 2.5 \text{ x } V_{CON}$

- $I_{OUT}$  range: 0 mA $\leq I_{OUT} \leq 650$  mA

## 4 Typical Application

All trademarks are the property of their respective owners.

1

www.ti.com

Evaluation Board Layout

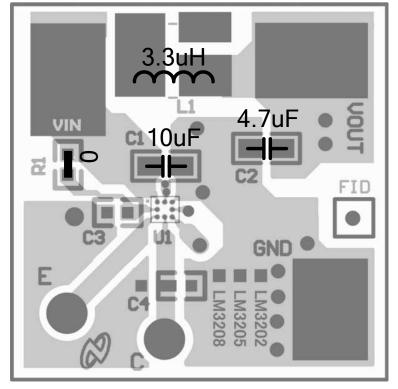

# 5 Evaluation Board Layout

Figure 1. Top Layer

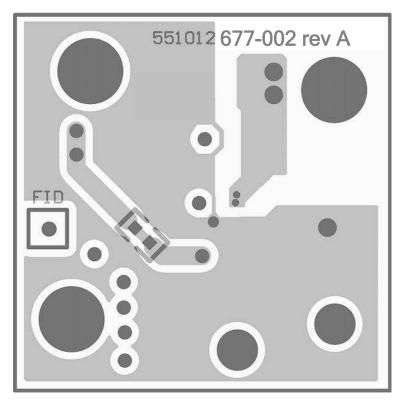

## Figure 2. Bottom Layer

www.ti.com

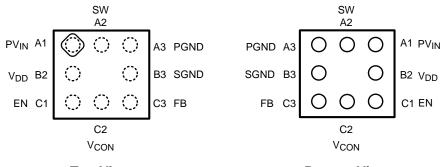

## 6 Connection Diagram and Package Mark Information

Top View

Bottom View

#### Table 1. Pin Descriptions

| Pin No | Name             | Description                                                                                                                                                                                                                      |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | PVIN             | Power supply voltage Input to the internal PFET switch.                                                                                                                                                                          |

| B1     | V <sub>DD</sub>  | Analog supply input.                                                                                                                                                                                                             |

| C1     | EN               | Enable input. Set this digital input high for normal operation. For shutdown, set low.                                                                                                                                           |

| C2     | V <sub>CON</sub> | Voltage control analog input. V <sub>CON</sub> controls V <sub>OUT</sub> in PWM mode.                                                                                                                                            |

| C3     | FB               | Feedback analog input. Connect to the output at the output filter capacitor.                                                                                                                                                     |

| B3     | SGND             | Analog and control ground                                                                                                                                                                                                        |

| A3     | PGND             | Power ground                                                                                                                                                                                                                     |

| A2     | SW               | Switch node connection to the internal PFET switch and NFET synchronous rectifier.<br>Connect to an inductor with a saturation current rating that exceeds the maximum Switch Peak Current<br>Limit specification of the LM3205. |

| Table 2. Bill of Materials (E | BOM) For ( | Common Confi | gurations |

|-------------------------------|------------|--------------|-----------|

|-------------------------------|------------|--------------|-----------|

|                                                  | Manufacture        | Manufacture No | Description                               |

|--------------------------------------------------|--------------------|----------------|-------------------------------------------|

| C1 (input C)                                     | TDK                | C2012X5R0J106M | 10 µF, 6.3 V, 20%,0805                    |

| C2 (output C)                                    | TDK                | C1608X5R0J475M | 4.7 μF, 6.3 V, 20%,0603                   |

| C3 (optional, input C)                           |                    |                | 0.1 μF, 25 V , 0402 <sup>(1)</sup>        |

| C4 (optional, filter for V <sub>CON</sub> )      |                    |                | 10 - 100 pF, 25 V , 0402 <sup>(1)</sup>   |

| L1 (inductor)                                    | Taiyo-Yuden        | NR3015T3R3M    | 3.3 μH, 1210 mA, 3x3x1.5 mm               |

| R1 (jumper PV <sub>IN</sub> to V <sub>DD</sub> ) | Vishay             | CRCW04020R00F  | 0 Ω, 0402                                 |

| V <sub>IN</sub> banana jack - red                | Johnson Components | 108-0902-001   | connector, insulated banana jack (red)    |

| V <sub>out</sub> banana jack - yellow            | Johnson Components | 108-0907-001   | connector, insulated banana jack (yellow) |

| GND banana jack - black                          | Johnson Components | 108-0903-001   | connector, insulated banana jack (black)  |

<sup>(1)</sup> C3 and C4 are recommended for a better noise performance.

3

#### Board Layout Considerations

www.ti.com

#### 7 Board Layout Considerations

Figure 4. Current Loop

The LM3205 converts higher input voltage to lower output voltage with high efficiency. This is achieved with an inductor-based switching topology. During the first half of the switching cycle, the internal PMOS switch turns on and the input voltage is applied to the inductor in which the current flows from  $PV_{DD}$  line to the output capacitor (C2) through the inductor. During the second half cycle, the PMOS turns off and the internal NMOS turns on. The inductor current continues to flow via the inductor from the device PGND line to the output capacitor (C2).

Referring to Figure 4, the LM3205 has two major current loops where pulse and ripple current flow. The loop shown in the left hand side is important because pulse current flows in this path. In the loop on the right hand side, the current waveform in this path is triangular. Pulse current has many high-frequency components due to fast di/dt. Triangular ripple current also has wide high-frequency components. Board layout and circuit pattern design of these two loops are key factors for reducing noise radiation and achieiving stable operation. Other lines, such as input and output terminals are DC current, therefore, pattern width (current capability) and DCR drop considerations are needed.

## 7.1 Board Layout Flow

- 1. Minimize C1, PV<sub>IN</sub>, and PGND loop. These traces should be as wide and short as possible.

- 2. Minimize L1, C2, SW and PGND loop. These traces also should be as wide and short as possible.

- The layout patterns should be placed on the component side of the printed circuit board (PCB) to minimize parasitic inductance and resistance due to via-holes. SW to L1 path should be routed between C2(+) and C2(-) land patterns. If vias are used in these large current paths, multiple via-holes should be used if possible.

- 4. Connect C1(-), C2(-) and PGND with wide GND pattern. This pattern should be short, so C1(-), C2(-), and PGND are as close as possible. Then connect to a PCB common GND pattern with as many viaholes as possible.

- 5. SGND should not be connect directly to PGND. Connecting these pins under the device should be avoided. (If possible, connect SGND to the common port of C1(-), C2(-) and PGND.)

- 6.  $V_{DD}$  should not be connected directly to  $PV_{IN}$ . Connecting these pins under the device should be avoided. It is recommended to connect  $V_{DD}$  to the C1(+) to avoid switching noise injection to the  $V_{DD}$  line.

- 7. FB line should be protected from noise. It is recommended to use an inner GND layer (if available) as a shield.

- **NOTE:** The evaluation board shown in Figure 1 and Figure 2 for the LM3205 was designed with the considerations mentioned above, and it shows good performance. However some aspects have not been optimized because of limitations due to evaluation-specific requirements. The board can be used as a reference. For specific questions, contact a Texas Instruments representative.

4

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated