# AN-2070 AVS Adaptor Board for USB AVS System Mainboards

## 1 AVS Adaptor Board for USB AVS System Mainboards

The AVS Adaptor Board (AAB) is not intended for standalone use, but rather to enable interconnect of non-PEK/SPEK footprint daughterboards to Texas Instruments PowerWise/SPMI System Mainboards. The AAB provides a means to plug in TI's evaluation boards with the modified DOSA style connector, the proprietary MAK style connector, or the standard 1x9 SIP interface. The AAB provides various power supply options for bench evaluation, and several jumper options to support the desired setup.

## 2 Evaluation Board Overview

The AAB is, for the most part, a passive board. The vast majority of its functionality is to appropriately route power and signals from the system mainboard and/or bench equipment to the DUT. The only active circuitry on the board is a low-power LDO which can be used to provide the PWI/SPMI I/O signaling voltage. Because of the flexibility designed into the board, you must be very careful with the jumper set-up of the board stack to ensure no damage is done to any of the circuitry. While it would be impossible to cover all combinations of board stacks, great effort will be taken to provide a method/procedure to ensure that the boards can be configured without damaging anything.

All trademarks are the property of their respective owners.

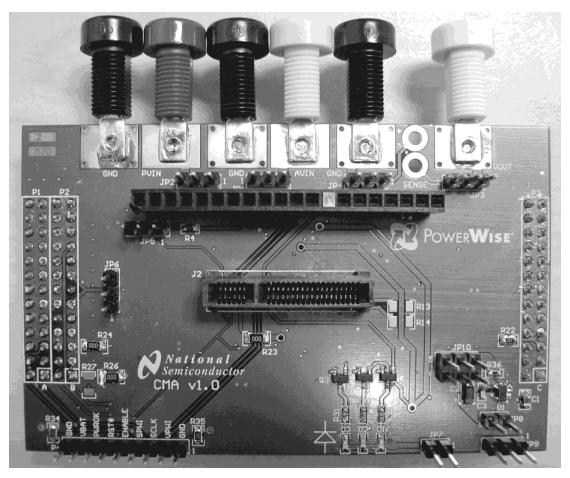

Figure 1. AVS Adaptor Board

# 3 LM10000 Evaluation Board Quick Start

A typical set up using AAB requires a Texas Instruments AVS System Mainboard, the AAB, and a compliant evaluation board to make up the board stack. The board is driven from a PC with a GUI that is tailored to the evaluation board and DUT. The system mainboard connects to the PC via USB. The board stack can be entirely standalone and powered from USB for quick evaluation/demo purposes, or can be powered from a bench supply for more thorough testing of the regulator(s).

#### 3.1 Basic Setup

- 1. Set the appropriate jumpers for power supply on the chosen system board. Details of the supply can be found in the documentation for that TI system board.

- 2. Plug the AAB into the system board...

- 3. Set the jumpers on the AAB per the following tables.

- 4. Plug the DUT board into the AAB.

- 5. Follow the associated documentation for the device you are working with as to power up sequence and special GUI considerations. As a general rule though, you want any external/bench supplies to be on prior to plugging in the USB cable.

- 6. Plug in the USB cable of the TI system board and follow the documentation pertaining to that device and GUI.

There are many jumper options on the AAB to allow it to perform in as many roles as possible. Great care must be taken in setting up the jumpers prior to applying power to avoid damaging the boards in the board stack. The jumpers and their purpose is explained here:

| Jumper                        | Purpose                                                                   | Note                                                                                                       |  |

|-------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| JP1                           | Selects the power source for AVIN.<br>AVIN is typically used to power the | 1-2: AVIN is supplied via the system mainboard's "VBAT" input; DEFAULT.                                    |  |

|                               | power supply's control electronics.                                       | 2-3: AVIN is supplied via the YELLOW banana jack on the AAB.                                               |  |

| JP2                           | Selects the power source for PVIN.<br>PVIN is typically used to power the | 1-2: PVIN is supplied via the system mainboard's "VBAT" input; DEFAULT.                                    |  |

| JF2                           | power electronics of the power supply.                                    | 2-3: PVIN is supplied via the RED banana jack on the AAB.                                                  |  |

| JP3 (+Sense) and JP4 (-Sense) | Selects either local feedback for the                                     | 1-2: The regulated sense point will be based on the remote sense points labeled "Sense" in the silkscreen. |  |

| sense lines or remote sense.  |                                                                           | 2-3: The regulated sense point for the supply will occur at the WHITE banana jack; DEFAULT.                |  |

| JP5                           | ENABLE pull-up/pull-down strap.                                           | 1-2: ENABLE is pulled-up to AVIN via 10K.                                                                  |  |

| JF5                           | ENABLE puil-up/puil-down strap.                                           | 2-3: ENABLE is pulled-down to GND via 10K.                                                                 |  |

| JP6                           | Selects the PWI/SPMI sideband (signals other than the 2-wire data and     | 1-2: Referenced to the "VBAT" supply from the system board; depends on what that supply is set to.         |  |

|                               | clock) I/O level reference.                                               | 2-3: Referenced to the same voltage as the PWI/SPMI signals, "VPWI"; DEFAULT.                              |  |

| JP7                           | LED supply On/Off. The LEDs are powered from the system board             | On: With the jumper installed, the LED indicators will be functional; DEFAULT.                             |  |

|                               | "VBAT".                                                                   | Off: LEDs are disabled.                                                                                    |  |

| JP8                           | Short out on-board "VPWI" regulator.                                      | On: U1, the "VPWI" LDO will be shorted. This will make "VPWI" equal to the system board "VBAT".            |  |

| JF0                           | Short out on-board ve will regulator.                                     | Off: "VPWI" can be generated on-board or elsewhere; DEFAULT.                                               |  |

| JP9                           | VPWI" regulator On/Off.                                                   | 1-2: "VPWI" LDO is enabled; DEFAULT.                                                                       |  |

|                               |                                                                           | 2-3: "VPWI" LDO is disabled.                                                                               |  |

|                               |                                                                           | 1-2: 3.3V; DEFAULT.                                                                                        |  |

| JP10                          | 'VPWI'' regulator output voltage selection.                               | 3-4: 2.5V.                                                                                                 |  |

|                               |                                                                           | 5-6: 1.8V.                                                                                                 |  |

## 3.2 Interconnects

There are several ways to connect to/from the AAB board. The board will nearly always be paired with a system mainboard that will connect via P1, P2, and P3. These are male pin headers on the bottom side of the board that allow the board to plug down into the standard mainboard footprint. The AAB itself then breaks out the required power and signal traces to the appropriate locations on the interconnects.

LM10000 Evaluation Board Quick Start

www.ti.com

J1 is the modified DOSA-style interconnect. It leverages the DOSA Standard for Non-Isolated 9.6 – 14.4VIN, 15/16/20A DC/DC converters. It is completely backwards compatible with existing DOSA style parts, but expands upon the connector footprint to add in PWI/SPMI functionality. The pinout is in the below table:

| DOSA Pin Number | AAB Pin Number    | Function             |  |

|-----------------|-------------------|----------------------|--|

| 1               | 1                 | VOUT                 |  |

| 2               | 2                 | VOUT                 |  |

| 3               | 3                 | SENSE                |  |

| 4               | 4                 | VOUT                 |  |

| 5               | 5                 | GND                  |  |

|                 | 6                 | GND                  |  |

|                 | 7                 | GND                  |  |

|                 | < <key>&gt;</key> | Mechanical Key       |  |

|                 | 8                 | SCLK                 |  |

|                 | 9                 | SPWI                 |  |

|                 | 10                | VPWI                 |  |

|                 | 11                | AVIN                 |  |

|                 | 12                | PGOOD                |  |

| A               | 13                | I Share - Not Routed |  |

| 6               | 14                | GND                  |  |

| 7               | 15                | VIN                  |  |

| 8               | 16                | VIN                  |  |

| В               | 17                | SEQ - Not Routed     |  |

| 9               | 18                | TRIM - Not Routed    |  |

| 10              | 19                | ON/OFF               |  |

J2 is the "MAK" connector that is utilized to connect to a few TI DUT boards. It is a vertical edge-card socket strip. Its use is relegated to a couple of very specific applications and will not be detailed here. For further details, see the device-specific schematics and DUT documentation.

The last major connector is P4. This 1x9 SIP connector has been on the vast majority of TI AVS products for several years. It allows a convenient means to access most of the major signals involved in the PWI/SPMI interface, and can also be used to cable across to an external AVS setup to provide the proper signaling environment. The P4 pinout is found in the following table:

| Pin Number | Function | Description                              |  |

|------------|----------|------------------------------------------|--|

| 1          | GND      | System ground                            |  |

| 2          | VPWI     | VPWI voltage                             |  |

| 3          | SCLK     | Serial clock                             |  |

| 4          | SPWI     | Serial data                              |  |

| 5          | ENABLE   | Regulator enable                         |  |

| 6          | RST#     | Regulator reset (active low)             |  |

| 7          | PWROK    | Regulator output of power okay indicator |  |

| 8          | VBAT     | Mainboard "VBAT" voltage                 |  |

| 9          | GND      | System ground                            |  |

## 3.3 Indicator LEDS

When JP7 is ON and the indicator LEDs are enabled, they have the following functionality:

| Ref Des | Color  | Description                     |

|---------|--------|---------------------------------|

| D1      | Red    | AVIN is powered up              |

| D2      | Yellow | VPWI is powered up              |

| D3      | Green  | The PWROK signal is driven high |

- R26 and R27 can be used either as a voltage divider for the output voltage or as a RC for the ADC converter on the system mainboard. By default, R26 is shorted and R27 is open, but you can mount these as desired. You must ensure that the VOUT fed back to the mainboard does NOT exceed 3.3V for the USB Interface Board or 1.8V for the PEK/SPEK. VOUTs above this should be divided down to appropriate levels.

- If "VPWI" is provided externally by you in some fashion, care should be taken to disable U1 (set JP9 to 2-3) and open JP8. Additionally, you should make sure that the provided "VPWI" does NOT exceed the mainboard "VBAT" by more than 1 diode drop or current may flow from "VPWI" to "VBAT". "VBAT" is dependent upon the system board used and the settings applied to it.

## 4 Bill of Materials (BOM)

| Qty | Designator                           | Value               | Description                      | Mfg. P/N                       |

|-----|--------------------------------------|---------------------|----------------------------------|--------------------------------|

| 1   | AVIN                                 | Yellow Banana Jack  | Yellow Nylon Banana<br>Jack      | Emerson 108-0907-001           |

| 1   | C1                                   | 1µF/35V/X7R         |                                  | T-Y GMK212B7105KG-T            |

| 1   | C2                                   | 2.2µF/10V/20%/Tant  | VPWI C <sub>OUT</sub>            | Nichicon F931A225MAA           |

| 1   | СЗ                                   | 7pF/50V/C0G         | VPWI Feedback<br>Bypass          | TDK C1608C0G1H070D             |

| 1   | D1                                   | LS L29K-H1J2-1-Z    | Red LED for AVIN<br>Indicator    | OSRAM LS L29K-H1J2-<br>1-Z     |

| 1   | D2                                   | LY L29K-J1K2-26-Z   | Yellow LED for VPWI<br>Indicator | OSRAM LY L29K-J1K2-<br>26-Z    |

| 1   | D3                                   | LG L29K-G2J1-24-Z   | Green LED for<br>PGOOD Indicator | OSRAM LG L29K-G2J1-<br>24-Z    |

| 3   | GND, GND2, GND3                      | Black Banana Jack   | Black Nylon Banana<br>Jack       | Emerson 108-0903-001           |

| 1   | J1                                   | DOSA Receptacle     | 1x20 100-mil<br>Receptacle       | Тусо 6-534237-8                |

| 1   | J1-Key                               | DOSA Receptacle Key | Key to make pin 8 inaccessible   | Тусо 86286-1                   |

| 1   | J2                                   | Samtec HSEC8        | MAK Connector<br>Receptacle      | Samtec HSEC8-125-01-<br>S-DV-A |

| 7   | JP1, JP2, JP3, JP4, JP5,<br>JP6, JP9 | 1x3, 100-mil Header | 1x3 100-mil Jumper               | Molex 90120-0763               |

| 2   | JP7, JP8                             | 1x2, 100-mil Header | 1x2 100-mil Jumper               | Molex 90120-0762               |

| 1   | JP10                                 | 2x3, 100-mil Header | VPWI Voltage Select<br>Jumper    | Molex 90131-0763               |

| 3   | P1, P2, P3                           | A28694-ND           | Baseboard Connectors             | Тусо 1-87227-3                 |

| 1   | P4                                   | 1x9, 100-mil Header | 1x9 PWI Access<br>Header         | Molex 90120-0769               |

| 1   | PVIN                                 | Red Banana Jack     | Red Nylon Banana<br>Jack         | Emerson 108-0902-001           |

| 3   | Q1, Q2, Q3                           | NDS331N             | Logic NFET                       | Fairchild NDS331N              |

| 4   | R1, R22, R34, R35                    | 10R/0.25W/5%        | Fuse Rs                          | Rohm ESR10EZPJ100              |

#### Table 1. Bill of Materials (BOM)

| Qty | Designator                                                                                    | Value             | Description                | Mfg. P/N                        |

|-----|-----------------------------------------------------------------------------------------------|-------------------|----------------------------|---------------------------------|

| 2   | R2, R3                                                                                        | 1.5K/0.1W/1%      | Presence Detect Rs         | Rohm<br>MCR03EZPFX1501          |

| 2   | R4, R9                                                                                        | 10K/0.1W/1%       | ENABLE P-U/P-D             | Stackpole RMCF 1/16<br>10K 1% R |

| 18  | R5, R6, R7, R8, R10, R11,<br>R12, R15, R16, R17, R18,<br>R19, R20, R21, R23, R24,<br>R25, R26 | 0R/0.25W          | Pad shorts                 | Vishay<br>CRCW12060000Z0EA      |

| 3   | R13, R14, R27                                                                                 | No Load           | Open pads                  | N/A                             |

| 1   | R28                                                                                           | 53.6K/0.1W/1%     | 2.5V VPWI Divider R        | Panasonic ERJ-<br>3EKF5362V     |

| 3   | R29, R30, R31                                                                                 | 1.6K/0.1W/1%      | LED Current Limit R        | Yageo RC0603FR-<br>071K6L       |

| 1   | R32                                                                                           | 86.6K/0.1W/1%     | 3.3V VPWI Divider R        | Panasonic ERJ-<br>3EKF8662V     |

| 1   | R33                                                                                           | 24.0K/0.1W/1%     | 1.8V VPWI Divider R        | Panasonic ERJ-<br>3EKF2402V     |

| 1   | R36                                                                                           | 51.1K/0.1W/1%     | LS VPWI Divider R          | Panasonic ERJ-<br>3EKF5112V     |

| 2   | TP1, TP2                                                                                      | No Load           | Remote Sense pads          | N/A                             |

| 1   | U1                                                                                            | LP2980            | VPWI Adjust LDO            | Texas Instruments<br>LP2980     |

| 1   | VOUT                                                                                          | White Banana Jack | White Nylon Banana<br>Jack | Emerson 108-0901-001            |

| 9   | Jumper Shunts Installed<br>Per Golden Sample                                                  | 1x2 Shunt         | Jumper                     | Sullins SPC02SYAN               |

Table 1. Bill of Materials (BOM) (continued)

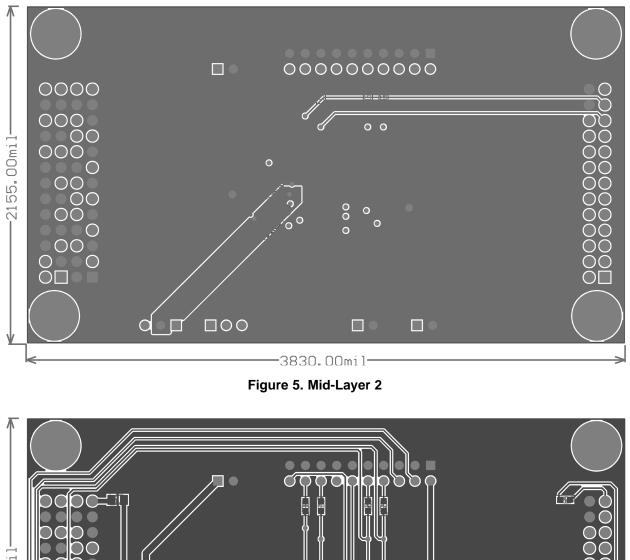

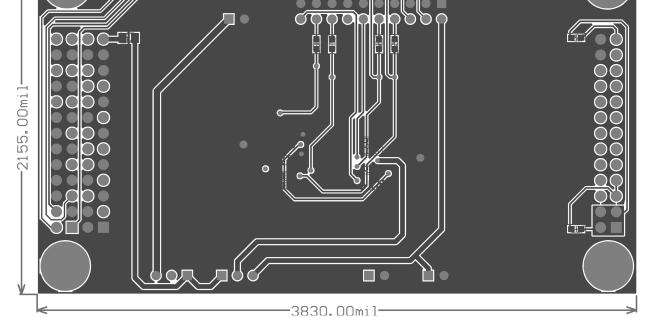

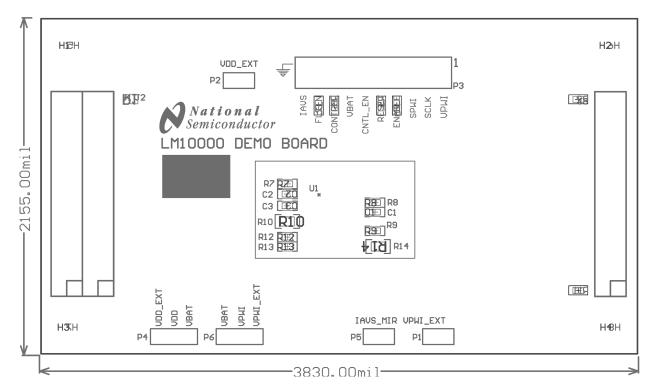

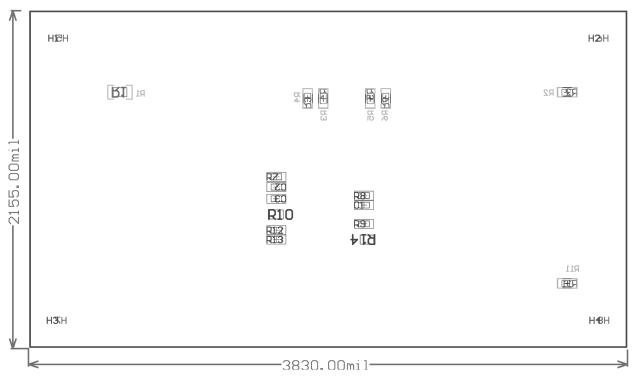

# 5 Layout Artwork

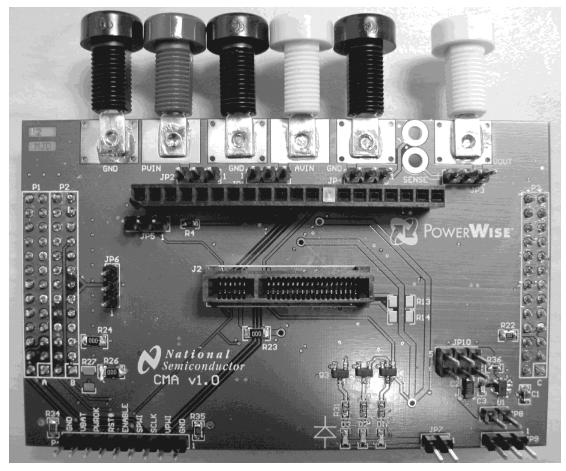

Figure 2. Evaluation Board (Top View)

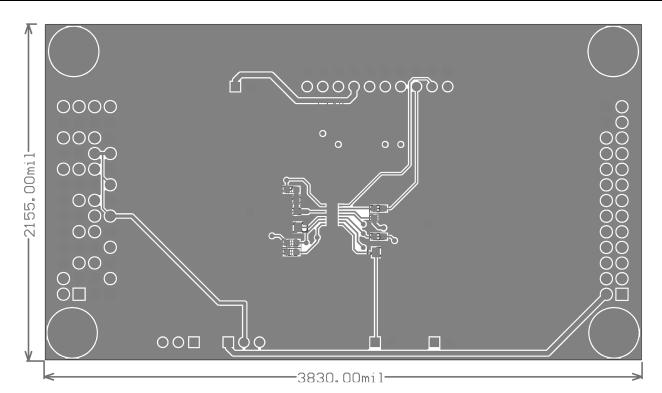

Figure 3. Top Layer

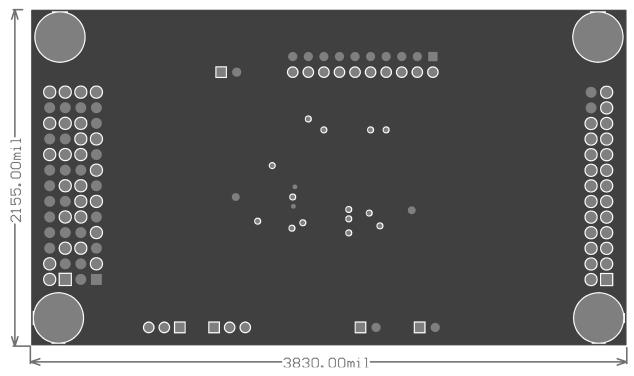

Figure 6. Bottom Layer

Figure 7. Top Silk Screen

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated