# LM4132, LM4132-Q1 Pin FMEA

### Marcoo Zamora

### **ABSTRACT**

The LM4132 family of precision voltage references performs comparably to the best laser-trimmed bipolar references, but in cost-effective CMOS technology. Unlike other LDO references, the LM4132 can deliver up to 20 mA and does not require an output capacitor or buffer amplifier.

#### **Contents** 2 3 LM4132 Pin Configurations and Functions 3 4 **List of Figures** 1 2 **List of Tables** 1 2 3 4

### **Trademarks**

All trademarks are the property of their respective owners.

### 1 Pin FMEA

This application provides Failure Modes and Effects Analysis (FMEA) for the device pins of the LM4132 and LM4132-Q1 voltage reference. The failure conditions covered in this document include the typical pin-by-pin failure scenarios:

- · Pin short-circuited to Ground;

- Pin is open circuited;

- Pin short-circuited to LM4132 V<sub>IN</sub>; and

- Pin short-circuited to an adjacent pin.

This application note also details how these pin conditions affect the device:

- Does the pin condition cause permanent damage?

- Is the device is functional under the pin condition?

- How does a particular pin condition affect the device operation?

Scope www.ti.com

## 2 Scope

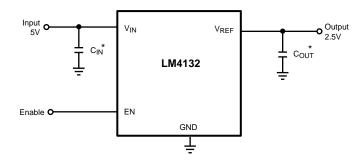

The LM4132 is a series voltage reference that provides low power consumption because it does not have to idle the maximum possible load current under no-load conditions. This device also comes with an enable pin for disabling the LM4132. The LM4132 has two functional states:

- Enabled, where the output voltage is enabled through the EN pin and is regulated to a specific value within a range of output load currents.

- Disabled, where the output voltage is disabled through the EN pin.

In many applications, the EN pin is isolated from the VIN pin voltage by a control device.

For the purposes of this report:

- Unless otherwise specified, the voltage applied to the VIN pin and EN pin is within the LM4132 Recommended Operating Range.

- The EN pin is driven from an external source.

- Functionality = Yes indicates that the LM4132 status can be remotely changed between the two functional states (ENABLED and DISABLED) by the external control connected to the EN pin.

## 3 LM4132 Pin Configurations and Functions

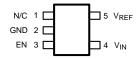

Figure 1. 5-Pin SOT-23 Package (Top View)

Figure 2. Typical LM4132 Schematic

## **Pin Functions**

| PIN    |      | I/O | DESCRIPTION                     |  |  |

|--------|------|-----|---------------------------------|--|--|

| NUMBER | NAME | 1/0 | DESCRIPTION                     |  |  |

| 1      | N/C  | _   | No connect pin, leave floating. |  |  |

| 2      | GND  | G   | Ground                          |  |  |

| 3      | EN   | I   | Enable pin                      |  |  |

| 4      | VIN  | I   | Input supply                    |  |  |

| 5      | VREF | 0   | Reference output                |  |  |

FMEA Analysis www.ti.com

## 4 FMEA Analysis

Table 1. Pin FMEA Analysis for Pin Short Circuit to Ground

| PIN    |      | SHORT TO V <sub>IN</sub> |                                                                      |                                                                                                                |  |

|--------|------|--------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME | DAMAGE                   | AGE FUNCTIONAL COMMENTS                                              |                                                                                                                |  |

| 1      | N/C  | No                       | Yes In the actual application, make sure N/C pin is always floating. |                                                                                                                |  |

| 2      | GND  | No                       | Yes                                                                  | No effect.                                                                                                     |  |

| 3      | EN   | No                       | No                                                                   | No output voltage. Output is forced OFF.                                                                       |  |

| 4      | VIN  | No                       | No                                                                   | No output voltage.                                                                                             |  |

| 5      | VREF | No                       | No                                                                   | No, or low, output voltage. Output current is at short-circuit curre limit; thermal shutdown may be activated. |  |

## Table 2. Pin FMEA Analysis for Pin Open Circuit

| PIN    |      | SHORT TO V <sub>IN</sub> |               |                                                     |  |  |

|--------|------|--------------------------|---------------|-----------------------------------------------------|--|--|

| NUMBER | NAME | DAMAGE                   | FUNCTIONAL    | IONAL COMMENTS                                      |  |  |

| 1      | N/C  | No                       | Yes No effect |                                                     |  |  |

| 2      | GND  | No                       | No            | Output is not regulated.                            |  |  |

| 3      | EN   | No                       | No            | EN pin is floating and its state is indeterminable. |  |  |

| 4      | VIN  | No                       | No            | No output voltage.                                  |  |  |

| 5      | VREF | No                       | No            | No output voltage to load.                          |  |  |

## Table 3. Pin FMEA Analysis for Pin Short Circuit to $V_{\mbox{\scriptsize IN}}$

| PIN    |      | OPEN   |                                                           |                                                                                                                |  |  |

|--------|------|--------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER | NAME | DAMAGE | FUNCTIONAL COMMENTS                                       |                                                                                                                |  |  |

| 1      | N/C  | No     | Yes In actual application, make sure N/C pin is floating. |                                                                                                                |  |  |

| 2      | GND  | No     | No                                                        | No output voltage.                                                                                             |  |  |

| 3      | EN   | No     | No                                                        | Output forced ON.                                                                                              |  |  |

| 4      | VIN  | No     | Yes                                                       | No effect.                                                                                                     |  |  |

| 5      | VREF | No     | No                                                        | No VREF regulation. Output voltage is same as input voltage. Power supply might experience a current increase. |  |  |

## Table 4. Pin FMEA Analysis for Pin Short Circuit to an Adjacent Pin

| PIN    |      | SHORT TO PIN |      | SHORT TO ADJACENT PIN |            |                                                                  |  |

|--------|------|--------------|------|-----------------------|------------|------------------------------------------------------------------|--|

| NUMBER | NAME | NUMBER       | NAME | DAMAGE                | FUNCTIONAL | COMMENTS                                                         |  |

| 1      | N/C  | 2            | GND  | No                    | Yes        | In the actual application, make sure N/C pin is always floating. |  |

| 2      | GND  | 3            | EN   | No                    | No         | No output voltage. Output is forced OFF.                         |  |

| 3      | EN   | 4            | VIN  | No                    | No         | Output forced ON.                                                |  |

| 4      | VIN  | 5            | VREF | No                    | No         | No VREF regulation. Output voltage is same as input voltage.     |  |

| 5      | VREF | 1            | N/C  | No                    | Yes        | In actual application, make sure N/C pin is floating.            |  |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated