## Application Report **Power Supply Design for Mobileye EyeQ4 High Using** LP875761-Q1

## TEXAS INSTRUMENTS

Tomi Koskela

#### ABSTRACT

This document details the design considerations of a power management unit solution for the Mobileye EyeQ4<sup>®</sup> High SoC (system-on-chip) core rail using the LP875761-Q1 power management IC. This power solution assumes an input voltage of 3.3 V or 5 V ( $\pm$ 5%). If the system input voltage is higher, for example a car battery, a buck converter as a pre-regulator should be used to generate a supply voltage of 3.3 V or 5 V.

The LP875761A-Q1 has 4 buck converters configured to work as single 1 V output multiphase converter. LP875761 operates in PWM mode with all 4 phases switching in interleaved mode when output is activated.

## **Table of Contents**

| Design Parameters               | 2  |

|---------------------------------|----|

| Power Solution                  | 2  |

| Schematic                       | 3  |

| Layout                          | 4  |

| Layout                          | 4  |

| 4.2 Example Layout              | 5  |

| Recommended External Components | 8  |

| Measurements                    | 8  |

| Conclusion                      | 11 |

| References                      |    |

#### Trademarks

EyeQ4<sup>®</sup> is a registered trademark of Mobileye N.V.. All trademarks are the property of their respective owners.

## **1 Design Parameters**

Design target parameters for the EyeQ4 High core rail power is show in Table 1-1 and typical measurement data is seen in Section 6.

| DESIGN PARAMETER           | VALUE                                                                       |  |  |  |

|----------------------------|-----------------------------------------------------------------------------|--|--|--|

| VIN                        | 3.3 V / 5 V (±5%)                                                           |  |  |  |

| V <sub>OUT</sub>           | 1 V                                                                         |  |  |  |

| I <sub>OUT</sub>           | 12 A max (LP875761A-Q1 supports up to 16 A load current)                    |  |  |  |

| V <sub>OUT</sub> tolerance | ±3% in all conditions including DC accuracy and load transient              |  |  |  |

| Load transient             | 8 A/µs, 4 A to 12 A to 4 A                                                  |  |  |  |

| C <sub>IN</sub> (nom)      | At least 10 µF capacitor per phase                                          |  |  |  |

| C <sub>OUT</sub> (nom)     | 144 µF total capacitance per phase, including point of load capacitors      |  |  |  |

| C <sub>OUT</sub> (min)     | 100 $\mu$ F total capacitance per phase, including point of load capacitors |  |  |  |

| C <sub>OUT</sub> (max)     | 1500 µF total, all phases combined, including point of load capacitors      |  |  |  |

| L (nom)                    | 330 nH, at least 3.5 A saturation current                                   |  |  |  |

| Phase margin               | >45°                                                                        |  |  |  |

| Gain margin                | >10 dB                                                                      |  |  |  |

#### Table 1-1. Design Parameters

### 2 Power Solution

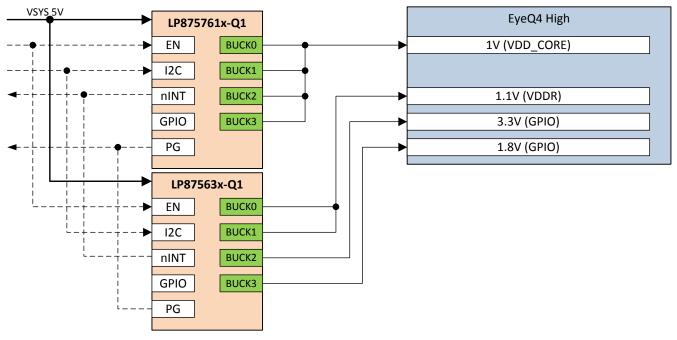

Figure 2-1 shows an example block diagram of LP875761-Q1 device powering the EyeQ4 High core rail, and LP87563x PMIC powering the other required rails. PMIC from the LP87563x family could be configured to power the other rails depending on use case.

#### Figure 2-1. EyeQ4 High Power Solution Block Diagram

After the devices are powered, the microcontroller can set the EN pin high to enable the PMIC. Startup delay of the LP875761ARNFRQ1 has been set to 0 ms. Full OTP register settings of LP875761ARNFRQ1 can be found in *LP875761A-Q1 Technical Reference Manual*. I<sup>2</sup>C can be used to read status registers and reset interrupts.

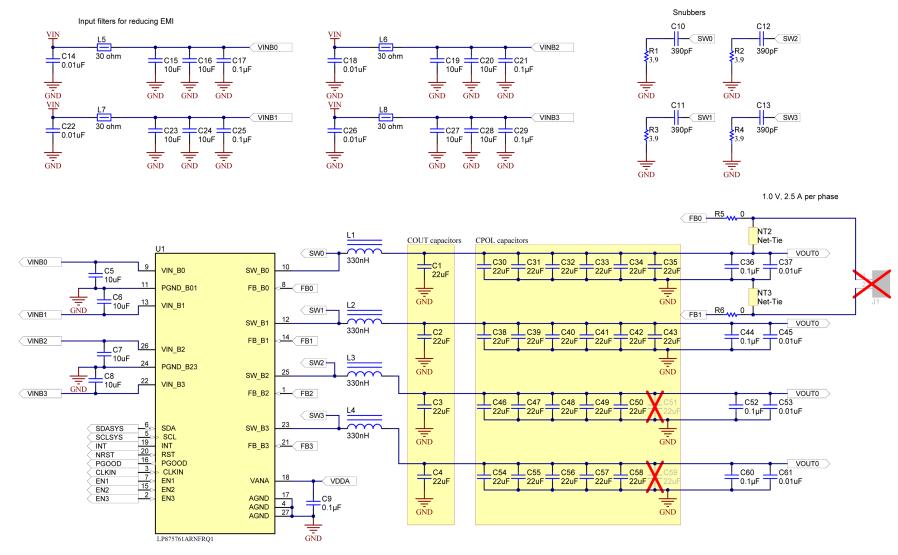

## **3 Schematic**

LP875761-Q1 schematic with critical components is shown in Figure 3-1. Input EMI filters are optional. Snubbers are needed when input voltage of the system is >4 V, otherwise they are optional.

# 4 Layout

Layout

## 4.1 Layout Considerations

The high frequency and large switching currents of the LP875761-Q1 make the choice of layout important. Good power supply results only occur when care is given to correct design and layout. Layout affects noise pickup and generation and can cause a good design to perform with less-than-expected results. With a range of output currents from milliamps to 16 A and over, a good power supply layout is much more difficult than most general PCB design. Use the following steps as a reference to make sure the device is stable and keeps the correct voltage and current regulation across its intended operating voltage and current range.

- Place each CIN as close as possible to the VIN\_Bx pin and the PGND\_Bxx pin. Input capacitors are placed

on the bottom side of the board to help with the layout routing in the example layout. Use multiple vias with a

high enough current rating, and route the VIN trace wide and thick to avoid IR drops. The trace between the

positive node of the input capacitor and one or more of the VIN\_Bx pins of LP875761-Q1, as well as the trace

between the negative node of the input capacitor and one or more of the power PGND\_Bxx pins, must be

kept as short as possible. The input capacitance provides a low-impedance voltage source for the switching

converter. The inductance of the connection is the most important parameter of a local decoupling capacitor

parasitic inductance can be decreased by using a ground plane as close as possible to the top and bottom

layer by using a thin dielectric layer between the top and bottom layer and the ground plane.

- The output filter, consisting of COUT and L, converts the switching signal at SW\_Bx to the noiseless output voltage. It must be placed as close as possible to the device keeping the switch node small, for best EMI behavior. Route the traces between the LP875761-Q1 output capacitors and the load direct and wide to avoid losses due to the IR drop.

- Input for analog blocks (VANA and AGND) must be isolated from noisy signals. Connect VANA directly to a quiet system voltage node and AGND to a quiet ground point where no IR drop occurs. Place the decoupling capacitor as close as possible to the VANA pin.

- Connect the feedback pins FB\_Bx of the LP875761-Q1 device to the respective sense pins on the processor if the processor load supports remote voltage sensing. In any case connect the feedback pin FB\_B0 to the supply terminal of the point-of-load, and the feedback pin FB\_B1 to the GND of the point-of-load. This compensates for the IR drop from the buck output to the point-of-load and on the GND. The sense lines are susceptible to noise, so they must be kept away from noisy signals such as PGND\_Bxx, VIN\_Bx, and SW\_Bx, as well as high bandwidth signals such as the I<sup>2</sup>C. Avoid both capacitive and inductive coupling by keeping the sense lines short, direct, and close to each other. Run the lines in a quiet layer. Isolate them from noisy signals by a voltage or ground plane if possible. Running the signal as a differential pair is recommended for multiphase outputs.

- PGND\_Bxx, VIN\_Bx, and SW\_Bx must be routed on thick layers. They must not surround inner signal layers, which cannot withstand interference from noisy PGND\_Bxx, VIN\_Bx, and SW\_Bx.

- Place snubber components (capacitor and resistor) between SW\_Bx and ground on all four phases if the input voltage is above 4 V. The components can be also placed to the other side of the board if there are area limitations and the routing traces can be kept short.

- Due to the small package of this converter and the overall small solution size, the thermal performance of the PCB layout is important. Many system-dependent parameters such as thermal coupling, airflow, added heat sinks, convection surfaces, and the presence of other heat-generating components affect the power dissipation limits of a given component. A correct PCB layout, focusing on thermal performance, results in lower die temperatures. Wide and thick power traces can sink dissipated heat. This can be further improved on multilayer PCB designs with vias to different planes. This results in decreased junction-to-ambient ( $R_{\theta JA}$ ) and junction-to-board ( $R_{\theta JB}$ ) thermal resistances, thereby decreasing the device junction temperature, T<sub>J</sub>. TI strongly recommends doing a careful system-level 2D or full 3D dynamic thermal analysis at the beginning of the product design process, by using a thermal modeling analysis software.

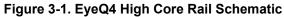

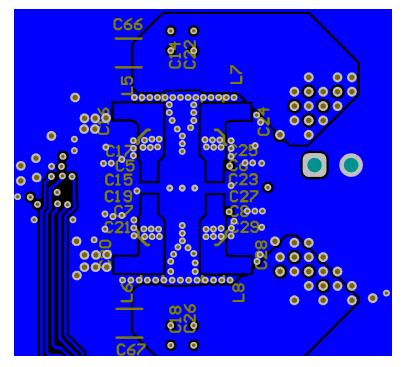

LP875761-Q1 Layout from LP875761Q1EVM with critical components is shown in this section. See *The LP875761Q1EVM (BMC043) Evaluation Module* for more details.

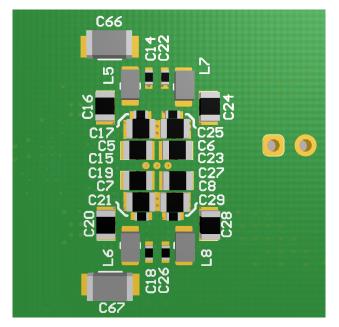

Figure 4-1. LP875761-Q1 Top Component Placement

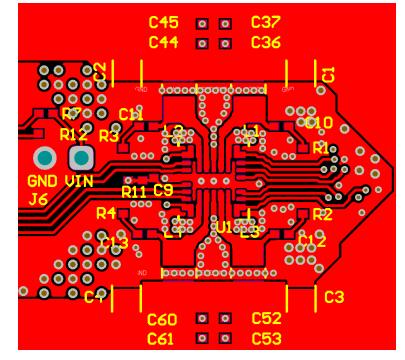

Figure 4-2. LP875761-Q1 Bottom Component Placement

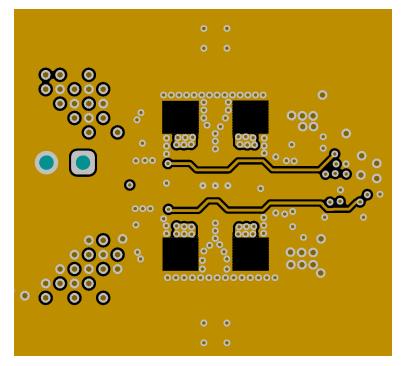

Figure 4-3. LP875761-Q1 Layout, Layer 1

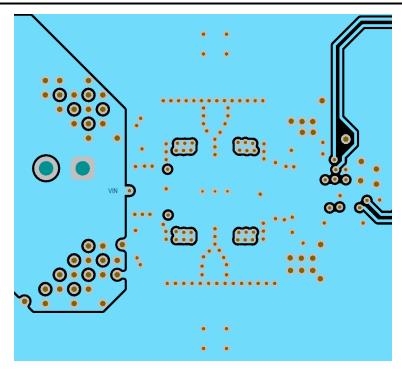

Figure 4-4. LP875761-Q1 Layout, Layer 2

Figure 4-5. LP875761-Q1 Layout, Layer 3

## **5** Recommended External Components

See Table 5-1 for the recommended external components to use in this solution with the LP875761-Q1. It also shows the total solution size including the PMIC device and the external components.

| SYSTEM COMPONENT      | COUNT | VALUE   | SIZE       | PART NUMBER          | MANUFACTURER | BOARD SIZE <sup>(1)</sup> |  |

|-----------------------|-------|---------|------------|----------------------|--------------|---------------------------|--|

| PMIC                  | 1     | -       | 4.5 x 4 mm | LP875761ARNFRQ1      | TI           | 27.5 mm <sup>2</sup>      |  |

| Buck input capacitor  | 4     | 10 µF   | 0805       | GCM21BR71A106KE22L   | Murata       | 27 mm <sup>2</sup>        |  |

| Buck output inductor  | 4     | 0.33 µH | 1008       | DFE252012PD-R33M     | Murata       | 42 mm <sup>2</sup>        |  |

| Buck output capacitor | 26    | 22 µF   | 1206       | GCM31CR71A226KE02    | Murata       | 283.9 mm <sup>2</sup>     |  |

| Buck output capacitor | 4     | 100 nF  | 0402       | GCM155R71C104JA55D   | Murata       | 12 mm <sup>2</sup>        |  |

| Buck output capacitor | 4     | 10 nF   | 0402       | GCM155R71H103KA55D   | Murata       | 12 mm <sup>2</sup>        |  |

| VANA supply capacitor | 1     | 100 nF  | 0402       | GCM155R71C104JA55D   | Murata       | 3 mm <sup>2</sup>         |  |

| Snubber resistor      | 4     | 3.9 Ω   | 0402       | CRCW04023R90JNED     | Vishay-Dale  | 12 mm <sup>2</sup>        |  |

| Snubber capacitor     | 4     | 390 pF  | 0402       | CGA2B2C0G1H391J050BA | TDK          | 12 mm <sup>2</sup>        |  |

| TOTAL                 | 52    | -       | -          | -                    | -            | 431.4 mm <sup>2</sup>     |  |

|       |      | <b></b> |    |           |

|-------|------|---------|----|-----------|

| lable | 5-1. | BIII    | OŤ | Materials |

(1) Assuming 1 mm keep-out around each component, and multiplying by component count.

#### 6 Measurements

Test data can be found in the Application Curves section of the *LP875761-Q1 Four-Phase 3-MHz 1-V 16-A DC/DC Buck Converter With Integrated Switches Datasheet.*

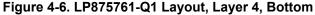

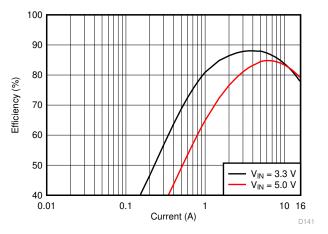

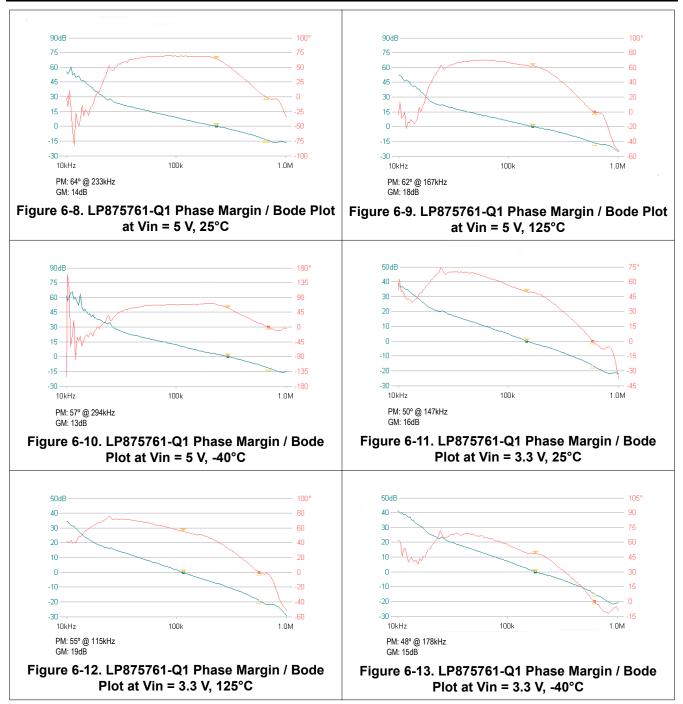

Additional bench test data for load transient response, efficiency, and phase margin can be seen in this section at different input voltages.

Measurements were taken on LP875761Q1EVM with default components. For load transient a special high speed amplifier controlled current sink was used to realize 4 A to 12 A to 4 A transient with 1  $\mu$ s slew rate (8A /  $\mu$ s).

Control loop response (Bode plot) was measured with Keysight MSOX6004A oscilloscope.

Figure 6-1. LP875761-Q1 Efficiency at Vin = 5 V and Vin = 3.3 V

### 7 Conclusion

With this presented solution with LP875761-Q1 the output voltage accuracy requirement is met for EyeQ4 High application processor while maintaining good efficiency. Phase margin is over 50° in all measured conditions which shows good stability of the control loop. Table 7-1 shows combined data for the critical parameters.

| Table 7-1. Results                                                                                                             |                                      |                                            |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------|--|--|--|

| Parameter                                                                                                                      | Result                               | Comment                                    |  |  |  |

| DC output voltage accuracy,<br>includes voltage reference, DC<br>load and line regulations,<br>process, and temperature effect | Within ±10 mV                        | ±1.0% with 1 V output voltage              |  |  |  |

| Transient load step response 4 A<br>to 12 A to 4 A. 8 A/µs                                                                     | Within ±20 mV                        | ±2% with 1 V output voltage                |  |  |  |

| Total accuracy including DC +<br>transient                                                                                     | Within ±30 mV                        | ±3% with 1 V output voltage                |  |  |  |

| Efficiency                                                                                                                     | 88% at 4 A load, VIN = 3.3 V         |                                            |  |  |  |

| Phase margin                                                                                                                   | 50 – 64° depending on condition      | >45° is considered good design target      |  |  |  |

| Gain margin                                                                                                                    | 13 – 19 dB depending on condition    | >10 dB is considered as good design target |  |  |  |

| Bandwidth                                                                                                                      | 114 – 294 kHz depending on condition |                                            |  |  |  |

#### 8 References

See these references for additional information:

- 1. Texas Instruments, LP875761-Q1 Four-Phase 3-MHz 1-V 16-A DC/DC Buck Converter With Integrated Switches Datasheet

- 2. Texas Instruments, LP875761A-Q1 Technical Reference Manual

- 3. Texas Instruments, The LP875761Q1EVM (BMC043) Evaluation Module

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated