**TPS7H4010-SEP** SNVSBL0A - NOVEMBER 2020 - REVISED DECEMBER 2021

# TPS7H4010-SEP Radiation Hardened 3.5-V to 32-V, 6-A Synchronous **Step-Down Voltage Converter in Space Enhanced Plastic**

# 1 Features

- Radiation Hardened

- SEL, SEB, and SEGR immune up to  $LET = 43 \text{ MeV-cm}^2/\text{mg}$

- SET and SEFI characterized up to LET = 43 MeV-cm<sup>2</sup>/mg

- TID assured for every wafer lot up to 20 krad(Si)

- TID characterized up to 30 krad(Si)

- Space Enhanced Plastic

- Controlled baseline

- Au bondwire and NiPdAu lead finish

- Enhanced mold compound for low outgassing

- One fabrication, assembly and test site

- Extended product life cycle

- Extended product change notification

- Product traceability

- Wide voltage conversion range:

- $t_{ON-MIN} = 60 \text{ ns (typical)}$

- t<sub>OFF-MIN</sub> = 70 ns (typical)

- Low MOSFET ON-resistance:

- R<sub>DS\_ON HS</sub> = 53 mΩ (typical) - R<sub>DS ON LS</sub> = 31 mΩ (typical)

- Adjustable frequency range: 350 kHz to 2.2 MHz

- Synchronizable to external clock

- Internal compensation

- Power-good flag

- Precision enable to program system UVLO

- Fixed or adjustable soft-start time

- Cycle-by-cycle current limiting

- Short-circuit protection with hiccup mode

- Thermal shutdown protection

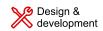

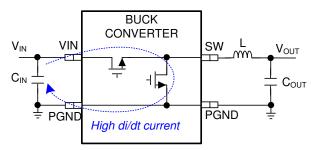

**Simplified Schematic**

# 2 Applications

- Space satellite point of load supply for FPGAs, microcontrollers, data converters and ASICs

- Communications payload

- Command and data handling

- Optical imaging payload

- Radar imaging payload

- Laser communications payload

- Navigations payload

- Scientific exploration payload

# 3 Description

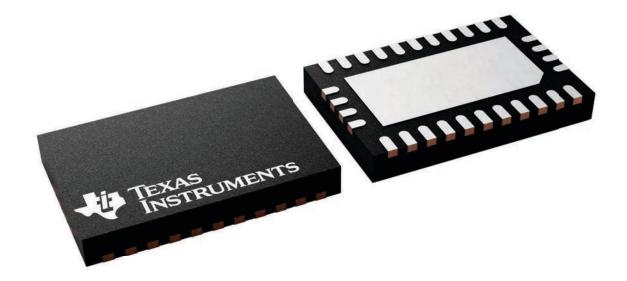

The TPS7H4010-SEP is an easy-to-use synchronous step-down DC/DC converter capable of driving up to 6 A of load current from a supply voltage ranging from 3.5 V to 32 V. The TPS7H4010-SEP provides exceptional efficiency and output accuracy in a very small solution size. Peak current-mode control is employed. Additional features such as adjustable switching frequency, synchronization to an external clock, FPWM option, power-good flag, precision enable, adjustable soft start, and tracking provide both flexible and easy-to-use solutions for a wide range of applications. Automatic frequency foldback at light load and optional external bias improve efficiency over the entire load range. The device requires few external components and has a pinout designed for simple PCB layout with optimal EMI and thermal performance. Protection features include thermal shutdown, input undervoltage lockout, cycle-by-cycle current limiting, and hiccup short-circuit protection.

## **Device Information**

| PART NUMBER <sup>(1)</sup> | GRADE                   | PACKAGE                                             |  |

|----------------------------|-------------------------|-----------------------------------------------------|--|

| TPS7H4010MRNPTSEP          | 20 krad(Si)             | WQFN (30)                                           |  |

| TPS7H4010MRNPSEP           | DIAT `´                 | 6.00 mm × 4.00 mm<br>Mass = $57.2 \text{ mg}^{(2)}$ |  |

| TPS7H4010MKGDSEP           | 20 krad(Si)<br>RLAT KGD | Die                                                 |  |

- For all available packages, see the orderable addendum at the end of the data sheet.

- Mass is accurate to ±10%.

# **Table of Contents**

| 1 Features                           | 1  | 7.4 Device Functional Modes                     | 26                     |

|--------------------------------------|----|-------------------------------------------------|------------------------|

| 2 Applications                       | 1  | 8 Application and Implementation                | 28                     |

| 3 Description                        |    | 8.1 Application Information                     |                        |

| 4 Revision History                   |    | 8.2 Typical Application                         |                        |

| 5 Pin Configuration and Functions    |    | 9 Power Supply Recommendations                  |                        |

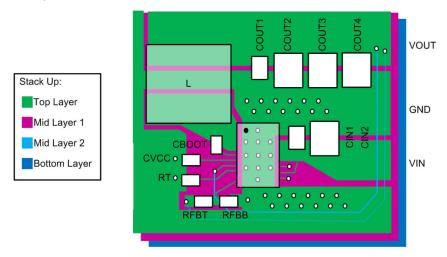

| 6 Specifications                     | 7  | 10 Layout                                       |                        |

| 6.1 Absolute Maximum Ratings         |    | 10.1 Layout Guidelines                          |                        |

| 6.2 ESD Ratings                      |    | 10.2 Layout Example                             |                        |

| 6.3 Recommended Operating Conditions |    | 11 Device and Documentation Support             |                        |

| 6.4 Thermal Information              | 8  | 11.1 Device Support                             |                        |

| 6.5 Electrical Characteristics       | 8  | 11.2 Related Documentation                      |                        |

| 6.6 Timing Characteristics           | 10 | 11.3 Receiving Notification of Documentation Up | pdates <mark>42</mark> |

| 6.7 Switching Characteristics        |    | 11.4 Support Resources                          |                        |

| 6.8 Typical Characteristics          |    | 11.5 Trademarks                                 |                        |

| 7 Detailed Description               |    | 11.6 Electrostatic Discharge Caution            | 42                     |

| 7.1 Overview                         |    | 11.7 Glossary                                   |                        |

| 7.2 Functional Block Diagram         |    | 12 Mechanical, Packaging, and Orderable         |                        |

| 7.3 Feature Description              |    | Information                                     | 42                     |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| ( | Changes from Revision * (November 2020) to Revision A (December 2021)                         | Page |

|---|-----------------------------------------------------------------------------------------------|------|

| • | Updated package description from QFN to WQFN in Description section and throughout data sheet | 1    |

| • | Added additional device orderables to Device Information table in Description section         | 1    |

| • | Added bare die information to Pin Configuration and Functions section                         | 3    |

| • | Updated maximum limit for Junction temperature in Absolute Maximum Ratings table              | 7    |

| • | Added specification for Junction temperature to Recommended Operating Conditions table        |      |

| • | Updated Optimize Thermal Performance section                                                  | 40   |

|   | Updated Related Documentation section                                                         |      |

|   | ·                                                                                             |      |

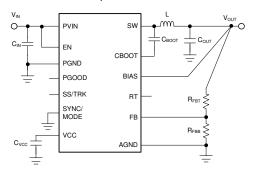

# **5 Pin Configuration and Functions**

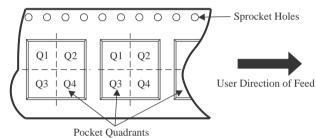

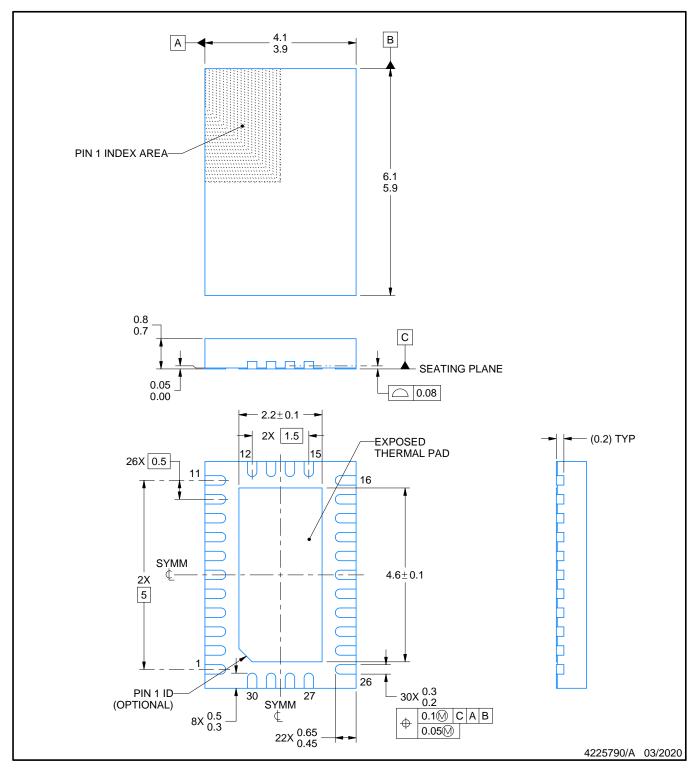

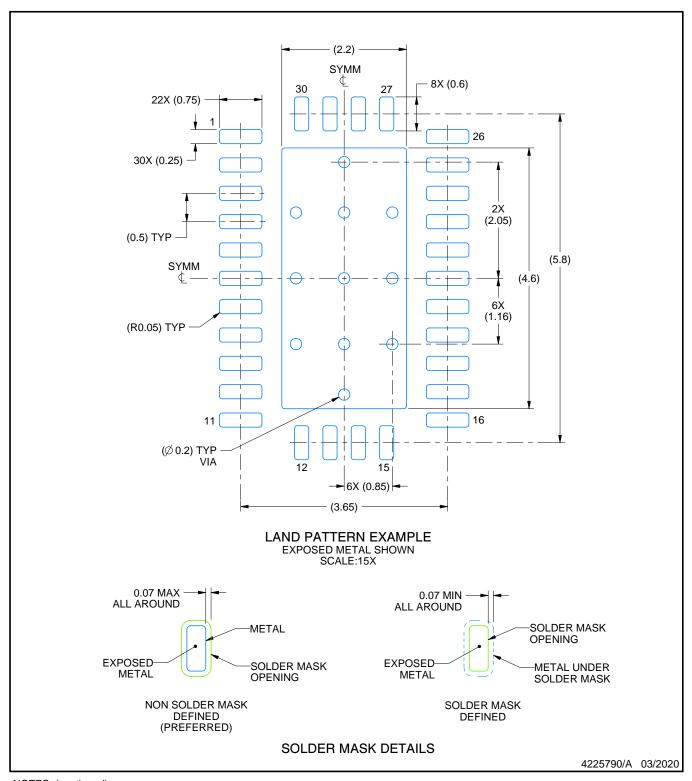

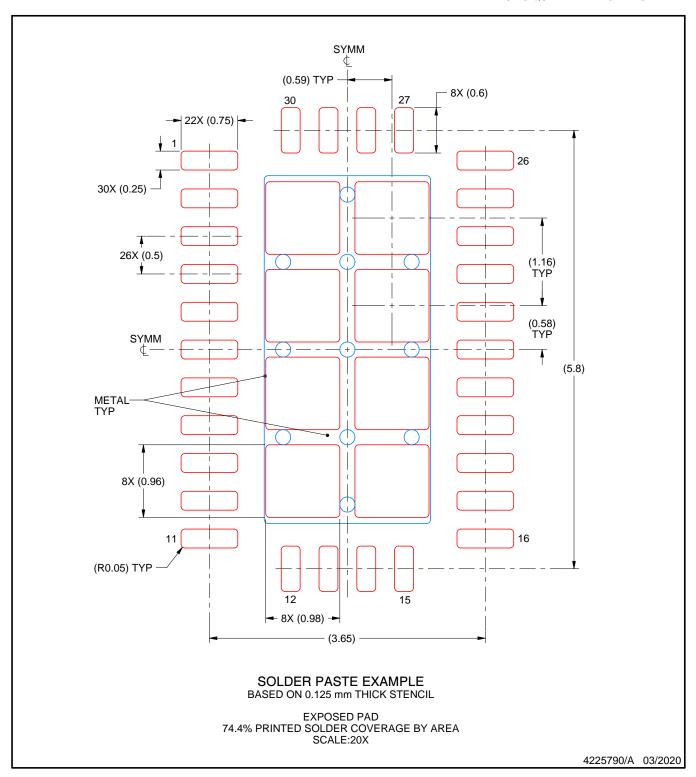

Figure 5-1. RNP Package 30-Pin WQFN 6 mm × 4 mm × 0.8 mm (Top View)

Table 5-1. Pin Functions

|                 | PIN    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |

|-----------------|--------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.             | NAME   | 1/0(-/             | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |

| 1–5             | sw     | Р                  | Switching output of the regulator. Internally connected to source of the HS FET and drain of the LS FET. Connect to power inductor and bootstrap capacitor.                                                                                                                                                                        |

| 6               | СВООТ  | Р                  | Bootstrap capacitor connection for HS FET driver. Connect a high-quality 470-nF capacitor from this pin to the SW pin.                                                                                                                                                                                                             |

| 7               | VCC    | Р                  | Output of internal bias supply. Used as supply to internal control circuits and drivers. Connect a high-quality 2.2-µF capacitor from this pin to GND. TI does not recommend loading this pin by external circuitry.                                                                                                               |

| 8               | BIAS   | Р                  | Optional BIAS LDO supply input. TI recommends tying to $V_{OUT}$ when 3.3 V $\leq$ $V_{OUT} \leq$ 18 V, or tie to an external 3.3-V or 5-V rail if available, to improve efficiency. BIAS pin voltage must not be greater than $V_{IN}$ . Tie to ground when not in use.                                                           |

| 9               | RT     | А                  | Switching frequency setting pin. Place a resistor from this pin to ground to set the switching frequency. If floating, the default switching frequency is 500 kHz. Do not short to ground.                                                                                                                                         |

| 10              | SS/TRK | A                  | Soft-start control pin. Leave this pin floating for a fixed internal soft-start ramp. An external capacitor can be connected from this pin to ground to extend the soft start time. A 2-µA current sourced from this pin charges the capacitor to provide the ramp. Connect to external ramp for tracking. Do not short to ground. |

| 11              | FB     | I                  | Feedback input for output voltage regulation. Connect a resistor divider to set the output voltage.  Never short this pin to ground during operation.                                                                                                                                                                              |

| 12–15,<br>27–30 | NC     | _                  | No internal connection. Connect to ground net and copper to improve heat sinking and board-level reliability.                                                                                                                                                                                                                      |

| 16              | PGOOD  | 0                  | Open drain power-good flag output. Connect to suitable voltage supply through a current limiting resistor. High = $V_{OUT}$ regulation OK, Low = $V_{OUT}$ regulation fault. PGOOD = LOW when EN = low and $V_{IN} > 2$ V.                                                                                                         |

# **Table 5-1. Pin Functions (continued)**

| F     | PIN       | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |

|-------|-----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.   |           |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                |  |

| 17    | SYNC/MODE | I                  | Synchronization input and mode setting pin. Do not float. Tie to ground if not used.  Tie to ground: auto mode, higher efficiency at light loads.  Tie to logic high: forced PWM, constant switching frequency over load.  Tie to external clock source: forced PWM, synchronize to the rising edge of the external clock. |  |

| 18    | EN        | I                  | nable input to regulator. Do not float. High = ON, Low = OFF. Can be tied to PVIN. Precision nable input allows adjustable input voltage UVLO using external resistor divider.                                                                                                                                             |  |

| 19    | AGND      | GND                | Analog ground. Ground reference for internal circuitry. All electrical parameters are measured wirespect to this pin. Connect to system ground on PCB.                                                                                                                                                                     |  |

| 20–22 | PVIN      | Р                  | Supply input to internal bias LDO and HS FET. Connect to input supply and input bypass capacitors $C_{\text{IN}}$ . $C_{\text{IN}}$ must be placed right next to this pin and PGND pins on PCB, and connected with short and wide traces.                                                                                  |  |

| 23–26 | PGND      | GND                | Power ground, connected to the source of LS FET internally. Connect to system ground, DAP/EP, AGND, ground side of $C_{IN}$ and $C_{OUT}$ on PCB. Path to $C_{IN}$ must be as short as possible.                                                                                                                           |  |

| EP    | DAP       | GND                | Low impedance connection to AGND. Connect to system ground on PCB. Major heat dissipation path for the device. Must be used for heat sinking by soldering to ground copper on PCB. Thermal vias are preferred to improve heat dissipation to other layers.                                                                 |  |

(1) A = analog, I = input, O = output, P = power, GND = ground

## **Table 5-2. Bare Die Information**

| DIE THICKNESS | BACKSIDE FINISH        | BACKSIDE POTENTIAL | BOND PAD<br>METALLIZATION<br>COMPOSITION | BOND PAD THICKNESS |

|---------------|------------------------|--------------------|------------------------------------------|--------------------|

| 7.52 mils     | Silicon with backgrind | GND                | MetDCu                                   | 574.5 nm           |

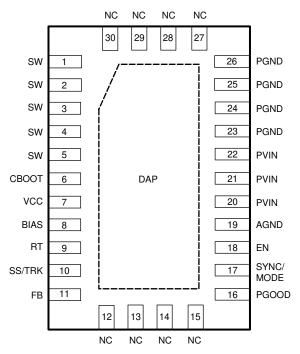

Figure 5-2. TPS7H4010-SEP Bare Die Diagram

Table 5-3. Bond Pad Coordinates in Microns

|             | Table 5-3. Bottu Fau Coordinates III Microns |          |          |          |          |  |  |

|-------------|----------------------------------------------|----------|----------|----------|----------|--|--|

| DESCRIPTION | PAD NUMBER                                   | X MIN    | Y MIN    | X MAX    | Y MAX    |  |  |

| NC          | 1                                            | 105.175  | 4204.585 | 235.375  | 4334.785 |  |  |

| SW          | 2                                            | 105.175  | 3917.305 | 235.375  | 4047.505 |  |  |

| SW          | 3                                            | 105.175  | 3630.025 | 235.375  | 3760.225 |  |  |

| SW          | 4                                            | 105.175  | 3342.745 | 235.375  | 3472.945 |  |  |

| SW          | 5                                            | 105.175  | 3055.465 | 235.375  | 3185.665 |  |  |

| SW          | 6                                            | 105.175  | 2768.185 | 235.375  | 2898.385 |  |  |

| SW          | 7                                            | 76.79    | 2352.945 | 206.99   | 2483.145 |  |  |

| SW          | 8                                            | 76.79    | 2090.795 | 206.99   | 2220.995 |  |  |

| SW          | 9                                            | 76.79    | 1828.645 | 206.99   | 1958.845 |  |  |

| SW          | 10                                           | 76.79    | 1566.495 | 206.99   | 1696.695 |  |  |

| СВООТ       | 11                                           | 74.375   | 1214.15  | 204.575  | 1344.35  |  |  |

| PVCC        | 12                                           | 65.24    | 1006.81  | 195.44   | 1137.01  |  |  |

| VCC         | 13                                           | 67.025   | 787.99   | 197.225  | 918.19   |  |  |

| BIAS        | 14                                           | 67.025   | 595.56   | 197.225  | 725.76   |  |  |

| RT          | 15                                           | 67.025   | 385.595  | 197.225  | 515.795  |  |  |

| SS          | 16                                           | 67.025   | 211.435  | 197.225  | 341.635  |  |  |

| FB          | 17                                           | 334.25   | 64.365   | 464.45   | 194.565  |  |  |

| PGOOD       | 18                                           | 1511.79  | 227.185  | 1641.99  | 357.385  |  |  |

| SYNC        | 19                                           | 1511.79  | 465.08   | 1641.99  | 595.28   |  |  |

| EN          | 20                                           | 1511.79  | 673.54   | 1641.99  | 803.74   |  |  |

| AGND        | 21                                           | 1497.72  | 881.895  | 1627.92  | 1012.095 |  |  |

| AVIN        | 22                                           | 1497.72  | 1064.91  | 1627.92  | 1195.11  |  |  |

| PVIN        | 23                                           | 1428.07  | 1566.495 | 1558.27  | 1696.695 |  |  |

| PVIN        | 24                                           | 1428.07  | 1828.645 | 1558.27  | 1958.845 |  |  |

| PVIN        | 25                                           | 1428.07  | 2090.795 | 1558.27  | 2220.995 |  |  |

| PVIN        | 26                                           | 1428.07  | 2352.945 | 1558.27  | 2483.145 |  |  |

| PGND        | 27                                           | 1535.835 | 2768.185 | 1666.035 | 2898.385 |  |  |

| PGND        | 28                                           | 1535.835 | 3055.465 | 1666.035 | 3185.665 |  |  |

| PGND        | 29                                           | 1535.835 | 3342.745 | 1666.035 | 3472.945 |  |  |

| PGND        | 30                                           | 1535.835 | 3630.025 | 1666.035 | 3760.225 |  |  |

| PGND        | 31                                           | 1535.835 | 3917.305 | 1666.035 | 4047.505 |  |  |

| PGND        | 32                                           | 1535.835 | 4204.585 | 1666.035 | 4334.785 |  |  |

|             | •                                            |          |          |          | •        |  |  |

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range of -55°C to +125°C (unless otherwise noted)(1)

|                  |                                       | MIN         | MAX                         | UNIT |

|------------------|---------------------------------------|-------------|-----------------------------|------|

|                  | PVIN to PGND                          | -0.3        | 36                          |      |

|                  | EN to AGND                            | -0.3        | PVIN + 0.3                  |      |

|                  | FB, RT, SS/TRK to AGND                | -0.3        | 5                           |      |

| Input voltages   | PGOOD to AGND                         | -0.3        | 20                          | V    |

|                  | SYNC to AGND                          | -0.3        | 5.5                         |      |

|                  | BIAS to AGND                          | -0.3        | Lower of (PVIN + 0.3) or 20 |      |

|                  | AGND to PGND                          | -0.3        | 0.3                         |      |

|                  | SW to PGND                            | -0.3        | PVIN + 0.3                  |      |

| Output voltages  | SW to PGND less than 10-ns transients | -3.5        | 36                          | V    |

| Output voltages  | CBOOT to SW                           | -0.3        | 5                           | V    |

|                  | VCC to AGND                           | -0.3        | 5                           |      |

| T <sub>J</sub>   | Junction temperature                  | <b>–</b> 55 | 150                         | °C   |

| T <sub>stg</sub> | Storage temperature                   | -65         | 150                         | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                                            |                                                                             |                                                                                          | VALUE                                 | UNIT |

|--------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|------|

|                                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2000                                                                                    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |      |

| V <sub>(ESD)</sub> Electrostatic discharge |                                                                             | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±750                                  | '    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range of -55°C to +125°C (unless otherwise noted)

|                      |                     | MIN  | MAX                         | UNIT |

|----------------------|---------------------|------|-----------------------------|------|

|                      | PVIN to PGND        | 3.5  | 32                          |      |

|                      | EN                  | 0    | PVIN                        |      |

|                      | FB                  | 0    | 4.5                         |      |

| Input voltages       | PGOOD               | 0    | 18                          | V    |

|                      | BIAS input not used | 0    | 0.3                         |      |

|                      | BIAS input used     | 0    | Lower of (PVIN + 0.3) or 18 |      |

|                      | AGND to PGND        | -0.1 | 0.1                         |      |

| Output voltage       | VOUT                | 1    | 95% of PVIN                 | V    |

| Output current       | IOUT                | 0    | 6                           | Α    |

| Junction temperature | T <sub>J</sub>      | -55  | 125                         | °C   |

## **6.4 Thermal Information**

|                       |                                              | TPS7H4010-SEP |      |

|-----------------------|----------------------------------------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RNP (WQFN)    | UNIT |

|                       |                                              | 30 PINS       |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 29.7          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 17.7          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.1           | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2           | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 9.0           | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.0           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise stated. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated,  $V_{IN}$  = 12 V.

|                          | PARAMETER                                                                   | TEST CONDITIONS                                                                    | MIN   | TYP   | MAX   | UNIT |

|--------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY VOLTAG            | GE (PVIN PINS)                                                              |                                                                                    |       |       |       |      |

| PVIN                     | Operating input voltage                                                     |                                                                                    | 3.5   |       | 32    | V    |

| I <sub>SD</sub>          | Shutdown quiescent current; measured at PVIN pin <sup>(1)</sup>             | V <sub>EN</sub> = AGND, T <sub>J</sub> = 25°C                                      |       | 0.8   | 10    | μΑ   |

| I <sub>Q_NONSW</sub>     | Operating quiescent current from PVIN (non-switching)                       | $V_{EN}$ = 2 V, $V_{FB}$ = 1.5 V, $V_{BIAS}$ = 3.3 V external                      |       | 0.6   | 12    | μA   |

| ENABLE (EN PIN           | ١)                                                                          |                                                                                    |       |       |       |      |

| V <sub>EN_VCC_H</sub>    | Enable input high level for V <sub>CC</sub> output                          | V <sub>EN</sub> rising                                                             |       |       | 1.15  | V    |

| V <sub>EN_VCC_L</sub>    | Enable input low level for V <sub>CC</sub> output                           | V <sub>EN</sub> falling                                                            | 0.3   |       |       | V    |

| V <sub>EN_VOUT_</sub> H  | Enable input high level for V <sub>OUT</sub>                                | V <sub>EN</sub> rising                                                             | 1.14  | 1.196 | 1.25  | V    |

| V <sub>EN_VOUT_HYS</sub> | Enable input hysteresis for V <sub>OUT</sub>                                | V <sub>EN</sub> falling hysteresis                                                 |       | 100   |       | mV   |

| I <sub>LKG_EN</sub>      | Enable input leakage current                                                | V <sub>EN</sub> = 2 V                                                              |       | 1.4   | 200   | nA   |

| INTERNAL LDO             | (VCC PIN, BIAS PIN)                                                         |                                                                                    |       |       |       |      |

| \/                       | Internal V <sub>CC</sub> voltage                                            | PWM operation                                                                      |       | 3.27  |       | V    |

| V <sub>CC</sub>          | internal v <sub>CC</sub> voltage                                            | PFM operation                                                                      |       | 3.1   |       | V    |

| \/                       | Internal V <sub>CC</sub> undervoltage                                       | V <sub>CC</sub> rising                                                             | 2.96  | 3.14  | 3.27  | V    |

| V <sub>CC_UVLO</sub>     | lockout                                                                     | V <sub>CC</sub> falling hysteresis                                                 |       | 605   |       | mV   |

| \/                       | Innut shangesup                                                             | V <sub>BIAS</sub> rising                                                           |       | 3.09  | 3.25  | V    |

| V <sub>BIAS_ON</sub>     | Input changeover                                                            | V <sub>BIAS</sub> falling hysteresis                                               |       | 63    |       | mV   |

| I <sub>BIAS_NONSW</sub>  | Operating quiescent current from external V <sub>BIAS</sub> (non-switching) | V <sub>EN</sub> = 2 V, V <sub>FB</sub> = 1.5 V, V <sub>BIAS</sub> = 3.3 V external |       | 21    | 50    | μA   |

| VOLTAGE REFE             | RENCE (FB PIN)                                                              |                                                                                    |       |       |       |      |

| V <sub>FB</sub>          | Feedback voltage                                                            | PWM mode                                                                           | 0.987 | 1.006 | 1.017 | V    |

| I <sub>LKG FB</sub>      | Input leakage current at FB pin                                             | V <sub>FB</sub> = 1 V                                                              |       | 0.2   | 60    | nA   |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# **6.5 Electrical Characteristics (continued)**

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise stated. Minimum and maximum limits are specified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated,  $V_{IN}$  = 12 V.

|                                | PARAMETER                                             | TEST CONDITIONS                                                          | MIN      | TYP   | MAX  | UNIT |

|--------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------|----------|-------|------|------|

| HIGH SIDE DRIV                 | ER (CBOOT PIN)                                        |                                                                          |          |       |      |      |

| V <sub>CBOOT_UVLO</sub>        | CBOOT - SW undervoltage lockout                       |                                                                          | 1.6      | 2.2   | 2.7  | V    |

| CURRENT LIMIT                  | S AND HICCUP                                          |                                                                          | <b>'</b> | ,     |      |      |

| I <sub>HS_LIMIT</sub>          | Short-circuit, high-side current limit <sup>(2)</sup> |                                                                          | 7.4      | 8.7   | 9.85 | Α    |

| I <sub>LS_LIMIT</sub>          | Low-side current limit <sup>(2)</sup>                 |                                                                          | 5.8      | 6.6   | 7.25 | Α    |

| I <sub>NEG_LIMIT</sub>         | Negative current limit                                |                                                                          |          | -5    |      | Α    |

| V <sub>HICCUP</sub>            | Hiccup threshold on FB pin                            |                                                                          | 0.36     | 0.4   | 0.44 | V    |

| I <sub>L_ZC</sub>              | Zero cross-current limit                              |                                                                          |          | -0.05 |      | Α    |

| SOFT START (S                  | S/TRK PIN)                                            |                                                                          |          |       |      |      |

| I <sub>SSC</sub>               | Soft-start charge current                             |                                                                          | 1.8      | 2     | 2.2  | μΑ   |

| R <sub>SSD</sub>               | Soft-start discharge resistance                       | UVLO, TSD, OCP, or EN = AGND                                             |          | 1     |      | kΩ   |

| POWER GOOD (                   | PGOOD PIN) and OVERVOLTAGE                            | PROTECTION                                                               |          |       |      |      |

| V <sub>PGOOD_OV</sub>          | Power-good overvoltage threshold                      | % of FB voltage                                                          | 106%     | 110%  | 113% |      |

| V <sub>PGOOD_UV</sub>          | Power-good undervoltage threshold                     | % of FB voltage                                                          | 86%      | 90%   | 93%  |      |

| V <sub>PGOOD_HYS</sub>         | Power-good hysteresis                                 | % of FB voltage                                                          |          | 1.2%  |      |      |

| V <sub>PGOOD_</sub> VALID      | Minimum input voltage for proper PGOOD function       | 50-µA pullup to PGOOD pin, V <sub>EN</sub> = AGND, T <sub>J</sub> = 25°C |          | 1.3   | 2    | V    |

| D                              | Dower good ON registeres                              | V <sub>EN</sub> = 2.5 V                                                  |          | 40    | 100  |      |

| R <sub>PGOOD</sub>             | Power-good ON-resistance                              | V <sub>EN</sub> = AGND                                                   | 30       |       | 90   | Ω    |

| MOSFETS                        |                                                       |                                                                          |          |       |      |      |

| R <sub>DS_ON_HS</sub> (3)      | High-side MOSFET ON-<br>resistance                    | I <sub>OUT</sub> = 1 A, V <sub>BIAS</sub> = V <sub>OUT</sub> = 3.3 V     |          | 53    | 90   | mΩ   |

| R <sub>DS_ON_LS</sub> (3)      | Low-side MOSFET ON-<br>resistance                     | I <sub>OUT</sub> = 1 A, V <sub>BIAS</sub> = V <sub>OUT</sub> = 3.3 V     |          | 31    | 55   | mΩ   |

| THERMAL SHUT                   | rdown .                                               |                                                                          |          |       |      |      |

| <b>T</b> (4)                   | Thermal shutdown threshold Shutdown threshold         |                                                                          |          | 160   |      |      |

| T <sub>SD</sub> <sup>(4)</sup> | Recovery threshold                                    |                                                                          |          | 135   |      | °C   |

<sup>(1)</sup> Shutdown current includes leakage current of the switching transistors.

<sup>(2)</sup> This current limit was measured as the internal comparator trip point. Due to inherent delays in the current limit comparator and drivers, the peak current limit measured in closed loop with faster slew rate will be larger, and valley current limit will be lower.

<sup>(3)</sup> Measured at pins.

<sup>(4)</sup> Ensured by design.

# **6.6 Timing Characteristics**

| P                                                 | ARAMETER                                            | TEST CONDITIONS                                      | MIN | NOM | MAX | UNIT   |  |  |

|---------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|-----|-----|-----|--------|--|--|

| CURRENT LIMITS A                                  | CURRENT LIMITS AND HICCUP                           |                                                      |     |     |     |        |  |  |

| N <sub>OC</sub> (1)                               | Number of switching cycles before hiccup is tripped |                                                      |     | 128 |     | cycles |  |  |

| toc                                               | Overcurrent hiccup retry delay time                 |                                                      |     | 46  |     | ms     |  |  |

| SOFT START (SS/T                                  | SOFT START (SS/TRK PIN)                             |                                                      |     |     |     |        |  |  |

| t <sub>SS</sub>                                   | Internal soft-start time                            | CSS = OPEN, from EN rising edge to PGOOD rising edge | 3.5 | 6.3 |     | ms     |  |  |

| POWER GOOD (PGOOD PIN) and OVERVOLTAGE PROTECTION |                                                     |                                                      |     |     |     |        |  |  |

| t <sub>PGOOD_RISE</sub>                           | PGOOD rising edge deglitch delay                    |                                                      | 80  | 140 | 200 | μs     |  |  |

| t <sub>PGOOD_FALL</sub>                           | PGOOD falling edge deglitch delay                   |                                                      | 80  | 140 | 200 | μs     |  |  |

<sup>(1)</sup> Ensured by design.

# **6.7 Switching Characteristics**

| PARAMETER              |                                              | TEST CONDITIONS       | MIN  | TYP  | MAX  | UNIT |  |

|------------------------|----------------------------------------------|-----------------------|------|------|------|------|--|

| PWM LIMITS (SW PINS)   |                                              |                       |      |      |      |      |  |

| t <sub>ON-MIN</sub>    | Minimum switch on-time                       |                       |      | 60   | 82   | ns   |  |

| t <sub>OFF-MIN</sub>   | Minimum switch off-time                      |                       |      | 70   | 120  | ns   |  |

| t <sub>ON-MAX</sub>    | Maximum switch on-time                       | HS timeout in dropout | 3    | 6    | 9    | μs   |  |

| OSCILLATOR (           | RT and SYNC PINS)                            |                       |      |      |      |      |  |

| fosc                   | Internal oscillator frequency                | RT = Open             | 440  | 500  | 560  | kHz  |  |

| f <sub>ADJ</sub>       | Minimum adjustable frqeuency by RT or SYNC   | RT = 115 kΩ, 0.1%     | 315  | 350  | 385  | kHz  |  |

|                        | Maximum adjustable frqeuency by RT or SYNC   | RT = 17.4 kΩ, 0.1%    | 1980 | 2200 | 2420 |      |  |

| V <sub>SYNC_HIGH</sub> | Sync input high-level threshold              |                       |      |      | 2    | V    |  |

| V <sub>SYNC_LOW</sub>  | Sync input low-level threshold               |                       | 0.4  |      |      | V    |  |

| V <sub>MODE_HIGH</sub> | Mode input high-level threshold for FPWM     |                       |      | 0.42 |      | V    |  |

| V <sub>MODE_LOW</sub>  | Mode input low-level threshold for AUTO mode |                       |      | 0.4  |      | V    |  |

| tsync_min              | Sync input minimum ON and OFF time           |                       |      | 80   |      | ns   |  |

Product Folder Links: TPS7H4010-SEP

Submit Document Feedback

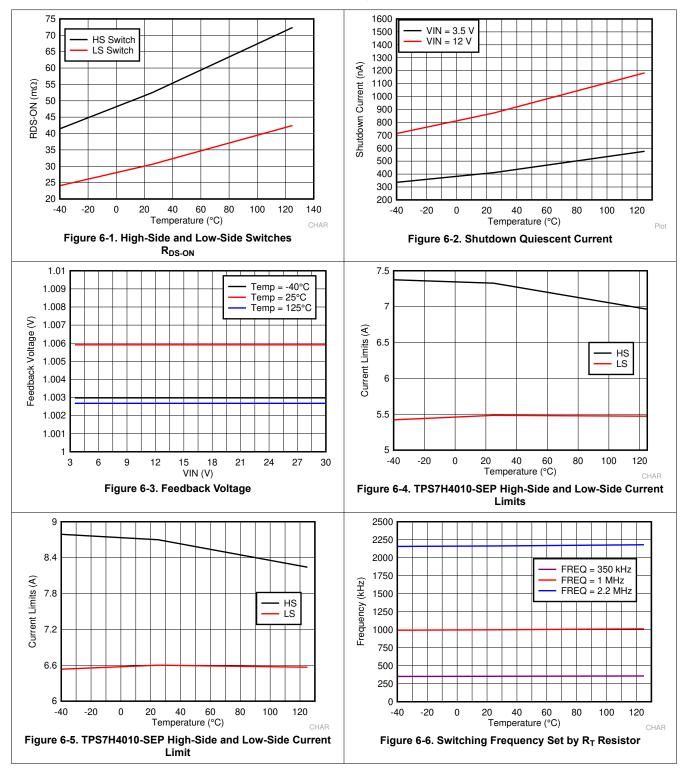

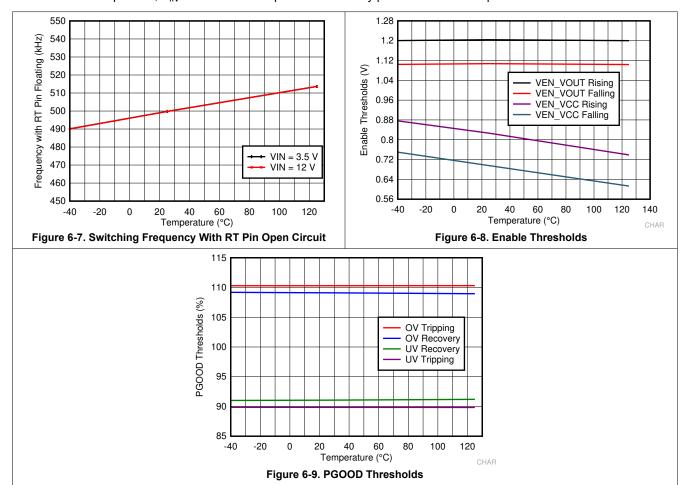

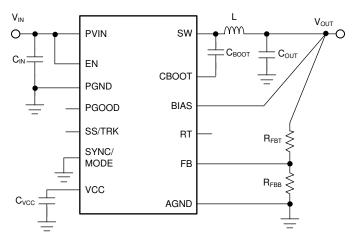

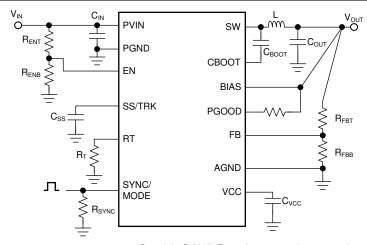

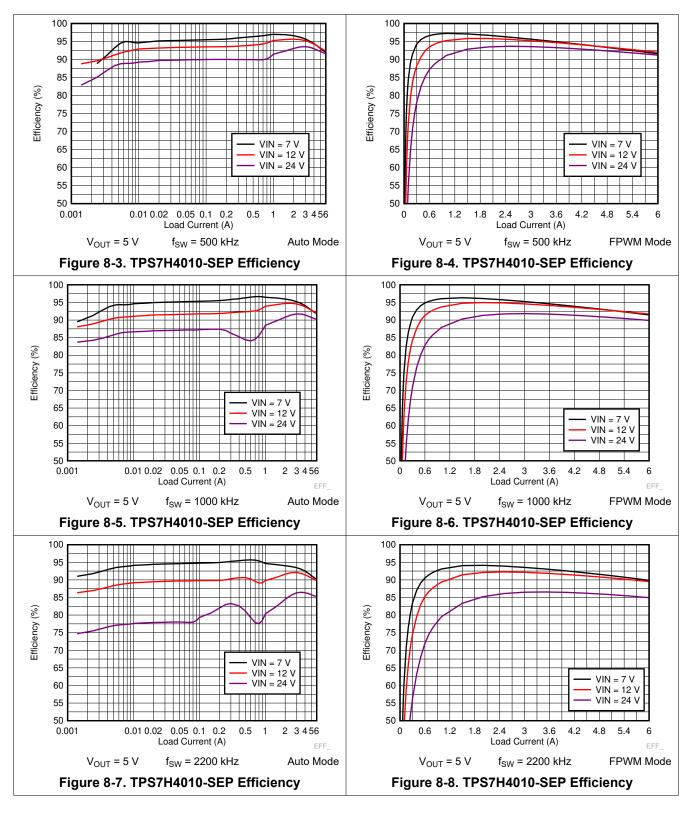

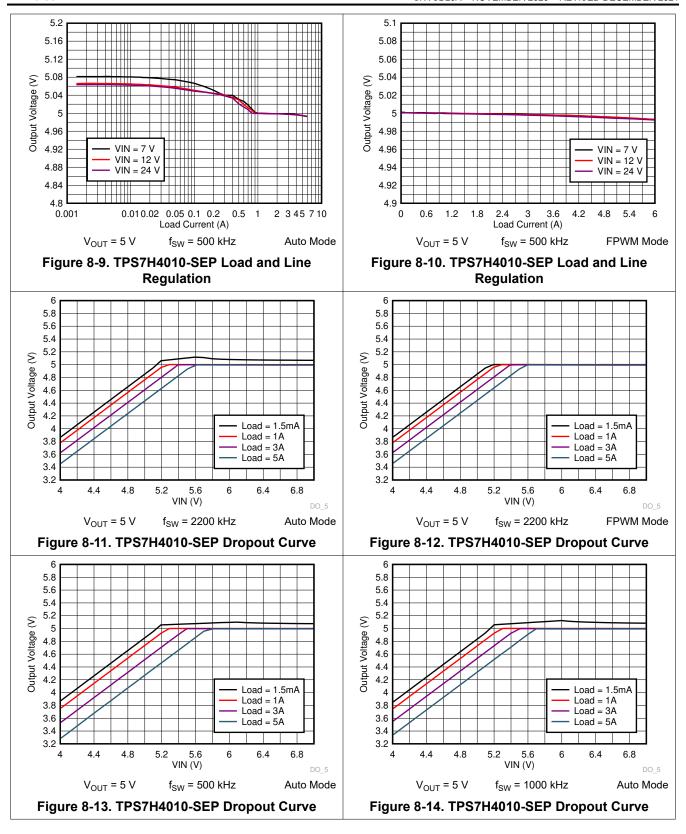

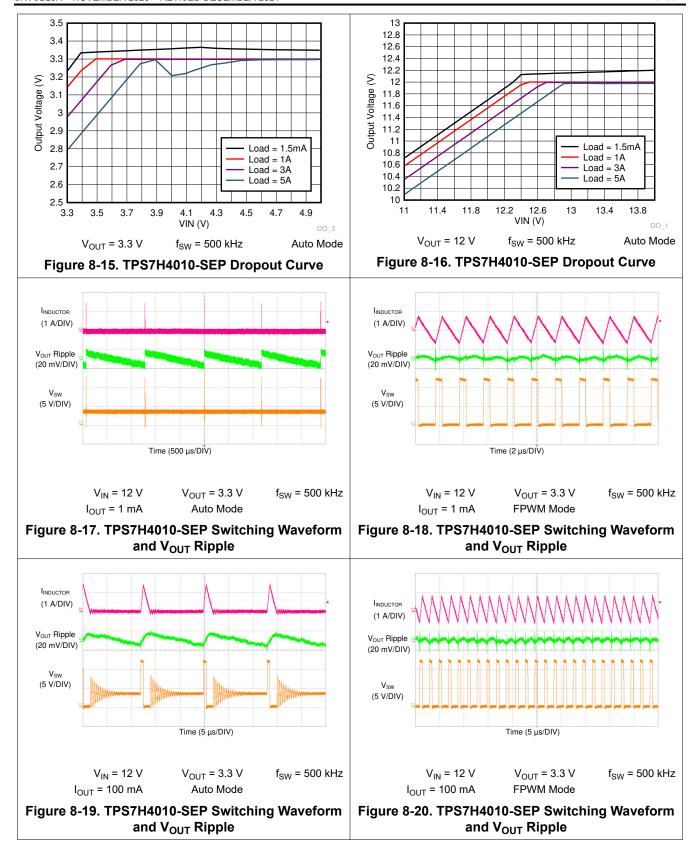

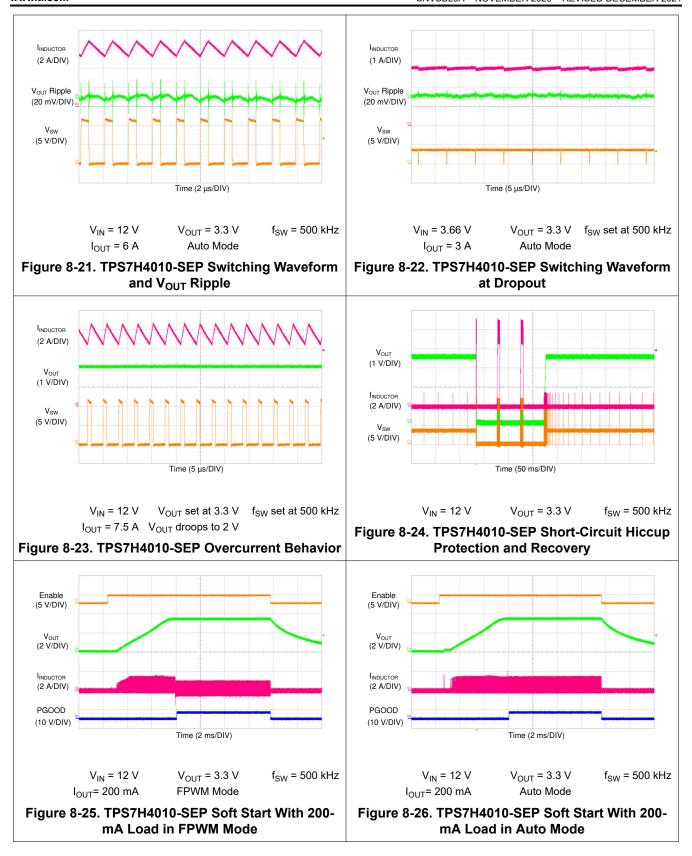

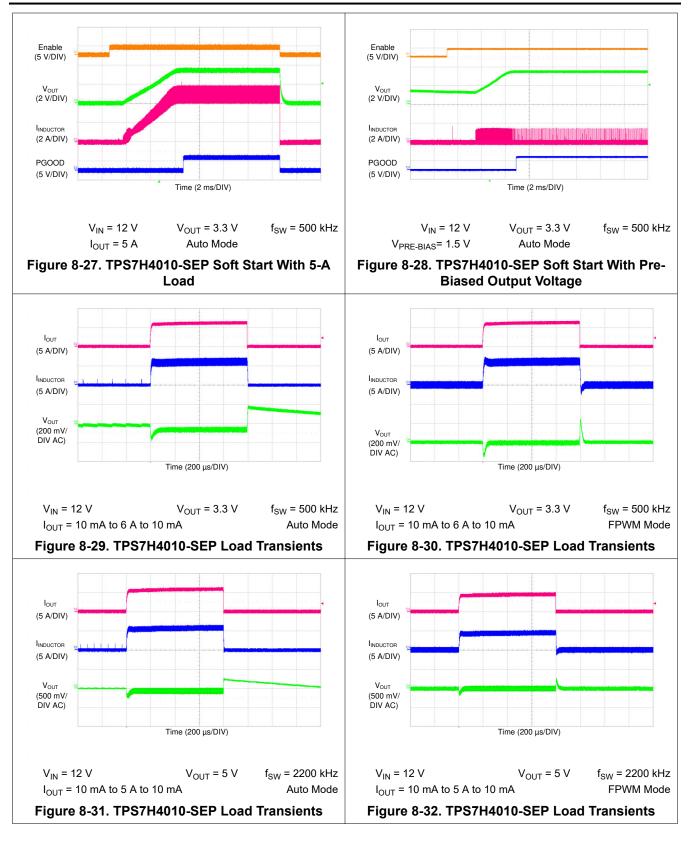

## 6.8 Typical Characteristics

Unless otherwise specified, V<sub>IN</sub> = 12 V. Curves represent most likely parametric norm at specified condition.

# **6.8 Typical Characteristics (continued)**

Unless otherwise specified, V<sub>IN</sub> = 12 V. Curves represent most likely parametric norm at specified condition.

# 7 Detailed Description

## 7.1 Overview

The TPS7H4010-SEP is an easy-to-use synchronous step-down DC/DC converter that operates from a 3.5-V to 32-V supply voltage. It is capable of delivering up to 6 A of DC load current with exceptional efficiency and thermal performance in a very small solution size.

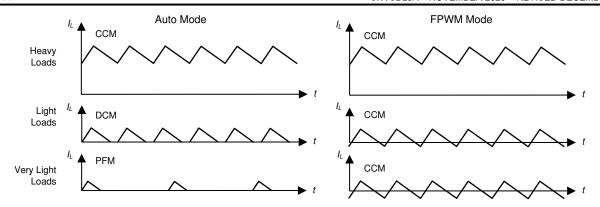

The TPS7H4010-SEP employs fixed-frequency peak current-mode control with configurable auto or FPWM operation mode. Auto mode provides very high efficiency at light loads, and FPWM mode maintains constant switching frequency over entire load range.

The device is internally compensated, which reduces design time and the number of external components. The switching frequency is programmable from 350 kHz to 2.2 MHz by an external resistor. The TPS7H4010-SEP can also synchronize to an external clock within the same frequency range. The wide switching frequency range allows the device to be optimized for a wide range of system requirements. It can be optimized for small solution size with higher frequency; or for high efficiency with lower switching frequency. The TPS7H4010-SEP has very low quiescent current, which is critical for battery operated systems. It allows for a wide range of voltage conversion ratios due to very small minimum on-time  $(t_{ON-MIN})$  and minimum off-time  $(t_{OFF-MIN})$ . Automated frequency foldback is employed at very high or low duty cycles to further extend the operating range.

The TPS7H4010-SEP also features a power-good (PGOOD) flag, precision enable, internal or adjustable soft start, pre-biased start-up, and output voltage tracking. Protection features include thermal shutdown, undervoltage lockout (UVLO), cycle-by-cycle current limiting, and short-circuit hiccup protection. It provides flexible and easy-to-use solutions for a wide range of applications.

The device requires very few external components and has a pin out designed for simple, optimum PCB layout for enhanced EMI and thermal performance. The TPS7H4010-SEP device is available in a 30-pin WQFN leadless package.

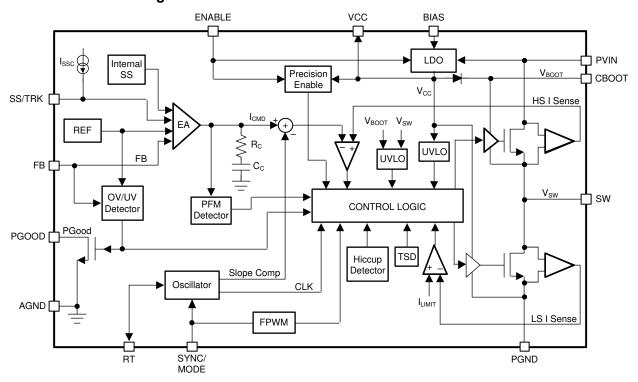

## 7.2 Functional Block Diagram

## 7.3 Feature Description

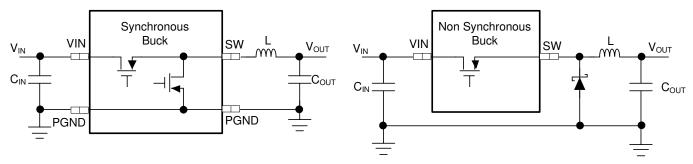

## 7.3.1 Synchronous Step-Down Regulator

The TPS7H4010-SEP is a synchronous buck converter with both power MOSFETs integrated in the device. Figure 7-1 shows a simplified schematic for synchronous and non-synchronous buck converters. The synchronous buck integrates both high-side (HS) and low-side (LS) power MOSFETs. The non-synchronous buck integrates HS MOSFET and works with a discrete power diode as LS rectifier.

Figure 7-1. Simplified Synchronous vs Non-synchronous Buck Converters

A synchronous converter with integrated HS and LS MOSFETs offers benefits such as less design effort, lower external components count, reduced total solution size, higher efficiency at heavier load, easier PCB design, and more control flexibility.

The main advantage of a synchronous converter is that the voltage drop across the LS MOSFET is lower than the voltage drop across the power diode of a non-synchronous converter. Lower voltage drop translates into less power dissipation and higher efficiency. The TPS7H4010-SEP integrates HS and LS MOSFETs with very low on-time resistance to improve efficiency. It is especially beneficial when the output voltage is low. Because the LS MOSFET is integrated into the device, at light loads a synchronous converter has the flexibility to operate in either discontinuous or continuous conduction mode.

An integrated LS MOSFET also allows the controller to obtain inductor current information when the LS switch is on. It allows the control loop to make more complex decisions based on HS and LS currents. It allows the TPS7H4010-SEP to have peak and valley cycle-by-cycle current limiting for more robust protection.

#### 7.3.2 Auto Mode and FPWM Mode

The TPS7H4010-SEP has pin configurable auto mode or FPWM options.

In auto mode, the device operates in diode emulation mode (DEM) at light loads. In DEM, inductor current stops flowing when it reaches 0 A. This is also referred to as discontinuous conduction mode (DCM). This is the same behavior as the non-synchronous regulator, with higher efficiency. At heavier load, when the inductor current valley is above 0 A, the device operates in continuous conduction mode (CCM), where the switching frequency is fixed and set by RT pin.

In auto mode, the peak inductor current has a minimum limit,  $I_{PEAK\_MIN}$ , in the TPS7H4010-SEP. When peak current reaches  $I_{PEAK\_MIN}$ , the switching frequency reduces to regulate the required load current. Switching frequency lowers when load reduces. This is when the device operates in pulse frequency modulation (PFM). PFM further improves efficiency by reducing switching losses. Light load efficiency is especially important for battery operated systems.

In forced PWM (FPWM) mode, the device operates in CCM regardless of load with the frequency set by RT pin or synchronization input. Inductor current can go negative at light loads. At light loads, the efficiency is lower than auto mode, due to higher conduction losses and switching losses. In FPWM, the device has fixed switching frequency over the entire load range, which is beneficial to noise sensitive applications.

Figure 7-2 shows the inductor current waveforms in each mode with heavy load, light load, and very light load. The difference between the two modes is at lighter loads where inductor current valley reaches zero.

Figure 7-2. Inductor Current Waveforms at Auto Mode and FPWM Mode With Different Loads

In CCM, the inductor current peak-to-peak ripple can be estimated by Equation 1:

$$I_{Lripple} = \frac{(V_{IN} - V_{OUT})}{f_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

(1)

The average or DC value of the inductor current equals the load current, or output current I<sub>OUT</sub>, in steady state. Peak inductor current can be calculated by Equation 2:

$$I_{PEAK} = I_{OUT} + I_{Lripple} / 2$$

(2)

Valley inductor current can be calculated by Equation 3:

$$I_{VALLEY} = I_{OUT} - I_{Lripple} / 2$$

(3)

In auto mode, the CCM to DCM boundary condition is when  $I_{VALLEY} = 0$  A. When  $I_{Lripple} \ge I_{PEAK\_MIN}$ , the load current at the DCM boundary condition can be found by Equation 4. When the peak-to-peak ripple current is smaller than  $I_{Lripple} \ge I_{PEAK\_MIN}$ , the PFM boundary will be reached first.

$$I_{OUT\ DCM} = I_{Lripple} / 2$$

(4)

when

I<sub>Lripple</sub> ≥ I<sub>PEAK MIN</sub>

In auto mode, the PFM operation boundary condition is when  $I_{PEAK} = I_{PEAK\_MIN}$ . Frequency foldback occurs when peak current drops to  $I_{PEAK\_MIN}$ , no matter whether in CCM or DCM operation. When current ripple is small,  $I_{Lripple} < I_{PEAK\_MIN}$ , the peak current reaches  $I_{PEAK\_MIN}$  when still in CCM. The output current at CCM PFM boundary can be found by Equation 5:

$$I_{OUT\ CCM\ PFM} = I_{PEAK\ MIN} - I_{Lripple} / 2$$

(5)

when

I<sub>Lripple</sub> < I<sub>PEAK MIN</sub>

The current ripple increases with reduced frequency if load reduces. When valley current reaches zero, the frequency continues to fold back with constant peak current and discontinuous current.

In FPWM mode, there is no I<sub>PEAK-MIN</sub> limit. The peak current is defined by Equation 2 at light loads and heavy loads.

Mode setting only affects operation at light loads. There is no difference if load current is above the DCM and PFM boundary conditions discussed above.

See Frequency Synchronization and Mode Setting section for mode setting options in TPS7H4010-SEP.

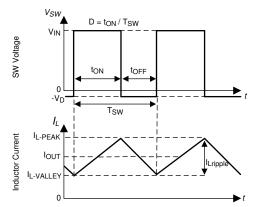

### 7.3.3 Fixed-Frequency Peak Current-Mode Control

The TPS7H4010-SEP synchronous switched mode voltage regulator employs fixed frequency peak current mode control with advanced features. The fixed switching frequency is controlled by an internal clock. To get accurate DC load regulation, a voltage feedback loop is implemented to generate peak current command. The HS switch is turned on at the rising edge of the clock. As shown in Figure 7-3, during the HS switch on-time  $t_{\rm ON}$ , the SW pin voltage  $V_{\rm SW}$  swings up to approximately  $V_{\rm IN}$ , and the inductor current  $I_{\rm L}$  increases with a linear slope. The HS switch is turned off when the inductor current reaches the peak current command. During the HS switch off-time  $t_{\rm OFF}$ , the LS switch is turned on. Inductor current discharges through the LS switch, which forces the  $V_{\rm SW}$  to swing below ground by the voltage drop across the LS switch. The LS switch is turned off at the next clock cycle, before the HS switch is turned on. The regulation loop adjusts the peak current command to maintain a constant output voltage.

Figure 7-3. SW Voltage and Inductor Current Waveforms in CCM

Duty cycle D is defined by the on-time of the HS switch over the switching period:

$$D = t_{ON} / T_{SW}$$

(6)

where

T<sub>SW</sub> = 1 / f<sub>SW</sub> is the switching period

In an ideal buck converter, where losses are ignored, D is proportional to the output voltage and inverse proportional to the input voltage:  $D = V_{OUT} / V_{IN}$ .

When the TPS7H4010-SEP is set to operate in auto mode, the LS switch is turned off when its current reaches zero ampere before the next clock cycle comes. Both HS switch and LS switch are off before the HS switch is turned on at the next clock cycle.

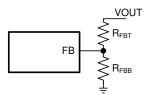

## 7.3.4 Adjustable Output Voltage

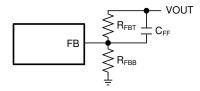

The voltage regulation loop in the TPS7H4010-SEP regulates the FB pin voltage to be the same as the internal reference voltage. The output voltage of the TPS7H4010-SEP is set by a resistor divider to program the ratio from  $V_{OUT}$  to  $V_{FB}$ . The resistor divider is connected from the output to ground with the mid-point connecting to the FB pin.

Figure 7-4. Output Voltage Setting by Resistor Divider

The internal voltage reference and feedback loop produce precise voltage regulation over temperature. The recommends using divider resistors with 1% tolerance or better, and with temperature coefficient of 100 ppm or lower. Typically,  $R_{FBT}$  = 10 k $\Omega$  to 100 k $\Omega$  is recommended. Larger  $R_{FBT}$  and  $R_{FBB}$  values reduce the quiescent current going through the divider, which help maintain high efficiency at very light load. But larger divider values also make the feedback path more susceptible to noise. If efficiency at very light load is critical in a certain application,  $R_{FBT}$  up to 1 M $\Omega$  can be used.

R<sub>FBB</sub> can be calculated by Equation 7:

$$R_{FBB} = \frac{V_{FB}}{V_{OUT} - V_{FB}} R_{FBT} \tag{7}$$

The minimum programmable  $V_{OUT}$  equals  $V_{FB}$ , with  $R_{FBB}$  open. The maximum  $V_{OUT}$  is limited by the maximum duty cycle at a given frequency:

$$D_{MAX} = 1 - (t_{OFF-MIN} / T_{SW})$$

(8)

#### where

- · t<sub>OFF-MIN</sub> is the minimum off time of the HS switch

- T<sub>SW</sub> = 1 / f<sub>SW</sub> is the switching period

Ideally, without frequency foldback,  $V_{OUT\ MAX} = V_{IN\ MIN} \times D_{MAX}$ .

Power losses in the circuit reduces the maximum output voltage. The TPS7H4010-SEP folds back switching frequency under  $t_{OFF\_MIN}$  condition to further extend  $V_{OUT\_MAX}$ . The device maintains output regulation with lower input voltage. The minimum fold-back frequency is limited by the maximum HS on-time,  $t_{ON\_MAX}$ . Maximum output voltage with frequency foldback can be estimated by:

$$V_{OUT\_MAX} = V_{IN\_MIN} \times \frac{t_{ON-MAX}}{t_{ON-MAX} + t_{OFF-MIN}} - I_{OUT} \times (R_{DS\_ON\_HS} + DCR)$$

(9)

The voltage drops on the HS MOSFET and inductor DCR have been taken into account in Equation 9. The switching losses were not included.

If the resistor divider is not connected properly, the output voltage cannot be regulated because the feedback loop cannot obtain correct output voltage information. If the FB pin is shorted to ground or disconnected, the output voltage is driven close to  $V_{IN}$ . The load connected to the output could be damaged under this condition. Do not short FB to ground or leave it open circuit during operation.

The FB pin is a noise sensitive node. It is important to place the resistor divider as close as possible to the FB pin, and route the feedback node with a short and thin trace. The trace connecting  $V_{OUT}$  to  $R_{FBT}$  can be long, but it must be routed away from the noisy area of the PCB. For more layout recommendations, see *Layout* section.

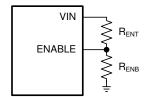

### 7.3.5 Enable and UVLO

The TPS7H4010-SEP regulates output voltage when the VCC voltage is higher than the undervoltage lock out (UVLO) level,  $V_{CC\_UVLO}$ , and the EN voltage is higher than  $V_{EN\_VOUT\_H}$ .

The internal LDO output voltage VCC is turned on when the EN voltage is higher than  $V_{EN\_VCC\_H}$ . The precision enable circuitry is also turned on when VCC is above UVLO. Normal operation of the TPS7H4010-SEP with regulated output voltage is enabled when the EN voltage is greater than  $V_{EN\_VOUT\_H}$ . When the EN voltage is less than  $V_{EN\_VCC\_L}$ , the device is in shutdown mode. The internal dividers make sure  $V_{EN\_VOUT\_H}$  is always higher than  $V_{EN\_VCC\_H}$ .

The EN pin cannot be left floating. The simplest way to enable the operation of the TPS7H4010-SEP is to connect the EN pin to PVIN, which allows self-start-up of the TPS7H4010-SEP when  $V_{\rm IN}$  rises. Use of a pullup resistor between PVIN and EN pins helps reduce noise coupling from PVIN pin to the EN pin.

Many applications benefit from employing an enable divider to establish a customized system UVLO. This can be used either for sequencing, system timing requirement, or to reduce the occurrence of deep discharge of a

battery power source. Figure 7-5 shows how to use a resistor divider to set a system UVLO level. An external logic output can also be used to drive the EN pin for system sequencing.

Figure 7-5. System UVLO

With a selected  $R_{ENT}$ , the  $R_{ENB}$  can be calculated by Equation 10:

$$R_{ENB} = \frac{V_{EN\_VOUT\_H}}{V_{IN\_ON\_H} - V_{EN\_VOUT\_H}} R_{ENT}$$

(10)

where

•  $V_{IN\_ON\_H}$  is the desired supply voltage threshold to turn on this device

Note that the divider adds to supply quiescent current by  $V_{IN}$  / ( $R_{ENT}$  +  $R_{ENB}$ ). Small  $R_{ENT}$  and  $R_{ENB}$  values add more quiescent current loss. However, large divider values make the node more sensitive to noise.  $R_{ENT}$  in the hundreds of  $k\Omega$  range is a good starting point.

## 7.3.6 Internal LDO, V<sub>CC UVLO</sub>, and BIAS Input

The TPS7H4010-SEP integrates an internal LDO, generating VCC voltage for control circuitry and MOSFET drivers. The VCC pin must have a 1- $\mu$ F to 4.7- $\mu$ F bypass capacitor placed as close as possible to the pin and properly grounded. Do not load the VCC pin or short it to ground during operation. Shorting VCC pin to ground during operation may damage the device.

The UVLO on VCC voltage,  $V_{CC\_UVLO}$ , turns off the regulation when VCC voltage is too low. It prevents the TPS7H4010-SEP from operating until the VCC voltage is enough for the internal circuitry. Hysteresis on  $V_{CC\_UVLO}$  prevents the part from turning off during power up if  $V_{IN}$  droops due to input current demands. The LDO generates VCC voltage from one of the two inputs: the supply voltage  $V_{IN}$ , or the BIAS input. When BIAS is tied to ground, the LDO input is  $V_{IN}$ . When BIAS is tied to a voltage higher than 3.3 V, the LDO input is  $V_{BIAS}$ . BIAS voltage must be lower than both  $V_{IN}$  and 18 V.

The BIAS input is designed to reduce the LDO power loss. The LDO power loss is:

$$P_{LOSS LDO} = I_{LDO} \times (V_{IN LDO} - V_{OUT LDO})$$

(11)

The higher the difference between the input and output voltages of the LDO, the more loss occurs to supply the same LDO output current. The BIAS input provides an option to supply the LDO with a lower voltage than  $V_{IN}$ , to reduce the difference of the input and output voltages of the LDO and reduce power loss. For example, if the LDO current is 10 mA at a certain frequency with  $V_{IN} = 24$  V and  $V_{OUT} = 5$  V. The LDO loss with BIAS tied to ground is equal to 10 mA × (24 V – 3.27 V) = 207.3 mW, while the loss with BIAS tied to  $V_{OUT}$  is equal to 10 mA × (5 – 3.27) = 17.3 mW.

The efficiency improvement is more significant at light and mid loads because the LDO loss is a higher percentage in the total loss. The improvements is more significant with higher switching frequency because the LDO current is higher at higher switching frequency. The improvement is more significant when  $V_{\text{IN}} \gg V_{\text{OUT}}$  because the voltage difference is higher.

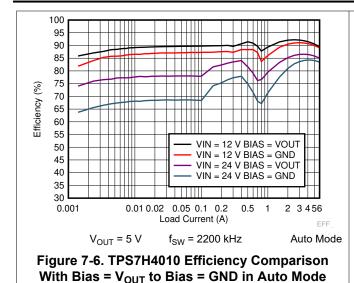

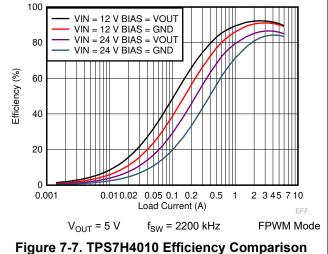

Figure 7-6 and Figure 7-7 show efficiency improvement with bias tied to  $V_{OUT}$  in a  $V_{OUT}$  = 5 V and  $f_{SW}$  = 2200 kHz application, in auto mode and FPWM mode, respectively.

With Bias = V<sub>OUT</sub> to Bias = GND in FPWM Mode

TI recommends tying the BIAS pin to  $V_{OUT}$  when  $V_{OUT}$  is equal to or greater than 3.3 V and no greater than 18 V. Tie the BIAS pin to ground when not in use. A ceramic capacitor,  $C_{BIAS}$ , can be used from the BIAS pin to ground for bypassing. If  $V_{OUT}$  has high frequency noise or spikes during transients or fault conditions, a resistor (1 to 10  $\Omega$ ) connected between  $V_{OUT}$  to BIAS can be used together with  $C_{BIAS}$  for filtering.

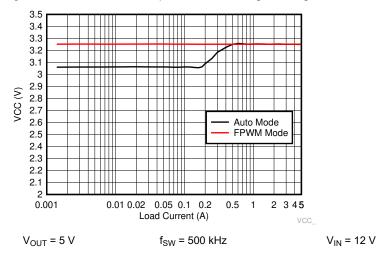

The VCC voltage is typically 3.27 V. When the TPS7H4010-SEP is operating in PFM mode with frequency foldback, VCC voltage is reduced to 3.1 V (typical) to further decrease the quiescent current and improve efficiency at very light loads. Figure 7-8 shows an example of VCC voltage change with mode change.

Figure 7-8. VCC Voltage vs Load Current

VCC voltage has an internal UVLO threshold,  $V_{CC\_UVLO}$ . When VCC voltage is higher than  $V_{CC\_UVLO}$  rising threshold, the device is active and in normal operation if  $V_{EN} > V_{EN\_VOUT\_H}$ . If VCC voltage droops below  $V_{CC\_UVLO}$  falling threshold, the  $V_{OUT}$  is shut down.

## 7.3.7 Soft Start and Voltage Tracking

The TPS7H4010-SEP features controlled output voltage ramp during start-up. The soft-start feature reduces inrush current during start-up and improves system performance and reliability.

If the SS/TRK pin is floating, the TPS7H4010-SEP starts up following the fixed internal soft-start ramp.

If longer soft-start time is desired, an external capacitor can be added from SS/TRK pin to ground. There is a  $2-\mu A$  (typical) internal current source,  $I_{SSC}$ , to charge the external capacitor. For a desired soft-start time  $t_{SS}$ , capacitance of  $C_{SS}$  can be found by Equation 12.

$$C_{SS} = I_{SSC} \times t_{SS} \tag{12}$$

#### where

- C<sub>SS</sub> = soft-start capacitor value (F)

- I<sub>SSC</sub> = soft-start charging current (A)

- t<sub>SS</sub> = desired soft-start time (s)

The FB voltage always follows the lower potential of the internal voltage ramp or the voltage on the SS/TRK pin. Thus, the soft-start time can only be extended longer than the internal soft-start time by connecting  $C_{SS}$ . Use  $C_{SS}$  to extend soft-start time when there are a large amount of output capacitors, or the output voltage is high, or the output is heavily loaded during start-up.

TPS7H4010-SEP is operating in diode emulation mode during start-up regardless of mode setting. The device is capable of starting up into pre-biased output conditions. During start-up, the device sets the minimum inductor current to zero to avoid back charging the input capacitors.

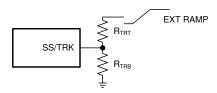

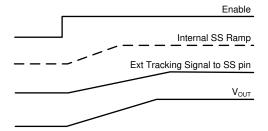

TPS7H4010-SEP can track an external voltage ramp applied to the SS/TRK pin, if the ramp is slower than the internal soft-start ramp. The external ramp final voltage after start-up must be greater than 1.5 V to avoid noise interfering with the reference voltage. Figure 7-9 shows how to use resistor divider to set V<sub>OUT</sub> to follow an external ramp.

Figure 7-9. Soft Start Tracking External Ramp

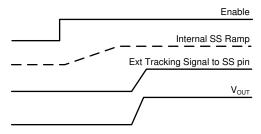

$V_{OUT}$  tracking also provides the option of ramping up faster than the internal start-up ramp. The FB voltage always follows the lower potential of the internal voltage ramp and the voltage on the SS/TRK pin. Figure 7-10 shows the case when  $V_{OUT}$  ramps slower than the internal ramp, while Figure 7-11 shows when  $V_{OUT}$  ramps faster than the internal ramp is delayed after the internal ramp is completed,  $V_{FB}$  follows the tracking ramp even if it is faster than the internal ramp. Faster start-up time may result in large inductor current during start-up. Use with special care.

Figure 7-10. Tracking With Longer Start-up Time Than the Internal Ramp

Figure 7-11. Tracking With Shorter Start-up Time Than the Internal Ramp

The SS/TRK pin is discharged to ground by an internal pulldown resistor  $R_{SSD}$  when the output voltage is shutting down, such as in the event of UVLO, thermal shutdown, hiccup, or  $V_{EN}$  = 0. If a large  $C_{SS}$  is used, and the time when  $V_{EN}$  = 0 V is very short, the  $C_{SS}$  may not be fully discharged before the next soft start. Under this condition, the FB voltage follows the internal ramp slew rate until the voltage on  $C_{SS}$  is reached, then follow the slew rate defined by  $C_{SS}$ .

## 7.3.8 Adjustable Switching Frequency

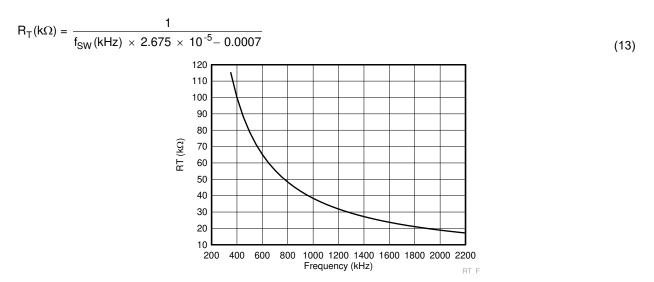

The internal oscillator frequency is controlled by the impedance on the RT pin. If the RT pin is open circuit, the TPS7H4010-SEP operates at its default switching frequency, 500 kHz. The RT pin is not designed to be connected directly to ground. To program the switching frequency by R<sub>T</sub> resistor, either Equation 13, Figure 7-12, or Table 7-1 can be used to find the resistance value.

Figure 7-12. R<sub>T</sub> Resistance vs Switching Frequency

**Table 7-1. Typical Frequency Setting Resistance**

| SWITCHING FREQUENCY f <sub>SW</sub> (kHz) | $R_T$ RESISTANCE (k $\Omega$ ) |

|-------------------------------------------|--------------------------------|

| 350                                       | 115                            |

| 400                                       | 100                            |

| 500                                       | 78.7 (or open)                 |

| 750                                       | 52.3                           |

| 1000                                      | 39.2                           |

| 1500                                      | 26.1                           |

| 2000                                      | 19.1                           |

| 2200                                      | 17.4                           |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

The choice of switching frequency is usually a compromise between conversion efficiency and the size of the solution. Lower switching frequency has lower switching losses (including gate charge losses, switch transition losses, etc.) and usually results in higher overall efficiency. However, higher switching frequency allows the use of smaller power inductor and output capacitors, hence a more compact design. Lower inductance also helps transient response (higher large signal slew rate of inductor current), and has lower DCR. The optimal switching frequency is usually a trade-off in a given application and thus needs to be determined on a case-by-case basis. Factors that need to be taken into account include input voltage range, output voltage, most frequent load current level or levels, external component choices, solution size/cost requirements, efficiency, and thermal management requirements.

The choice of switching frequency may also be limited whether an operating condition triggers  $t_{ON-MIN}$  or  $t_{OFF-MIN}$ . Minimum on-time,  $t_{ON-MIN}$ , is the smallest time that the HS switch can be on. Minimum off-time,  $t_{OFF-MIN}$ , is the smallest duration that the HS switch can be off.

In CCM operation,  $t_{ON-MIN}$  and  $t_{OFF\_MIN}$  limits the voltage conversion range given a selected switching frequency,  $t_{SW}$ . The minimum duty cycle allowed is:

$$D_{MIN} = t_{ON-MIN} \times f_{SW} \tag{14}$$

The maximum duty cycle allowed is:

$$D_{MAX} = 1 - t_{OFF-MIN} \times f_{SW}$$

(15)

Given an output voltage, the choice of the switching frequency affects the allowed input voltage range, solution size and efficiency. The maximum operational supply voltage can be found by:

$$V_{\text{IN MAX}} = V_{\text{OUT}} / (f_{\text{SW}} \times t_{\text{ON-MIN}}) \tag{16}$$

At lower supply voltage, the switching frequency decreases once  $t_{OFF-MIN}$  is tripped. The minimum  $V_{IN}$  without frequency foldback can be approximated by:

$$V_{\text{IN MIN}} = V_{\text{OUT}} / (1 - f_{\text{SW}} \times t_{\text{OFF-MIN}}) \tag{17}$$

With a desired V<sub>OUT</sub>, the range of allowed V<sub>IN</sub> is narrower with higher switching frequency.

TPS7H4010-SEP has an advanced frequency fold-back algorithm under both  $t_{ON\_MIN}$  and  $t_{OFF\_MIN}$  conditions. With frequency foldback, stable output voltage regulation is extended to wider range of supply voltages.

At very high  $V_{IN}$  conditions, where  $t_{ON\text{-}MIN}$  limitation is met, the switching frequency reduces to allow higher  $V_{IN}$  while maintaining  $V_{OUT}$  regulation. Note that the peak to peak inductor current ripple will increase with higher  $V_{IN}$  and lower frequency. TI does not recommend designing the circuit to operate with  $t_{ON\_{MIN}}$  under typical conditions.

At very low  $V_{IN}$  conditions, where  $t_{OFF-MIN}$  limitation is met, the switching frequency decreases until  $t_{ON-MAX}$  condition is met. Such frequency foldback mechanism allows the TPS7H4010-SEP to have very low dropout voltage regardless of frequency setting.

## 7.3.9 Frequency Synchronization and Mode Setting

The TPS7H4010-SEP switching action can synchronize to an external clock from 350 kHz to 2.2 MHz. TI recommends connecting the external clock to the SYNC/MODE pin with an appropriate termination resistor. Ground the SYNC/MODE pin if not used.

Figure 7-13. Frequency Synchronization

www.ti.com

Recommendations for the external clock include a high level no lower than 2 V, low level no higher than 0.4 V, duty cycle between 10% and 90%, and both positive and negative pulse width no shorter than 80 ns. When the external clock fails at logic high or low, the TPS7H4010-SEP switches at the frequency programmed by the R<sub>T</sub> resistor after a time-out period. TI recommends connecting a resistor to the RT pin such that the internal oscillator frequency is the same as the external clock frequency. This allows the regulator to continue operating at approximately the same switching frequency if the external clock fails with the same control loop behavior.

The SYNC/MODE pin is also used as an operation mode control input.

- To set the operation in auto mode, connect SYNC/MODE pin to ground, or a logic signal lower than 0.3 V.

- To set the operation in FPWM mode, connect SYNC/MODE pin to a bias voltage or logic signal greater than 0.6 V.

- When the TPS7H4010-SEP is synchronized to an external clock, the operation mode is FPWM.

Table 7-2 summarizes the operation mode and features according to the SYNC/MODE input signal. For more details, see Active Mode and Auto Mode and FPWM Mode sections.

| SYNC/MODE INPUT | SWITCHING<br>FREQUENCY         | OPERATING<br>MODE | LIGHT LOAD BEHAVIOR                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|--------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic low       | Set by R <sub>T</sub> resistor | Auto mode         | <ul> <li>No negative inductor current, device operates in discontinuous conduction mode (DCM) when current valley reaches 0 A</li> <li>Minimum peak inductor current is limited at I<sub>PEAK_MIN</sub>; device operates in pulse frequency modulation (PFM) mode when peak current reaches I<sub>PEAK_MIN</sub></li> <li>Switching frequency reduces in PFM mode</li> </ul> |

| Logic high      | Set by R <sub>T</sub> resistor |                   | Fixed frequency continuous conduction mode (CCM) regardless of load                                                                                                                                                                                                                                                                                                          |

| External clock  | Set by external clock          | FPWM mode         | <ul> <li>Inductor current have negative portion at light loads</li> <li>No I<sub>PEAK_MIN</sub></li> </ul>                                                                                                                                                                                                                                                                   |

Table 7-2. SYNC/MODE Pin Settings and Operation Modes

## 7.3.10 Internal Compensation and CFF

The TPS7H4010-SEP is internally compensated. The internal compensation is designed such that the loop response is stable over a wide operating frequency and output voltage range. The internal R-C values are 500  $k\Omega$  and 30 pF, respectively.

When large resistance value (M $\Omega$ ) is used for R<sub>FBT</sub>, the pole formed by an internal parasitic capacitor and R<sub>FBT</sub> can be low enough to reduce the phase margin. If only low ESR output capacitors (ceramic types) are used for C<sub>OUT</sub>, the control loop could have low phase margin. To provide a phase boost an external feed-forward capacitor (C<sub>FF</sub>) can be added in parallel with R<sub>FBT</sub>. Choose the C<sub>FF</sub> capacitor to provide most phase boost at the estimated crossover frequency fx:

$$f_X = \frac{K}{V_{OUT} \times C_{OUT}}$$

(18)

#### where

## K = 24.16 with TPS7H4010-SEP

Select  $C_{OUT}$  so that the  $f_X$  is no higher than 1/6 of the switching frequency. Typically,  $f_X$  /  $f_{SW}$  = 1/10 to 1/8 provides a good combination of stability and performance.

Place the external feed-forward capacitor in parallel with the top resistor divider R<sub>FBT</sub> when additional phase boost is needed.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

Figure 7-14. Feed-Forward Capacitor for Loop Compensation

The feed-forward capacitor  $C_{FF}$  in parallel with  $R_{FBT}$  places an additional zero before the crossover frequency of the control loop to boost phase margin. The zero frequency can be found by Equation 19:

$$f_{Z-CFF} = 1 / (2\pi \times R_{FBT} \times C_{FF})$$

(19)

An additional pole is also introduced with CFF at the frequency of:

$$f_{P-CFF} = 1 / (2\pi \times C_{FF} \times (R_{FBT} / R_{FBB}))$$

(20)

Select the  $C_{FF}$  so that the bandwidth of the control loop without the  $C_{FF}$  is centered between  $f_{Z-CFF}$  and  $f_{P-CFF}$ . The zero at  $f_{Z-CFF}$  adds phase boost at the crossover frequency and improves transient response. The pole at  $f_{P-CFF}$  helps maintaining proper gain margin at frequency beyond the crossover.

The need of  $C_{FF}$  depends on  $R_{FBT}$  and  $C_{OUT}$ . Typically, choose  $R_{FBT} \le 100$  k $\Omega$ .  $C_{FF}$  may not be required, because the internal parasitic pole is at higher frequency. If  $C_{OUT}$  has larger ESR, and ESR zero  $f_{Z-ESR} = 1$  /  $(2\pi \times ESR \times C_{OUT})$  is low enough to provide phase boost around the crossover frequency, do not use  $C_{FF}$ . Equation 21 was tested for ceramic output capacitors:

$$C_{FF} = \frac{1}{2 \times \pi \times f_{x}} \times \frac{1}{\sqrt{R_{FBT} \times (R_{FBT} // R_{FBB})}}$$

(21)

The  $C_{FF}$  creates a time constant with  $R_{FBT}$  that couples in the attenuated output voltage ripple to the FB node. If the  $C_{FF}$  value is too large, it can couple too much ripple to the FB and affect  $V_{OUT}$  regulation. It could also couple too much transient voltage deviation and falsely trigger PGOOD flag.

## 7.3.11 Bootstrap Capacitor and V<sub>BOOT-UVLO</sub>

The driver of the HS switch requires a bias voltage higher than the  $V_{IN}$  voltage. The capacitor,  $C_{BOOT}$  in Figure 8-1, connected between CBOOT and SW pins works as a charge pump to boost voltage on the CBOOT pin to  $(V_{SW} + V_{CC})$ . A boot diode is integrated on the die to minimize external component count. TI recommends a high-quality 0.47- $\mu$ F, 6.3-V or higher voltage ceramic capacitor for  $C_{BOOT}$ . The  $V_{BOOT\_UVLO}$  threshold is designed to maintain proper HS switch operation. If the  $C_{BOOT}$  is not charged above this voltage with respect to SW, the device initiates a charging sequence using the LS switch before turning on the HS switch.

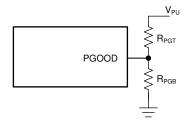

#### 7.3.12 Power-Good and Overvoltage Protection

The TPS7H4010-SEP has a built-in power-good (PGOOD) flag to indicate whether the output voltage is at an appropriate level or not. The PGOOD flag can be used for start-up sequencing of multiple rails. The PGOOD pin is an open-drain output that requires a pullup resistor to an appropriate logic voltage (any voltage below 15 V). The pin can sink 5 mA of current and maintain its specified logic low level. A typical pullup resistor value is 10 k $\Omega$  to 100 k $\Omega$ . When the FB voltage is higher than  $V_{PGOOD-OV}$  or lower than  $V_{PGOOD-UV}$  threshold, the PGOOD internal switch is turned on, and the PGOOD pin voltage is pulled low. When the FB is within the range, the PGOOD switch is turned off, and the pin is pulled up to the voltage connected to the pullup resistor. The PGOOD function also have a deglitch timer for about 140  $\mu$ s for each transition. If it is desired to pull up PGOOD pin to a voltage higher than 15 V, a resistor divider can be used to divide the voltage down.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Figure 7-15. Divider for PGOOD Pullup Voltage

With a given pullup voltage  $V_{PU}$ , select a desired voltage on the PGOOD pin,  $V_{PG}$ . With a selected  $R_{PGT}$ , the  $R_{PGB}$  can be found by:

$$R_{PGB} = \frac{V_{PG}}{V_{PU} - V_{PG}} R_{PGT}$$

(22)

When the device is disabled, the output voltage is low, and the PGOOD flag indicates logic low as long as  $V_{IN} > 2 \text{ V}$ .

#### 7.3.13 Overcurrent and Short-Circuit Protection

The TPS7H4010-SEP is protected from overcurrent conditions with cycle-by-cycle current limiting on both HS and LS MOSFETs.

The HS switch is turned off when HS current goes beyond the peak current limit,  $I_{HS-LIMIT}$ . The LS switch can only be turned off when LS current is below LS current limit,  $I_{LS-LIMIT}$ . If the LS switch current is higher than  $I_{LS-LIMIT}$  at the end of a switching cycle, the switching cycle is extended until the LS current reduces below the limit.

Current limiting on both HS and LS switches provides tighter control of the maximum DC inductor current, or output current. They also help prevent runaway current at extreme conditions. With TPS7H4010-SEP, the maximum output current is always limited at:

$$I_{DC LIMIT} = (I_{HS LIMIT} + I_{LS LIMIT})/2$$

(23)