# **LM3S1776 ROM**

# **USER'S GUIDE**

# Copyright

Copyright © 2008-2011 Texas Instruments Incorporated. All rights reserved. Stellaris and StellarisWare are registered trademarks of Texas Instruments. ARM and Thumb are registered trademarks and Cortex is a trademark of ARM Limited. Other names and brands may be claimed as the property of others.

APlease be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

Texas Instruments 108 Wild Basin, Suite 350 Austin, TX 78746 Main: +1-512-279-8800 Fax: +1-512-279-8879 http://www.ti.com/stellaris

# **Revision Information**

This is version 461 of this document, last updated on September 9, 2011.

# **Table of Contents**

| Copy                                                                                                                          | yright                                                                                                                                                                                                                                                                                | 2                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Revi                                                                                                                          | sion Information                                                                                                                                                                                                                                                                      | 2                                                                                     |

| 1                                                                                                                             | Introduction                                                                                                                                                                                                                                                                          | 5                                                                                     |

| <b>2</b><br>2.1<br>2.2                                                                                                        | Boot Loader                                                                                                                                                                                                                                                                           | <b>7</b><br>7<br>7                                                                    |

| 3<br>3.1<br>3.2                                                                                                               | Analog to Digital Converter (ADC)                                                                                                                                                                                                                                                     | 13<br>13<br>13                                                                        |

| <b>4</b><br>4.1<br>4.2                                                                                                        | Flash                                                                                                                                                                                                                                                                                 | 25<br>25<br>25                                                                        |

| <b>5</b><br>5.1<br>5.2                                                                                                        | GPIO                                                                                                                                                                                                                                                                                  | <b>35</b><br>35<br>35                                                                 |

| <b>6</b><br>6.1<br>6.2                                                                                                        | Inter-Integrated Circuit (I2C) Introduction                                                                                                                                                                                                                                           | <b>51</b> 51 52                                                                       |

| <b>7</b><br>7.1<br>7.2                                                                                                        | Interrupt Controller (NVIC) Introduction                                                                                                                                                                                                                                              | <b>67</b><br>67                                                                       |

| 8                                                                                                                             | Pulse Width Modulator (PWM)                                                                                                                                                                                                                                                           | 71                                                                                    |

| 8.1<br>8.2                                                                                                                    | Introduction                                                                                                                                                                                                                                                                          | 71<br>71                                                                              |

| 8.1                                                                                                                           | Introduction                                                                                                                                                                                                                                                                          | 71                                                                                    |

| 8.1<br>8.2<br><b>9</b><br>9.1<br>9.2<br><b>10</b>                                                                             | Introduction                                                                                                                                                                                                                                                                          | 71<br>71<br><b>87</b><br>87                                                           |

| 8.1<br>8.2<br>9<br>9.1<br>9.2<br>10<br>10.1<br>10.2<br>11                                                                     | Introduction . Functions .  Synchronous Serial Interface (SSI) Introduction . Functions .  System Control . Introduction . Functions .  System Tick (SysTick)                                                                                                                         | 71<br>71<br><b>87</b><br>87<br>87<br><b>95</b><br>96<br><b>115</b>                    |

| 8.1<br>8.2<br>9<br>9.1<br>9.2<br>10<br>10.1<br>10.2<br>11<br>11.1<br>11.2<br>12<br>12.1                                       | Introduction Functions  Synchronous Serial Interface (SSI) Introduction Functions  System Control Introduction Functions  System Tick (SysTick) Introduction Functions  Timer Introduction                                                                                            | 71<br>71<br><b>87</b><br>87<br>87<br><b>95</b><br>96<br>115                           |

| 8.1<br>8.2<br>9<br>9.1<br>9.2<br>10<br>10.1<br>10.2<br>11<br>11.1<br>11.2<br>12.1<br>12.2<br>13<br>13.1                       | Introduction Functions  Synchronous Serial Interface (SSI) Introduction Functions  System Control Introduction Functions  System Tick (SysTick) Introduction Functions  Timer Introduction Functions  UART Introduction                                                               | 71<br>71<br>87<br>87<br>87<br>95<br>95<br>115<br>115<br>119                           |

| 8.1<br>8.2<br>9<br>9.1<br>9.2<br>10<br>10.1<br>10.2<br>11<br>11.1<br>11.2<br>12.1<br>12.2<br>13<br>13.1<br>13.2<br>14<br>14.1 | Introduction Functions  Synchronous Serial Interface (SSI) Introduction Functions  System Control Introduction Functions  System Tick (SysTick) Introduction Functions  Timer Introduction Functions  UART Introduction Functions  Watchdog Timer Introduction Introduction Functions | 71<br>71<br><b>87</b><br>87<br>87<br>87<br>95<br>95<br>96<br>115<br>115<br>119<br>119 |

# 1 Introduction

The LM3S1776 ROM contains the Stellaris® Peripheral Driver Library and the Stellaris Boot Loader. The peripheral driver library can be utilized by applications to reduce their flash footprint, allowing the flash to be used for other purposes (such as additional features in the application). The boot loader is used as an initial program loader (when the flash is empty) as well as an application-initiated firmware upgrade mechanism (by calling back to the boot loader).

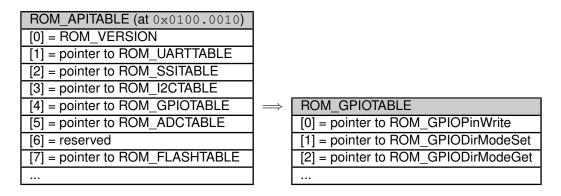

There is a table at the beginning of the ROM that points to the entry points for the APIs that are provided in the ROM. Accessing the API through these tables provides scalability; while the API locations may change in future versions of the ROM, the API tables will not. The tables are split into two levels; the main table contains one pointer per peripheral which points to a secondary table that contains one pointer per API that is associated with that peripheral. The main table is located at  $0 \times 0100.0010$ , right after the Cortex-M3 vector table in the ROM.

The following table shows a small portion of the API tables in a graphical form that helps to illustrate the arrangement of the tables:

From this, the address of the ROM\_GPIOTABLE table is located in the memory location at  $0 \times 0100.0020$ . The address of the ROM\_GPIODirModeSet() function is contained at offset  $0 \times 4$  from that table. In the function documentation, this is represented as:

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIODirModeSet is a function pointer located at ROM_GPIOTABLE[1].

```

The Stellaris Peripheral Driver Library contains a file called <code>driverlib/rom.h</code> that assists with calling the peripheral driver library functions in the ROM. The naming conventions for the tables and APIs that are used in this document match those used in that file.

The following is an example of calling the ROM GPIODirModeSet() function:

```

#define TARGET_IS_DUSTDEVIL_RA0

#include "inc/hw_memmap.h"

#include "inc/hw_types.h"

#include "driverlib/gpio.h"

#include "driverlib/rom.h"

int

main(void)

{

// ...

ROM_GPIODirModeSet(GPIO_PORTA_BASE, GPIO_PIN_0, GPIO_DIR_MODE_OUT);

```

```

// ....

```

See the "Using the ROM" chapter of the *Stellaris Peripheral Driver Library User's Guide* for more details on calling the ROM functions and using driverlib/rom.h.

The API provided by the ROM can be utilized by any compiler so long as it complies with the Embedded Applications Binary Interface (EABI), which includes all recent compilers for the Stellaris microcontroller.

### **Documentation Overview**

The ROM-based Stellaris Boot Loader is described in chapter 2, and the ROM-based Stellaris Peripheral Driver Library is described in chapters 3 through 14.

# 2 Boot Loader

| Introduction      | <br>. 7 |

|-------------------|---------|

| Serial Interfaces | <br>. 7 |

## 2.1 Introduction

The ROM-based boot loader is executed each time the device is reset when the flash is empty. The flash is assumed to be empty if the first two words are all ones (since the second word is the reset vector address, it must be programmed for an application in flash to execute). When run, it will allow the flash to be updated using one of the following interfaces:

- UART0 using a custom serial protocol

- SSI0 using a custom serial protocol

- I2C0 using a custom serial protocol

Since the boot loader has no knowledge of the frequency of the attached crystal, or in fact if one is even present, it operates entirely from the internal oscillator. This is a 12-MHz clock, with an accuracy of  $\pm$  30%, meaning that the boot loader can expect to run from a clock as slow as 8.4 MHz or as fast as 15.6 MHz.

The LM Flash Programmer GUI can be used to download an application via the boot loader over the UART on a PC. The LM Flash Programmer utility is available for download from www.ti.com/stellaris.

# 2.2 Serial Interfaces

The serial interfaces used to communicate with the boot loader share a common protocol and differ only in the physical connections and signaling used to transfer the bytes of the protocol.

### 2.2.1 UART Interface

The UART pins **U0Tx** and **U0Rx** are used to communicate with the boot loader. The device communicating with the boot loader is responsible for driving the **U0Rx** pin on the Stellaris microcontroller, while the Stellaris microcontroller drives the **U0Tx** pin.

The serial data format is fixed at 8 data bits, no parity, and one stop bit. An auto-baud feature is used to determine the baud rate at which data is transmitted. Since the system clock must be at least 32 times the baud rate, the maximum baud rate that can be used is 262.5 Kbaud (which is 8.4 MHz divided by 32).

When an application calls back to the ROM-based boot loader to start an update over the UART port, the auto-baud feature is bypassed, along with UART configuration and pin configuration. Therefore, the UART must be configured and the UART pins switched to their hardware function before calling the boot loader.

### 2.2.2 SSI Interface

The SSI pins **SSIFss**, **SSICIk**, **SSITx**, and **SSIRx** are used to communicate with the boot loader. The device communicating with the boot loader is responsible for driving the **SSIRx**, **SSICIk**, and **SSIFss** pins, while the Stellaris microcontroller drives the **SSITx** pin.

The serial data format is fixed to the Motorola format with SPH set to 1 and SPO set to 1 (see the applicable Stellaris family data sheet for more information on this format). Since the system clock must be at least 12 times the serial clock rate, the maximum serial clock rate that can be used is 700 KHz (which is 8.4 MHz divided by 12).

When an application calls back to the ROM-based boot loader to start an update over the SSI port, the SSI configuration and pin configuration is bypassed. Therefore, the SSI port must be configured and the SSI pins switched to their hardware function before calling the boot loader.

### 2.2.3 I2C Interface

The I2C pins I2CSCL and I2CSDA are used to communicate with the boot loader. The device communicating with the boot loader must operate as the I2C master and provide the I2CSCL signal. The I2CSDA pin is open-drain and can be driven by either the master or the slave I2C device.

The I2C interface can run at up to 400 KHz, the maximum rate supported by the I2C protocol. The boot loader uses an I2C slave address of 0x42.

When an application calls back to the ROM-based boot loader to start an update over the I2C port, the I2C configuration and pin configuration is bypassed. Therefore, the I2C port must be configured, the I2C slave address set, and the I2C pins switched to their hardware function before calling the boot loader. Additionally, the I2C master must be enabled since it is used to detect start and stop conditions on the I2C bus.

### 2.2.4 Protocol

The boot loader uses well-defined packets to ensure reliable communications with the update program. The packets are always acknowledged or not acknowledged by the communicating devices. The packets use the same format for receiving and sending packets. This includes the method used to acknowledge successful or unsuccessful reception of a packet. While the actual signaling on the serial ports is different, the packet format remains independent of the method of transporting the data.

The following steps must be performed to successfully send a packet:

- 1. Send the size of the packet that will be sent to the device. The size is always the number of bytes of data + 2 bytes.

- 2. Send the checksum of the data buffer to help ensure proper transmission of the command. The checksum is simply a sum of the data bytes.

- 3. Send the actual data bytes.

- 4. Wait for a single-byte acknowledgment from the device that it either properly received the data or that it detected an error in the transmission.

The following steps must be performed to successfully receive a packet:

- Wait for non-zero data to be returned from the device. This is important as the device may send zero bytes between a sent and received data packet. The first non-zero byte received will be the size of the packet that is being received.

- 2. Read the next byte which will be the checksum for the packet.

- Read the data bytes from the device. There will be packet size 2 bytes of data sent during the data phase. For example, if the packet size was 3, then there is only 1 byte of data to be received.

- 4. Calculate the checksum of the data bytes and ensure that it matches the checksum received in the packet.

- 5. Send an acknowledge (ACK) or not-acknowledge (NAK) to the device to indicate the successful or unsuccessful reception of the packet.

An acknowledge packet is sent whenever a packet is successfully received and verified by the boot loader. A not-acknowledge packet is sent whenever a sent packet is detected to have an error, usually as a result of a checksum error or just malformed data in the packet. This allows the sender to re-transmit the previous packet.

The following commands are used by the custom protocol:

```

COMMAND_PING = 0x20

```

This command is used to receive an acknowledge from the boot loader indicating that communication has been established. This command is a single byte.

The format of the command is as follows:

```

unsigned char ucCommand[1];

ucCommand[0] = COMMAND_PING;

```

COMMAND\_DOWNLOAD = 0x21

This command is sent to the boot loader to indicate where to store data and how many bytes will be sent by the COMMAND\_SEND\_DATA commands that follow. The command consists of two 32-bit values that are both transferred MSB first. The first 32-bit value is the address to start programming data into, while the second is the 32-bit size of the data that will be sent. This command also triggers a mass erase of the flash, which causes the command to take longer to send the ACK/NAK in response to the command. This command should be followed by a COMMAND\_GET\_STATUS to ensure that the program address and program size were valid for the microcontroller running the boot loader.

The format of the command is as follows:

```

unsigned char ucCommand[9];

ucCommand[0] = COMMAND_DOWNLOAD;

ucCommand[1] = Program Address [31:24];

ucCommand[2] = Program Address [23:16];

ucCommand[3] = Program Address [7:0];

ucCommand[5] = Program Size [31:24];

ucCommand[6] = Program Size [23:16];

ucCommand[7] = Program Size [15:8];

ucCommand[8] = Program Size [7:0];

```

$COMMAND_RUN$ = 0x22

This command is sent to the boot loader to transfer execution control to the specified address. The command is followed by a 32-bit value, transferred MSB first, that is the address to which execution control is transferred.

The format of the command is as follows:

```

unsigned char ucCommand[5];

ucCommand[0] = COMMAND_RUN;

ucCommand[1] = Run Address [31:24];

ucCommand[2] = Run Address [23:16];

ucCommand[3] = Run Address [15:8];

ucCommand[4] = Run Address [7:0];

```

COMMAND\_GET\_STATUS = 0x23

This command returns the status of the last command that was issued. Typically, this command should be received after every command is sent to ensure that the previous command was successful or, if unsuccessful, to properly respond to a failure. The command requires one byte in the data of the packet and the boot loader should respond by sending a packet with one byte of data that contains the current status code.

The format of the command is as follows:

```

unsigned char ucCommand[1];

ucCommand[0] = COMMAND_GET_STATUS;

```

The following are the definitions for the possible status values that can be returned from the boot loader when COMMAND\_GET\_STATUS is sent to the the microcontroller.

```

COMMAND_RET_SUCCESS

COMMAND_RET_UNKNOWN_CMD

COMMAND_RET_INVALID_CMD

COMMAND_RET_INVALID_ADD

COMMAND_RET_FLASH_FAIL

```

COMMAND\_SEND\_DATA = 0x24 This command should only follow a COMMAND\_DOWNLOAD command or another COMMAND\_SEND\_DATA command, if more data is needed. Consecutive send data commands automatically increment the address and continue programming from the previous location. The transfer size is limited by the maximum size of a packet, which allows up to 252 data bytes to be transferred at a time. The command terminates programming once the number of bytes indicated by the COMMAND\_DOWNLOAD command has been received. Each time this function is called, it should be followed by a COMMAND\_GET\_STATUS command to ensure that the data was successfully programmed into the flash. If the boot loader sends a NAK to this command, the boot loader will not increment the current address which allows for retransmission of the previous data.

The format of the command is as follows:

```

unsigned char ucCommand[9];

ucCommand[0] = COMMAND_SEND_DATA

ucCommand[1] = Data[0];

ucCommand[2] = Data[1];

ucCommand[3] = Data[2];

ucCommand[4] = Data[3];

ucCommand[5] = Data[4];

ucCommand[6] = Data[5];

ucCommand[7] = Data[6];

ucCommand[8] = Data[7];

```

COMMAND\_RESET = 0x25

This command is used to tell the boot loader to reset. This is used after downloading a new image to the microcontroller to cause the new application to start from a reset. The normal boot sequence occurs and the image runs as if from a hardware reset. It can also be used to reset the boot loader if a critical error occurs and the host device wants to restart communication with the boot loader.

The boot loader responds with an ACK signal to the host device before actually executing the software reset on the microcontroller running the boot loader. This informs the updater application that the command was received successfully and the part will be reset.

The format of the command is as follows:

```

unsigned char ucCommand[1];

ucCommand[0] = COMMAND_RESET;

```

The definitions for these commands are provided as part of the Stellaris Peripheral Driver Library, in boot\_loader/bl\_commands.h.

# 3 Analog to Digital Converter (ADC)

| Introductio | n. | <br> | <br> | <br> | <br> | <br> | <br> | <br>٠. | ٠. | <br> | <br> | <br> | ٠. | <br>٠. | ٠. | ٠. | <br> | <br>13 |

|-------------|----|------|------|------|------|------|------|--------|----|------|------|------|----|--------|----|----|------|------|------|------|------|------|------|------|--------|

| Functions   |    | <br>   |    | <br> | <br> | <br> |    | <br>   |    |    | <br> | <br>13 |

## 3.1 Introduction

The analog to digital converter (ADC) API provides a set of functions for dealing with the ADC. Functions are provided to configure the sample sequencers, read the captured data, register a sample sequence interrupt handler, and handle interrupt masking/clearing.

The ADC supports six input channels plus an internal temperature sensor. Four sampling sequences, each with configurable trigger events, can be captured. The first sequence will capture up to eight samples, the second and third sequences will capture up to four samples, and the fourth sequence will capture a single sample. Each sample can be the same channel, different channels, or any combination in any order.

The sample sequences have configurable priorities that determine the order in which they are captured when multiple triggers occur simultaneously. The highest priority sequence that is currently triggered will be sampled. Care must be taken with triggers that occur frequently (such as the "always" trigger); if their priority is too high it is possible to starve the lower priority sequences.

Hardware oversampling of the ADC data is available for improved accuracy. An oversampling factor of 2x, 4x, 8x, 16x, 32x, and 64x is supported, but reduces the throughput of the ADC by a corresponding factor. Hardware oversampling is applied uniformly across all sample sequences.

# 3.2 Functions

### **Functions**

- void ROM\_ADCHardwareOversampleConfigure (unsigned long ulBase, unsigned long ulFactor)

- void ROM ADCIntClear (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM ADCIntDisable (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM\_ADCIntEnable (unsigned long ulBase, unsigned long ulSequenceNum)

- unsigned long ROM\_ADCIntStatus (unsigned long ulBase, unsigned long ulSequenceNum, tBoolean bMasked)

- void ROM ADCProcessorTrigger (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM\_ADCSequenceConfigure (unsigned long ulBase, unsigned long ulSequenceNum, unsigned long ulTrigger, unsigned long ulPriority)

- long ROM\_ADCSequenceDataGet (unsigned long ulBase, unsigned long ulSequenceNum, unsigned long \*pulBuffer)

- void ROM\_ADCSequenceDisable (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM ADCSequenceEnable (unsigned long ulBase, unsigned long ulSequenceNum)

- long ROM\_ADCSequenceOverflow (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM\_ADCSequenceOverflowClear (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM\_ADCSequenceStepConfigure (unsigned long ulBase, unsigned long ulSequenceNum, unsigned long ulStep, unsigned long ulConfig)

- long ROM\_ADCSequenceUnderflow (unsigned long ulBase, unsigned long ulSequenceNum)

- void ROM\_ADCSequenceUnderflowClear (unsigned long ulBase, unsigned long ulSequenceNum)

### 3.2.1 Function Documentation

### 3.2.1.1 ROM ADCHardwareOversampleConfigure

Configures the hardware oversampling factor of the ADC.

### Prototype:

void

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCHardwareOversampleConfigure is a function pointer located at ROM_ADCTABLE[14].

```

#### Parameters:

ulBase is the base address of the ADC module.ulFactor is the number of samples to be averaged.

### **Description:**

This function configures the hardware oversampling for the ADC, which can be used to provide better resolution on the sampled data. Oversampling is accomplished by averaging multiple samples from the same analog input. Six different oversampling rates are supported; 2x, 4x, 8x, 16x, 32x, and 64x. Specifying an oversampling factor of zero will disable the hardware oversampler.

Hardware oversampling applies uniformly to all sample sequencers. It does not reduce the depth of the sample sequencers like the software oversampling APIs; each sample written into the sample sequence FIFO is a fully oversampled analog input reading.

Enabling hardware averaging increases the precision of the ADC at the cost of throughput. For example, enabling 4x oversampling reduces the throughput of a 250 KSps ADC to 62.5 KSps.

#### Returns:

None.

### 3.2.1.2 ROM ADCIntClear

Clears sample sequence interrupt source.

#### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCIntClear is a function pointer located at ROM_ADCTABLE[4].

```

#### Parameters:

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

### **Description:**

The specified sample sequence interrupt is cleared, so that it no longer asserts. This must be done in the interrupt handler to keep it from being called again immediately upon exit.

#### Note:

Since there is a write buffer in the Cortex-M3 processor, it may take several clock cycles before the interrupt source is actually cleared. Therefore, it is recommended that the interrupt source be cleared early in the interrupt handler (as opposed to the very last action) to avoid returning from the interrupt handler before the interrupt source is actually cleared. Failure to do so may result in the interrupt handler being immediately reentered (since NVIC still sees the interrupt source asserted).

#### Returns:

None.

### 3.2.1.3 ROM ADCIntDisable

Disables a sample sequence interrupt.

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCIntDisable is a function pointer located at ROM_ADCTABLE[1].

```

#### Parameters:

```

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

```

### Description:

This function disables the requested sample sequence interrupt.

### Returns:

None.

### 3.2.1.4 ROM ADCIntEnable

Enables a sample sequence interrupt.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCINtEnable is a function pointer located at ROM_ADCTABLE[2].

```

#### Parameters:

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

### **Description:**

This function enables the requested sample sequence interrupt. Any outstanding interrupts are cleared before enabling the sample sequence interrupt.

#### Returns:

None.

### 3.2.1.5 ROM\_ADCIntStatus

Gets the current interrupt status.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCIntStatus is a function pointer located at ROM_ADCTABLE[3].

```

#### Parameters:

ulBase is the base address of the ADC module.

ulSequenceNum is the sample sequence number.

**bMasked** is false if the raw interrupt status is required and true if the masked interrupt status is required.

### Description:

This returns the interrupt status for the specified sample sequence. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

#### Returns:

The current raw or masked interrupt status.

### 3.2.1.6 ROM ADCProcessorTrigger

Causes a processor trigger for a sample sequence.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCProcessorTrigger is a function pointer located at ROM_ADCTABLE[13].

```

#### Parameters:

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

### **Description:**

This function triggers a processor-initiated sample sequence if the sample sequence trigger is configured to ADC\_TRIGGER\_PROCESSOR.

#### Returns:

None.

### 3.2.1.7 ROM ADCSequenceConfigure

Configures the trigger source and priority of a sample sequence.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceConfigure is a function pointer located at ROM_ADCTABLE[7].

```

### Parameters:

ulBase is the base address of the ADC module.

ulSequenceNum is the sample sequence number.

ulTrigger is the trigger source that initiates the sample sequence; must be one of the ADC\_TRIGGER\_\* values.

**ulPriority** is the relative priority of the sample sequence with respect to the other sample sequences.

### **Description:**

This function configures the initiation criteria for a sample sequence. Valid sample sequences range from zero to three; sequence zero will capture up to eight samples, sequences one and

two will capture up to four samples, and sequence three will capture a single sample. The trigger condition and priority (with respect to other sample sequence execution) is set.

The *ulTrigger* parameter can take on the following values:

- ADC\_TRIGGER\_PROCESSOR A trigger generated by the processor, via the ROM\_ADCProcessorTrigger() function.

- ADC TRIGGER EXTERNAL A trigger generated by an input from the Port B4 pin.

- ADC\_TRIGGER\_TIMER A trigger generated by a timer; configured with ROM TimerControlTrigger().

- ADC\_TRIGGER\_PWM0 A trigger generated by the first PWM generator; configured with ROM\_PWMGenIntTrigEnable().

- ADC\_TRIGGER\_PWM1 A trigger generated by the second PWM generator; configured with ROM\_PWMGenIntTrigEnable().

- ADC\_TRIGGER\_PWM2 A trigger generated by the third PWM generator; configured with ROM\_PWMGenIntTrigEnable().

- ADC\_TRIGGER\_ALWAYS A trigger that is always asserted, causing the sample sequence to capture repeatedly (so long as there is not a higher priority source active).

Note that not all trigger sources are available on all Stellaris family members; consult the data sheet for the device in question to determine the availability of triggers.

The *ulPriority* parameter is a value between 0 and 3, where 0 represents the highest priority and 3 the lowest. Note that when programming the priority among a set of sample sequences, each must have unique priority; it is up to the caller to guarantee the uniqueness of the priorities.

#### Returns:

None.

### 3.2.1.8 ROM ADCSequenceDataGet

Gets the captured data for a sample sequence.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceDataGet is a function pointer located at ROM_ADCTABLE[0].

```

### Parameters:

```

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.pulBuffer is the address where the data is stored.

```

### **Description:**

This function copies data from the specified sample sequence output FIFO to a memory resident buffer. The number of samples available in the hardware FIFO are copied into the buffer, which is assumed to be large enough to hold that many samples. This will only return the samples that are presently available, which may not be the entire sample sequence if it is in the process of being executed.

#### Returns:

Returns the number of samples copied to the buffer.

### 3.2.1.9 ROM\_ADCSequenceDisable

Disables a sample sequence.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceDisable is a function pointer located at ROM_ADCTABLE[6].

```

#### **Parameters:**

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

### **Description:**

Prevents the specified sample sequence from being captured when its trigger is detected. A sample sequence should be disabled before it is configured.

#### Returns:

None.

### 3.2.1.10 ROM ADCSequenceEnable

Enables a sample sequence.

### Prototype:

```

void

ROM_ADCSequenceEnable(unsigned long ulBase,

unsigned long ulSequenceNum)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceEnable is a function pointer located at ROM_ADCTABLE[5].

```

### Parameters:

ulBase is the base address of the ADC module.

ulSequenceNum is the sample sequence number.

### **Description:**

Allows the specified sample sequence to be captured when its trigger is detected. A sample sequence must be configured before it is enabled.

#### Returns:

None.

### 3.2.1.11 ROM\_ADCSequenceOverflow

Determines if a sample sequence overflow occurred.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceOverflow is a function pointer located at ROM_ADCTABLE[9].

```

#### Parameters:

```

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

```

### Description:

This determines if a sample sequence overflow has occurred. This will happen if the captured samples are not read from the FIFO before the next trigger occurs.

### Returns:

Returns zero if there was not an overflow, and non-zero if there was.

### 3.2.1.12 ROM ADCSequenceOverflowClear

Clears the overflow condition on a sample sequence.

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceOverflowClear is a function pointer located at ROM_ADCTABLE[10].

```

#### Parameters:

```

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

```

### **Description:**

This will clear an overflow condition on one of the sample sequences. The overflow condition must be cleared in order to detect a subsequent overflow condition (it otherwise causes no harm).

#### Returns:

None.

### 3.2.1.13 ROM ADCSequenceStepConfigure

Configure a step of the sample sequencer.

### **Prototype:**

unsigned long ulStep,

unsigned long ulConfig)

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceStepConfigure is a function pointer located at ROM_ADCTABLE[8].

```

#### Parameters:

ulBase is the base address of the ADC module.

ulSequenceNum is the sample sequence number.

ulStep is the step to be configured.

ulConfig is the configuration of this step; must be a logical OR of ADC\_CTL\_TS, ADC\_CTL\_IE, ADC\_CTL\_END, ADC\_CTL\_D, and one of the input channel selects (ADC\_CTL\_CH0 through ADC\_CTL\_CH7).

### **Description:**

This function will set the configuration of the ADC for one step of a sample sequence. The ADC can be configured for single-ended or differential operation (the ADC\_CTL\_D bit selects differential operation when set), the channel to be sampled can be chosen (the ADC\_CTL\_CH0 through ADC\_CTL\_CH7 values), and the internal temperature sensor can be selected (the ADC\_CTL\_TS bit). Additionally, this step can be defined as the last in the sequence (the ADC\_CTL\_END bit) and it can be configured to cause an interrupt when the step is complete (the ADC\_CTL\_IE bit). The configuration is used by the ADC at the appropriate time when the trigger for this sequence occurs.

The *ulStep* parameter determines the order in which the samples are captured by the ADC when the trigger occurs. It can range from zero to seven for the first sample sequence, from zero to three for the second and third sample sequence, and can only be zero for the fourth sample sequence.

Differential mode only works with adjacent channel pairs (e.g. 0 and 1). The channel select must be the number of the channel pair to sample (e.g. **ADC\_CTL\_CH0** for 0 and 1, or **ADC\_CTL\_CH1** for 2 and 3) or undefined results will be returned by the ADC. Additionally, if differential mode is selected when the temperature sensor is being sampled, undefined results will be returned by the ADC.

It is the responsibility of the caller to ensure that a valid configuration is specified; this function does not check the validity of the specified configuration.

#### Returns:

None.

### 3.2.1.14 ROM ADCSequenceUnderflow

Determines if a sample sequence underflow occurred.

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceUnderflow is a function pointer located at ROM_ADCTABLE[11].

```

#### Parameters:

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

### **Description:**

This determines if a sample sequence underflow has occurred. This will happen if too many samples are read from the FIFO.

#### Returns:

Returns zero if there was not an underflow, and non-zero if there was.

### 3.2.1.15 ROM\_ADCSequenceUnderflowClear

Clears the underflow condition on a sample sequence.

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_ADCTABLE is an array of pointers located at ROM_APITABLE[5].

ROM_ADCSequenceUnderflowClear is a function pointer located at ROM_ADCTABLE[12].

```

### Parameters:

```

ulBase is the base address of the ADC module.ulSequenceNum is the sample sequence number.

```

### **Description:**

This will clear an underflow condition on one of the sample sequences. The underflow condition must be cleared in order to detect a subsequent underflow condition (it otherwise causes no harm).

### Returns:

None.

# 4 Flash

| Introduction | <br>. 2 | 2! |

|--------------|---------|----|

| Functions    | <br>. 2 | 2! |

## 4.1 Introduction

The flash API provides a set of functions for dealing with the on-chip flash. Functions are provided to program and erase the flash, configure the flash protection, and handle the flash interrupt.

The flash is organized as a set of 1 kB blocks that can be individually erased. Erasing a block causes the entire contents of the block to be reset to all ones. These blocks are paired into a set of 2 kB blocks that can be individually protected. The blocks can be marked as read-only or execute-only, providing differing levels of code protection. Read-only blocks cannot be erased or programmed, protecting the contents of those blocks from being modified. Execute-only blocks cannot be erased or programmed, and can only be read by the processor instruction fetch mechanism, protecting the contents of those blocks from being read by either the processor or by debuggers.

The flash can be programmed on a word-by-word basis. Programming causes 1 bits to become 0 bits (where appropriate); because of this, a word can be repeatedly programmed so long as each programming operation only requires changing 1 bits to 0 bits.

The timing for the flash is automatically handled by the flash controller. In order to do this, the flash controller must know the clock rate of the system in order to be able to time the number of micro-seconds certain signals are asserted. The number of clock cycles per micro-second must be provided to the flash controller for it to accomplish this timing.

The flash controller has the ability to generate an interrupt when an invalid access is attempted (such as reading from execute-only flash). This can be used to validate the operation of a program; the interrupt will keep invalid accesses from being silently ignored, hiding potential bugs. The flash protection can be applied without being permanently enabled; this, along with the interrupt, allows the program to be debugged before the flash protection is permanently applied to the device (which is a non-reversible operation). An interrupt can also be generated when an erase or programming operation has completed.

# 4.2 Functions

### **Functions**

- long ROM FlashErase (unsigned long ulAddress)

- void ROM\_FlashIntClear (unsigned long ulIntFlags)

- void ROM FlashIntDisable (unsigned long ulIntFlags)

- void ROM\_FlashIntEnable (unsigned long ulIntFlags)

- unsigned long ROM FlashIntStatus (tBoolean bMasked)

- long ROM\_FlashProgram (unsigned long \*pulData, unsigned long ulAddress, unsigned long ulCount)

- tFlashProtection ROM FlashProtectGet (unsigned long ulAddress)

- long ROM FlashProtectSave (void)

- long ROM FlashProtectSet (unsigned long ulAddress, tFlashProtection eProtect)

- unsigned long ROM\_FlashUsecGet (void)

- void ROM\_FlashUsecSet (unsigned long ulClocks)

- long ROM\_FlashUserGet (unsigned long \*pulUser0, unsigned long \*pulUser1)

- long ROM FlashUserSave (void)

- long ROM\_FlashUserSet (unsigned long ulUser0, unsigned long ulUser1)

### 4.2.1 Function Documentation

### 4.2.1.1 ROM FlashErase

Erases a block of flash.

### Prototype:

long

ROM FlashErase (unsigned long ulAddress)

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashErase is a function pointer located at ROM_FLASHTABLE[3].

```

#### Parameters:

ulAddress is the start address of the flash block to be erased.

#### **Description:**

This function will erase a 1 kB block of the on-chip flash. After erasing, the block will be filled with 0xFF bytes. Read-only and execute-only blocks cannot be erased.

This function will not return until the block has been erased.

### Returns:

Returns 0 on success, or -1 if an invalid block address was specified or the block is write-protected.

### 4.2.1.2 ROM FlashIntClear

Clears flash controller interrupt sources.

### Prototype:

```

void

```

ROM\_FlashIntClear(unsigned long ulIntFlags)

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashIntClear is a function pointer located at ROM_FLASHTABLE[13].

```

### Parameters:

**ullntFlags** is the bit mask of the interrupt sources to be cleared. Can be any of the **FLASH\_FCMISC\_PROGRAM** or **FLASH\_FCMISC\_ACCESS** values.

### **Description:**

The specified flash controller interrupt sources are cleared, so that they no longer assert. This must be done in the interrupt handler to keep it from being called again immediately upon exit.

#### Note:

Since there is a write buffer in the Cortex-M3 processor, it may take several clock cycles before the interrupt source is actually cleared. Therefore, it is recommended that the interrupt source be cleared early in the interrupt handler (as opposed to the very last action) to avoid returning from the interrupt handler before the interrupt source is actually cleared. Failure to do so may result in the interrupt handler being immediately reentered (since NVIC still sees the interrupt source asserted).

#### Returns:

None.

### 4.2.1.3 ROM FlashIntDisable

Disables individual flash controller interrupt sources.

### Prototype:

```

void

ROM_FlashIntDisable(unsigned long ulIntFlags)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashIntDisable is a function pointer located at ROM_FLASHTABLE[11].

```

#### Parameters:

ullntFlags is a bit mask of the interrupt sources to be disabled. Can be any of the FLASH FCIM PROGRAM or FLASH FCIM ACCESS values.

### Description:

Disables the indicated flash controller interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

#### Returns:

None.

### 4.2.1.4 ROM FlashIntEnable

Enables individual flash controller interrupt sources.

### Prototype:

void

ROM\_FlashIntEnable(unsigned long ulIntFlags)

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE [7].

ROM_FlashIntEnable is a function pointer located at ROM_FLASHTABLE [10].

```

### Parameters:

ulIntFlags is a bit mask of the interrupt sources to be enabled. Can be any of the FLASH FCIM PROGRAM or FLASH FCIM ACCESS values.

### **Description:**

Enables the indicated flash controller interrupt sources. Only the sources that are enabled can be reflected to the processor interrupt; disabled sources have no effect on the processor.

#### Returns:

None.

### 4.2.1.5 ROM FlashIntStatus

Gets the current interrupt status.

### Prototype:

```

unsigned long

ROM_FlashIntStatus(tBoolean bMasked)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashIntStatus is a function pointer located at ROM_FLASHTABLE[12].

```

### Parameters:

**bMasked** is false if the raw interrupt status is required and true if the masked interrupt status is required.

#### **Description:**

This returns the interrupt status for the flash controller. Either the raw interrupt status or the status of interrupts that are allowed to reflect to the processor can be returned.

#### Returns:

The current interrupt status, enumerated as a bit field of FLASH\_FCMISC\_PROGRAM and FLASH\_FCMISC\_ACCESS.

### 4.2.1.6 ROM FlashProgram

Programs flash.

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashProgram is a function pointer located at ROM_FLASHTABLE[0].

```

#### Parameters:

*pulData* is a pointer to the data to be programmed.

ulAddress is the starting address in flash to be programmed. Must be a multiple of four.

*ulCount* is the number of bytes to be programmed. Must be a multiple of four.

### **Description:**

This function will program a sequence of words into the on-chip flash. Programming each location consists of the result of an AND operation of the new data and the existing data; in other words bits that contain 1 can remain 1 or be changed to 0, but bits that are 0 cannot be changed to 1. Therefore, a word can be programmed multiple times as long as these rules are followed; if a program operation attempts to change a 0 bit to a 1 bit, that bit will not have its value changed.

Since the flash is programmed one word at a time, the starting address and byte count must both be multiples of four. It is up to the caller to verify the programmed contents, if such verification is required.

This function will not return until the data has been programmed.

#### Returns:

Returns 0 on success, or -1 if a programming error is encountered.

### 4.2.1.7 ROM FlashProtectGet

Gets the protection setting for a block of flash.

### Prototype:

```

tFlashProtection

ROM_FlashProtectGet(unsigned long ulAddress)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashProtectGet is a function pointer located at ROM_FLASHTABLE[4].

```

### Parameters:

*ulAddress* is the start address of the flash block to be queried.

### **Description:**

This function will get the current protection for the specified 2 kB block of flash. Each block can be read/write, read-only, or execute-only. Read/write blocks can be read, executed, erased, and programmed. Read-only blocks can be read and executed. Execute-only blocks can only be executed; processor and debugger data reads are not allowed.

#### Returns:

Returns the protection setting for this block. See ROM\_FlashProtectSet() for possible values.

### 4.2.1.8 ROM FlashProtectSave

Saves the flash protection settings.

### Prototype:

long

ROM FlashProtectSave (void)

### **ROM Location:**

ROM\_APITABLE is an array of pointers located at 0x0100.0010.

ROM\_FLASHTABLE is an array of pointers located at ROM\_APITABLE[7].

ROM\_FlashProtectSave is a function pointer located at ROM\_FLASHTABLE[6].

### **Description:**

This function will make the currently programmed flash protection settings permanent. This is a non-reversible operation; a chip reset or power cycle will not change the flash protection.

This function will not return until the protection has been saved.

#### Returns:

Returns 0 on success, or -1 if a hardware error is encountered.

### 4.2.1.9 ROM FlashProtectSet

Sets the protection setting for a block of flash.

### Prototype:

#### **ROM Location:**

ROM\_APITABLE is an array of pointers located at  $0 \times 0100.0010$ . ROM\_FLASHTABLE is an array of pointers located at ROM\_APITABLE[7]. ROM\_FlashProtectSet is a function pointer located at ROM\_FLASHTABLE[5].

### Parameters:

**ulAddress** is the start address of the flash block to be protected.

**eProtect** is the protection to be applied to the block. Can be one of **FlashReadWrite**, **FlashReadOnly**, or **FlashExecuteOnly**.

### **Description:**

This function will set the protection for the specified 2 kB block of flash. Blocks which are read/write can be made read-only or execute-only. Blocks which are read-only can be made execute-only. Blocks which are execute-only cannot have their protection modified. Attempts to make the block protection less stringent (i.e. read-only to read/write) will result in a failure (and be prevented by the hardware).

Changes to the flash protection are maintained only until the next reset. This allows the application to be executed in the desired flash protection environment to check for inappropriate flash access (via the flash interrupt). To make the flash protection permanent, use the ROM\_FlashProtectSave() function.

#### Returns:

Returns 0 on success, or -1 if an invalid address or an invalid protection was specified.

### 4.2.1.10 ROM FlashUsecGet

Gets the number of processor clocks per micro-second.

### Prototype:

```

unsigned long

ROM_FlashUsecGet(void)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashUsecGet is a function pointer located at ROM_FLASHTABLE[1].

```

### **Description:**

This function returns the number of clocks per micro-second, as presently known by the flash controller.

#### Returns:

Returns the number of processor clocks per micro-second.

### 4.2.1.11 ROM FlashUsecSet

Sets the number of processor clocks per micro-second.

### Prototype:

```

void

ROM_FlashUsecSet(unsigned long ulClocks)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashUsecSet is a function pointer located at ROM_FLASHTABLE[2].

```

#### Parameters:

ulClocks is the number of processor clocks per micro-second.

### **Description:**

This function is used to tell the flash controller the number of processor clocks per microsecond. This value must be programmed correctly or the flash most likely will not program correctly; it has no affect on reading flash.

### Returns:

None.

### 4.2.1.12 ROM\_FlashUserGet

Gets the User Registers

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashUserGet is a function pointer located at ROM_FLASHTABLE[7].

```

### Parameters:

pulUser0 is a pointer to the location to store USER Register 0.pulUser1 is a pointer to the location to store USER Register 1.

### **Description:**

This function will read the contents of User Registers (0 and 1), and store them in the specified locations.

#### Returns:

Returns 0 on success, or -1 if a hardware error is encountered.

### 4.2.1.13 ROM FlashUserSave

Saves the User Registers

### Prototype:

```

long

ROM_FlashUserSave(void)

```

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashUserSave is a function pointer located at ROM_FLASHTABLE[9].

```

### **Description:**

This function will make the currently programmed User register settings permanent. This is a non-reversible operation; a chip reset or power cycle will not change this setting.

This function will not return until the protection has been saved.

#### Returns:

Returns 0 on success, or -1 if a hardware error is encountered.

### 4.2.1.14 ROM FlashUserSet

Sets the User Registers

### Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_FLASHTABLE is an array of pointers located at ROM_APITABLE[7].

ROM_FlashUserSet is a function pointer located at ROM_FLASHTABLE[8].

```

### Parameters:

ulUser0 is the value to store in USER Register 0.ulUser1 is the value to store in USER Register 1.

### **Description:**

This function will set the contents of the User Registers (0 and 1) to the specified values.

### Returns:

Returns 0 on success, or -1 if a hardware error is encountered.

# 5 GPIO

| Introduction | n | <br> | <br>٠. | ٠. | <br> | <br> | ٠. | ٠. | ٠. | <br> | <br> | <br> | <br> | <br> | <br> | <br>٠. | ٠. | 3 | 5 |

|--------------|---|------|------|------|------|------|------|------|------|------|--------|----|------|------|----|----|----|------|------|------|------|------|------|--------|----|---|---|

| Functions    |   | <br>   |    | <br> | <br> |    |    |    | <br>   |    | 3 | 5 |

## 5.1 Introduction

The GPIO module provides control for up to eight independent GPIO pins (the actual number present depend upon the GPIO port and part number). Each pin has the following capabilities:

- Can be configured as an input or an output. On reset, they default to being an input.

- In input mode, can generate interrupts on high level, low level, rising edge, falling edge, or both edges.

- In output mode, can be configured for 2 mA, 4 mA, or 8 mA drive strength. The 8 mA drive strength configuration has optional slew rate control to limit the rise and fall times of the signal. On reset, they default to 2 mA drive strength.

- Optional weak pull-up or pull-down resistors. On reset, they default to no pull-up or pull-down resistors.

- Optional open-drain operation. On reset, they default to standard push/pull operation.

- Can be configured to be a GPIO or a peripheral pin. On reset, they default to being GPIOs. Note that not all pins on all parts have peripheral functions, in which case the pin is only useful as a GPIO (that is, when configured for peripheral function the pin will not do anything useful).

Most of the GPIO functions can operate on more than one GPIO pin (within a single module) at a time. The *ucPins* parameter to these functions is used to specify the pins that are affected; the GPIO pins whose corresponding bits in this parameter that are set will be affected (where pin 0 is in bit 0, pin 1 in bit 1, and so on). For example, if *ucPins* is 0x09, then pins 0 and 3 will be affected by the function.

This is most useful for the ROM\_GPIOPinRead() and ROM\_GPIOPinWrite() functions; a read will return only the value of the requested pins (with the other pin values masked out) and a write will affect the requested pins simultaneously (that is, the state of multiple GPIO pins can be changed at the same time). This data masking for the GPIO pin state occurs in the hardware; a single read or write is issued to the hardware, which interprets some of the address bits as an indication of the GPIO pins to operate upon (and therefore the ones to not affect). See the part data sheet for details of the GPIO data register address-based bit masking.

For functions that have a *ucPin* (singular) parameter, only a single pin is affected by the function. In this case, this value specifies the pin number (that is, 0 through 7).

# 5.2 Functions

### **Functions**

- unsigned long ROM GPIODirModeGet (unsigned long ulPort, unsigned char ucPin)

- void ROM\_GPIODirModeSet (unsigned long ulPort, unsigned char ucPins, unsigned long ulPinIO)

- unsigned long ROM\_GPIOIntTypeGet (unsigned long ulPort, unsigned char ucPin)

- void ROM\_GPIOIntTypeSet (unsigned long ulPort, unsigned char ucPins, unsigned long ulInt-Type)

- void ROM\_GPIOPadConfigGet (unsigned long ulPort, unsigned char ucPin, unsigned long \*pulStrength, unsigned long \*pulPinType)

- void ROM\_GPIOPadConfigSet (unsigned long ulPort, unsigned char ucPins, unsigned long ulStrength, unsigned long ulPinType)

- void ROM GPIOPinIntClear (unsigned long ulPort, unsigned char ucPins)

- void ROM GPIOPinIntDisable (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinIntEnable (unsigned long ulPort, unsigned char ucPins)

- long ROM GPIOPinIntStatus (unsigned long ulPort, tBoolean bMasked)

- long ROM\_GPIOPinRead (unsigned long ulPort, unsigned char ucPins)

- void ROM GPIOPinTypeGPIOInput (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinTypeGPIOOutput (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinTypeGPIOOutputOD (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinTypeI2C (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinTypePWM (unsigned long ulPort, unsigned char ucPins)

- void ROM GPIOPinTypeSSI (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinTypeTimer (unsigned long ulPort, unsigned char ucPins)

- void ROM GPIOPinTypeUART (unsigned long ulPort, unsigned char ucPins)

- void ROM\_GPIOPinWrite (unsigned long ulPort, unsigned char ucPins, unsigned char ucVal)

### 5.2.1 Function Documentation

### 5.2.1.1 ROM GPIODirModeGet

Gets the direction and mode of a pin.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIODirModeGet is a function pointer located at ROM_GPIOTABLE[2].

```

#### Parameters:

ulPort is the base address of the GPIO port.ucPin is the pin number.

### **Description:**

This function gets the direction and control mode for a specified pin on the selected GPIO port. The pin can be configured as either an input or output under software control, or it can be under hardware control. The type of control and direction are returned as an enumerated data type.

### Returns:

Returns one of the enumerated data types described for ROM\_GPIODirModeSet().

# 5.2.1.2 ROM GPIODirModeSet

Sets the direction and mode of the specified pin(s).

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIODirModeSet is a function pointer located at ROM_GPIOTABLE[1].

```

#### Parameters:

```

ulPort is the base address of the GPIO portucPins is the bit-packed representation of the pin(s).ulPinIO is the pin direction and/or mode.

```

### **Description:**

This function will set the specified pin(s) on the selected GPIO port as either an input or output under software control, or it will set the pin to be under hardware control.

The *ulPinIO* parameter is an enumerated data type that can be one of the following values:

- GPIO\_DIR\_MODE\_IN

- GPIO\_DIR\_MODE\_OUT

- GPIO DIR MODE HW

where **GPIO\_DIR\_MODE\_IN** specifies that the pin will be programmed as a software controlled input, **GPIO\_DIR\_MODE\_OUT** specifies that the pin will be programmed as a software controlled output, and **GPIO\_DIR\_MODE\_HW** specifies that the pin will be placed under hardware control.

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

#### Returns:

None.

# 5.2.1.3 ROM GPIOIntTypeGet

Gets the interrupt type for a pin.

## Prototype:

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOIntTypeGet is a function pointer located at ROM_GPIOTABLE[4].

```

#### Parameters:

ulPort is the base address of the GPIO port.ucPin is the pin number.

# **Description:**

This function gets the interrupt type for a specified pin on the selected GPIO port. The pin can be configured as a falling edge, rising edge, or both edge detected interrupt, or it can be configured as a low level or high level detected interrupt. The type of interrupt detection mechanism is returned as an enumerated data type.

#### Returns:

Returns one of the enumerated data types described for ROM\_GPIOIntTypeSet().

# 5.2.1.4 ROM\_GPIOIntTypeSet

Sets the interrupt type for the specified pin(s).

# Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOIntTypeSet is a function pointer located at ROM_GPIOTABLE[3].

```

# Parameters:

```

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).ulIntType specifies the type of interrupt trigger mechanism.

```

# **Description:**

This function sets up the various interrupt trigger mechanisms for the specified pin(s) on the selected GPIO port.

The *ulIntType* parameter is an enumerated data type that can be one of the following values:

- **GPIO FALLING EDGE**

- GPIO\_RISING\_EDGE

- GPIO BOTH EDGES

- GPIO\_LOW\_LEVEL

- **GPIO HIGH LEVEL**

where the different values describe the interrupt detection mechanism (edge or level) and the particular triggering event (falling, rising, or both edges for edge detect, low or high for level detect).

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

#### Note:

In order to avoid any spurious interrupts, the user must ensure that the GPIO inputs remain stable for the duration of this function.

#### Returns:

None.

# 5.2.1.5 ROM\_GPIOPadConfigGet

Gets the pad configuration for a pin.

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPadConfigGet is a function pointer located at ROM_GPIOTABLE[6].

```

### Parameters:

```

ulPort is the base address of the GPIO port.

ucPin is the pin number.

pulStrength is a pointer to storage for the output drive strength.

pulPinType is a pointer to storage for the output drive type.

```

#### **Description:**

This function gets the pad configuration for a specified pin on the selected GPIO port. The values returned in *eStrength* and *eOutType* correspond to the values used in ROM\_GPIOPadConfigSet(). This function also works for pin(s) configured as input pin(s); however, the only meaningful data returned is whether the pin is terminated with a pull-up or down resistor.

#### Returns:

None

# 5.2.1.6 ROM\_GPIOPadConfigSet

Sets the pad configuration for the specified pin(s).

#### Prototype:

```

void

ROM_GPIOPadConfigSet(unsigned long ulPort,

```

unsigned char ucPins,

unsigned long ulStrength,

unsigned long ulPinType)

#### **ROM Location:**

ROM\_APITABLE is an array of pointers located at 0x0100.0010.

ROM\_GPIOTABLE is an array of pointers located at ROM\_APITABLE[4].

ROM\_GPIOPadConfigSet is a function pointer located at ROM\_GPIOTABLE[5].

#### Parameters:

ulPort is the base address of the GPIO port.

ucPins is the bit-packed representation of the pin(s).

ulStrength specifies the output drive strength.

ulPinType specifies the pin type.

### **Description:**

This function sets the drive strength and type for the specified pin(s) on the selected GPIO port. For pin(s) configured as input ports, the pad is configured as requested, but the only real effect on the input is the configuration of the pull-up or pull-down termination.

The *ulStrength* parameter can be one of the following values:

- GPIO STRENGTH 2MA

- **GPIO STRENGTH 4MA**

- GPIO\_STRENGTH\_8MA

- GPIO\_STRENGTH\_8MA\_SC

where **GPIO\_STRENGTH\_xMA** specifies either 2, 4, or 8 mA output drive strength, and **GPIO\_OUT\_STRENGTH\_8MA\_SC** specifies 8 mA output drive with slew control.

The *ulPinType* parameter can be one of the following values:

- **GPIO PIN TYPE STD**

- GPIO\_PIN\_TYPE STD WPU

- GPIO\_PIN\_TYPE\_STD\_WPD

- GPIO\_PIN\_TYPE\_OD

- GPIO PIN TYPE OD WPU

- GPIO\_PIN\_TYPE\_OD\_WPD

- **GPIO PIN TYPE ANALOG**

where **GPIO\_PIN\_TYPE\_STD**\* specifies a push-pull pin, **GPIO\_PIN\_TYPE\_OD**\* specifies an open-drain pin, \*\_**WPU** specifies a weak pull-up, \*\_**WPD** specifies a weak pull-down, and **GPIO\_PIN\_TYPE\_ANALOG** specifies an analog input.

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

#### Returns:

None.

# 5.2.1.7 ROM GPIOPinIntClear

Clears the interrupt for the specified pin(s).

## Prototype:

# **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinIntClear is a function pointer located at ROM_GPIOTABLE[10].

```

### Parameters:

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).

# Description:

Clears the interrupt for the specified pin(s).

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

#### Note:

Since there is a write buffer in the Cortex-M3 processor, it may take several clock cycles before the interrupt source is actually cleared. Therefore, it is recommended that the interrupt source be cleared early in the interrupt handler (as opposed to the very last action) to avoid returning from the interrupt handler before the interrupt source is actually cleared. Failure to do so may result in the interrupt handler being immediately reentered (since NVIC still sees the interrupt source asserted).

#### Returns:

None.

# 5.2.1.8 ROM GPIOPinIntDisable

Disables interrupts for the specified pin(s).

# Prototype:

# **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinIntDisable is a function pointer located at ROM_GPIOTABLE[8].

```

#### Parameters:

```

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).

```

# **Description:**

Masks the interrupt for the specified pin(s).

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

#### Returns:

None.

# 5.2.1.9 ROM GPIOPinIntEnable

Enables interrupts for the specified pin(s).

# Prototype:

### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0 \times 0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinIntEnable is a function pointer located at ROM_GPIOTABLE[7].

```

#### Parameters:

```

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).

```

# **Description:**

Unmasks the interrupt for the specified pin(s).

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

### Returns:

None.

# 5.2.1.10 ROM GPIOPinIntStatus

Gets interrupt status for the specified GPIO port.

## Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinIntStatus is a function pointer located at ROM_GPIOTABLE[9].

```

#### Parameters:

ulPort is the base address of the GPIO port.

**bMasked** specifies whether masked or raw interrupt status is returned.

#### **Description:**

If *bMasked* is set as **true**, then the masked interrupt status is returned; otherwise, the raw interrupt status will be returned.

#### Returns:

Returns a bit-packed byte, where each bit that is set identifies an active masked or raw interrupt, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc. Bits 31:8 should be ignored.

# 5.2.1.11 ROM GPIOPinRead

Reads the values present of the specified pin(s).

### Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinRead is a function pointer located at ROM_GPIOTABLE[11].

```

#### **Parameters:**

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).

# Description:

The values at the specified pin(s) are read, as specified by *ucPins*. Values are returned for both input and output pin(s), and the value for pin(s) that are not specified by *ucPins* are set to 0.

The pin(s) are specified using a bit-packed byte, where each bit that is set identifies the pin to be accessed, and where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc.

### Returns:

Returns a bit-packed byte providing the state of the specified pin, where bit 0 of the byte represents GPIO port pin 0, bit 1 represents GPIO port pin 1, etc. Any bit that is not specified by *ucPins* is returned as a 0. Bits 31:8 should be ignored.

# 5.2.1.12 ROM\_GPIOPinTypeGPIOInput

Configures pin(s) for use as GPIO inputs.

# Prototype:

#### **ROM Location:**

```

ROM_APITABLE is an array of pointers located at 0x0100.0010.

ROM_GPIOTABLE is an array of pointers located at ROM_APITABLE[4].

ROM_GPIOPinTypeGPIOInput is a function pointer located at ROM_GPIOTABLE[14].

```

#### Parameters:

ulPort is the base address of the GPIO port.ucPins is the bit-packed representation of the pin(s).

# **Description:**