# Hercules Family Frequency Slewing to Reduce Voltage and Current Transients

Kevin Lavery

## ABSTRACT

This application report describes a method to dynamically increase device frequency in a way that minimizes voltage dips on the board power supply. The PLL's multiplier can be stepped in 8% steps every 50 reference clocks.

| Contents |

|----------|

|----------|

| 1 | Overview of Slewing Considerations               | 1 |

|---|--------------------------------------------------|---|

| 2 | System Considerations Affecting the Power Supply | 2 |

|   | Procedure for Changing Frequency                 |   |

|   | Examples                                         |   |

|   | References                                       |   |

| - |                                                  |   |

#### List of Figures

| 1 | PLL Block Diagram                               | 1 |

|---|-------------------------------------------------|---|

|   | PLL CLK Frequency Step With a Multiplier Change |   |

#### List of Tables

| 1 | Procedure for Changing Frequency                                                | 3 |

|---|---------------------------------------------------------------------------------|---|

| 2 | 16 MHz crystal, 180 MHz GCLK and HCLK, 90 MHz VCLK (TMS570LSxx and TMS570RM4xx) | 5 |

#### 1 Overview of Slewing Considerations

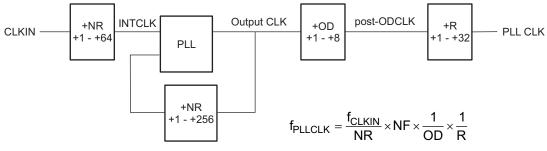

The Hercules<sup>™</sup> family of devices has a phase-locked loop (PLL) for synthesizing device frequencies. The simplified block diagram of the PLL is shown in Figure 1.

Figure 1. PLL Block Diagram

Hercules is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

1

System Considerations Affecting the Power Supply

www.ti.com

The oscillator provides CLKIN to the PLL. It is divided by NR before multiplication by NF. After the PLL frequency synthesis, there are two cascaded dividers that allow the PLL CLK frequency to be reduced *digitally*. For more detailed information on the PLL operation, see the *Oscillator and PLL* section of the *TMS570LS31x/21x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual* (SPNU499). As discussed in the TRM and the device-specific data sheet, the PLL has frequency limits on *INTCLK*, *Output CLK*, and *post-OD CLK*. Obviously, the device maximum frequency governs the upper end of the PLL CLK range. For these limits, see the device-specific TRM and data sheet.

The PLL CLK frequency can be changed through the OD-divider and R-divider in order to implement digital steps to the frequency. Additionally, this PLL is capable of re-locking on-the-fly without generating a slip signal if:

- The step size is small enough

- The update rate for the stepping is slow enough

The on-the-fly change to the multiplier (NF) produces a smaller frequency-step than can be achieved with the digital divider; the on-the-fly multiplier change results in a more gradual frequency (and current) increase that is easier for an external regulator to supply.

This document is intended to define the pattern of steps that can be used to smooth the current steps for an external voltage regulator.

From an application perspective, a smooth increase in frequency (no large digital steps) reduces the current jumps to which the power supply circuitry must respond. If the PLL frequency is stepped on-the-fly in order to reduce the current transients seen by the power control circuitry, the stepping of the PLL must be slow compared to the rate of change of the power control circuitry.

This application report recommends a PLL maximum step size for the multiply factor of 8%.

The PLL requires time to lock to the new value before an additional step can occur. This settling time is defined in terms of INTCLK cycles:  $f_{INTCLK} = \frac{f_{CLKIN}}{NR} (and T_{INTCLK} = NR \times T_{OSCIN})$ . The required settling time

defined in terms of INTCLK cycles: *NR* (*and NNCLK NR* (*and NNCLK interview*). The required settling time for a small perturbation to the PLL multiplier is 50 INTCLK periods (reference periods).

# 2 System Considerations Affecting the Power Supply

Although the PLL stabilizes within 50 reference cycles, the PLL's rate of change must be slower than the response of the board-level power supply system. That is, the response of the board-level voltage regulator must be known in order to choose an update rate.

For switching regulators, the first limitation on the update rate is the external stabilization circuitry. If the regulator requires a 10  $\mu$ H inductor and 10  $\mu$ F capacitor to filter the switching voltage, then the breakpoint

of the filter occurs at  ${}^{f_B = \frac{1}{2\pi\sqrt{LC}}}$ , which in this example falls at 16 kHz. If the DC operating point changes faster than 16 kHz (62.5 µs), the filter output shows an accumulating voltage droop. In order to minimize this droop, small frequency steps are programmed with a sufficient delay for the DC operating point to be re-established prior to the next step. Frequency steps smaller than 8% make each current/voltage step response smaller.

The frequency jump due to a fixed percentage step is much bigger when the PLL is at the top end of its range than when it is at the first frequency step of the ramp. Said another way, adding a constant percentage to the divider produces an exponential increase in frequency and current. If this exponential ramp is not acceptable, add a constant value (starting from the initial 8% step) and generate a linear ramp.

# 3 **Procedure for Changing Frequency**

The procedure for slewing the device to its final frequency depends upon whether the final PLL CLK frequency exceeds 250 MHz. If the final PLL CLK frequency exceeds 250 MHz, then the *PLL* should be used with all output dividers equal to 1. If the final PLL CLK frequency is less than 250 MHz, the final divider may be maintained as 2. The procedure is as shown in Table 1.

2

www.ti.com

Texas

STRUMENTS

| PLL CLK < 250 MHz                                                                                                                                                                                                                                                 | PLLCLK ≥ 250 MHz                                                                                                                                                                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1) Determine maximal frequency step [ $\Delta f_{max}$ in terms of MHz];<br>this step is seen when the PLL changes its R-divider from /3 to<br>/2. The maximal step determines the initial Output CLK<br>frequency.                                               | 1) Determine maximal frequency step [ $\Delta f_{max}$ in terms of MHz]; this step is seen when the PLL changes its R-divider from /2 to /1. The maximal step determines the initial Output CLK frequency (typically close to VCO <i>min</i> ). |  |  |

| $\Delta f_{\max} = \frac{(f_{VCO})_{init}}{2} - \frac{(f_{VCO})_{init}}{3}$                                                                                                                                                                                       | $\Delta f_{\text{max}} = \frac{(f_{VCO})_{init}}{1} - \frac{(f_{VCO})_{init}}{2}$                                                                                                                                                               |  |  |

| $(f_{VCO})_{init} = 6 \times \Delta f_{max}$                                                                                                                                                                                                                      | $(f_{VCO})_{init} = 2 \times \Delta f_{max}$                                                                                                                                                                                                    |  |  |

| Note:                                                                                                                                                                                                                                                             | Note:                                                                                                                                                                                                                                           |  |  |

| The initial Output CLK frequency must be greater than the minimum VCO frequency. This constraint effectively ties the maximal frequency step to the minimum VCO frequency.                                                                                        | The initial Output CLK frequency must be greater than the minimum VCO frequency. This constraint effectively ties the maximal frequency step to the minimum VCO frequency.                                                                      |  |  |

| Increase PLL CLK frequency through R-divider changes $(/6 \rightarrow /3 \rightarrow /2)$                                                                                                                                                                         | Increase PLL CLK frequency through R-divider changes $(/6 \rightarrow /2 \rightarrow /1)$                                                                                                                                                       |  |  |

| 2) Set the initial PLL CLK frequency as a frequency step above the set to /6. The initial frequency step from the crystal to the first PLI                                                                                                                        |                                                                                                                                                                                                                                                 |  |  |

| Lock the PLL to this divided initial Output CLK frequency. When t output.                                                                                                                                                                                         | he PLL is valid, enable the GCLK and HCLK to run on the PLL                                                                                                                                                                                     |  |  |

| 3) Delay changing the frequency based upon the response time of the power supply. The Dual Clock Comparator (DCC) can be used to count oscillator cycles in order to set this delay                                                                               |                                                                                                                                                                                                                                                 |  |  |

| <b>Note:</b> When the DCC is configured to count oscillator cycles, the Therefore, a 50 µs delay is achieved with a 20 MHz crystal by co the DCC operation, see the <i>Dual-Clock Comparator (DCC) Modu Microcontroller Technical Reference Manual</i> (SPNU499). | unting = 1250 oscillator cycles. For more detailed information on                                                                                                                                                                               |  |  |

| 4) Set the next PLL CLK frequency as a frequency step above the initial frequency; maintain OD-divider at /1 and set the R-divider to /3 $^{(1)}$ . There is no change to the PLL loop so immediately begin the delay.                                            | 4) Set the next PLL CLK frequency as a frequency step above<br>the initial frequency; maintain OD-divider at /1 and set the R-<br>divider to /2 <sup>(1)</sup> There is no change to the PLL loop so<br>immediately begin the delay.            |  |  |

| 5) Delay changing the frequency based upon the response time of cycles in order to set this delay                                                                                                                                                                 | f the power supply. The DCC can be used to count oscillator                                                                                                                                                                                     |  |  |

| 6) Set the next PLL CLK frequency as a frequency step above<br>the previous frequency; maintain the OD-divider at /1 and step<br>the R-divider to /2. There is no change to the PLL loop so<br>immediately begin the delay.                                       | 6) Set the next PLL CLK frequency as a frequency step above<br>the previous frequency; maintain the OD-divider at /1 and step<br>the R-divider to /1. There is no change to the PLL loop so<br>immediately begin the delay.                     |  |  |

| 7) Delay changing the frequency based upon the response time of cycles in order to set this delay                                                                                                                                                                 | f the power supply. The DCC can be used to count oscillator                                                                                                                                                                                     |  |  |

| Increase Output CLK frequency through multiplier changes (maxi                                                                                                                                                                                                    | mum change is NF + 8%)                                                                                                                                                                                                                          |  |  |

Increase Output CLK frequency through multiplier changes (maximum change is NF + 8%)

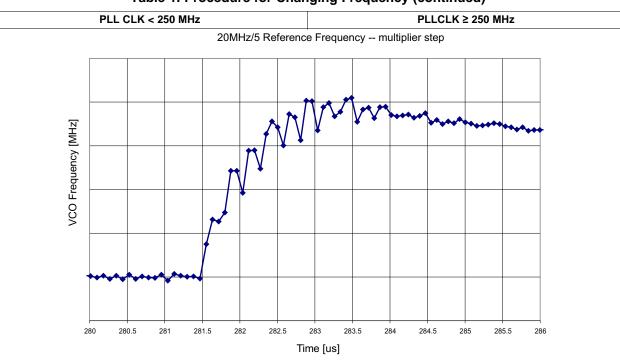

8) Increase the NF multiplier by no more than 8%. The PLL loop is changed, locking to the new Output CLK frequency following a response similar to what is shown in Figure 2.

<sup>&</sup>lt;sup>(1)</sup> This procedure assumes that the ramp should be carried out in as few steps as possible (with appropriate delays between each step). If the regulator can supply a consistent jump of ΔI, then it makes sense to step in the largest divider steps possible (for example, /6 → /3 → /2 or /6 → /2 → /1). However, regulators are sensitive to not only ΔI but also ΔI/I (or the step as a fraction of the current bias point). Therefore, choose the largest jump that does not violate ΔI at the current bias condition.

www.ti.com

#### Table 1. Procedure for Changing Frequency (continued)

9) Delay changing the frequency *based upon the response time of the power supply*; because these frequency and current steps are typically smaller than the digital stepping, the delay might be reduced based upon the response of the *power supply*. The DCC can be used to count oscillator cycles in order to set this delay.

Continue to increase the frequency by increasing the multiplier and then waiting for the power supply to settle (steps 8 and 9). The frequency ramp can be exponential (by continuing to increase the multiplier NF by a fixed *percentage*) or linear (by continuing to increase the multiplier NF by a fixed *amount*).

NOTE: The PLL parameters must continue to be obeyed. That is:

- The Output CLK frequency cannot exceed VCO<sub>max</sub>

- The PLL multiplier cannot exceed the maximum multiplier

- The post-ODCLK frequency cannot exceed the maximum post-ODCLK frequency

- **NOTE:** When changing the PLL multiplier (NF), the change must be the smaller of {8%,  $\Delta f_{max}$ }. For an exponential frequency ramp, it is likely that the last steps will be governed by limiting  $\Delta f_{max}$  rather than maintaining a fixed percentage increase in the multiplier.

Copyright © 2012, Texas Instruments Incorporated

#### www.ti.com

## 4 Examples

Examples assume that the regulator can step 150 mA with a 100 µs recovery time for a digital step and 40 µs recovery from a smaller (analog) step. These delay times should be verified against the particular regulator topology used in the final system. Estimate is active (dynamic) current.

# 4.1 16 MHz crystal, 180 MHz GCLK and HCLK, 90 MHz VCLK (TMS570LSxx and TMS570RM4xx)

| Table 2. 16 MHz crystal | 180 MHz GCLK and HCLK, | 90 MHz VCLK (TMS570LSxx and |  |

|-------------------------|------------------------|-----------------------------|--|

| TMS570RM4xx)            |                        |                             |  |

| Frequency [MHz] | Current [mA] | Current Step<br>[mA and %] | Configuration          | Delay [µs] |

|-----------------|--------------|----------------------------|------------------------|------------|

| 16              | 41.2         |                            | Crystal                |            |

| 60              | 91.3         | 50.1 and 121.5%            | 16/ 4 * 90/(1*6) = 60  | 100        |

| 120             | 159.5        | 68.3 and 74.8%             | 16/ 4 * 90/(1*3) = 120 | 100        |

| 180             | 227.8        | 68.3 and 42.8%             | 16/ 4 * 90/(1*2) = 180 | 100        |

# 5 References

• TMS570LS31x/21x 16/32-Bit RISC Flash Microcontroller Technical Reference Manual (SPNU499)

5

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated