# TMS470R1x Expansion Bus Multiplexer Module (EBM) Reference Guide

SPNU222C

August 2009

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and application s using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different form or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding an applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |

|--------------------|------------------------|--------------------|---------------------------|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |

| Low Power Wireless | wwwti.com/lpw          | Telephony          | www.ti.com/telephony      |

|                    |                        | Video & Imaging    | www.ti.com/video          |

|                    |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments Post Office Box 655303 Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated

### **REVISION HISTORY**

| REVISION | DATE    | NOTES                                                                                                                                                        |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С        | 8/09    | Corrected description for the EBADDR bits in the EBM Address Control Register 3.                                                                             |

| В        | 11/04   | Added overview diagram.<br>Updated register names/information,<br>Added individual register information for all regis-<br>ters.<br>Added example, section 5. |

| А        | 10/2002 | Converted to a standalone book.<br>Page 6, EBMXCRx bit description corrected.                                                                                |

| *        | 7/2002  | Initial Version                                                                                                                                              |

# Contents

| 1 | Overv | iew                                                 | 2  |

|---|-------|-----------------------------------------------------|----|

| 2 |       | iption                                              |    |

| _ | 2.1   | EBM Signals                                         |    |

| 3 | EBM F | Register Overview                                   |    |

|   |       | Register Detailed Description                       |    |

|   | 4.1   | EBM Request Control Register (EBDMACR)              |    |

|   | 4.2   | EBM Read/Write Control Register (EBRWCR)            | 8  |

|   | 4.3   | EBM Address Control Register 1 (EBACR1)             | 9  |

|   | 4.4   | EBM Data Control Register (EBDCR) 1                 | 10 |

|   | 4.5   | EBM Address/Data Control Register (EBADCR) 1        | 11 |

|   | 4.6   | EBM Address Control Register 2 (EBACR2)             |    |

|   | 4.7   | EBM Address Control Register 3 (EBACR3) 1           |    |

|   | 4.8   | EBM Control Register 1 (EBMCR1)                     |    |

| 5 | Exam  | ole for Interfacing 64k of External 16-Bit Memory 1 |    |

# Figures

| 1  | EBM Overview                               | 3  |

|----|--------------------------------------------|----|

| 2  | EBM Register Summary                       | 6  |

| 3  | EBM Request Control Register (EBDMACR)     | 7  |

| 4  | EBM Read/Write Control Register (EBRWCR)   | 8  |

| 5  | EBM Address Control Register 1 (EBACR1)    | 9  |

| 6  | EBM Data Control Register (EBDCR)          | 10 |

| 7  | EBM Address/Data Control Register (EBADCR) | 11 |

| 8  | EBM Address Control Register 2 (EBACR2)    | 12 |

| 9  | EBM Address Control Register 3 (EBACR3)    | 13 |

| 10 | EBM Control Register 1 (EBMCR1)            | 14 |

# **Tables**

| 1  | EBM Pin Description                                           | . 4 |

|----|---------------------------------------------------------------|-----|

| 2  | EBM Internal Registers                                        | . 5 |

| 3  | EBM Request Control Register (EBDMACR) Field Descriptions     | . 7 |

| 4  | EBM Read/Write Control Register (EBRWCR) Field Descriptions.  | . 8 |

| 5  | EBM Address Control Register 1 (EBACR1) Field Descriptions    | . 9 |

| 6  | EBM Data Control Register (EBDCR) Field Descriptions          | 10  |

| 7  | EBM Address/Data Control Register (EBADCR) Field Descriptions | 11  |

| 8  | EBM Address Control Register 2 (EBACR2) Field Descriptions    | 12  |

| 9  | EBM Address Control Register 3 (EBACR3) Field Descriptions    | 13  |

| 10 | EBM Control Register 1 (EBMCR1) Bit Descriptions              | 14  |

|    |                                                               |     |

# **Expansion Bus Multiplexer Module (EBM)**

The expansion bus multiplexer module (EBM) is a stand-alone module providing bond out for both general purpose input/output pins and expansion bus interface pins for the Texas Instruments (TI) TMS470 microcontroller family. The module supports the multiplexing of the input/output (I/O) functions and the expansion bus interface. When the I/O functions are not used, the EBM can be used to interface 8- or 16-bit memories.

#### 1 Overview

The expansion bus multiplexer module (EBM) has the following features:

- o Multiplexing of I/O signals to an expansion memory interface or a peripheral interface

- $\rm o~Supports$  8- and 16- bit expansion bus memory interface mappings

- o Supports mapping of the following expansion bus signals:

- n Up to 30-bit address bus (EBADDR[29:0]) for 8- bit data bus

- n Up to 22-bit address bus (EBADDR[21:0]) for 16- bit data bus

- n 8- or 16- bit data bus (EBDATA[7:0] or EBDATA[15:0])

- n Up to 2 write strobes

- n Up to 4 memory chip selects

- n 1 output enable

- n 1 external hold signal for interfacing to slow memories

- n Up to 8 DMA request lines

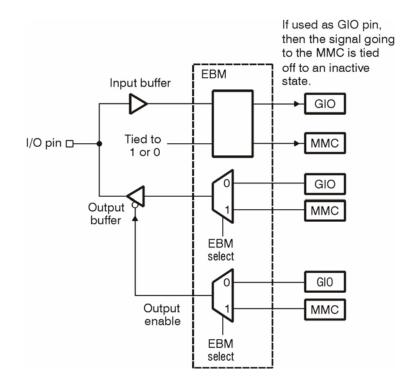

Figure 1 provides a diagram of the EBM.

# Figure 1. EBM Overview

# 2 Description

This section describes the EBM signals and provides the timing parameters.

#### 2.1 EBM Signals

-

Table 1 contains the names of the EBM signals and their descriptions.

Table 1. EBM Pin Description

| PIN      | DESCRIPTION                                                                                                                |

|----------|----------------------------------------------------------------------------------------------------------------------------|

| EBDMAREQ | Expansion bus DMA request                                                                                                  |

| EBOE     | Expansion bus output enable                                                                                                |

| EBWR     | Expansion bus write strobe. $\overline{\text{WR1}}$ controls EBDATA[15:8] and $\overline{\text{WR0}}$ controls EBDATA[7:0] |

| EBCS     | Expansion bus chip select                                                                                                  |

| EBADDR   | Expansion bus address pin                                                                                                  |

| EBDATA   | Expansion bus data pin                                                                                                     |

| EBHOLD   | Expansion bus hold. An external device may assert this signal to add wait states to an expansion bus transaction.          |

Note:

Please refer to the specific data sheet for the actual EBM signal mappings to the device functional pins.

# Note:

Signals that are not used for expansion bus functions can be used as  $\ensuremath{\mathsf{I/O}}$  signals.

# 3 EBM Register Overview

Table 2 displays a general representation of the EBM internal registers. Writes have no effect on the upper 16 bits of these registers. Figure 2 shows the summary of the register bits.

| Address               |         |                                      |                                                                                                                                                                                                                                          |

|-----------------------|---------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset <sup>(1)</sup> | Label   | Name                                 | Description                                                                                                                                                                                                                              |

| 0x00                  | EBDMACR | EBM DMA Request<br>Control Register  | Controls the multiplexing of the expansion bus DMA requests with the functional I/O pins.                                                                                                                                                |

| 0x04                  | EBRWCR  | EBM Read Write<br>Control Register   | Controls the multiplexing of the expansion bus chip selects, the read enable, the write enable and the hold signals with the functional I/O pins.                                                                                        |

| 0x08                  | EBACR1  | EBM Address Control<br>Register 1    | Controls the multiplexing of the expansion bus address lines 5 down to 0 with the functional I/O pins. Also controls the multiplexing of the write enable signals 3–2.                                                                   |

| 0x0C                  | EBDCR   | EBM Data<br>Control Register         | Controls the multiplexing of the expansion bus data lines 7–0 with the functional I/O pins.                                                                                                                                              |

| 0x10                  | EBADCR  | EBM Address/Data<br>Control Register | <i>8-bit mode:</i> Controls the multiplexing of the expansion bus address lines 13–6.<br><i>16-bit mode:</i> Controls the multiplexing of the expansion bus data lines 15–8 in 16-bit mode.                                              |

| 0x14                  | EBACR2  | EBM Address<br>Control Register 2    | <i>8-bit mode:</i> Controls the multiplexing of the expansion address lines 21–14 with the functional I/O pins. <i>16-bit mode:</i> Controls the multiplexing of the expansion address lines 13–6 with the functional I/O pins.          |

| 0x18                  | EBACR3  | EBM Address<br>Control Register 3    | <i>8-bit mode:</i> Controls the multiplexing of the expansion bus address lines 29–22 with the functional I/O pins. <i>16-bit mode:</i> Controls the multiplexing of the expansion bus address lines 21–14 with the functional I/O pins. |

| 0x1C                  | EBMCR1  | EBM Control Register 1               | Controls the type of expansion bus interface.                                                                                                                                                                                            |

## Table 2. EBM Internal Registers

1) The actual address of these registers is device- and CPU-specific. See the specific device data sheet to verify the EBM register addresses.

| gure 2. EBM Register Summary |              |          |                       |  |      |       |       |  |  |               |        |           |           |          |         |        |      |

|------------------------------|--------------|----------|-----------------------|--|------|-------|-------|--|--|---------------|--------|-----------|-----------|----------|---------|--------|------|

| Offset<br>Addres             | s † Register | 15       | 15 14 13 12 11 10 9 8 |  |      |       |       |  |  | 7             | 6      | 5         | 4         | 3        | 2       | 1      | 0    |

| 0x00                         | EBDMACR      | Reserved |                       |  |      |       |       |  |  | EBDMAREQ[7:0] |        |           |           |          |         |        |      |

| 0x04                         | EBRWCR       | Reserved |                       |  |      |       |       |  |  |               |        | EBC       | S[3:0]    |          | EBW     | R[1:0] | EBOE |

| 0x08                         | EBACR1       | Reserved |                       |  |      |       |       |  |  | EBW           | R[3:2] |           |           | EBADI    | DR[5:0] |        |      |

| 0x0C                         | EBDCR        | Reserved |                       |  |      |       |       |  |  | EBDATA[7:0]   |        |           |           |          |         |        |      |

| 0x10                         | EBADCR       |          |                       |  | Rese | erved |       |  |  |               |        | EBAD      | DDR[13:6] | ]/EBDATA | [15:8]  |        |      |

| 0x14                         | EBACR2       | Reserved |                       |  |      |       |       |  |  |               |        | EBAD      | DR[21:14  | ]/EBADDF | R[13:6] |        |      |

| 0x18                         | EBACR3       | Reserved |                       |  |      |       |       |  |  |               | EBADI  | DR[29:22] | /EBADDF   | R[21:14] |         |        |      |

| 0x1C                         | EBMCR1       |          |                       |  |      | Rese  | erved |  |  |               |        |           | 0         |          | DS      | IZE    | LPM  |

• Figure 2. EBM Register Summary

# 4 EBM Register Detailed Description

The following sections describe the registers individually.

## 4.1 EBM Request Control Register (EBDMACR)

Figure 3 and Table 3 describe this register.

## Figure 3. EBM Request Control Register (EBDMACR)

| Bits  | 7            | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---------------|---|---|---|---|---|---|--|

| 0x00h |              | EBDMAREQ[7:0] |   |   |   |   |   |   |  |

|       | R/W-0        |               |   |   |   |   |   |   |  |

|       | R/W = Read/W | rite          |   |   |   |   |   |   |  |

#### Table 3. EBM Request Control Register (EBDMACR) Field Descriptions

| Bit | Name          | Value | Description                                                  |

|-----|---------------|-------|--------------------------------------------------------------|

| 7–0 | EBDMAREQ[7:0] |       | DMA Request                                                  |

|     |               | 0     | I/O signals are mapped to the mux output.                    |

|     |               | 1     | Expansion bus DMA signals 7–0 are mapped to the out-<br>put. |

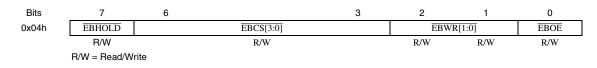

# 4.2 EBM Read/Write Control Register (EBRWCR)

Figure 4 and Table 4 describe this register.

## Figure 4. EBM Read/Write Control Register (EBRWCR)

## Table 4. EBM Read/Write Control Register (EBRWCR) Field Descriptions

| Bit | Name      | Value | Description                                                                                                         |

|-----|-----------|-------|---------------------------------------------------------------------------------------------------------------------|

| 7   | EBHOLD    |       | Hold                                                                                                                |

|     | EBHOLD    |       | Note: See note in Examples section                                                                                  |

|     |           | 0     | The I/O signal is mapped to the mux output.                                                                         |

|     |           | 1     | This pin is available to be asserted by an external device to add wait states to an expansion bus transac-<br>tion. |

| 6–3 | EBCS[3:0] |       | Chip Selects                                                                                                        |

|     |           | 0     | The I/O signal is mapped to the mux output.                                                                         |

|     |           | 1     | The expansion bus chip selects 3–0 are mapped to the mux output.                                                    |

| 2–1 | EBWR[1:0] |       | Write Enable                                                                                                        |

|     |           | 0     | The I/O signal is mapped to the mux output.                                                                         |

|     |           | 1     | The write enable bits are mapped to the mux output.                                                                 |

| 0   | EBOE      |       | Output Enable                                                                                                       |

|     |           | 0     | The I/O signal is mapped to the mux output.                                                                         |

|     |           | 1     | The output enable bits are mapped to the mux output.                                                                |

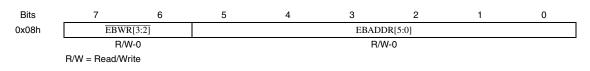

# 4.3 EBM Address Control Register 1 (EBACR1)

Figure 5 and Table 5 describe this register.

#### Figure 5. EBM Address Control Register 1 (EBACR1)

### Table 5. EBM Address Control Register 1 (EBACR1) Field Descriptions

| Bit | Name        | Value | Description                                         |

|-----|-------------|-------|-----------------------------------------------------|

| 7–6 | EBWR[3:2]   |       | Write Enable                                        |

|     |             | 0     | The I/O signal is mapped to the mux output.         |

|     |             | 1     | The write enables are mapped to the mux output.     |

| 5–0 | EBADDR[5:0] |       | Address Line                                        |

|     |             | 0     | The I/O signal is mapped to the mux output.         |

|     |             | 1     | The address lines 5–0 are mapped to the mux output. |

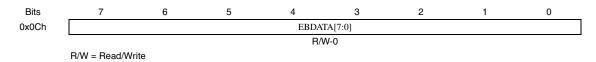

# 4.4 EBM Data Control Register (EBDCR)

Figure 6 and Table 6 describe this register.

## Figure 6. EBM Data Control Register (EBDCR)

## Table 6. EBM Data Control Register (EBDCR) Field Descriptions

| Bit | Name        | Value | Description                                      |

|-----|-------------|-------|--------------------------------------------------|

| 7–0 | EBDATA[7:0] |       | Expansion Bus Data                               |

|     |             | 0     | The I/O signal is mapped to the mux output.      |

|     |             | 1     | The data lines 7–0 are mapped to the mux output. |

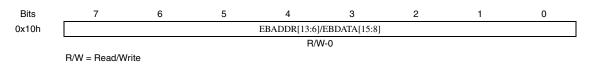

## 4.5 EBM Address/Data Control Register (EBADCR)

Figure 7 and Table 7 describe this register.

#### Figure 7. EBM Address/Data Control Register (EBADCR)

## Table 7. EBM Address/Data Control Register (EBADCR) Field Descriptions

| Bit | Name                          | Value | Description                                                                                                                                                       |

|-----|-------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | EBADDR[13:6]/<br>EBDATA[15:8] |       | Address/Data                                                                                                                                                      |

|     |                               | 0     | In both 8-bit and 16-bit modes:<br>The I/O signal is mapped to the mux output.                                                                                    |

|     |                               | 1     | <i>In 8-Bit Mode:</i><br>The address lines 13–6 are mapped to the mux out-<br>put.<br><i>In 16-Bit Mode:</i><br>The data lines 15–8 are mapped to the mux output. |

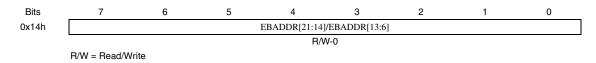

# 4.6 EBM Address Control Register 2 (EBACR2)

Figure 8 and Table 8 describe this register.

## Figure 8. EBM Address Control Register 2 (EBACR2)

## Table 8. EBM Address Control Register 2 (EBACR2) Field Descriptions

| Bit | Name                           | Value | Description                                                                                                                                                      |

|-----|--------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | EBADDR[21:14]/<br>EBADDR[13:6] |       | Address/Data                                                                                                                                                     |

|     |                                | 0     | In both 8-bit and 16-bit modes:<br>The I/O signal is mapped to the mux output.                                                                                   |

|     |                                | 1     | <i>In 8-Bit Mode:</i><br>The address lines 21–14 are mapped to the mux output.<br><i>In 16-Bit Mode:</i><br>The address lines 13–6 are mapped to the mux output. |

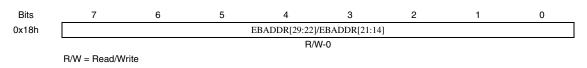

# 4.7 EBM Address Control Register 3 (EBACR3)

Figure 9 and Table 9 describe this register.

#### Figure 9. EBM Address Control Register 3 (EBACR3)

## Table 9. EBM Address Control Register 3 (EBACR3) Field Descriptions

| Bit | Name                            | Value | Description                                                                                                                                                       |

|-----|---------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 | EBADDR[29:22]/<br>EBADDR[21:14] |       | Address/Data                                                                                                                                                      |

|     |                                 | 0     | In both 8-bit and 16-bit modes:<br>The I/O signal is mapped to the mux output.                                                                                    |

|     |                                 | 1     | <i>In 8-Bit Mode:</i><br>The address lines 29–22 are mapped to the mux output.<br><i>In 16-Bit Mode:</i><br>The address lines 21–14 are mapped to the mux output. |

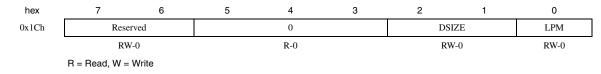

## 4.8 EBM Control Register 1 (EBMCR1)

Figure 10 and Table 10 describe the EBM control register 1.

Figure 10. EBM Control Register 1 (EBMCR1)

Table 10. EBM Control Register 1 (EBMCR1) Bit Descriptions

| Bit | Name     | Value | Description                               |

|-----|----------|-------|-------------------------------------------|

| 7–6 | Reserved |       | Reads are zero and writes have no effect. |

| 5–3 | 0        | 000   | These bits are tied to 0 by default       |

| 2–1 | DSIZE    |       | Memory Interface Data Size                |

|     |          | 00    | 8-bit data bus width                      |

|     |          | 01    | 16-bit data bus width                     |

|     |          | 10    | Reserved                                  |

|     |          | 11    | Reserved                                  |

| 0   | LPM      |       | Local Power Down Mode                     |

|     |          | 0     | Module is not locally powered down.       |

|     |          | 1     | Module is locally powered down.           |

#### 5 Example for Interfacing 64k of External 16-Bit Memory

Only the setup of registers pertinent to the EBM are mentioned here. Assumptions:

- o 64k of 16-bit memory is connected to chip select 5.

- o Chip select 5 corresponds to MCBAHR2/MCBALR2 and SMCR5.

To implement interfacing 64k of external 16-bit memory, follow these steps.

- 1) Configure system clock. For example: GLBCTRL = 0x09;

- Set the memory course base address registers (MCBAHRx, MCBALRx) for the chip select connected to the EBM memory or peripheral. Enable the memory map. For example:

MCBAHR2 = 0x0030; //EBM RAM base addr at 0x00300000 MCBALR2 = 0x0020; //Size of 64k MFBALR0 = 0x0100; //Enable the memory map

In the SMCR register, set the memory location as "external" and set the wait states, if needed. For example:

SMCR5 = 0x35; //16-bit data width/External/Big Endian/3 wait

states

For expansion bus clock and wait states information, please refer to SPNU189. Please refer to the specific device data sheet for expansion bus timing information.

#### Note: Slow Memory

For interfaces to slow **memory**, allow the wait states to be generated by the CPU. The wait state generation is configured in the SMCR register.

#### Note: Slow Peripherals

For optimum performance when interfacing to slow **peripherals**, reads need to be accompanied by an EBHOLD signal from the peripheral to generate the wait states. However, if the peripheral cannot generate EBHOLD, and it is not possible to do so with an external programmable logic device, then allow the wait state generation to be handled by the CPU, as is the case when interfacing to memories. 4) Configure peripheral ICLK. For example: PCR = 0x02;

For expansion bus clock and wait states information, please refer to SPNU189.

- 5) Release peripheral reset. For example: PCR |= 0x01; // Enable Peripherals

- 6) Set the EBM address, data and control lines that are required in the application in the EBM control registers. Configure the data bus bit width in EBMCR1. For example:

- (If needed) Set up the DMA registers for the DMA channel(s) that the expansion bus DMA request line(s) (EBDMAREQx) maps to.