# TMS320C6000 Expansion Bus to Intel80960Kx/Jx Microprocessor Interface

Zoran Nikolic

DSP Applications

## ABSTRACT

This application report describes how to interface the Texas Instruments (TI) TMS320C6000<sup>™</sup> (C6000<sup>™</sup>) digital signal processor (DSP) to the Intel 80960Kx/Jx microprocessor. This document contains:

- A block diagram of the interface

- Information required to configure the Intel80960

- Timing diagrams illustrating the interface functionality

## Note:

The information presented in this application report has been verified using VHDL simulation.

## Contents

| 1   | Intel8096 | 60Kx/Jx Interface                 | 2  |

|-----|-----------|-----------------------------------|----|

| 2   | Configu   | ration                            | 3  |

| 3   | Timing V  | /erification                      | 5  |

| 4   | Reference | ces                               | 9  |

| Арр | endix A   | i80960 Timing Requirements        | 10 |

| Арр | endix B   | TMS320C6000 DSP Timing Parameters | 11 |

## List of Figures

| Figure 1. | Intel80960Jx to Expansion Bus Interface                   | 2 |

|-----------|-----------------------------------------------------------|---|

| Figure 2. | Burst Write Initiated by Intel80960Kx/Jx to Expansion Bus | 6 |

| Figure 3. | Burst Read Initiated by Intel80960Kx/Jx to Expansion Bus  | 7 |

## List of Tables

| Table 1. Intel80960Jx/Kx to Expansion Bus Signal Connections                        | 3 |

|-------------------------------------------------------------------------------------|---|

| Fable 2. TMS320C6000 Boot Configuration via Pull-Up/Pull-Down Resistors on XD[31:0] | 4 |

| Fable 3. Timing Requirements for TMS320C6000 (Intel80960JD Expansion Bus Master)    | 8 |

| Fable 4. Timing Requirements for i960JD (i960JD Expansion Bus Master)               | 8 |

TMS320C6000 and C6000 are trademarks of Texas Instruments.

Trademarks are the property of their respective owners.

| Table A-1. | Intel 80960JD Timing Parameters                                               | 10 |

|------------|-------------------------------------------------------------------------------|----|

| Table B-1. | TMS320C6202/C6202B/C6203/C6204 Timing Parrameters                             |    |

|            | (External Device is a Master)                                                 | 11 |

| Table B–2. | TMS320C6202/C6202B/C6203/C6204 Timing Parameters<br>(TMS320C620x is a Master) | 11 |

# 1 Intel80960Kx/Jx Interface

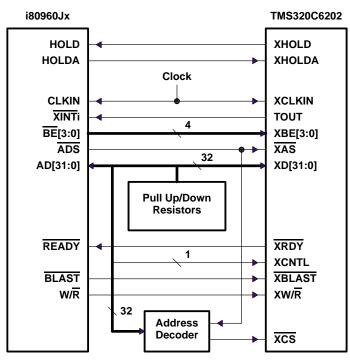

The Intel80960Kx/Jx microprocessors have a multiplexed data/address bus similar to the expansion bus. The only glue required is the address decoder that selects the expansion bus. Figure 1 shows the interface between the Intel80960Kx/Jx and the expansion bus. Note that the internal bus arbiter of the expansion bus is disabled. The TMS320C6000 DSP requests the expansion bus only if it needs to access the FIFO or asynchronous I/O port (this is not shown in the block diagram).

Figure 1. Intel80960Jx to Expansion Bus Interface

| Expansion Bus Signal | Intel80960Jx/Kx Pin                                  | Comments                                                                                                                                                                                                                                |

|----------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XCNTL                | A[2]                                                 | Address bit of Intel80960 is used as control signal.                                                                                                                                                                                    |

| XBLAST               | BLAST                                                | Indicates the last transfer in a burst. The polarity of XBLAST (in this case active low) is determined during reset using pull-down resistor on XD[13].                                                                                 |

| XW/R                 | W/R                                                  | Indicates a read or write access. The polarity of XW/R is determined during reset using pull-down resistor on XD[12].                                                                                                                   |

| XD[31:0]             | AD[31:0]                                             | 32 bits of data                                                                                                                                                                                                                         |

| XHOLD                | HOLD                                                 | Bus arbitration signal (internal bus arbiter of the expansion bus is disabled).                                                                                                                                                         |

| XHOLDA               | HOLDA                                                | Bus arbitration signal (internal bus arbiter of the expansion bus is disabled).                                                                                                                                                         |

| XAS                  | ADS                                                  | Address strobe indicates the transfer of a physical address.                                                                                                                                                                            |

| XCS                  | Address lines are decoded and synchronized using ADS | Because the Intel80960Jx/Kx does not have a chip<br>select line, it is necessary to use some decode logic<br>as an input to XCS.<br>The XBISA and XBD registers were mapped to<br>locations 0x10000004 and 0x10000000,<br>respectively. |

| XBE[3:0]             | BE[3:0]                                              | Expansion bus byte enables                                                                                                                                                                                                              |

| XINTi                | TOUT                                                 | The expansion bus does not have an interrupt pin,<br>so general-purpose output TOUT is used as an<br>interrupt output.                                                                                                                  |

| XRDY                 | RDYRCV                                               | Ready signal                                                                                                                                                                                                                            |

| XCLK                 | CLKIN                                                | Expansion bus clock                                                                                                                                                                                                                     |

## Table 1. Intel80960Jx/Kx to Expansion Bus Signal Connections

If a 5-V host device is used (for example, the Intel80960Kx), the voltage translation interface is needed. (The voltage translation logic is not shown in the block diagram.)

The C6000 DSP uses the data pins on the expansion bus to latch the configuration word during reset. The configuration word is set using pull-up/down resistors. When in reset, the Intel microprocessor drives the bus; and if the DSP and the i80960Kx/Jx are in reset together, the DSP cannot latch proper configuration values. Therefore, the i80960Kx/Jx has to be reset first. After the i80960Kx/Jx gets out of reset, the HOLD signal has to be sent to the i80960Kx/Jx to ensure that the bus is not driven during the period when the DSP is getting out of reset. This way the i80960Kx/Jx does not interfere with the DSP configuration procedure. The reset circuitry that ensures that the DSP latches the correct configuration word of the expansion bus during reset is not shown in Figure 1.

## 2 Configuration

The only programmable physical memory attribute for the Intel80960Jx/Kx microprocessor is the bus width, which can be 8-, 16- or 32-bits wide.

For the purposes of assigning memory attributes, the physical address space is partitioned into eight fixed 512-MB regions determined by the upper three address bits. The physical memory attributes for each region are programmable through the PMCON registers. The PMCON registers are loaded from the control table. The Intel80960Jx microprocessor provides one PMCON register for each region.

The bus width for a region is controlled by the BW[1:0] bits in the PMCON register. The BW1 = 1 and BW0 = 0 for the 32-bit expansion-bus interface.

All eight PMCON registers are loaded automatically during system auto-initialization. Immediately after a hardware reset, the PMCON register contents are marked invalid in the bus control (BCON) register. The initial PMCON register values are stored in the control table in the initialization boot record. After hardware reset, the processor first loads all PMCON registers from the control table. The processor then loads BCON from the control table. The BCON.ctv bit in BCON must be set to use the programmed PMCON values for each memory region.

The default logical memory configuration register (DLMCON) provides default logical memory control for those accesses not falling within a region defined by the logical memory control register pairs. On the Intel80960Jx, the byte order programmed in the DLMCON register controls byte ordering for the entire 32-bit memory space. The DCEN bit field of the DLMCON register must be set to zero to disable data caching. The BE bit field of the DLMCON register must be set to zero to enable little-endian byte order for all accesses.

The interrupt controller register of the Intel80960Jx processors controls basic functionality such as interrupt mode, signal detection, global enable/disable, mask operation, interrupt vector caching, and sampling mode (for more detailed information on interrupt configuration, please see the *i960 Jx Microprocessor User's Manual*).

The Timers chapter in the *TMS320C6000 Peripherals Reference Guide* (SPRU190) describes how to configure timer pins for general-purpose input and output (Tout is used to generate an interrupt to the host microprocessor.).

The TMS320C6000 DSP boot configuration is presented in Table 2.

| Field         | Description                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLPOL         | Determines polarity of /XBLAST signal<br>BLPOL = 0, XBLAST is active low.                                                                                                                            |

| RWPOL         | Determines polarity of expansion bus read/write signal RWPOL = 0, XW/R                                                                                                                               |

| HMOD          | Host mode (status in XB HPIC)<br>HMOD = 1, external host interface is in synchronous master/slave mode                                                                                               |

| XARB          | Expansion bus arbiter (status in XBGC)<br>XARB = 0, internal expansion bus arbiter is disabled.                                                                                                      |

| FMOD          | FIFO mode (status in XBGC)                                                                                                                                                                           |

| LEND          | Little-endian mode<br>LEND = 1, system operates in little-endian mode                                                                                                                                |

| BootMode[4:0] | Dictates the boot mode of the device, including host port boot, ROM boot, memory map selection. For a complete list of boot modes, see the <i>TMS320C6000 Peripherals Reference Guide</i> (SPRU190). |

## 3 Timing Verification

To verify proper operation, two functions have been examined:

1. An Intel80960JD write to the expansion bus

## 2. An Intel80960JD read from the expansion bus

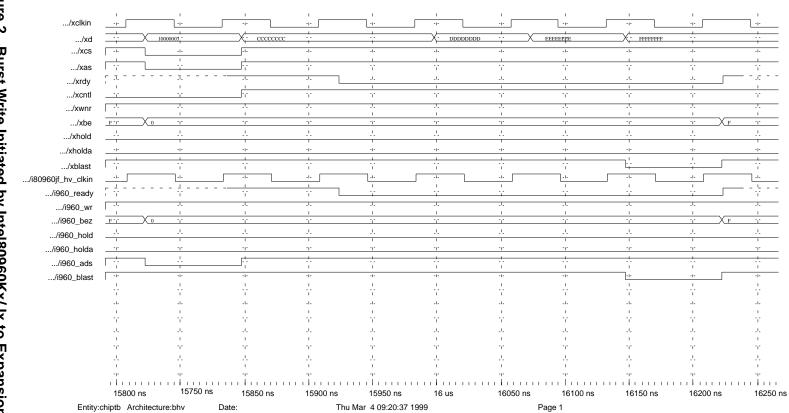

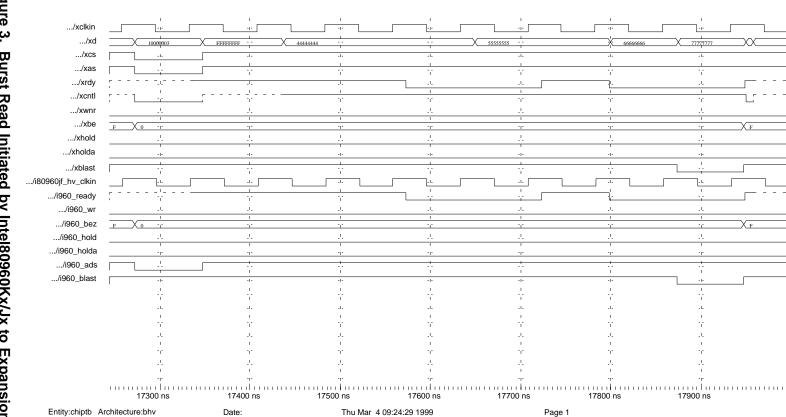

In each instance, timing requirements were compared for each of the devices and the results are shown in Figure 2, Figure 3, Table 3, and Table 4.

The interface was functionally verified using VHDL simulation (Synopsys SmartModel of the Intel80960KA was used in the test bench). The timing diagrams shown in Figure 2 and Figure 3 are outputs from the simulation. The clock ratio between the operating frequency of the TMS320C6202 and the XCLKIN frequency was set to 7.5.

Note that the expansion bus timing parameters for the TMS320C6202, C6202B, C6203, and C6204 are similar.

ი

# Figure Ņ Burst Write Initiated by Intel80960Kx/Jx to Expansion Bus

# Figure 3. Burst Read Initiated by Intel80960Kx/Jx to Expansion Bus

## Table 3. Timing Requirements for TMS320C6000 (Intel80960JD Expansion Bus Master)

| Intel80960JD Symbol | C6000 Symbol     | Parameter                                          | Intel80960JD Min<br>(ns) | C6000* Min<br>(ns) |

|---------------------|------------------|----------------------------------------------------|--------------------------|--------------------|

| Tcyc-tOV1-tPAL      | Tsu(XCSV-XCKIH)  | Chip-select (XCS) valid before XCLKIN<br>high      | 11.5                     | 3.5                |

| tOV1+tPAL           | Th(XCKIH -XCSV)  | Chip-select (XCS) valid after XCLKIN<br>high       | 7.5                      | 2.8                |

| Tcyc-tOV1           | Tsu(XASV-XCKIH)  | Address strobe (XAS) valid before<br>XCLKIN high   | 16.5                     | 3.5                |

| TOV1                | Th(XCKIH-XASV)   | Address strobe (XAS) valid after XCLKIN<br>high    | 13.5                     | 2.8                |

| Tcyc-tOV1           | Tsu(XBLTV-XCKIH) | Burst last (XBLAST) valid before XCLKIN<br>high    | 16.5                     | 3.5                |

| TOV1                | Th(XCKIH-XBLTV)  | Burst last (XBLAST) valid after XCLKIN<br>high     | 13.5                     | 2.8                |

| Tcyc-tOV1           | Tsu(XD-XCKIH)    | Data (XD) valid before XCLKIN high (WRITE)         | 16.5                     | 3.5                |

| TOV1                | Th(XCKIH-XD)     | Data (XD) valid after XCLKIN high<br>(WRITE)       | 13.5                     | 2.8                |

| Tcyc-tOV1           | Tsu(XBEV-XCKIH)  | Byte enable (XBE[3:0]) valid before<br>XCLKIN high | 16.5                     | 3.5                |

| TOV1                | Th(XCKIH-XBEV)   | Byte enable (XBE[3:0]) valid after<br>XCLKIN high  | 13.5                     | 2.8                |

| Tcyc-tOV1           | Tsu(XWR-XCKIH)   | Read/write (XR/W) valid before XCLKIN<br>high      | 16.5                     | 3.5                |

| TOV1                | Th(XCKIH-XWR)    | Read/write (XR/W) valid after XCLKIN<br>high       | 13.5                     | 2.8                |

\* C6000 in this case refers to C6202, C6202B, C6203, and C6204.

## Table 4. Timing Requirements for i960JD (i960JD Expansion Bus Master)

| Intel80960JD<br>Symbol | C6000 Symbol       | Parameter                                      | Intel80960JD<br>Min (ns) | C6000*<br>Min (ns) |

|------------------------|--------------------|------------------------------------------------|--------------------------|--------------------|

| TIS2                   | Tcyc-Td(XCKIH-XRY) | Ready signal (RDYRCV) valid before XCLKIN high | 6.5                      | 14.5               |

| TIH2                   | Td(XCKIH-XRY)      | Ready signal (RDYRCV) valid after XCLKIN high  | 1                        | 5                  |

| TIS1                   | Tcyc-Td(XCKIH-XDV) | Data (XD) valid before<br>XCLKN high (READ)    | 6                        | 14.5               |

| TIH1                   | Td(XCKIH-XDIV)     | Data (XD) invalid after<br>XCLKIN high (READ)  | 1.5                      | 5                  |

\* C6000 in this case refers to C6202, C6202B, C6203, and C6204.

The timing tables above show that the timing parameters for both devices are met in the interface of Intel80960JD and TMS320C6202. This interface is based on the Intel80960JD (local bus is running at 33 MHz) and the TMS320C6000 device (C6202, C6202B, C6203, and C6204) at any frequency ranging from 100 MHz-250 MHz.

## 4 References

- 1. TMS320C6000 Peripherals Reference Guide (SPRU190).

- 2. TMS320C6202, TMS320C6202B Fixed-Point Digital Signal Processors (SPRS104).

- 3. TMS320C6204 Fixed-Point Digital Signal Processor (SPRS152).

- 4. 1960 Jx Microprocessor User's Manual, Order #272483, Intel Corporation.

# Appendix A i80960 Timing Requirements

| Characteristic                                                            | Symbol | Min (ns) | Max (ns) |

|---------------------------------------------------------------------------|--------|----------|----------|

| Output valid delay, except ALE inactive and DT/R- for 3.3-V input signals | tOV1   | 2.5      | 13.5     |

| Output float delay                                                        | tOF    | 2.5      | 13.5     |

| input setup to CLKIN- AD[31:0]                                            | tIS1   | 6        |          |

| Input hold from CLKIN AD[31:0]                                            | tlH1   | 1.5      |          |

| Input setup to CLKIN RDYRCV-                                              | tIS2   | 6.5      |          |

| Input hold from CLKIN RDYRCV-                                             | tIH2   | 1        |          |

| Address valid to ALE Inactive                                             | tLX    | 10       |          |

| ALE width                                                                 | tLXL   | 8        |          |

| Address hold from ALE inactive                                            | tLXA   | 8        |          |

| DT/R- valid to DEN- active                                                | tDXD   | 8        |          |

## Table A-1. Intel 80960JD Timing Parameters

The timing requirements in Table A–1 are provided for quick reference only. For detailed description, notes, and restrictions, please see the *I960JD Microprocessor User's Manual*.

Setup time, XBLAST valid before XCLKIN high

Hold time, XBLAST valid after XCLKIN high

Setup time, XBE valid before XCLKIN high

Hold time, XBE valid after XCLKIN high

Hold time, XD valid after XCLKIN high

Delay time, XCLKIN high to XD valid

Delay time, XCLKIN high to XD invalid

Delay time, XCLKIN high to XRDY valid

Setup time, XD valid before XCLKIN high

Delay time, XCLKIN high to XD low impedance

Delay time, XCLKIN high XD high impedance

# Appendix B TMS320C6000 Timing Parameters

| (External Device is a Master)              |                 |          |          |  |

|--------------------------------------------|-----------------|----------|----------|--|

| Characteristic                             | Symbol          | Min (ns) | Max (ns) |  |

| Setup time, XCS valid before XCLKIN high   | Tsu(XCSV-XCKIH) | 3.5      |          |  |

| Hold time, XCS valid after XCLKIN high     | Th(XCKIH-XCSV)  | 2.8      |          |  |

| Setup time, XAS valid before XCLKIN high   | Tsu(XASV-XCKIH) | 3.5      |          |  |

| Hold time, XAS valid after XCLKIN high     | Th(XCKIH-XASV)  | 2.8      |          |  |

| Setup time, XCNTL valid before XCLKIN high | Tsu(XCTL-XCKIH) | 3.5      |          |  |

| Hold time, XCNTL valid after XCLKIN high   | Th(XCKIH-XCTL)  | 2.8      |          |  |

| Setup time, XWR valid before XCLKIN high   | Tsu(XWR-XCKIH)  | 3.5      |          |  |

| Hold time, XWR valid after XCLKIN high     | Th(XCKIH-XWR)   | 2.8      |          |  |

Tsu(XBLTV-XCKIH)

Th(XCKIH-XBLTV)

Tsu(XBEV-XCKIH)

Th(XCKIH-XBEV)

Tsu(XD-XCKIH)

Th(XCKIH-XD)

Td(XCKIH-XDLZ)

Td(XCKIH-XDV)

Td(XCKIH-XDIV)

Td(XCKIH-XDHZ)

Td(XCKIH-XRY)

3.5

2.8

3.5

2.8

3.5

2.8

16.5

4P

16.5

0

5

5

## Table B-1. TMS320C6202/C6202B/C6203/C6204 Timing Parrameters (External Device is a Master)

## Table B-2. TMS320C6202/C6202B/C6203/C6204 Timing Parameters (TMS320C620x is a Master)

| Characteristic                               | Symbol          | Min (ns) | Max (ns) |

|----------------------------------------------|-----------------|----------|----------|

| Setup time, XD valid before XCLKIN high      | Tsu(XDV-XCKIH)  | 3.5      |          |

| Hold time, XD valid after XCLKIN high        | Th(XCKIH-XDV)   | 2.8      |          |

| Setup time, XRDY valid before XCLKIN high    | Tsu(XRY-XCKIH)  | 3.5      |          |

| Hold time, XRDY valid after XCLKIN high      | Th(XCKIH-XRY)   | 2.8      |          |

| Setup time, XBOFF valid before XCLKIN high   | Tsu(XBFF-XCKIH) | 3.5      |          |

| Hold time, XBOFF valid after XCLKIN high     | Th(XCKIH-XBFF)  | 2.8      |          |

| Delay time, XCLKIN high to XAS valid         | Td(XCKIH-XAS)   | 5        | 16.5     |

| Delay time, XCLKIN high to XWR valid         | Td(XCKIH-XWR)   | 5        | 16.5     |

| Delay time, XCLKIN high to XBLAST valid      | Td(XCKIH-XBLTV) | 5        | 16.5     |

| Delay time, XCLKIN high to XBE valid         | Td(XCKIH-XBEV)  | 5        | 16.5     |

| Delay time, XCLKIN high to XD low impedance  | Td(XCKIH-XDLZ)  | 0        |          |

| Delay time, XCLKIN high to XD valid          | Td(XCKIH-XDV)   |          | 16.5     |

| Delay time, XCLKIN high to XD invalid        | Td(XCKIH-XDIV)  | 5        |          |

| Delay time, XCLKIN high to XD high impedance | Td(XCKIH-XDHZ)  |          | 16       |

| Delay time, XCLKIN high to XWE/XWAIT valid   | Td(XCKIH-XWTV)  | 5        | 16.5     |

The timing parameters in Table B-1 through Table B-2 are provided for quick reference only. For detailed description, notes, and restrictions, please see the corresponding Fixed-Point Digital Signal Processor data sheet.

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated