# 66AK2Ex KeyStone™ Multicore DSP+ARM® System-on-Chips

### **Overview**

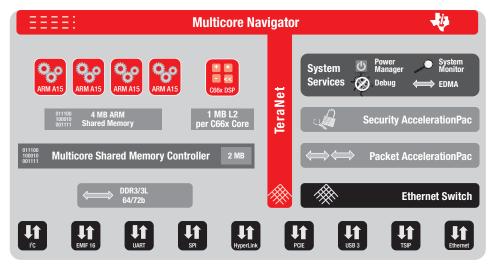

The 66AK2Ex platform, based on TI's industry leading KeyStone™ II architecture, combines up to four ARM<sup>®</sup> Cortex<sup>™</sup>-A15 MPCore<sup>™</sup> processors with TI's TMS320C66x highperformance fixed- and floating-point DSP. The 66AK2Ex platform provides up to 5.6 GHz of ARM and 1.4 GHz of DSP processing coupled with security and packet processing and Ethernet switching, all at lower power than multichip solutions making it optimal for embedded systems. For applications like industrial imaging, industrial control, industrial routing and switching, enterprise gateway, avionics and defense, and general-purpose embedded controllers, the 66AK2Ex platform combines ARM's best-in-class single-thread performance for control processing with the compute performance of the C66x DSP. Using TI's heterogeneous programming runtime software and tools, customers can easily develop differentiated products with 66AK2Ex SoCs.

#### **Power and Performance**

The combined floating-point processing power of the ARM Cortex-A15 processor and C66x DSP core is more than 67 GFLOPS of double-precision performance and more than 198 GFLOPS of single-precision performance. Combining the real-time performance of the C66x DSP with ARM Cortex-A15 general-purpose embedded processors yields new opportunities for bringing powerful analytics to emerging applications. These SoCs deliver new levels of power savings, achieving as low as 6 Watts on the 66AK2E02 SoC.

### **Fast and Wide Packet Interfaces**

Processing performance alone doesn't differentiate infrastructure from consumer applications. High-performance networking

## **Key Features**

Key features of 66AK2Ex devices include:

#### CorePac Processors

- Up to four Cortex-A15 processors, 19600 Dhrystone MIPS

- One C66x DSP core, 44.8 GMACS / 22.4 GFLOPS

#### Network AccelerationPac

- Packet coprocessor (IPv4/IPv6) for Layer 2–4

- Security coprocessor IPSec/SRTP

- Five-port 1Gb Ethernet switch

- Three-port 10Gb Ethernet switch

#### Memory

- Cache-coherent Multicore Shared Memory Controller (MSMC)

- 4MB Level 2 RAM/cache for ARM cluster with ECC and cache coherency

- 512KB Level 2 RAM/cache for DSP core with ECC

- 2MB shared memory with ECC and cache coherency

- One DDR3/3L 1600 interface with ECC

#### KeyStone II Architecture

- Multicore Navigator brings single-core programming simplicity to multicore SoCs

- 8,000 atomic hardware gueues

- TeraNet on-chip interconnect providing more than two terabits per second throughput

- Low power 6–9 Watts at 55°C case temperature, 8.5 Watts typical for 66AK2E05 SoC

### High-Speed I/O

- PCI Express Gen2—up to 20 Gbps

- USB 3.0

- 1Gb Ethernet/10Gb Ethernet

- HyperLink up to 50 Gbaud for chip-to-chip interconnect

For more technical detail see the **data sheet**.

interfaces are critical to deliver data to processors fast enough. The on-chip addition of a five-port 1Gb Ethernet switch, three-port 10Gb Ethernet switch, packet coprocessor and security coprocessor provides carrier-grade Ethernet throughput without the increase in ARM or DSP processor loading that normally comes from layer 2-4 processing, encryption and decryption. Other high-performance SERDES interfaces like PCle deliver data to processors at infrastructure speeds, enabling the 66AK2Ex platform to handle tremendous data throughput.

TeraNet is a multilevel interconnection of high-speed non-blocking channels that delivers over two terabits per second of concurrent throughput - enabling full multicore entitlement where every processing element can operate near full capacity all of the time.

HyperLink uses a low overhead protocol that extends the TeraNet off-chip to other KeyStone SoCs and third-party devices making them appear as one larger device while simplifying software development, reducing latency and improving system performance.

## **High-Speed Memory for Demanding Applications**

Infrastructure applications demand nonblocking, high-performance memory with error

correction. For KevStone II. TI upgraded the multicore shared memory controller (MSMC) so that memories can operate at the speed of the processor cores, which reduces latency and contention while providing high-bandwidth interconnections between processor cores and shared internal and external memory. The 72-bit DDR3/3L controller runs at 1600 MT/s with optional error correction (ECC) support and hardware-based cache coherency, enabling more than 12.8-Gbps data transfers between external and internal memory.

# **Tools and Software to Reduce Development Time**

Texas Instruments' development tools and runtime software support make migration and development for heterogeneous platforms simpler than ever.

The Multicore Software Development Kit (MCSDK) provides support for mainline Linux™ and TI's SYS/BIOS™ operating system for ARM and C66x DSP cores. Evaluation modules (EVMs) are available with the MCSDK and preloaded example projects. TI also provides optimized single and multicore DSP libraries for FFT, image and video analytics, matrix math and other commonly used algorithms. Thirdparty commercial RTOSes will also be available for 66AK2Ex processors.

TI was the first to support OpenMP® for multicore DSPs and will continue to advance OpenMP support for KeyStone II platforms. TI's OpenMP software uses a packetbased network-on-chip interconnect called Multicore Navigator to get the best multicore performance. The combination of OpenMP and Multicore Navigator frees developers from complex queue management and allows developers to use industry-standard APIs for programming TI's devices. Support for OpenCL™ is coming soon.

Code Composer Studio™ Integrated Development Environment (IDE) provides a development environment that reduces porting time and can be used as a plug-in to the opensource Eclipse IDE. TI also plans to support open source development and profiling tools for KeyStone II-based SoCs.

For more information about the 66AK2Ex platform and TI's portfolio of KeyStone multicore devices please visit

www.ti.com/multicore

The platform bar, Code Composer Studio, KeyStone and SYS/BIOS are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom Amplifiers amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID <u>www.ti-rfid.com</u>

OMAP Applications Processors <a href="https://www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="https://example.com/omap">e2e.ti.com/omap</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>