# TMS320C80 (MVP) Video Controller

# User's Guide

1995

**Digital Signal Processing Products**

Printed in U.S.A., March 1995

SPRU111A

User's Guide

# **TMS320C80 (MVP) Video Controller**

1995

# TMS320C80 (MVP) Video Controller User's Guide

SPRU111A March 1995

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1995, Texas Instruments Incorporated

### Preface

# **Read This First**

#### About This Manual

The TMS320C80 MVP (multimedia video processor) is Texas Instruments first single-chip multiprocessor DSP (digital signal processor) device. The MVP contains five powerful, fully programmable processors: a master processor (MP) and four parallel processors (PPs). The MP is a 32-bit RISC (reduced instruction set computer) with an integral, high-performance IEEE-754 floating-point unit. Each PP is an advanced 32-bit DSP; thus, in addition to having similar processing capabilities as conventional DSPs, each PP has advanced features to accelerate operation on a variety of data types.

The MVP supports a variety of parallel-processing configurations, which facilitates a wide range of multimedia and other applications that require high processing speeds. Applications include image processing, two- and three-dimensional and virtual reality graphics, audio/video digital compression, and telecommunications.

This manual describes the MVP video controller (VC). The VC provides the video interface between the MVP and the image capture and display systems to perform complex video and audio applications. The VC contains dual frame timers that provide simultaneous image capture and display. This manual provides information about the VC features, architecture, and operation; it also includes procedures and examples for programming the serial register transfer (SRT) controller and the frame timer registers.

#### Related Documentation From Texas Instruments

The following books describe the TMS320C80 MVP and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

- **TMS320C80 Multimedia Video Processor Data Sheet** (literature number SPRS023) describes the features of the 'C80 device and provides pinouts, electrical specifications, and timings for the device.

- **TMS320C80 Multimedia Video Processor (MVP) Technical Brief** (literature number SPRU106) provides an overview of the 'C80 features, development environment, architecture, and memory organization.

- **TMS320C80 (MVP) C Source Debugger User's Guide** (literature number SPRU107) describes the 'C80 master processor and parallel processor C source debuggers. This manual provides information about the features and operation of the debuggers and the parallel debug manager; it also includes basic information about C expressions and a description of progress and error messages.

- **TMS320C80 (MVP) Code Generation Tools User's Guide** (literature number SPRU108) describes the 'C80 code generation tools. This manual provides information about the features and operation of the linker and the master processor (MP) and parallel processor (PP) C compilers and assemblers. It also includes a description of the common object file format (COFF) and shows you how to link MP and PP code.

- **TMS320C80 (MVP) Master Processor User's Guide** (literature number SPRU109) describes the 'C80 master processor (MP). This manual provides information about the MP features, architecture, operation, and assembly language instruction set; it also includes sample applications that illustrate various MP operations.

- **TMS320C80 (MVP) Multitasking Executive User's Guide** (literature number SPRU112) describes the 'C80 multitasking executive software. This manual provides information about the multitasking executive software features, operation, and interprocessor communications; it also includes a list of task error codes.

- **TMS320C80 (MVP) Parallel Processor User's Guide** (literature number SPRU110) describes the 'C80 parallel processor (PP). This manual provides information about the PP features, architecture, operation, and assembly language instruction set; it also includes software applications and optimizations.

- **TMS320C80 (MVP) Transfer Controller User's Guide** (literature number SPRU105) describes the 'C80 transfer controller (TC). This manual provides information about the TC features, functional blocks, and operation; it also includes examples of block write operations for big- and little-endian modes.

- **TMS320C80 (MVP) System-Level Synopsis** (literature number SPRU113) contains the 'C80 system-level synopsis, which describes the 'C80 features, development environment, architecture, memory organization, and communication network (the crossbar).

If You Need Assistance. . .

| If you want to                                                                                        | Do this                                                                                                                                                                                                                                                                   |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Request more<br>information about Texas<br>Instruments Digital<br>Signal Processing<br>(DSP) products | Write to:<br>Texas Instruments Incorporated<br>Market Communications Manager, MS 736<br>P.O. Box 1443<br>Houston, Texas 77251–1443                                                                                                                                        |  |

| Order Texas Instruments documentation                                                                 | Call the TI Literature Response Center: (800) 477–8924                                                                                                                                                                                                                    |  |

| Ask questions about<br>product operation or<br>report suspected<br>problems                           | Call the DSP hotline:<br>(713) 274–2320<br>FAX: (713) 274–2324                                                                                                                                                                                                            |  |

| Report mistakes in this document or any other TI documentation                                        | Fill out and return the reader response card at<br>the end of this book, or send your comments to:<br>Texas Instruments Incorporated<br>Technical Publications Manager, MS 702<br>P.O. Box 1443<br>Houston, Texas 77251–1443<br>Electronic mail: comments@books.sc.ti.com |  |

# Contents

| 1 | Desci<br>(MVP                          | ribes the<br>) archite                | the Video Controller<br>video controller and its relative location within the<br>cture. Provides the memory maps for the frame tim<br>fer controller. | TMS320C80                            |

|---|----------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|   | 1.1<br>1.2                             | 1.1.1<br>1.1.2<br>The VC              | Detion of the VCVC Functional BlocksTypical ApplicationsC Memory MapFrame Timer Register MapsSRT Controller Register Maps                             | VC:1-4<br>VC:1-4<br>VC:1-5<br>VC:1-6 |

| 2 | Desci                                  |                                       | <b>iptions</b><br>e configuration, direction, and timing intervals                                                                                    | VC:2-1                               |

|   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Frame<br>Horizor<br>Vertical<br>Compo | Control Signals<br>Clock Signals<br>ntal Timing Signals<br>I Timing Signals<br>osite Timing Signals<br>ontroller Signals                              | VC:2-3<br>VC:2-4<br>VC:2-5<br>VC:2-5 |

| 3 |                                        | ribes the                             | <b>Registers</b> e registers associated with each of the frame timer ary of the Frame Timer Registers                                                 | S.                                   |

|   | 3.2                                    | Descrip                               | otion of the Frame Timer Registers                                                                                                                    | VC:3-4                               |

.

| <ul> <li>Discusses several video timing features of the video controller and how to program them.</li> <li>4.1 Understanding Horizontal and Vertical Timing</li></ul>                                                                                                                                                                                                                                                                                                                                                 | 4-1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <ul> <li>4.2 Horizontal Video Timing (Internal) VC:4-</li> <li>4.3 Vertical Video Timing (Internal) VC:4-</li> <li>4.3.1 Noninterlaced Vertical Timing VC:4-</li> <li>4.3.2 Interlaced Vertical Timing VC:4-</li> <li>4.4 Composite Video Timing VC:4-</li> <li>4.4.1 The Theory Behind Serration and Equalization Pulses VC:4-1</li> <li>4.4.2 Equalization Pulses on CSYNC VC:4-1</li> <li>4.4.3 Serration Pulses on CSYNC VC:4-1</li> <li>4.5 Noninterlaced Video Timing VC:4-1</li> </ul>                         |     |

| <ul> <li>4.2 Horizontal Video Timing (Internal)</li> <li>4.3 Vertical Video Timing (Internal)</li> <li>4.3 Vertical Video Timing (Internal)</li> <li>4.3.1 Noninterlaced Vertical Timing</li> <li>4.3.2 Interlaced Vertical Timing</li> <li>4.4 Composite Video Timing</li> <li>4.4 Composite Video Timing</li> <li>4.4.1 The Theory Behind Serration and Equalization Pulses</li> <li>4.4.2 Equalization Pulses on CSYNC</li> <li>4.4.3 Serration Pulses on CSYNC</li> <li>4.5 Noninterlaced Video Timing</li> </ul> | 4-2 |

| <ul> <li>4.3 Vertical Video Timing (Internal)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| <ul> <li>4.3.2 Interlaced Vertical Timing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| <ul> <li>4.3.2 Interlaced Vertical Timing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-6 |

| <ul> <li>4.4.1 The Theory Behind Serration and Equalization Pulses . VC:4-1</li> <li>4.4.2 Equalization Pulses on CSYNC</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     |     |

| <ul> <li>4.4.1 The Theory Behind Serration and Equalization Pulses . VC:4-1</li> <li>4.4.2 Equalization Pulses on CSYNC</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     | 4-9 |

| 4.4.3       Serration Pulses on CSYNC         4.5       Noninterlaced Video Timing                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 4.5 Noninterlaced Video Timing VC:4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -12 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -13 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 4.5.2 Noninterlaced Horizontal Timing Operation VC:4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -17 |

| 4.5.3 Noninterlaced Vertical Timing Operation VC:4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -19 |

| 4.5.4 Summary for Programming Noninterlaced                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Video Timing VC:4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 4.6 Interlaced Video Timing VC:4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

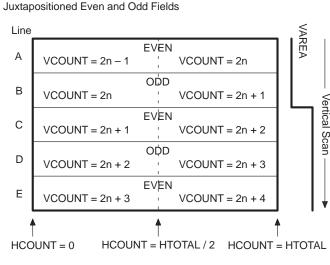

| 4.6.1 Understanding Interlaced Mode VC:4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 4.6.2 Interlaced Horizontal Timing Operation VC:4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 4.6.3 Interlaced Vertical Timing Operation VC:4-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 4.6.4 Summary for Programming Interlaced Video Timing VC:4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -32 |

| 4.7 Programming VSAREA, VEAREA, and VFTINT in                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ~~  |

| Interlaced Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 4.7.1 Vertical Start Area Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 4.7.2 Vertical End Area Programming VC:4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 4.7.3 Vertical Frame Timer Interrupt Programming VC:4-3                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .39 |

| 4.7.4 Alternative Programming for VFTINT, VSAREA,<br>and VEAREAVC:4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -42 |

| 4.8 External Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 4.8.1 Video Counter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 4.8.2 External Synchronization Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 4.8.3 Sync Output Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 4.8.4 Synchronizing to FCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 4.9 Synchronization Delay Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 4.10 High-Impedance Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 4.11 Frame Lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 5 | Descr<br>of the                                                     | I Register Transfer Controller                                                                                                                                                                                                                                                                                                                     | ng                                                                                                                         |

|---|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                       | Understanding the SRT ControllerV0SRT Controller RegistersV0SRT Control MasksVCSRT EventsVC5.4.1Start of Field EventVC5.4.2End of Field EventVC5.4.3Line EventVC5.4.4SAM Overflow EventVC5.4.5VC-Initiated Packet Transfer RequestsVCEvent PrioritizationVCAddress GenerationVC5.7.1Display ModeVC5.7.2Capture ModeVC5.7.4Interlaced Line RepeatVC | C:5-3<br>:5-16<br>:5-17<br>:5-18<br>:5-19<br>:5-20<br>:5-22<br>:5-23<br>:5-23<br>:5-25<br>:5-27<br>:5-27<br>:5-29<br>:5-31 |

| Α | Descr                                                               | ramming Procedures and Examples                                                                                                                                                                                                                                                                                                                    | er                                                                                                                         |

|   | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8<br>A.9<br>A.10 | Relationship Between Horizontal and Vertical Timing Signals VC                                                                                                                                                                                                                                                                                     | 2: A-4<br>2: A-5<br>2: A-6<br>2: A-7<br>2: A-7<br>2: A-7<br>2: A-10<br>2: A-12<br>2: A-13<br>2: A-16                       |

| В |                                                                     | sary                                                                                                                                                                                                                                                                                                                                               | :B-1                                                                                                                       |

# Figures

| 1–1  | MVP Block Diagram                                       | VC:1-2  |

|------|---------------------------------------------------------|---------|

| 1–2  | VC Block Diagram                                        | VC:1-3  |

| 1–3  | VC Memory Map                                           | VC:1-5  |

| 1–4  | Frame Timer 0 Register Map                              | VC:1-6  |

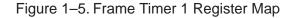

| 1–5  | Frame Timer 1 Register Map                              | VC:1-6  |

| 1–6  | 32-Bit Frame Timer Register Access                      | VC:1-7  |

| 1–7  | SRT Controller Register Map                             | VC:1-8  |

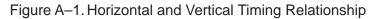

| 4–1  | Horizontal and Vertical Timing Relationship             |         |

| 4–2  | Horizontal Timing Signals                               |         |

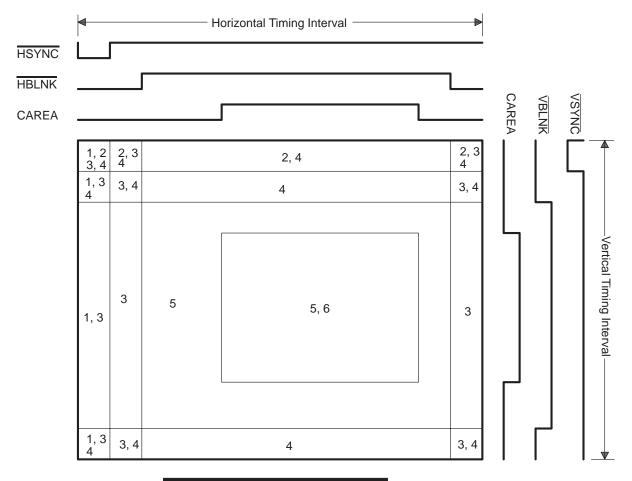

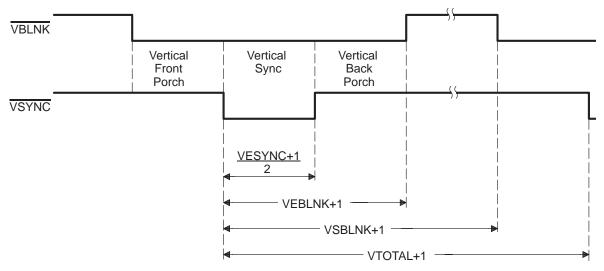

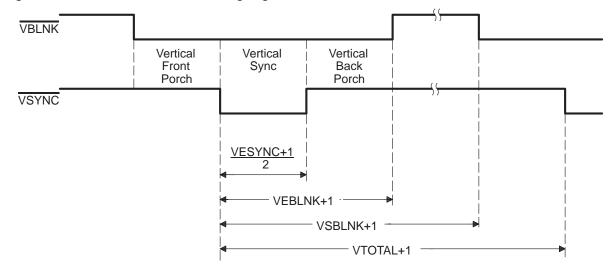

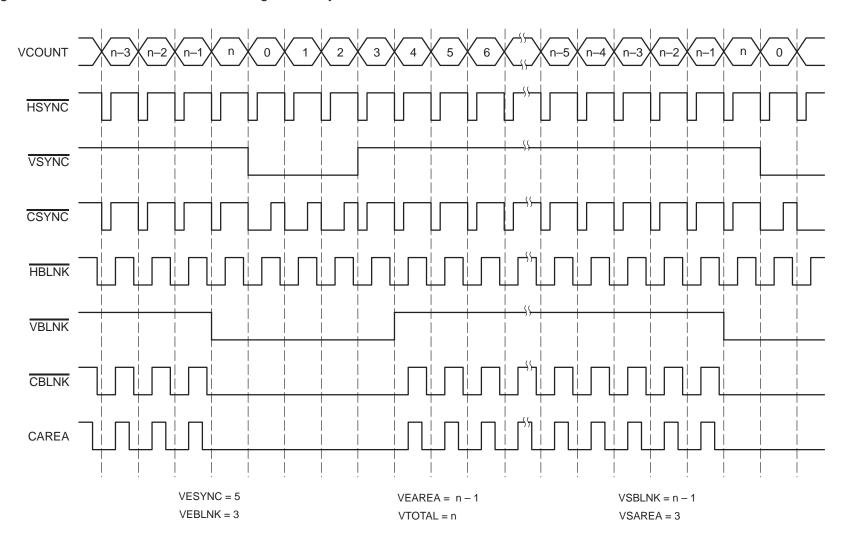

| 4–3  | Noninterlaced Vertical Timing Signals                   | VC:4-6  |

| 4–4  | Interlaced Vertical Timing Signals                      |         |

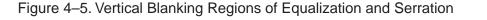

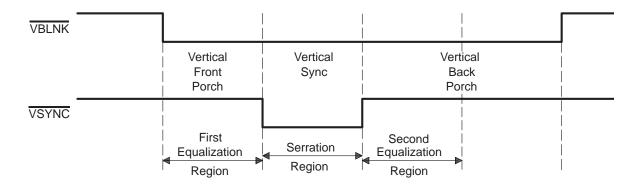

| 4–5  | Vertical Blanking Regions of Equalization and Serration |         |

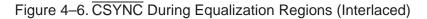

| 4–6  | CSYNC During Equalization Regions (Interlaced)          | VC:4-12 |

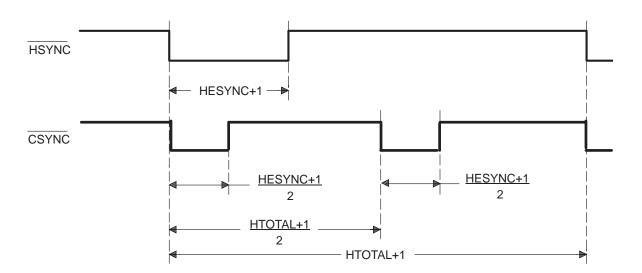

| 4–7  | CSYNC During Serration Region (Interlaced)              | VC:4-13 |

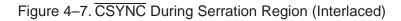

| 4–8  | CSYNC During Serration Region (Noninterlaced)           | VC:4-14 |

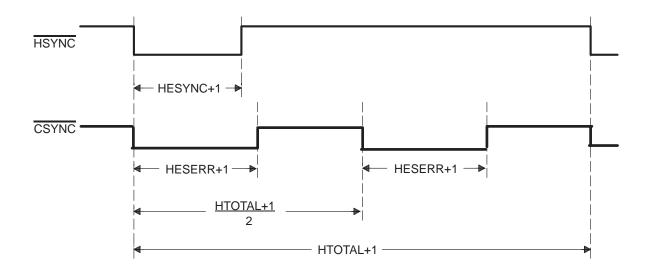

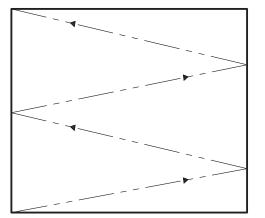

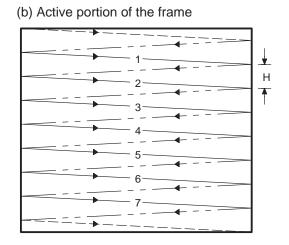

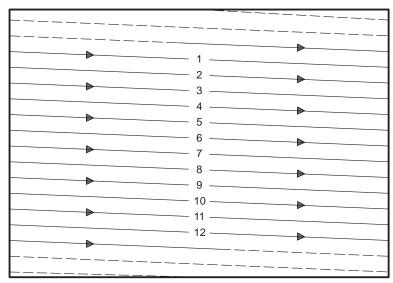

| 4–9  | Scan Pattern for Noninterlaced Monitors                 | VC:4-15 |

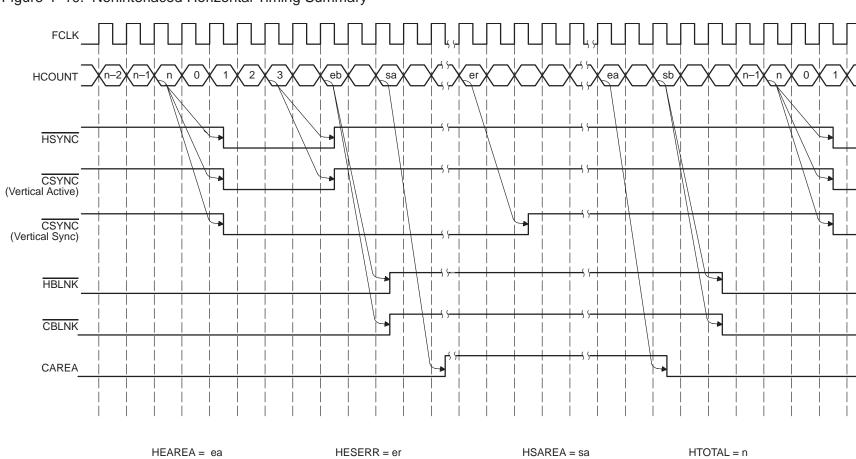

| 4–10 | Noninterlaced Horizontal Timing Summary                 | VC:4-18 |

| 4–11 | Noninterlaced Vertical Timing Summary                   | VC:4-20 |

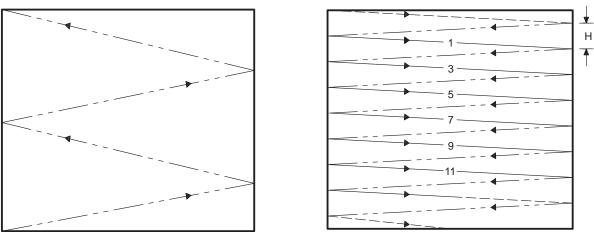

| 4–12 | Scan Pattern for Interlaced Monitors—Odd Field          | VC:4-22 |

| 4–13 | Scan Pattern for Interlaced Monitors—Even Field         | VC:4-23 |

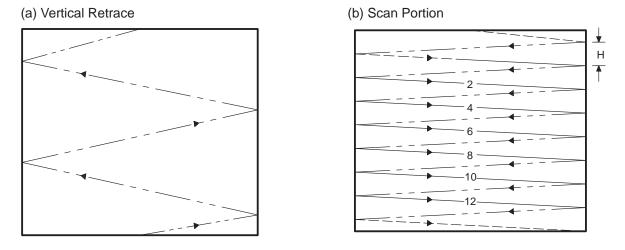

| 4–14 | Scan Pattern for Interlaced Monitors—Both Fields        | VC:4-24 |

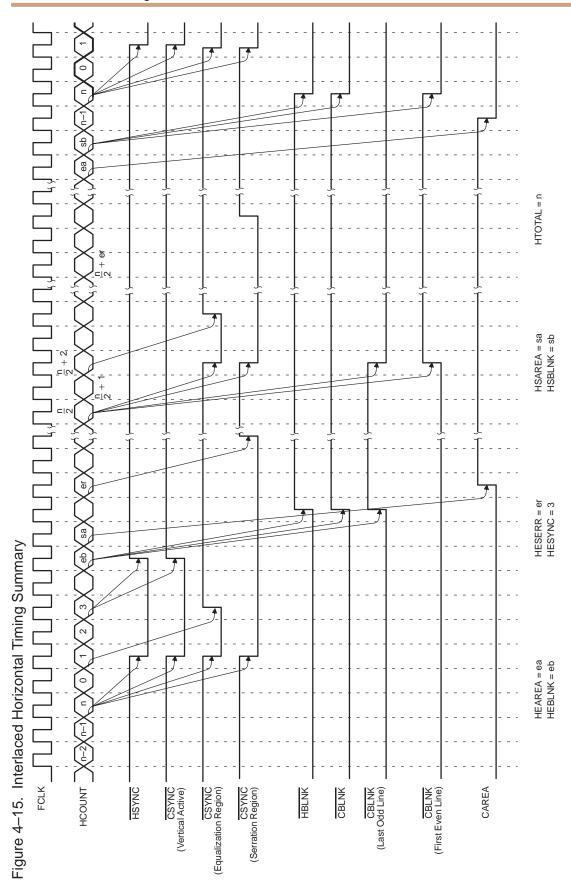

| 4–15 | Interlaced Horizontal Timing Summary                    | VC:4-26 |

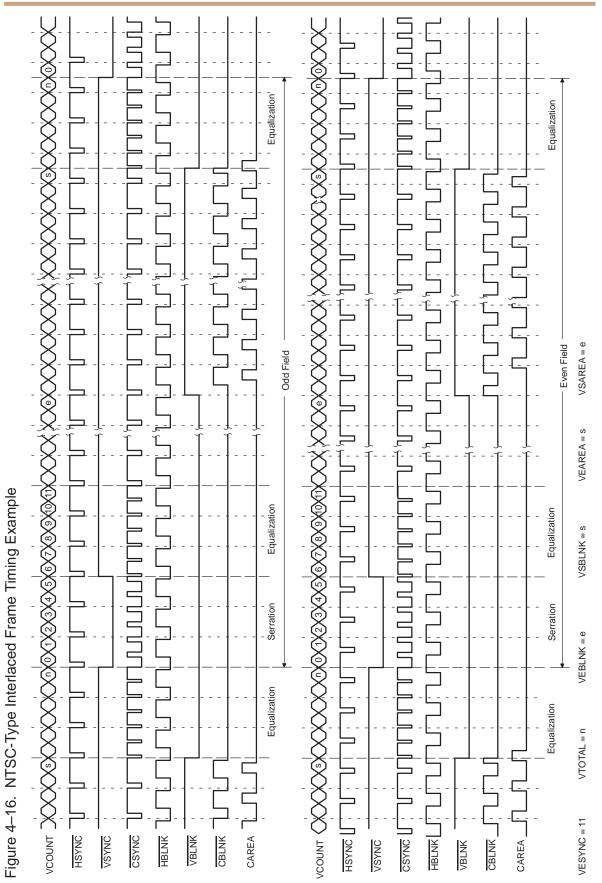

| 4–16 | NTSC-Type Interlaced Frame Timing Example               | VC:4-30 |

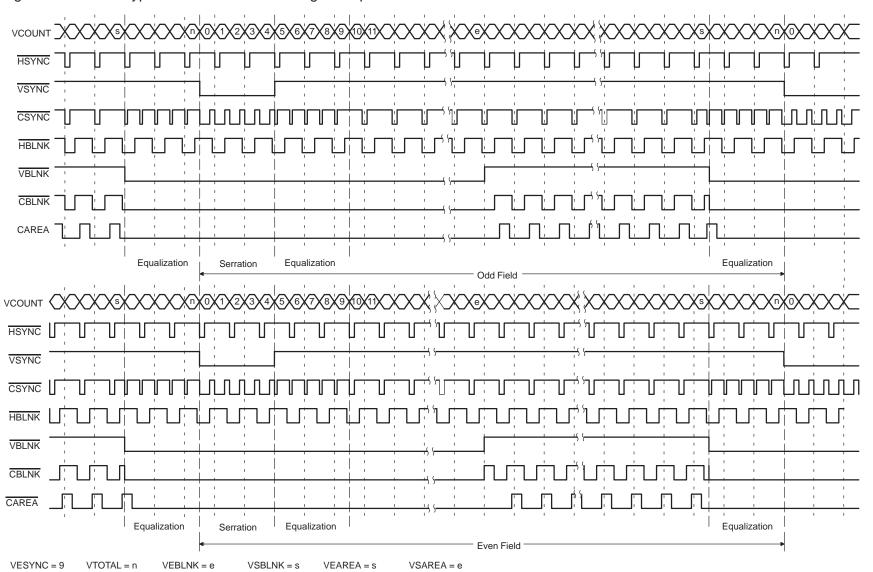

| 4–17 | PAL-Type Interlaced Frame Timing Example                | VC:4-31 |

| 4–18 | Programming VSAREA for NTSC                             | VC:4-34 |

| 4–19 | Programming VSAREA for PAL                              | VC:4-35 |

| 4–20 | Programming VEAREA for NTSC                             | VC:4-37 |

| 4–21 | Programming VEAREA for PAL                              | VC:4-38 |

| 4–22 | Programming VFTINT for NTSC (IIM = 1)                   | VC:4-40 |

| 4–23 | Programming VFTINT for PAL (IIM = 1)                    | VC:4-41 |

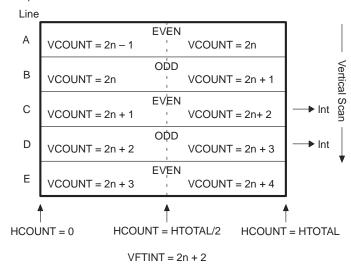

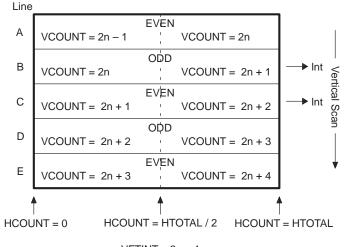

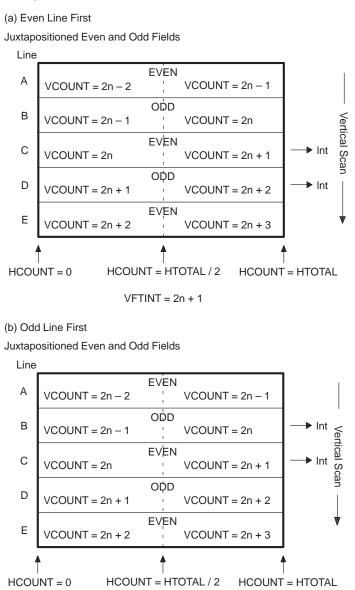

| 4–24 | Synchronization Delay Compensation                      | VC:4-50 |

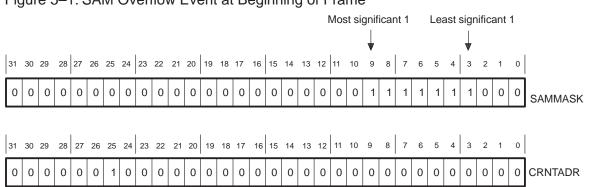

| 5–1  | SAM Overflow Event at Beginning of Frame                |         |

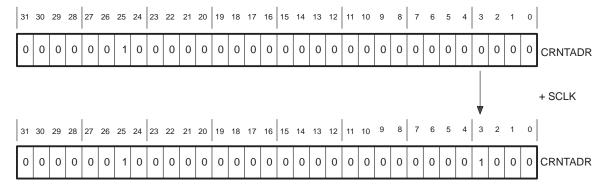

| 5–2  | SAM Overflow Event After the First SCLK Pulse           |         |

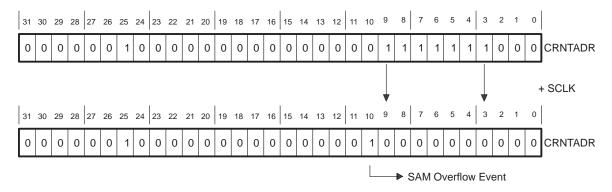

| 5–3  | SAM Overflow Event After 128th SCLK Pulse               | VC:5-21 |

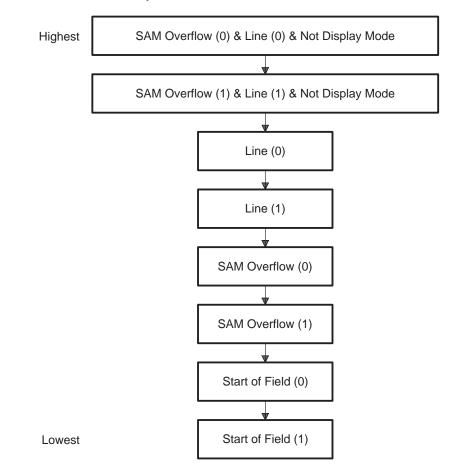

| 5–4 | SRT Event Priority VC:5-23                          |

|-----|-----------------------------------------------------|

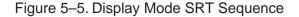

| 5–5 | Display Mode SRT Sequence VC:5-28                   |

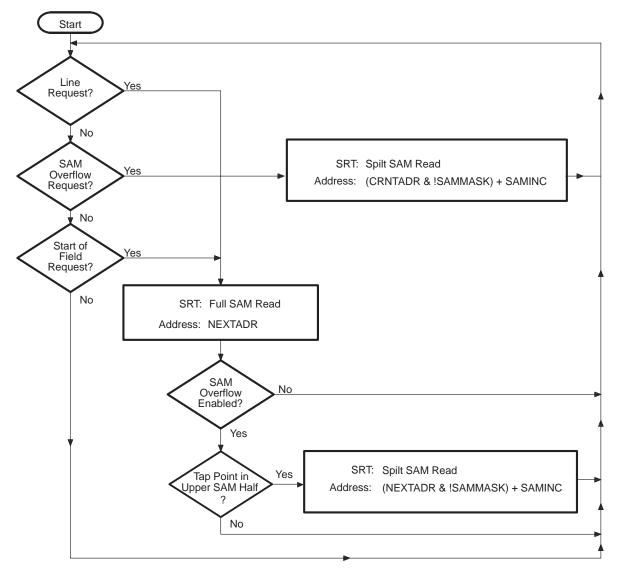

| 5–6 | Capture Mode SRT Sequence VC:5-30                   |

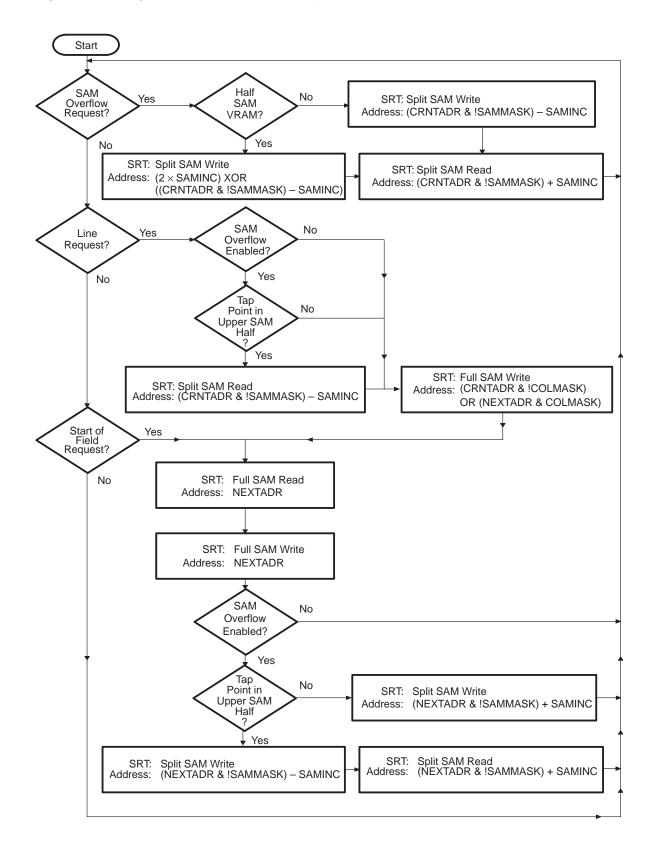

| 5–7 | Merge Capture Mode SRT Sequence VC:5-33             |

| A–1 | Horizontal and Vertical Timing Relationship VC:A-2  |

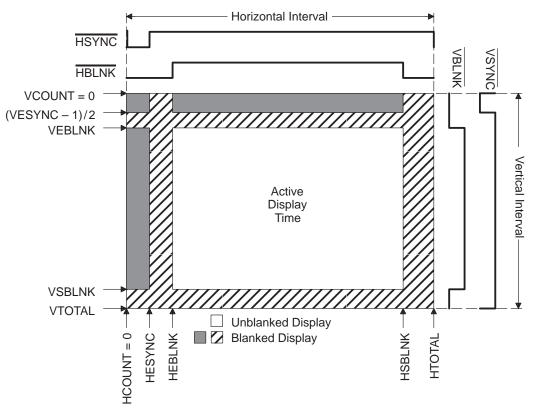

| A–2 | The Porches VC:A-3                                  |

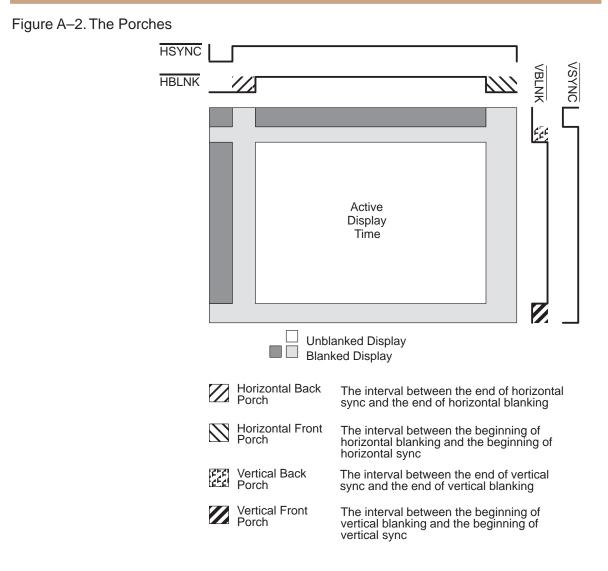

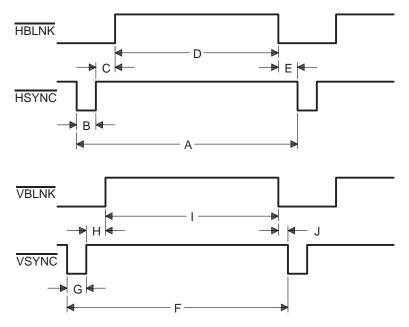

| A–3 | Noninterlaced Monitor Timing (Separate Sync) VC:A-5 |

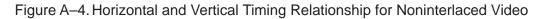

| A–4 | Horizontal and Vertical Timing Relationship for     |

|     | Noninterlaced Video VC:A-9                          |

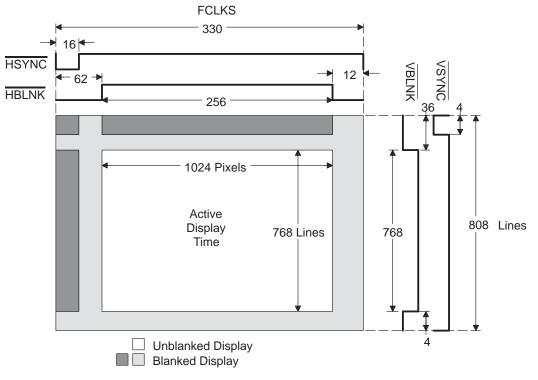

| A–5 | Interlaced Video Timing—Even Field VC:A-14          |

# **Tables**

| 2–1 | Timing Control Signals VC:2-2                                                                     |

|-----|---------------------------------------------------------------------------------------------------|

| 3–1 | Frame Timer Control Register Addresses VC:3-2                                                     |

| 3–2 | Horizontal Timing Register Addresses VC:3-2                                                       |

| 3–3 | Vertical Timing Register Addresses VC:3-3                                                         |

| 3–4 | HSYNC Pin Modes (HPM) VC:3-5                                                                      |

| 3–5 | VSYNC Pin Modes (VPM) VC:3-5                                                                      |

| 3–6 | CSYNC/HBLNK and CBLNK/VBLNK Pin Modes (CPM) VC:3-6                                                |

| 4–1 | Programming the Video Timing Registers for Noninterlaced Video . VC:4-21                          |

| 4–2 | Programming the Video Timing Registers for Interlaced Video VC:4-32                               |

| 5–1 | SRT Controller Registers VC:5-3                                                                   |

| 5–2 | Frame Timer Sequencing Modes (FTS) VC:5-9                                                         |

| 5–3 | SRT Event Modes (EMS) VC:5-10                                                                     |

| 5–4 | VCPT Event Modes (EMS) VC:5-11                                                                    |

| 5–5 | SRT Event Modes (TMS) VC:5-11                                                                     |

| 5–6 | Linked-List Start Addresses VC:5-22                                                               |

| A–1 | Typical Noninterlaced Monitor Timing VC:A-5                                                       |

| A–2 | Configuring the Values of the Frame Timer Registers for a Noninterlaced $1024 \times 768$ Display |

| A–3 | NTSC Timings VC:A-15                                                                              |

| A–4 | Configuring the Values of the Frame Timer Registers for<br>Interlaced Video VC:A-17               |

|     |                                                                                                   |

## Chapter 1

# **Overview of the Video Controller**

The video controller (VC) is an integral part of the TMS320C80 (MVP). The VC provides the video interface so that you can perform complex video and audio applications using the MVP.

This chapter describes the VC and its relative location within the MVP architecture. It also provides the memory maps for the frame timers and serial register transfer (SRT) controller.

#### Topics

| 1.1 | Description of the VC | VC:1-2 |

|-----|-----------------------|--------|

| 1.2 | The VC Memory Map     | VC:1-5 |

### **1.1 Description of the VC**

The VC portion of the MVP is responsible for the video interface. The VC provides simultaneous control over two independent frame systems. A frame system consists of an external frame buffer memory and control logic. The frame systems can function as either capture or display systems.

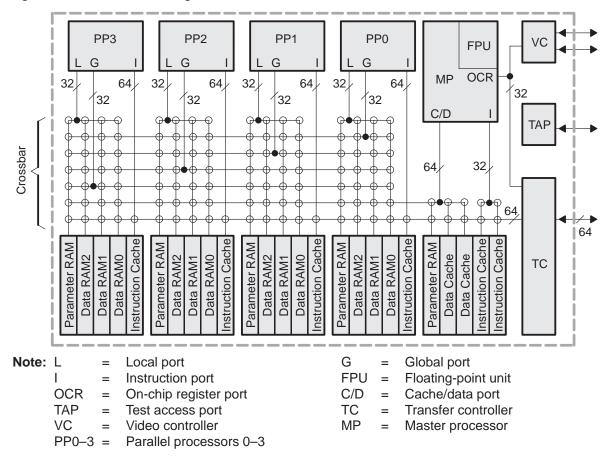

Figure 1–1 illustrates the individual processors of the MVP and the crossbar network that connects them to memory. The VC is located in the top right corner of this diagram.

Figure 1–1. MVP Block Diagram

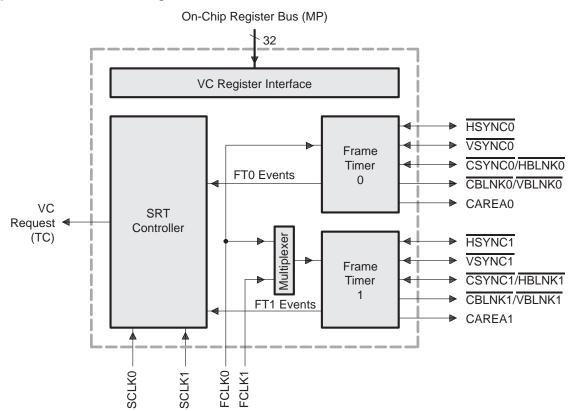

The VC can be split into functional blocks, as shown in Figure 1–2. The following subsection describes the blocks.

Figure 1–2. VC Block Diagram

#### **1.1.1 VC Functional Blocks**

Following are descriptions of the VC functional blocks.

Frame timers

Two identical frame timers provide video timing control. Each timer has its own input frame clock (FCLK) and operates asynchronously with respect to the rest of MVP logic. Each frame timer can be programmed to generate timing pulses on five video signals that can control an image capture or display device. These signals provide:

- Separate or composite synchronization and blanking

- Synchronization to internal or external signals

- Interlaced or noninterlaced frame control

- Limitless screen resolutions

#### Serial register transfer (SRT) controller

An SRT controller generates SRT cycle requests to the transfer controller (TC) to transfer data into and out of VRAM frame memories. The frame timers indicate to the SRT controller when an SRT is necessary, and the SRT controller generates the required addresses and synchronizes and prioritizes the requests before passing them on to the TC. The SRT controller may also generate packet transfer requests in place of SRT requests.

UC register interface

The VC register interface provides access to the VC registers via the master processor's (MP) 32-bit on-chip register bus.

Multiplexer

The multiplexer allows synchronization of the two frame timers to a single frame clock.

#### **1.1.2 Typical Applications**

The VC is ideal for applications such as:

- Uideo capture and display

- ☐ Image capture and display

- Printer, copier, or scanner control

## 1.2 The VC Memory Map

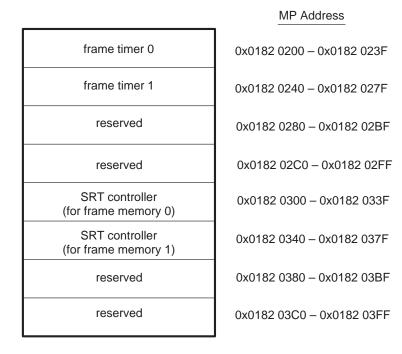

The video controller (VC) contains fourteen 32-bit and forty-two 16-bit registers. These registers are accessible to the master processor (MP) as memory-mapped registers. The on-chip memory regions for the VC registers are shown in Figure 1–3. Note that not all memory locations contain valid VC registers. The individual registers and their addresses are discussed in Chapter 3, *Frame Timer Registers*.

Figure 1–3. VC Memory Map

#### Note:

The on-chip register data bus used for accessing the VC registers is only 32 bits wide and allows for only word and halfword access. Byte (8-bit) and doubleword (64-bit) load and store instructions must not be used to access these registers.

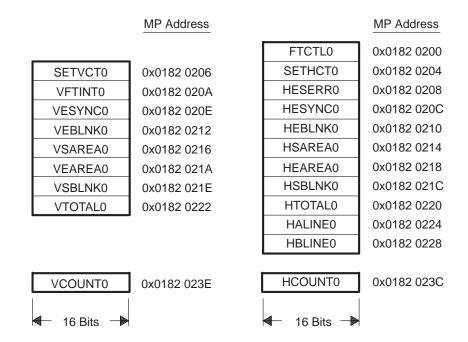

#### 1.2.1 Frame Timer Register Maps

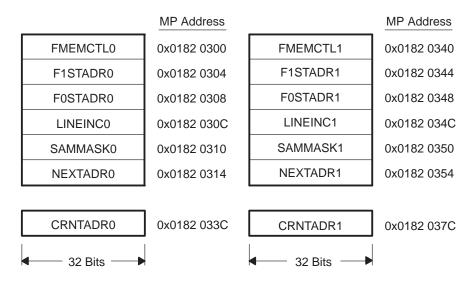

Each frame timer contains twenty-one 16-bit registers. The register addresses for frame timer 0 and frame timer 1 are shown in Figure 1–4 and Figure 1–5, respectively.

Figure 1–4. Frame Timer 0 Register Map

As Figure 1–4 and Figure 1–5 illustrate, horizontal timing registers are located at even halfword addresses. Their vertical counterparts are located at odd halfword addresses.

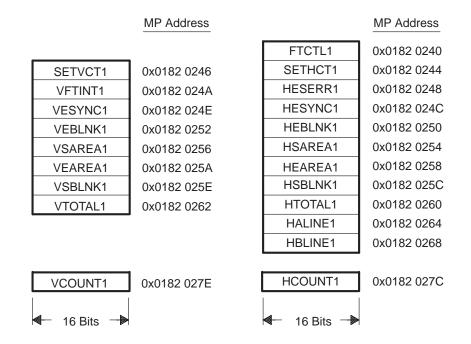

Normal procedure is to access a single horizontal or vertical timing register via a 16-bit load or store. The master processor can access the horizontal/vertical timing register pair with a single 32-bit access. The horizontal register is always represented by the 16 least significant bits (LSBs) of the word. The vertical register is always represented by the 16 most significant bits (MSBs) of the word. Since the timing registers are accessed via the MVP's on-chip register bus, the addresses are the same, regardless of the current endian mode, as shown in Figure 1–6.

#### Figure 1–6. 32-Bit Frame Timer Register Access

The following 16-bit locations return a zero value when read. Writing to these locations has no effect:

#### 1.2.2 SRT Controller Register Maps

Two sets of 32-bit registers are associated with the SRT controller—one set for each of the two supported frame memories. Figure 1–7 shows the SRT controller register maps for both frame memories. The registers and register functions for each set are identical and are described in Section 5.2, *SRT Controller Registers*.

Figure 1–7. SRT Controller Register Map

# Chapter 2

# **Signal Descriptions**

The MVP video controller (VC) timing signals provide programmable sync (separate or composite) and blanking. This chapter describes the configuration, direction, and timing intervals of each signal.

#### **Topics**

| 2.1 | Timing Control Signals    | VC:2-2 |

|-----|---------------------------|--------|

| 2.2 | Frame Clock Signals       | VC:2-3 |

| 2.3 | Horizontal Timing Signals | VC:2-4 |

| 2.4 | Vertical Timing Signals   | VC:2-5 |

| 2.5 | Composite Timing Signals  | VC:2-6 |

| 2.6 | SRT Controller Signals    | VC:2-8 |

## **2.1 Timing Control Signals**

The VC timing control signals are summarized in Table 2–1. The following sections describe each signal.

#### Table 2–1. Timing Control Signals

(a) Frame Timer 0 Signals

| Signal Name   | Direction | Description                                                            | See Page          |

|---------------|-----------|------------------------------------------------------------------------|-------------------|

| FCLK0         | Ι         | Frame clock for frame timer 0                                          | VC:2-3            |

| HSYNC0        | I/O/Hi-Z  | Horizontal sync on frame timer 0                                       | VC:2-4            |

| VSYNC0        | I/O/Hi-Z  | Vertical sync on frame timer 0                                         | VC:2-5            |

| CSYNC0/HBLNK0 | I/O/Hi-Z  | Composite sync on frame timer 0 /<br>Horizontal blank on frame timer 0 | VC:2-6/<br>VC:2-4 |

| CBLNK0/VBLNK0 | 0         | Composite blank on frame timer 0 /<br>Vertical blank on frame timer 0  | VC:2-7/<br>VC:2-5 |

| CAREA0        | 0         | Composite area on frame timer 0                                        | VC:2-6            |

(b) Frame Timer 1 Signals

| Signal Name   | Direction | Description                                                            | See Page          |

|---------------|-----------|------------------------------------------------------------------------|-------------------|

| FCLK1         | Ι         | Frame clock for frame timer 1                                          | VC:2-3            |

| HSYNC1        | I/O/Hi-Z  | Horizontal sync on frame timer 1                                       | VC:2-4            |

| VSYNC1        | I/O/Hi-Z  | Vertical sync on frame timer 1                                         | VC:2-5            |

| CSYNC1/HBLNK1 | I/O/Hi-Z  | Composite sync on frame timer 1 /<br>Horizontal blank on frame timer 1 | VC:2-6/<br>VC:2-4 |

| CBLNK1/VBLNK1 | 0         | Composite blank on frame timer 1 /<br>Vertical blank on frame timer 1  | VC:2-7/<br>VC:2-5 |

| CAREA1        | 0         | Composite area on frame timer 1                                        | VC:2-6            |

(c) Serial Register Transfer Signals

| Signal Name | Direction | Description         | See Page |

|-------------|-----------|---------------------|----------|

| SCLK0       | I         | VRAM serial clock 0 | VC:2-8   |

| SCLK1       | I         | VRAM serial clock 1 | VC:2-8   |

Note: I = input

O = output

Hi-Z = high impedance

## 2.2 Frame Clock Signals

The clock signals, FCLK0 and FCLK1, control the internal video logic for the VC's frame timers. FCLK0 and FCLK1 are derived from the dot clocks of the external video system.

The FCLK0 input clocks frame timer 0. It can also be used to clock frame timer 1 when the frame timers are synchronized. The FCLK1 input clocks frame timer 1.

## 2.3 Horizontal Timing Signals

The bidirectional horizontal timing signals control horizontal timing. CSYNC0/HBLNK0 and CSYNC1/HBLNK1 are multipurpose signals that can be used as composite sync **or** horizontal blanking signals. Following is a description of their use as horizontal blanking signals. For a description of their use as composite sync signals, refer to page VC:2-6.

#### Horizontal synchronization: HSYNC0 and HSYNC1

These signals occur once per line and have a pulse duration defined as an integral number of FCLK periods. HSYNC signals can be used to generate horizontal retrace or its equivalent for CRTs, LCDs, scanners, printers, and cameras.

You can configure  $\overrightarrow{\text{HSYNC}}$  signals for input, output, or high impedance with the  $\overrightarrow{\text{HSYNC}}$  pin mode (HPM) bits in the FTCTL register.

#### Horizontal blanking: CSYNC0/HBLNK0 and CSYNC1/HBLNK1

You configure the horizontal blanking signals via the CSYNC0/HBLNK0 pin mode (CPM) bits in the frame timer control (FTCTL) register.

When configured as HBLNK signals, these signals occur once per line and have a pulse duration defined as an integral number of FCLK periods. Horizontal blanking signals can be used to disable pixel capture or display during horizontal retrace.

In general, the HBLNK signal is used in conjunction with the VBLNK signal to determine when pixels are displayed or captured. The HBLNK signal can also be used for any timing signal that requires repetition at line intervals. When configured as HBLNK, these signals function as output only.

### 2.4 Vertical Timing Signals

The bidirectional vertical timing signals control vertical timing. CBLNK0/VBLNK0 and CBLNK1/VBLNK1 are multipurpose signals; they can be configured as composite blanking **or** vertical blanking signals. Following is a description of their use as vertical blanking signals. For information on their use as composite blanking signals, refer to page VC:2-7.

#### U Vertical synchronization: VSYNC0 and VSYNC1

These signals occur once per frame (once per field in an interlaced system) and have a pulse duration defined as an integral number of lines (halflines for interlaced). The vertical sync signals can be used to generate the vertical retrace or its equivalent for CRTs, LCDs, scanners, CCDs, and cameras.

These signals can also be used to indicate the "end of page" to a printer. In general, the vertical sync signals can be used for any timing signal that requires repetition at frame or field intervals. You can configure VSYNC for input, output, or high impedance with the  $\overline{VSYNC}$  pin mode (VPM) bits in the FTCTL register.

#### Vertical blanking: CBLNK0/VBLNK0 and CBLNK1/VBLNK1

These signals can be configured as vertical blanking signals via the CPM bits in the FTCTL register. VBLNK is always an output.

CBLNK/VBLNK signals are configured as VBLNK in conjunction with HBLNK. The VBLNK signal pulses occur once per frame (once per field in an interlaced system) and have a pulse duration defined as an integral number of lines (halflines for interlaced). CBLNK/VBLNK signals can be used to disable pixel capture/display during vertical retrace.

In general, VBLNK is used in conjunction with HBLNK to determine when pixels are displayed or captured. They are used to control both the capture/display device and the frame memory. The VBLNK signal can be used for any timing signal that requires repetition at frame intervals.

## 2.5 Composite Timing Signals

Following are descriptions of the composite timing signals. CSYNC0/HBLNK0 and CSYNC1/HBLNK1 can be configured independently as composite sync **or** horizontal blanking signals. For information on the use of CSYNC0/HBLNK0 and CSYNC1/HBLNK1 as horizontal blanking signals, refer to page VC:2-4. CBLNK0/VBLNK0 and CBLNK1/VBLNK1 can be configured as composite blanking **or** vertical blanking signals. For information on the use of CBLNK0/VBLNK0 and CBLNK1/VBLNK1 as vertical blanking signals, refer to page VC:2-5.

#### Composite area: CAREA0 and CAREA1

These signals represent the logic AND of the internal horizontal and vertical area signals. They are active (high) if both horizontal or vertical area signals are active (high).

CAREA signals provide a general-purpose region that you can use to define a special region, such as an overscan boundary. These signals behave identically in both noninterlaced and interlaced mode to define a purely rectangular region. CAREA is always an output.

# Composite sync: CSYNC0/HBLNK0 and CSYNC1/HBLNK1

You can configure the composite sync signals via the CPM bits in the FTCTL register.

The CSYNC signal combines horizontal and vertical timing information into a single signal that is more complex than either horizontal or vertical sync. The CSYNC signal is compatible with the existing standards used for image capture and display (RS-170, RS-330, RS-343, NTSC, PAL, and SECAM).

During an active frame, CSYNC looks exactly like HSYNC. However, special serration pulses are generated during the vertical sync interval, and equalization pulses are generated before and after vertical sync. Serration and equalization pulses have durations defined as an integral number of FCLK periods and occur every halfline in interlaced mode. You can configure CSYNC for input, output, or high impedance via the CPM bits in the FTCTL register.

# Composite blanking: CBLNK0/VBLNK0 and CBLNK1/VBLNK1

You can configure CBLNK0/VBLNK0 and CBLNK1/VBLNK1 using the CPM bits in the FTCTL register. When configured as CBLNK, these signals represent the composite blanking signals. CBLNK is always an output.

These signals are configured as CBLNK in conjunction with CSYNC. They represent the (negative logic) logical OR of the horizontal and vertical blanking signals. They are active (low) if either horizontal or vertical blanking signals are active (low). CBLNK can be used to disable pixel capture/display during both horizontal and vertical retrace periods.

## 2.6 SRT Controller Signals

The serial register transfer (SRT) controller signals, SCLK0 and SCLK1, are input clocks used by the SRT controller to track the VRAM tap point when using midline reload. SCLK0 should be the shift clock used by the VRAMs that make up frame memory 0. SCLK1 should be the shift clock used by the VRAMs that make up frame memory 1.

## Chapter 3

# **Frame Timer Registers**

The video controller (VC) contains two identical frame timers: frame timer 0 and frame timer 1. Each frame timer is controlled by a set of on-chip registers. This chapter describes these registers, which are listed alphabetically.

#### **Topics**

| 3.1 | Summary of the Frame Timer Registers VC:3-2     |

|-----|-------------------------------------------------|

| 3.2 | Description of the Frame Timer Registers VC:3-4 |

## 3.1 Summary of the Frame Timer Registers

The tables below list the address of each register. Table 3–1 lists the frame timer control registers. Table 3–2 lists the horizontal timing registers, which control the timing of horizontal signals and horizontal components of composite signals. Table 3–3 lists the vertical timing registers, which control the timing of vertical signals and vertical components of composite signals.

| Description                  | Register | Address     | Register | Address     | See<br>Page |

|------------------------------|----------|-------------|----------|-------------|-------------|

| Frame timer control register | FTCTL0   | 0x0182 0200 | FTCTL1   | 0x0182 0240 | VC:3-4      |

#### Table 3–2. Horizontal Timing Register Addresses

| Description                             | Register | Address     | Register | Address     | See<br>Page |

|-----------------------------------------|----------|-------------|----------|-------------|-------------|

| Horizontal area line<br>event register  | HALINE0  | 0x0182 0224 | HALINE1  | 0x0182 0264 | VC:3-8      |

| Horizontal blanking line event register | HBLINE0  | 0x0182 0228 | HBLINE1  | 0x0182 0268 | VC:3-9      |

| Horizontal counter                      | HCOUNT0  | 0x0182 023C | HCOUNT1  | 0x0182 027C | VC:3-10     |

| Horizontal end area register            | HEAREA0  | 0x0182 0218 | HEAREA1  | 0x0182 0258 | VC:3-11     |

| Horizontal end blanking register        | HEBLNK0  | 0x0182 0210 | HEBLNK1  | 0x0182 0250 | VC:3-12     |

| Horizontal end serration register       | HESERR0  | 0x0182 0208 | HESERR1  | 0x0182 0248 | VC:3-13     |

| Horizontal end sync register            | HESYNC0  | 0x0182 020C | HESYNC1  | 0x0182 024C | VC:3-14     |

| Horizontal start area register          | HSAREA0  | 0x0182 0214 | HSAREA1  | 0x0182 0254 | VC:3-15     |

| Horizontal start blanking register      | HSBLNK0  | 0x0182 021C | HSBLNK1  | 0x0182 025C | VC:3-16     |

| Horizontal total register               | HTOTAL0  | 0x0182 0220 | HTOTAL1  | 0x0182 0260 | VC:3-17     |

| Set HCOUNT register                     | SETHCT0  | 0x0182 0204 | SETHCT1  | 0x0182 0244 | VC:3-18     |

#### Table 3–3. Vertical Timing Register Addresses

| Description                             | Register | Address     | Register | Address     | See<br>Page |

|-----------------------------------------|----------|-------------|----------|-------------|-------------|

| Set VCOUNT register                     | SETVCT0  | 0x0182 0206 | SETVCT1  | 0x0182 0246 | VC:3-19     |

| Vertical counter                        | VCOUNT0  | 0x0182 023E | VCOUNT1  | 0x0182 027E | VC:3-20     |

| Vertical end area register              | VEAREA0  | 0x0182 021A | VEAREA1  | 0x0182 025A | VC:3-21     |

| Vertical end blanking register          | VEBLNK0  | 0x0182 0212 | VEBLNK1  | 0x0182 0252 | VC:3-22     |

| Vertical end sync register              | VESYNC0  | 0x0182 020E | VESYNC1  | 0x0182 024E | VC:3-23     |

| Vertical frame timer interrupt register | VFTINT0  | 0x0182 020A | VFTINT1  | 0x0182 024A | VC:3-24     |

| Vertical start area register            | VSAREA0  | 0x0182 0216 | VSAREA1  | 0x0182 0256 | VC:3-25     |

| Vertical start blanking register        | VSBLNK0  | 0x0182 021E | VSBLNK1  | 0x0182 025E | VC:3-26     |

| Vertical total register                 | VTOTAL0  | 0x0182 0222 | VTOTAL1  | 0x0182 0262 | VC:3-27     |

## 3.2 Description of the Frame Timer Registers

This section contains an alphabetical list and description of the registers for frame timers 0 and 1.

| Name      | Frame Timer Control Register: FTCTL0/FTCTL1 |

|-----------|---------------------------------------------|

| Addresses | FTCTL0: 0x0182 0200<br>FTCTL1: 0x0182 0240  |

#### Format

| 15  | 14  | 13  | 12 | 11 | 10 | 9   | 8   | 7 | 6 | 5  | 4  | 3 | 2  | 1  | 0  |

|-----|-----|-----|----|----|----|-----|-----|---|---|----|----|---|----|----|----|

| FTE | IFD | IIM |    |    |    | SSE | FLE |   |   | CF | PM | V | PM | HF | PM |

#### Fields

| Bits | Name | Function                  |

|------|------|---------------------------|

| 1–0  | HPM  | HSYNC pin mode            |

| 3–2  | VPM  | VSYNC pin mode            |

| 5–4  | CPM  | CSYNC/HBLNK pin mode      |

| 8    | FLE  | Frame lock enable         |

| 9    | SSE  | Set sync enable           |

| 13   | IIM  | Interlaced interrupt mode |

| 14   | IFD  | Interlaced frame disable  |

| 15   | FTE  | Frame timer enable        |

**Description** The frame timer control (FTCTL) register contains the mode bits that determine the frame timer's behavior. Upon reset, the FTCTL register defaults to all 0s.

**HPM** (HSYNC pin mode)

Bits 1 and 0 of the FTCTL register determine whether the HSYNC pin is configured as:

- High impedance

- Input that can lock the frame timer to an external timing source

- Output that can control an external device

Table 3–4 shows the values for these bits.

#### Table 3–4. HSYNC Pin Modes (HPM)

| Bi | its |                      |

|----|-----|----------------------|

| 1  | 0   | HSYNC configured as: |

| 0  | 0   | High impedance       |

| 0  | 1   | Input                |

| 1  | 0   | Output               |

| 1  | 1   | Reserved             |

#### □ VPM (VSYNC pin mode)

Bits 3 and 2 of the FTCTL register determine whether the VSYNC pin is configured as:

- High impedance

- Input that can lock the frame timer to an external timing source

- Output that can control an external device

Table 3–5 shows the values for these bits.

| Table 3–5. | <b>VSYNC</b> | Pin Modes | (VPM) |

|------------|--------------|-----------|-------|

|------------|--------------|-----------|-------|

| Bits |   |                      |

|------|---|----------------------|

| 3    | 2 | VSYNC configured as: |

| 0    | 0 | High impedance       |

| 0    | 1 | Input                |

| 1    | 0 | Output               |

| 1    | 1 | Reserved             |

|      |   |                      |

#### **CPM** (CSYNC/HBLNK pin mode)

Bits 5 and 4 of the FTCTL register determine whether the  $\overline{\text{CSYNC}}/\overline{\text{HBLNK}}$  pin is configured as:

- CSYNC high impedance

- CSYNC input

- CSYNC output

- HBLNK output

These bits also determine whether  $\overline{\text{CBLNK}}/\overline{\text{VBLNK}}$  is configured as:

- CBLNK output

- VBLNK output

Table 3–6 shows the values for these bits.

Table 3–6. CSYNC/HBLNK and CBLNK/VBLNK Pin Modes (CPM)

| Bi | ts | CSYNC/HBLNK            | CBLNK/VBLNK    |  |  |  |  |

|----|----|------------------------|----------------|--|--|--|--|

| 5  | 4  | configured as:         | configured as: |  |  |  |  |

| 0  | 0  | CSYNC — High impedance | CBLNK — Output |  |  |  |  |

| 0  | 1  | CSYNC — Input          | CBLNK — Output |  |  |  |  |

| 1  | 0  | CSYNC — Output         | CBLNK — Output |  |  |  |  |

| 1  | 1  | HBLNK — Output         | VBLNK — Output |  |  |  |  |

**FLE** (frame lock enable)

Bit 8 (FLE) is valid for the FTCTL1 register only. Setting FLE in the FTCTL0 register has no effect.

To lock the frame timers together (synchronized), set FLE to 1. When frame lock is enabled, frame timer 1 is clocked by FCLK0. See Section 4.11, *Frame Lock*.

When frame lock is disabled (FLE = 0), frame timer 1 is clocked by FCLK1 independently of frame timer 0.

#### **SSE** (set synchronization enable)

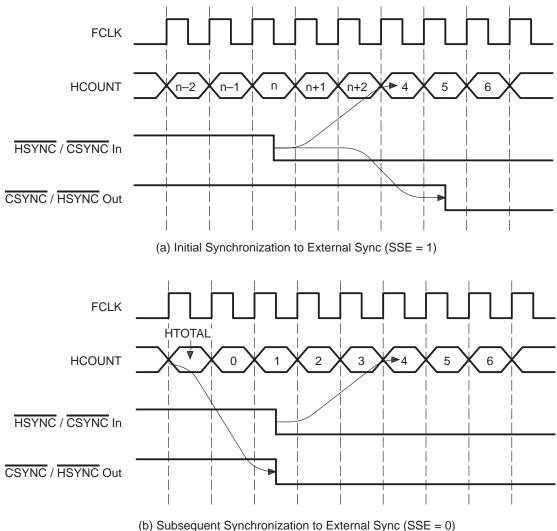

Bit 9 (SSE) of the FTCTL register determines how the frame timers operate when they are synchronizing to an external source.

When SSE is set to 0, external synchronization pulses do **not** cause the corresponding horizontal or vertical sync output to be activated. This allows precise synchronization to the external source via the SETHCT and/or SETVCT registers.

Setting SSE to 1 enables external synchronization pulses to activate the corresponding sync output. This mode can be used when only a crude synchronization is required. See subsection 4.8.3, *Sync Output Operation*.

SSE has no effect on internal synchronization operation.

**IIM** (interlaced interrupt mode)

Bit 13 (IIM) of the FTCTL register selects between field and frame interrupt mode **when the frame timer is in interlaced mode**. When IIM is 0, frame interrupt mode is selected, and a frame timer interrupt is generated only once per frame.

Setting bit IIM to 1 selects field interrupt mode, and a frame timer interrupt will be generated **twice** per frame (once in each field). See subsection 4.7.3, *Vertical Frame Timer Interrupt Programming* and Figure 4–22, *Programming VFTINT for NTSC (IIM = 1)*, on page VC:4-40.

IFD (interlaced frame disable)

Bit 14 (IFD) of the FTCTL register selects interlaced or noninterlaced frame timer operation. Setting IFD to 1 selects noninterlaced operation. Setting IFD to 0 selects interlaced operation.

**FTE** (frame timer enable)

Setting bit 15 (FTE) of the FTCTL register to 1 enables image capture/display. When FTE is set to 0, blanking and area outputs are forced low. SRT events still occur, and the frame timer interrupt is still active.

#### HALINE0/HALINE1 Horizontal Area Line Event Register

| Name Horizontal Area Line Event Register: HALINE0/HALINE1 |                                              |  |  |  |  |  |  |  |

|-----------------------------------------------------------|----------------------------------------------|--|--|--|--|--|--|--|

| Addresses                                                 | HALINE0: 0x0182 0224<br>HALINE1: 0x0182 0264 |  |  |  |  |  |  |  |

| Format<br>15 14 13                                        | 12   11 10 9 8   7 6 5 4   3 2 1 0           |  |  |  |  |  |  |  |

|                                                           | HALINE                                       |  |  |  |  |  |  |  |

| Description | The horizontal area line event (HALINE) register does not affect<br>the frame timer's video timing signals. It determines when line<br>events are generated when the serial register transfer (SRT) re-<br>quest timing is controlled by <b>area</b> . You should normally program<br>the HALINE register to be equal to or slightly larger than the hori-<br>zontal end area (HEAREA) register (see page VC:5-19). |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equation    | HALINE = (the number of FCLKs from the start of horizontal sync to the active area line event) $-1$                                                                                                                                                                                                                                                                                                                 |

|             |                 |    |                                                          | Н                                            | orizon | ntal Bl | anking | Line E | vent F | Register | HBL | INE | 0/HB | LINE1 |

|-------------|-----------------|----|----------------------------------------------------------|----------------------------------------------|--------|---------|--------|--------|--------|----------|-----|-----|------|-------|

| Name        | 9               |    | Horizontal Blanking Line Event Register: HBLINE0/HBLINE1 |                                              |        |         |        |        |        |          |     |     |      |       |

| Addr        | esse            | S  |                                                          | HBLINE0: 0x0182 0228<br>HBLINE1: 0x0182 0268 |        |         |        |        |        |          |     |     |      |       |

| <b>Form</b> | <b>at</b><br>14 | 13 | 12   11                                                  | 10                                           | 9      | 8       | 7      | 6      | 5      | 4        | 3   | 2   | 1    | 0     |

|             |                 |    |                                                          |                                              |        | HBI     | LINE   |        |        |          |     |     |      |       |

| Description | The horizontal blanking line event (HBLINE) register does not af-<br>fect the frame timer's video timing signals. HBLINE determines<br>when line events are generated when the serial register transfer<br>(SRT) request timing is controlled by <b>blanking</b> . You should nor-<br>mally program the HBLINE register to be equal to or slightly larg-<br>er than the horizontal start blanking (HSBLNK) register (see page<br>VC:5-19). |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equation    | UDI INF (the number of ECI Ke from the start of berizontal                                                                                                                                                                                                                                                                                                                                                                                 |

| Equation | HBLINE = | (the number of FCLKs from the start of horizontal |

|----------|----------|---------------------------------------------------|

|          |          | sync to the end blanking line event) – 1          |

#### HCOUNT0/HCOUNT1 Horizontal Counter

| Name Horizontal Counter: HCOUNT0/HCOUNT1                              |        |    |         |    |   |     |     |   |   |       |   |   |   |

|-----------------------------------------------------------------------|--------|----|---------|----|---|-----|-----|---|---|-------|---|---|---|

| Addresses         HCOUNT0: 0x0182 023C           HCOUNT1: 0x0182 027C |        |    |         |    |   |     |     |   |   |       |   |   |   |

| Form                                                                  | Format |    |         |    |   |     |     |   |   |       |   |   |   |

| 15                                                                    | 14     | 13 | 12   11 | 10 | 9 | 8   | 7   | 6 | 5 | 4   3 | 2 | 1 | 0 |

|                                                                       |        |    |         |    |   | НСО | UNT |   |   |       |   |   |   |

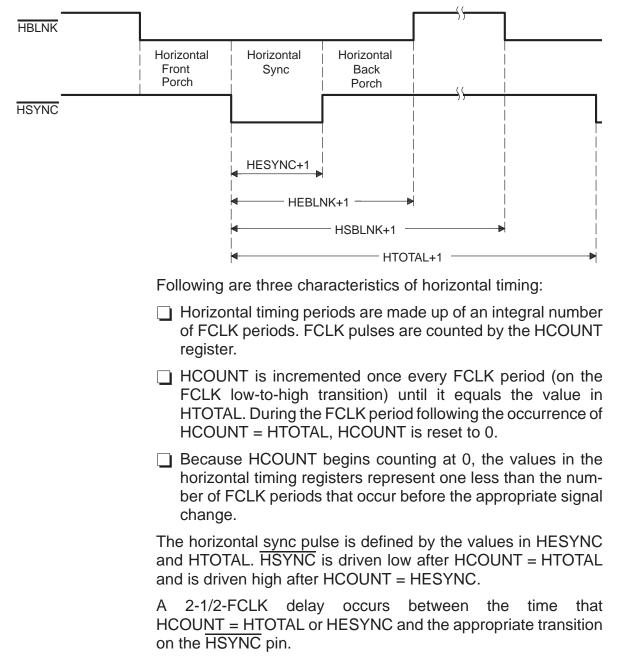

**Description** The horizontal counter (HCOUNT) is incremented by the frame clock (FCLK). HCOUNT generates horizontal timing signal transitions. When the condition HCOUNT = HTOTAL (horizontal total register) occurs, HCOUNT is reset to 0 on the next FCLK. Since HCOUNT is dynamically updated, HCOUNT cannot be reliably read while FCLK is running.

When you configure the frame timer for **interlaced compositesync** operation, equalization and serration pulses occur on the CSYNC output every halfline during the equalization and serration regions within vertical blanking (see Appendix A, *Programming Procedures and Examples*). Within these regions, the condition HCOUNT = 1/2 HTOTAL causes HCOUNT to be reset to 0 on the next FCLK.

If external sync is enabled, HCOUNT is reloaded with the value in the set horizontal count (SETHCT) register when horizontal sync occurs (HSYNC or CSYNC input is driven low).

|              |                                                    |    |         |                                              |   | Horizo | ontal I | End Are | ea Reg | gister | HEA | REA0 | /HEA | REA1 |

|--------------|----------------------------------------------------|----|---------|----------------------------------------------|---|--------|---------|---------|--------|--------|-----|------|------|------|

| Name         | lame Horizontal End Area Register: HEAREA0/HEAREA1 |    |         |                                              |   |        |         |         |        |        |     |      |      |      |

| Addres       | sse                                                | S  |         | HEAREA0: 0x0182 0218<br>HEAREA1: 0x0182 0258 |   |        |         |         |        |        |     |      |      |      |

| <b>Forma</b> |                                                    | 13 | 12   11 | 10                                           | 9 | 8      | 7       | 6       | 5      | 4      | 3   | 2    | 1    | 0    |

|              |                                                    |    |         |                                              |   | HEAR   | EA      |         |        |        |     |      |      |      |

| Description | The horizontal end area (HEAREA) register determines the end-<br>point of the horizontal component of the area signal output on<br>CAREA. When the condition HCOUNT = HEAREA occurs, the<br>horizontal component of CAREA ends on the next FCLK. For<br>more information on CAREA, see page VC:2-6. |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equation    | HEAREA = (the number of FCLKs from the start of horizontal sync to the end of horizontal area) – 1                                                                                                                                                                                                  |

| Name Horizontal End Blanking Register: HEBLNK0/HEBLNK1                |                                    |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|--|--|

| Addresses         HEBLNK0: 0x0182 0210           HEBLNK1: 0x0182 0250 |                                    |  |  |  |  |  |  |  |  |

| <b>Format</b><br>  15 14 13                                           | 12   11 10 9 8   7 6 5 4   3 2 1 0 |  |  |  |  |  |  |  |  |

| HEBLNK                                                                |                                    |  |  |  |  |  |  |  |  |

| Description | The horizontal end blanking (HEBLNK) register determines the endpoint of the horizontal blanking pulses output on the HBLNK and $\overrightarrow{CBLNK}$ pins. When the condition HCOUNT = HEBLNK occurs, the horizontal blanking pulse ends on the next FCLK. |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Equation    | HEBLNK = (the number of FCLKs from the start of horizontal sync to the end of horizontal blanking) – 1                                                                                                                                                         |

|             | Horizontal End Serration Register HESERR0/HESERR1                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Name        | Horizontal End Serration Register: HESERR0/HESERR1                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| Addresses   | HESERR0: 0x0182 0208<br>HESERR1: 0x0182 0248                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Format      |                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 15 14 13 12 | 11 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|             | HESERR                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

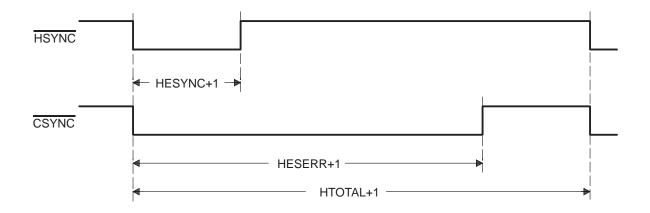

| Description | The horizontal end serration (HESERR) register determines the endpoint of the serration pulses output on the CSYNC signal during the serration period (active vertical sync). When the condition HCOUNT = HESERR occurs, the serration pulse ends on the next FCLK. |  |  |  |  |  |  |  |  |  |

|             | Note:                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|             | Serration timing is applicable only when you configure the frame timer for composite mode. HESERR can be left unpro-<br>grammed otherwise (see Appendix A, <i>Programming Proce-</i><br><i>dures and Examples</i> ).                                                |  |  |  |  |  |  |  |  |  |

| Equation    | HESERR = (the number of FCLKs from the start of horizontal sync to the end of serration pulse) – 1                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

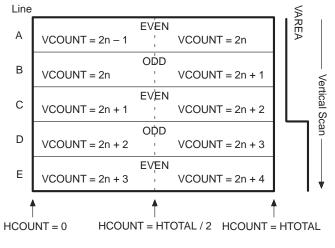

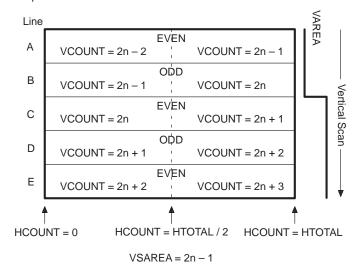

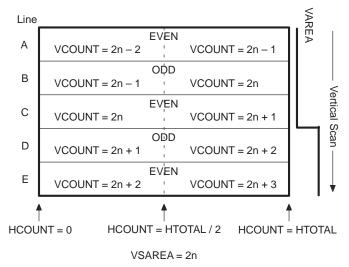

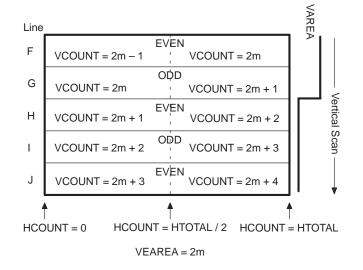

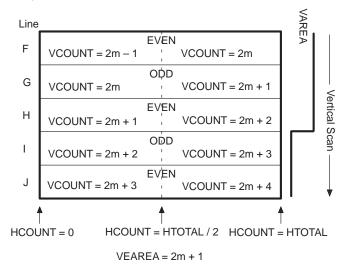

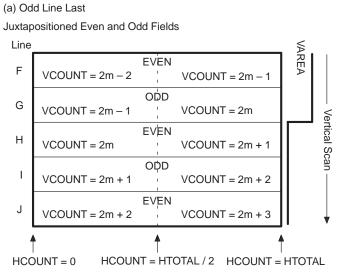

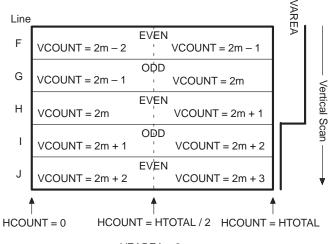

| Name Horizontal End Synchronization Register: HESYNC0/HES                                                                                                                    |  |  |  |  |  |  |  | /HES` | YNC1 |  |