# TMS320C62x DSP Expansion Bus (XBUS) Reference Guide

Literature Number: SPRU579A December 2003

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated

# Preface

# **Read This First**

#### About This Manual

This document describes the expansion bus (XBUS) used by the CPU to access off-chip peripherals, FIFOs, and peripheral component interconnect (PCI) interface devices in the TMS320C62x<sup>™</sup> digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family.

#### Notational Conventions

This document uses the following conventions.

- □ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

- Registers in this document are shown in figures and described in tables.

- Each register figure shows a rectangle divided into fields that represent the fields of the register. Each field is labeled with its bit name, its beginning and ending bit numbers above, and its read/write properties below. A legend explains the notation used for the properties.

- Reserved bits in a register figure designate a bit that is used for future device expansion.

#### **Related Documentation From Texas Instruments**

The following documents describe the C6000<sup>TM</sup> devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **TMS320C6000 CPU and Instruction Set Reference Guide** (literature number SPRU189) describes the TMS320C6000<sup>™</sup> CPU architecture, instruction set, pipeline, and interrupts for these digital signal processors.

- TMS320C6000 DSP Peripherals Overview Reference Guide (literature number SPRU190) describes the peripherals available on the TMS320C6000<sup>™</sup> DSPs.

3

- **TMS320C6000 Technical Brief** (literature number SPRU197) gives an introduction to the TMS320C62x<sup>™</sup> and TMS320C67x<sup>™</sup> DSPs, development tools, and third-party support.

- **TMS320C6000 Programmer's Guide** (literature number SPRU198) describes ways to optimize C and assembly code for the TMS320C6000<sup>™</sup> DSPs and includes application program examples.

- **TMS320C6000 Code Composer Studio Tutorial** (literature number SPRU301) introduces the Code Composer Studio<sup>™</sup> integrated development environment and software tools.

- Code Composer Studio Application Programming Interface Reference Guide (literature number SPRU321) describes the Code Composer Studio<sup>™</sup> application programming interface (API), which allows you to program custom plug-ins for Code Composer.

- **TMS320C6x Peripheral Support Library Programmer's Reference** (literature number SPRU273) describes the contents of the TMS320C6000<sup>™</sup> peripheral support library of functions and macros. It lists functions and macros both by header file and alphabetically, provides a complete description of each, and gives code examples to show how they are used.

- *TMS320C6000 Chip Support Library API Reference Guide* (literature number SPRU401) describes a set of application programming interfaces (APIs) used to configure and control the on-chip peripherals.

#### Trademarks

Code Composer Studio, C6000, C62x, C64x, C67x, TMS320C6000, TMS320C62x, TMS320C64x, TMS320C67x, and VelociTI are trademarks of Texas Instruments.

# Contents

| 1  | )verview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ٥                               |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| •  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                               |

| 2  | xpansion Bus Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                 |

| 3  | xpansion Bus I/O Port Operation       14         .1       Asynchronous Mode       11         .2       Synchronous FIFO Mode       11         .2.1       Write FIFO Interface       12         3.2.2       Read/Write FIFO Interface       12         3.2.3       Read FIFO Interface       22         3.2.4       Programming Offset Register       22         3.2.5       Flag Monitoring       22         .3       Single Frame Transfer Example       24                                                                                                                                                                                         | 7<br>9<br>0<br>1<br>2<br>2      |

|    | .4 Multiple Frame Transfer With Frame Synchronization Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                               |

| 4  | xpansion Bus Host Port Operation       20         .1       Synchronous Host Port Mode       21         4.1.1       TMS320C62x Master on the Expansion Bus       22         4.1.2       TMS320C62x Slave on the Expansion Bus       30         .2       Asynchronous Host Port Mode       44         .3       Special Circumstance of XBUS Host Memory Accesses       44                                                                                                                                                                                                                                                                             | 7<br>9<br>6<br>2                |

| 5  | xpansion Bus Arbitration44.1Internal Bus Arbiter Enabled4.2Internal Bus Arbiter Disabled4.3Expansion Bus Requestor Priority5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>8                          |

| 6  | Boot Configuration Control via Expansion Bus       52         .1       Boot and Device Configuration       52         .2       Boot Processes       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                               |

| 7  | segisters       54         .1       Expansion Bus Global Control Register (XBGC)       54         .2       Expansion Bus XCE Space Control Registers (XCECTL0-3)       64         .3       Expansion Bus Host Port Interface Control Register (XBHC)       65         .4       Expansion Bus Internal Master Address Register (XBIMA)       65         .5       Expansion Bus External Address Register (XBEA)       66         .6       Expansion Bus Data Register (XBD)       67         .7       Expansion Bus Internal Slave Address Register (XBISA)       66         .7       Expansion Bus Internal Slave Address Register (XBISA)       66 | 8<br>0<br>2<br>5<br>6<br>7<br>8 |

| пе |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                               |

5

# Figures

| 1  | Expansion Bus Block Diagram 1                                                                                                                                         | 0  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2  | TMS320C62x DSP Block Diagram 1                                                                                                                                        | 1  |

| 3  | Expansion Bus Interface to Four 8-Bit FIFOs 1                                                                                                                         | 5  |

| 4  | Expansion Bus Interface to Two 16-Bit FIFOs 1                                                                                                                         |    |

| 5  | Write FIFO Interface With Glueless Logic 1                                                                                                                            |    |

| 6  | Read and Write FIFO Interface With Glue Logic 2                                                                                                                       | 0  |

| 7  | Read and Write FIFO Interface With Glue Logic—FIFO Write Cycles                                                                                                       |    |

| 8  | Read FIFO Interface With Glueless Logic                                                                                                                               | 1  |

| 9  | Read FIFO Interface With Glueless Logic—FIFO Read Cycles                                                                                                              | 1  |

| 10 | Read FIFO Interface With Glue Logic—FIFO Read Cycles                                                                                                                  |    |

| 11 | DMA Channel Primary Control Register (PRICTL) Content for<br>Single Frame Transfer Example                                                                            |    |

| 12 | DMA Channel Primary Control Register (PRICTL) Content for<br>Multiple Frame Transfer Example                                                                          |    |

| 13 | DMA Channel Secondary Control Register (SECCTL) Content for<br>Multiple Frame Transfer Example                                                                        |    |

| 14 | Expansion Bus Host Port Interface Block Diagram 2                                                                                                                     | 6  |

| 15 | Read Transfer Initiated by the DSP and Throttled by XWAIT and XRDY Signals (Internal Bus Arbiter Disabled)                                                            | 0  |

| 16 | Write Transfer Initiated by the DSP and Throttled by XWAIT and XRDY Signals (Internal Bus Arbiter Disabled)                                                           | 2  |

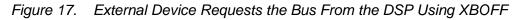

| 17 | External Device Requests the Bus From the DSP Using XBOFF                                                                                                             | 4  |

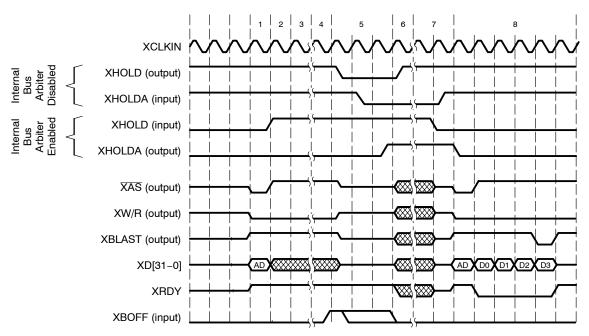

| 18 | Expansion Bus Master Writes a Burst of Data to the DSP                                                                                                                | 8  |

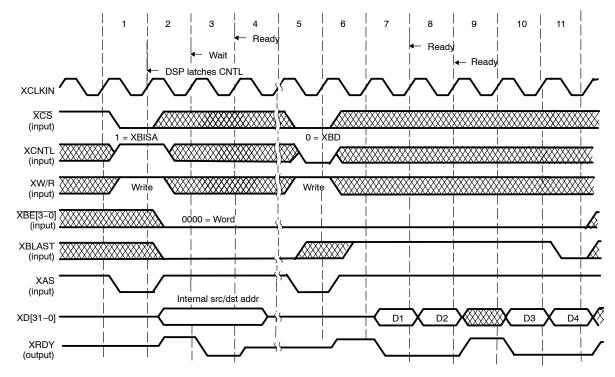

| 19 | Expansion Bus Master Reads a Burst of Data From the DSP                                                                                                               | 0  |

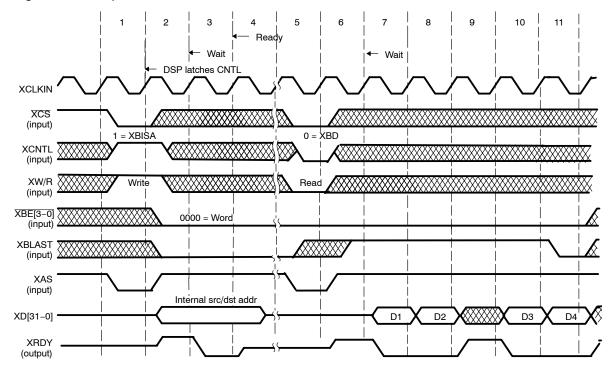

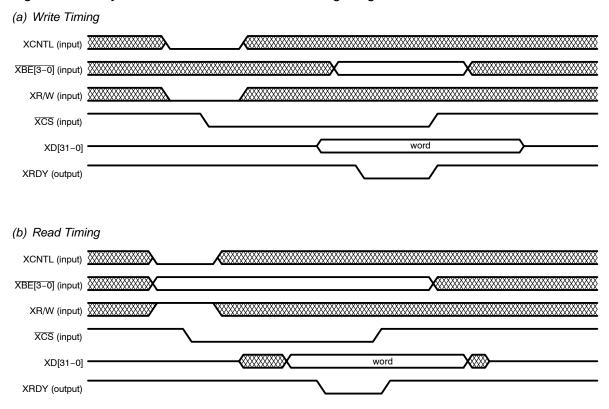

| 20 | Asynchronous Host Port Mode Timing Diagrams 4                                                                                                                         | 4  |

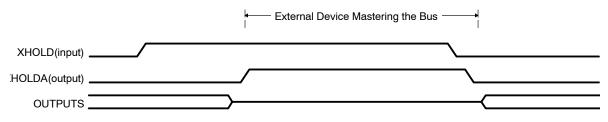

| 21 | XHOLD/XHOLDA Timing Diagram for Bus Arbitration With Internal Bus Arbiter Enabled                                                                                     | 7  |

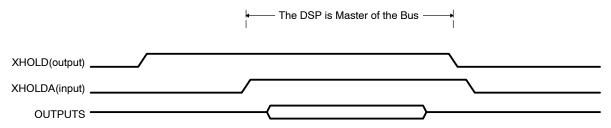

| 22 | XHOLD/XHOLDA Timing Diagram for Bus Arbitration With Internal Bus Arbiter Disabled                                                                                    | .8 |

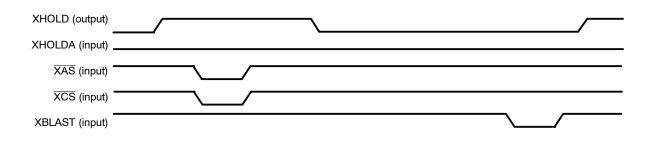

| 23 | XHOLD Timing Diagram When the External Host Starts a Transfer to the DSP Instead of Granting the DSP Access to the Expansion Bus With Internal Bus Arbiter Disabled 4 | .9 |

| 24 | Expansion Bus Global Control Register (XBGC) 5                                                                                                                        | 8  |

| 25 | Expansion Bus XCE Space Control Register (XCECTL)                                                                                                                     | 0  |

| 26 | Expansion Bus Host Port Interface Control Register (XBHC)                                                                                                             | 2  |

| 27 | Expansion Bus Internal Master Address Register (XBIMA)                                                                                                                | 5  |

| 28 | Expansion Bus External Address Register (XBEA)                                                                                                                        | 6  |

| 29 | Expansion Bus Data Register (XBD) 6                                                                                                                                   | 7  |

| 30 | Expansion Bus Internal Slave Address Register (XBISA)                                                                                                                 |    |

6 Expansion Bus (XBUS)

SPRU579A

# **Tables**

| 1  | Expansion Bus Signals                                                           | 12 |

|----|---------------------------------------------------------------------------------|----|

| 2  | Expansion Bus Signal State for Disabled Host Port                               |    |

| 3  | Addressing Scheme—Expansion Bus Interfaced to Four 8-Bit FIFOs                  | 15 |

| 4  | Addressing Scheme—Expansion Bus Interfaced to Two 16-Bit FIFOs                  | 16 |

| 5  | Signal Description—Synchronous FIFO Mode                                        | 18 |

| 6  | DMA Registers Content for Single Frame Transfer Example                         | 23 |

| 7  | DMA Registers Content for Multiple Frame Transfer Example                       | 24 |

| 8  | Signal Description—Synchronous Host Port Mode                                   | 27 |

| 9  | Signal Description—Asynchronous Host Port Mode                                  | 42 |

| 10 | XHOLD and XHOLDA Signal Functionality Based on XARB Bit Value                   | 46 |

| 11 | Possible Expansion Bus Arbitration Scenarios With Internal Bus Arbiter Disabled | 49 |

| 12 | Expansion Bus Requestor Priority                                                | 51 |

| 13 | Boot Configuration Summary                                                      | 52 |

| 14 | Boot and Device Configuration Description                                       | 54 |

| 15 | Expansion Bus Registers                                                         | 58 |

| 16 | Expansion Bus Global Control Register (XBGC) Field Descriptions                 | 59 |

| 17 | Expansion Bus XCE Space Control Register (XCECTL) Field Descriptions            | 60 |

| 18 | Expansion Bus Host Port Interface Control Register (XBHC) Field Descriptions    | 62 |

| 19 | Expansion Bus Internal Master Address Register (XBIMA) Field Descriptions       | 65 |

| 20 | Expansion Bus External Address Register (XBEA) Field Descriptions               | 66 |

| 21 | Expansion Bus Data Register (XBD) Field Descriptions                            | 67 |

| 22 | Expansion Bus Internal Slave Address Register (XBISA) Field Descriptions        | 68 |

| 23 | Document Revision History                                                       | 69 |

|    | -                                                                               |    |

7

This page is intentionally left blank.

8 Expansion Bus (XBUS)

This document describes the expansion bus (XBUS) used by the CPU to access off-chip peripherals, FIFOs, and peripheral component interconnect (PCI) interface devices in the TMS320C62x<sup>™</sup> digital signal processors (DSPs) of the TMS320C6000<sup>™</sup> DSP family.

#### 1 Overview

The expansion bus (XBUS) is a 32-bit wide bus that supports interfaces to a variety of asynchronous peripherals, asynchronous or synchronous FIFOs, PCI bridge chips, and other external masters.

The XBUS offers a flexible bus arbitration scheme, implemented with two signals, XHOLD and XHOLDA. The XBUS can operate with the internal arbiter enabled, in which case any external hosts must request the bus from the DSP. For increased flexibility, the internal arbiter can be disabled and the DSP requests the bus from an external arbiter.

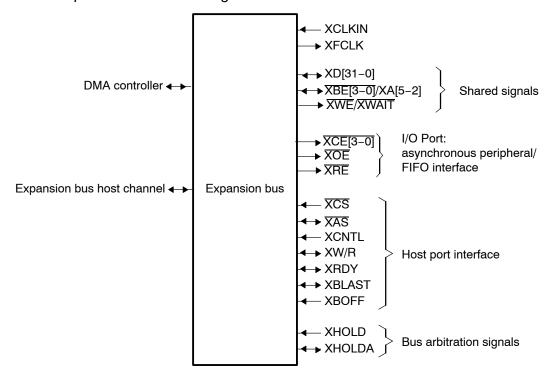

The XBUS has two major subblocks, the I/O port and host port interface. A block diagram of the XBUS is shown in Figure 1. The I/O port has two modes of operation that can coexist in a single system: asynchronous I/O mode and synchronous FIFO mode. These modes are selectable for each of the four XCE spaces in the XBUS. The asynchronous I/O mode provides output strobes that are highly programmable, like the asynchronous signals of the external memory interface (EMIF). The XBUS interface provides four output address signals in this mode, and with external decode this provides for up to 16 devices per XCE space. The FIFO mode provides a glueless interface to a single synchronous read FIFO or up to four synchronous write FIFOs. With a minimal amount of glue, this can be extended to up to 16 read and 16 write FIFOs per XCE space. Connectivity of the XBUS I/O port and DSP memory is provided through the direct-memory access (DMA) controller.

The host port interface can operate in one of two modes: synchronous and asynchronous. The synchronous mode offers master and slave functionality, and has multiplexed address and data signals. The asynchronous mode is slave only and is similar to the host-port interface (HPI) on the C6201/C6211/C6701/C6711 DSP, but is extended to a 32-bit data path. The asynchronous mode is used to interface to microprocessors that utilize an asynchronous bus.

# Figure 1. Expansion Bus Block Diagram

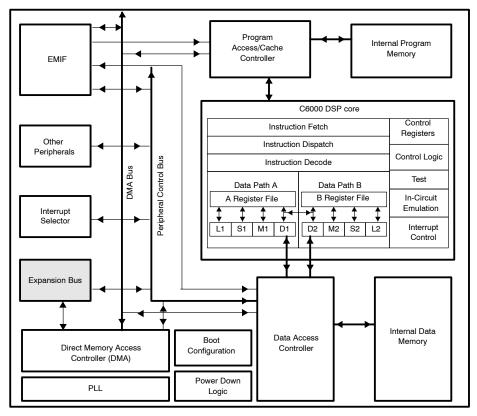

Connectivity of the XBUS host port interface and the DSP memory space is provided by the DMA auxiliary port. Dedicated address and data registers connect the host port interface to the XBUS host channel. An external master accesses these registers using external data and interface control signals. Through a dedicated port, the DMA provides connectivity between the processor and the XBUS I/O port. To initiate transfers via the synchronous host port interface, the CPU has to configure a set of registers. Figure 2 shows the XBUS interface on the C62x<sup>™</sup> DSP.

Figure 2. TMS320C62x DSP Block Diagram

Note: Refer to the specific device datasheet for its peripheral set.

# 2 Expansion Bus Signals

Table 1 lists the XBUS signals and their functionality in each mode. If only the I/O port of the XBUS is used (or if the XBUS is not used at all), the XBUS signals should be pulled inactive according to Table 2.

|                |       |               | ort Mode<br>Exclusive |                     | Mutually Exclusive<br>Host Port Modes |              |       |            |  |  |  |

|----------------|-------|---------------|-----------------------|---------------------|---------------------------------------|--------------|-------|------------|--|--|--|

| XBUS<br>Signal | I/O/Z |               |                       | Sync FIFO<br>Signal | I/O/Z                                 | Sync<br>Mode | I/O/Z | Async Mode |  |  |  |

| XD[31-0]       | I/O/Z | D[31–0]       | I/O/Z                 | D[31–0]             | I/O/Z                                 | D[31-0]      | I/O/Z | D[31–0]    |  |  |  |

| XFCLK          |       |               | 0                     | XFCLK               |                                       |              |       |            |  |  |  |

| XCLKIN         |       |               |                       |                     | I                                     | CLK          |       |            |  |  |  |

| XCE[3-0]       | 0     | <del>CS</del> | 0                     | RE/WE/CS            |                                       |              |       |            |  |  |  |

| XBE0/XA2       | O/Z   | XA2           | O/Z                   | XA2                 | I/O/Z                                 | BE0          | I     | BE0        |  |  |  |

| XBE1/XA3       | O/Z   | ХАЗ           | O/Z                   | ХАЗ                 | I/O/Z                                 | BE1          | I     | BE1        |  |  |  |

| XBE2/XA4       | O/Z   | XA4           | O/Z                   | XA4                 | I/O/Z                                 | BE2          | I     | BE2        |  |  |  |

| XBE3/XA5       | O/Z   | XA5           | O/Z                   | XA5                 | I/O/Z                                 | BE3          | I     | BE3        |  |  |  |

| XOE            | 0     | ŌĒ            | 0                     | ŌĒ                  |                                       |              |       |            |  |  |  |

| XRE            | 0     | RE            | 0                     | RE                  |                                       |              |       |            |  |  |  |

| XWE/XWAIT      | 0     | WE            | 0                     | WE                  | 0                                     | WAIT         |       |            |  |  |  |

| XAS            |       |               |                       |                     | I/O/Z                                 | AS           |       |            |  |  |  |

| XRDY           | I     | XRDY          |                       |                     | I/O/Z                                 | READY        | O/Z   | READY      |  |  |  |

| XW/R           |       |               |                       |                     | I/O/Z                                 | W/R          | I     | W/R        |  |  |  |

| XBLAST         |       |               |                       |                     | I/O/Z                                 | BLAST        |       |            |  |  |  |

| XHOLD          | I/O/Z | HOLD          | I/O/Z                 | HOLD                | I/O/Z                                 | HOLD         | I/O/Z | HOLD       |  |  |  |

| XHOLDA         | I/O/Z | HOLDA         | I/O/Z                 | HOLDA               | I/O/Z                                 | HOLDA        | I/O/Z | HOLDA      |  |  |  |

| XCNTL          |       |               |                       |                     | I                                     | CNTL         | I     | CNTL       |  |  |  |

| XBOFF          |       |               |                       |                     | I                                     | BOFF         |       |            |  |  |  |

| XCS            |       |               |                       |                     | I                                     | CS           | I     | CS         |  |  |  |

| Table 1. | Expansion E | Bus Signals |

|----------|-------------|-------------|

|----------|-------------|-------------|

12 Expansion Bus (XBUS)

| XBUS Signal         | I/O Port Mode<br>(I/O/Z) | External<br>Connection                            |

|---------------------|--------------------------|---------------------------------------------------|

| XD[31-0]            | I/O/Z                    | According to system<br>(See section 6)            |

| XFCLK               | 0                        | N/C                                               |

| XCLKIN              | I                        | Pull up                                           |

| XCE[3-0]            | 0                        | N/C                                               |

| XBE[3-0]/XA[5-2]    | O/Z                      | Pull down                                         |

| XOE                 | 0                        | N/C                                               |

| XRE                 | 0                        | N/C                                               |

| XWE                 | 0                        | N/C                                               |

| XAS                 | I/O/Z                    | Pull up                                           |

| XRDY                | I/O/Z                    | Pull up                                           |

| XW/R                | I/O/Z                    | Pull up                                           |

| XBLAST              | I/O/Z                    | Pull up, if BLPOL = 0;<br>Pull down, if BLPOL = 1 |

| XHOLD <sup>†</sup>  | I/O/Z                    | Pull down                                         |

| XHOLDA <sup>†</sup> | I/O/Z                    | Pull down                                         |

| XCNTL               | I                        | Pull up                                           |

| XBOFF               | I                        | Pull down                                         |

| XCS                 | I                        | Pull up                                           |

# Table 2. Expansion Bus Signal State for Disabled Host Port

<sup>†</sup> Internal arbitration should be enabled, such that the DSP is the master of the bus when not using the host port. See section 5 for more details.

# 3 Expansion Bus I/O Port Operation

For external I/O port accesses on the XBUS, the XBE signals act as address signals XA[5–2]. You can use the address signals to address as many as 16 different read/write peripherals or 32 FIFOs in each XCE space. For the FIFO interface, 32 devices are possible since a separate read and write FIFO can be located at each address.

Access to the XBUS I/O port can only be done through DMA channels 0–3. The DMEMC does not have direct access to the XBUS. Therefore, load and store (LD/ST) commands to the memory spaces of the XBUS I/O port via the CPU are not allowed, and result in undefined operation. A DMA transfer cannot occur from one XCE space to another XCE space. Also, a host port transaction cannot access any of the XCE spaces.

For reads, care must be taken to ensure that contention on the data bus does not occur when switching from one peripheral to the next in the same XCE space. The DMA can accomplish this since inactive cycles occur when the DMA switches from one frame to the next. The DMA can be set up to read (or write) a frame from each of the peripherals or FIFOs in turn. For example, the element index can be cleared to 0 and the frame index can be set to a multiple of 4 (ensure word strides), thus incrementing to a different location after each frame has completed.

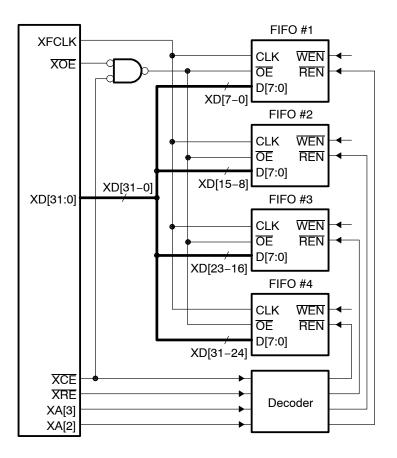

Although the XBUS does not explicitly support memory widths of less than 32 bits, the DMA can be used to read/write to 8-bit or 16-bit peripherals or FIFOs by controlling the byte/halfword logical addressing. For example, if an 8-bit-wide FIFO is in XCE2, then the DMA ESIZE bits can specify 8-bit transfers. The lower two address bits in the DMA source or destination address register determines the byte lane used for accessing the I/O port. If the bottom two bits are 00b (word aligned), then only XD[7–0] is used for valid data; if 01b, then XD[15–8] is used (see Figure 3 and Table 3).

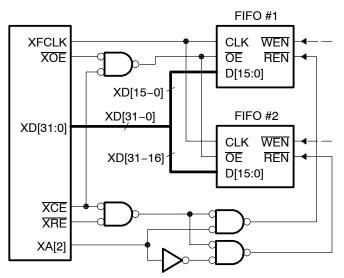

Figure 3 shows how to interface four 8-bit FIFOs to the I/O port (memory map for this case is described in Table 4). Figure 4 is an example of an interface between two 16-bit FIFOs and the I/O port.

The XOE, XRE, XWE, and XCEn signals are not tri-stated while the DSP releases control of the XBUS.

## Figure 3. Expansion Bus Interface to Four 8-Bit FIFOs

Table 3. Addressing Scheme—Expansion Bus Interfaced to Four 8-Bit FIFOs

| Logical Address  | A[31-6] | A5  | A4  | A3  | A2  | A1 | A0 |

|------------------|---------|-----|-----|-----|-----|----|----|

| FIFO #1 Address  | Х       | Х   | Х   | 0   | 0   | 0  | 0  |

| FIFO #2 Address  | Х       | х   | х   | 0   | 1   | 0  | 1  |

| FIFO #3 Address  | Х       | х   | х   | 1   | 0   | 1  | 0  |

| FIFO #4 Address  | Х       | х   | х   | 1   | 1   | 1  | 1  |

| Physical Address |         | XA5 | XA4 | ХАЗ | XA2 |    |    |

SPRU579A

Expansion Bus (XBUS)

15

Alternatively, if 16-bit (or 8-bit) peripherals are used, the DMA element index can be set up such that the stride value causes a read from alternating byte lanes during each read transfer. For example, the first access can be to address A[5-0] = xxxx00b, causing the lower half of the data bus to be driven by the peripheral. If the next address is A[5-0] = xxxx10b, the top half of the data bus is driven by the other peripheral (or FIFO) and no bus contention occurs. The only address signals that are externally provided are A[5-2]. If address decoding is required to address a specific peripheral or FIFO, these should be modified as necessary by the DMA to ensure that peripherals are only addressed when appropriate (see Figure 4 and Table 4).

#### Figure 4. Expansion Bus Interface to Two 16-Bit FIFOs

Table 4. Addressing Scheme—Expansion Bus Interfaced to Two 16-Bit FIFOs

| Logical Address  | A[31-6] | A5  | A4  | A3  | A2  | A1 | A0 |

|------------------|---------|-----|-----|-----|-----|----|----|

| FIFO #1 Address  | Х       | х   | Х   | Х   | 0   | 0  | 0  |

| FIFO #2 Address  | Х       | х   | х   | Х   | 1   | 1  | 0  |

| Physical Address |         | XA5 | XA4 | XA3 | XA2 |    |    |

## 3.1 Asynchronous Mode

The asynchronous cycles of the XBUS are identical to the asynchronous cycles provided by the EMIF. During asynchronous peripheral accesses, XRDY acts as an active-high ready input and XBE[3–0]/XA[5–2] operate as address signals XA[5–2]. The remaining asynchronous peripheral signals operate exactly like their EMIF counterparts. The following minimum values apply to the asynchronous parameters:

- $\Box \quad \text{SETUP} + \text{STROBE} + \text{HOLD} \ge 3$

- SETUP ≥ 1

- STROBE ≥ 1

- $\Box$  If XRDY is used to extend STROBE, then HOLD  $\geq$  2.

#### Notes:

- 1) XRDY is active (low) during host-port accesses.

- 2) XBE[3-0]/XA[5-2] operate as XBE[3-0] during host-port accesses.

An access to a section of memory that does not return a ready indication is not allowed. This includes accesses to XBUS I/O asynchronous spaces with XRDY pulled inactive or left floating on the device. Possible requestors are programmed DMA channels, or HPI/PCI/XBUS host mastering via the auxiliary DMA. This type of access can create a stall indefinitely.

## 3.2 Synchronous FIFO Mode

The synchronous FIFO mode of the XBUS offers a glueless and/or low glue interface to standard synchronous FIFOs. The XBUS can interface with up to four write FIFOs without using glue logic (one per XCE space) or three write FIFOs and a single read FIFO (in XCE3 only). However, with a minimal amount of glue logic, up to 16 read and write FIFOs can be used per XCE space.

Several FIFOs can be accessed in a single XCE space, if address decode logic is used to access each FIFO separately.

A description of the synchronous FIFO signals is listed in Table 5.

| Signal               |       |                                                   | Signal Fu                                                                                                                                                                                                                                                                    | nction                                                      |

|----------------------|-------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Name                 | I/O/Z | Signal Purpose                                    | Read/Write Mode                                                                                                                                                                                                                                                              | Read Mode                                                   |

| XFCLK                | 0     | FIFO clock output                                 | Programmable to either 1/2, 1/4,<br>frequency. If CPU clock = 250 MHz,<br>or 31.25 MHz. XFCLK continues<br>releases ownership of the XBUS.                                                                                                                                   | then XFCLK = 125, 62.5, 41.7,                               |

| XD[31-0]             | I/O/Z | Data                                              | Data lines                                                                                                                                                                                                                                                                   |                                                             |

| XCE[3-0]             | Ο     | FIFO read enable/<br>write enable/<br>chip select | Active for both read and write<br>transactions. They should be<br>logically ORed with output control<br>signals externally to create<br>dedicated controls for a FIFO. Also<br>can be used directly as FIFO write<br>enable signal for a single write FIFO<br>per XCE space. |                                                             |

| XWE                  | 0     | FIFO write enable                                 | Write enable signal for FIFO. Must<br>be logically ORed with<br>corresponding XCE signal to<br>ensure that only one FIFO is<br>addressed at a time.                                                                                                                          |                                                             |

| XRE                  | 0     | FIFO read enable                                  | Read enable signal for FIFO. Must<br>be logically ORed with<br>corresponding XCE signal to<br>ensure that only one FIFO is<br>addressed at a time.                                                                                                                           |                                                             |

| XOE                  | Ο     | FIFO output<br>enable                             | Shared output enable signal. Must<br>be logically ORed with<br>corresponding XCE signal to<br>ensure that only one FIFO is<br>addressed at a time.                                                                                                                           | signal in XCE3, if FIFO read mode is selected. If selected, |

| XBE[3-0]/<br>XA[5-2] | O/Z   | Expansion bus<br>address                          | Operate as XA[5–2]. Can be decoded to specify up to 16 different addresses, enabling interface with glue logic to 16 read FIFOs and 16 write FIFOs in a single XCE space.                                                                                                    |                                                             |

# Table 5. Signal Description—Synchronous FIFO Mode

# 3.2.1 Write FIFO Interface

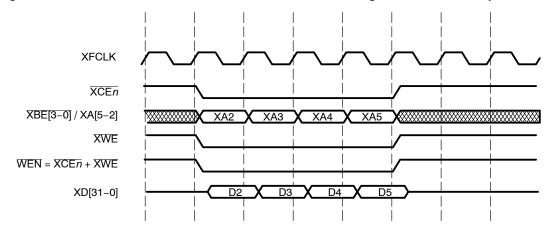

During write accesses to a memory space configured for read/write FIFO mode, the XCE signal and XWE signal are both active for a single rising edge of XFCLK. So, depending on the specific system environment, the write interface can be accomplished either with glue logic or without glue logic (glueless).

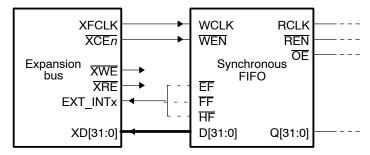

The glueless interface can be used if only a single write FIFO is used in a given XCE space (see Figure 5), since the XCE signal is used as the write enable signal. If this is true, the XCE signal is tied directly to the write enable ( $\overline{WEN}$ ) input of the FIFO. If a read FIFO is also used in the same XCE space, glue logic must be used since the XCE signal also goes low for reads from the read FIFO.

Figure 5. Write FIFO Interface With Glueless Logic

### 3.2.2 Read/Write FIFO Interface

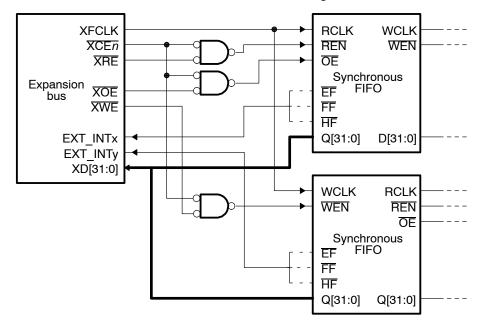

Figure 6 shows an interface to a read FIFO and a write FIFO in the same XCE space. For this example, the XCE signal is used to gate the appropriate read/write strobes to the FIFOs. The FIFO write timing diagram for this interface is shown in Figure 7.

Figure 6. Read and Write FIFO Interface With Glue Logic

Figure 7. Read and Write FIFO Interface With Glue Logic—FIFO Write Cycles

20 Expansion Bus (XBUS)

### 3.2.3 Read FIFO Interface

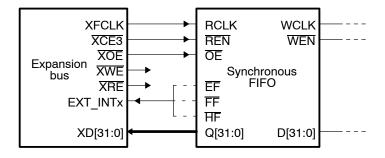

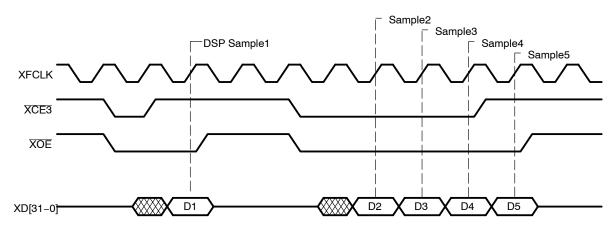

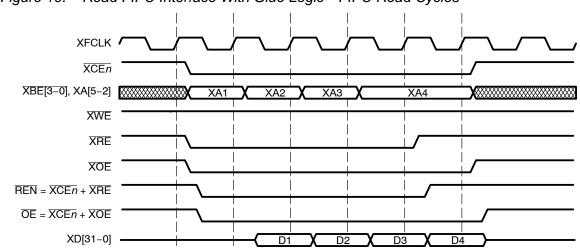

The read FIFO interface can be accomplished without glue logic (glueless) in XCE3 space or with a minimal amount of glue logic in any XCE space. If a glueless read FIFO interface is used (specified by boot configuration selection), the  $\overline{\text{XOE}}$  signal is only enabled in XCE3 space and is dedicated to use for the FIFO interface. If this mode is selected at boot, the XOE signal is disabled in all other XCE spaces. In this mode,  $\overline{\text{XCE3}}$  is used as the read enable signal (REN) and  $\overline{\text{XOE}}$  is used as the output enable signal ( $\overline{\text{OE}}$ ) of the FIFO. Figure 8 shows this interface and Figure 9 shows the read timing diagram. If the glueless read FIFO mode is not chosen, then a minimal amount of glue logic can be used in any XCE space specified as a FIFO interface. Figure 6 shows the required glue logic. Figure 10 shows the read timing diagram for the case when glue logic is used to read from FIFO.

#### Figure 8. Read FIFO Interface With Glueless Logic

Figure 9. Read FIFO Interface With Glueless Logic—FIFO Read Cycles

SPRU579A

Figure 10. Read FIFO Interface With Glue Logic—FIFO Read Cycles

#### 3.2.4 Programming Offset Register

The programmable offset registers of the FIFO are used to hold the offset values for the flags that indicate the condition of the FIFO contents. The programmable offset registers must be programmed in consecutive cycles and read in consecutive cycles. The writer should not write to the FIFO until the offset registers have been programmed. In addition, the reader should not read from the FIFO until the writer has programmed the offset registers. This should not be a problem, since the FIFO is not read until it has been written.

For programming (or reading) the offset registers, back-to-back accesses must be done. For example, the first XFCLK edge with the program input to the FIFO low, programs the PAE register; the second XFCLK edge, programs the PAF register. Also, for 9-bit or 18-bit FIFOs, it is common to require two or three write cycles to fully program each register. The first write programs the low bits, the second write programs the middle bits, and the third write programs the high bits.

A general-purpose output (DMACx or TOUTx) can be used to control whether FIFO reads/writes are done to the FIFO memory or to the programmable offset register of the memory. The XA[5–2] signals can also be decoded to control when the FIFO offset register is accessed.

#### 3.2.5 Flag Monitoring

To efficiently control bursts to and from the dedicated FIFO interfaces, the interrupt signals EXT\_INT4, EXT\_INT5, EXT\_INT6, and EXT\_INT7 are used as flags to control DMA transfers. The flag polarity used to start the transfer can be programmed in the DMA channel secondary control register (SECCTL). The CPU EXT\_INT and DMA EXT\_INT polarity is controlled separately.

## 3.3 Single Frame Transfer Example

Peripherals located on the I/O port of the XBUS are accessible only via DMA transactions. This example shows you how to transfer a single frame of 256 words from a FIFO located in XCE0 into internal data memory at 8000 0000h. This example sets up the source and destination registers, transfer counter register, and starts the DMA with an incrementing destination address (DSTDIR = 01) and a nonchanging source address (SRCDIR = 00). The source address does not change since the FIFO is located in a fixed-memory location. The content of relevant DMA registers is listed in Table 6 and the content of the DMA channel primary control register (PRICTL) is shown in Figure 11.

Table 6.

DMA Registers Content for Single Frame Transfer Example

| Register                                       | Contents                   |

|------------------------------------------------|----------------------------|

| DMA channel primary control register (PRICTL)  | 0000 0041h (see Figure 11) |

| DMA channel source address register (SRC)      | 4000 0000h                 |

| DMA channel destination address register (DST) | 8000 0000h                 |

| DMA channel transfer counter register (XFRCNT) | 0000 0100h                 |

## Figure 11. DMA Channel Primary Control Register (PRICTL) Content for Single Frame Transfer Example

| 31 |        | 30     | 29 |       | 2   | 8          | 27     |   | 26    | 2  | 25    | 24    |   |

|----|--------|--------|----|-------|-----|------------|--------|---|-------|----|-------|-------|---|

|    | 00     |        |    | 00    |     |            | 0      |   | 0     |    | 0     | 0     |   |

|    | DSTRLD | )      |    | SRCRL | D   |            | EMOD   |   | FS    | TC | INT   | PRI   |   |

|    |        |        |    |       |     |            |        |   |       |    |       |       |   |

| 23 |        |        |    | 19    | 18  |            |        |   |       | 14 | 13    | 12    |   |

|    |        | 0 0000 |    |       |     | 0 0000     |        |   |       |    | 0     | 0     |   |

|    |        | WSYNC  |    |       |     | RSYNC INDE |        |   |       |    | INDEX | CNTRI | D |

|    |        |        |    |       |     |            |        |   |       |    |       |       |   |

| 11 | 10     | 9      | 8  | 7     | 6   | 5          |        | 4 | 3     | 2  | 1     |       | 0 |

|    | 00     | 00     | )  | 0     | 1   |            | 00     |   | 00    |    |       | 01    |   |

|    | SPLIT  | ESI    | ZE | DST   | DIR |            | SRCDIR |   | STATU | S  | S     | TART  |   |

SPRU579A

Expansion Bus (XBUS) 23

# 3.4 Multiple Frame Transfer With Frame Synchronization Example

This example shows you how to transfer 10 frames of 256 words from a FIFO located in XCE0 into internal data memory at 8000 0000h. This example sets up the source and destination registers, transfer counter register, global count reload register, and starts the DMA with an incrementing destination address (DSTDIR = 01) and a nonchanging source address (SRCDIR = 00). The source address does not change since the FIFO is located in a fixed-memory location. Frame synchronization is enabled (FS = 1) and an active (high) EXT\_INT4 is used for the synchronization event (RSYNC = 0100). The content of relevant DMA registers is listed in Table 7 and the content of the DMA channel primary control register (PRICTL) and secondary control register (SECCTL) are shown in Figure 12 and Figure 13.

Table 7. DMA Registers Content for Multiple Frame Transfer Example

| Register                                        | Content                    |

|-------------------------------------------------|----------------------------|

| DMA channel primary control register (PRICTL)   | 0401 0041h (see Figure 12) |

| DMA channel secondary control register (SECCTL) | 0008 0000h (see Figure 13) |

| DMA channel source address register (SRC)       | 4000 0000h                 |

| DMA channel destination address register (DST)  | 8000 0000h                 |

| DMA channel transfer counter register (XFRCNT)  | 000A 0100h                 |

| DMA global count reload register A (GBLCNTA)    | 0000 0100h                 |

## Figure 12. DMA Channel Primary Control Register (PRICTL) Content for Multiple Frame Transfer Example

| 31 |        | 30     | 29 |       | 28  | 3 | 27     |    | 26    | 2  | 25    | 24    |    |

|----|--------|--------|----|-------|-----|---|--------|----|-------|----|-------|-------|----|

|    | 00     |        |    | 00    |     |   | 0      |    | 1     |    | 0     | 0     |    |

|    | DSTRLD | )      |    | SRCRL | D   |   | EMOD   |    | FS    | тс | INT   | PRI   |    |

| 23 |        |        |    | 19    | 18  |   |        |    |       | 14 | 13    | 12    |    |

|    |        | 0 0000 |    |       |     |   | 0 010  | 0  |       |    | 0     | 0     |    |

|    |        | WSYNC  |    |       |     |   | RSYN   | IC |       |    | INDEX | CNTR  | LD |

| 11 | 10     | 9      | 8  | 7     | 6   | 5 |        | 4  | 3     | 2  | 1     |       | 0  |

|    | 00     | 00     | )  | 0     | 1   |   | 00     |    | 00    |    |       | 01    |    |

|    | SPLIT  | ESI    | ZE | DST   | DIR |   | SRCDIR |    | STATU | S  | S     | START |    |

24 Expansion Bus (XBUS)

| 31       |                |                    |                          |                   |                |         | 24             |  |

|----------|----------------|--------------------|--------------------------|-------------------|----------------|---------|----------------|--|

|          | 0000 0000      |                    |                          |                   |                |         |                |  |

|          |                |                    | Rese                     | erved             |                |         |                |  |

| 23       | 22             | 21                 | 20                       | 19                | 18             |         | 16             |  |

| 00       |                | 0                  | 0                        | 1                 |                | 000     |                |  |

| Reser    | ved            | WSPOL <sup>†</sup> | <b>RSPOL<sup>†</sup></b> | FSIG <sup>†</sup> |                | DMACEN  |                |  |

| 15       | 14             | 13                 | 12                       | 11                | 10             | 9       | 8              |  |

| 0        | 0              | 0                  | 0                        | 0                 | 0              | 0       | 0              |  |

| WSYNCCLR | WSYNC-<br>STAT | RSYNCCLR           | RSYNC-<br>STAT           | WDROPIE           | WDROP-<br>COND | RDROPIE | RDROP-<br>COND |  |

| 7        | 6              | 5                  | 4                        | 3                 | 2              | 1       | 0              |  |

| 0        | 0              | 0                  | 0                        | 0                 | 0              | 0       | 0              |  |

| BLOCKIE  | BLOCK-<br>COND | LASTIE             | LAST-<br>COND            | FRAMEIE           | FRAME-<br>COND | SXIE    | SXCOND         |  |

# Figure 13. DMA Channel Secondary Control Register (SECCTL) Content for Multiple Frame Transfer Example

$^{\dagger}$  Available only on C6202 and C6203 devices.

# 4 Expansion Bus Host Port Operation

The XBUS host port has two modes of operation that enable interfaces to external processors, PCI bridge devices, or other external peripherals. These two operation modes are the synchronous host port mode and the asynchronous host port mode. The synchronous host port mode can interface with minimum glue logic to PCI bridge devices and many common microprocessors. The asynchronous host port mode enables interfacing to genuine asynchronous devices. The XBUS host port block diagram is shown in Figure 14.

Using pull-up/pull-down resistors on the data bus during reset sets the host port operational mode, the DSP bootmode, and endianness.

Figure 14. Expansion Bus Host Port Interface Block Diagram

## 4.1 Synchronous Host Port Mode

In this mode, the host port has address and data signals multiplexed and is i960Jx compatible. This allows a minimum glue logic interface to the PCI bus, since major PCI interface device manufacturers adopted the i960 bus for the local bus on their devices.

The synchronous host port can also easily interface to many other common processors, and essentially act in a slave only mode. This is done by not initiating transactions on the XBUS. The XBUS has the capability to initiate and receive burst transfers.

A description of the synchronous host port signals is listed in Table 8.

### Table 8. Signal Description—Synchronous Host Port Mode

| Signal<br>Name | I/O/Z | Signal<br>Purpose    | Signal Function                                                                                                                                                      |

|----------------|-------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XCLKIN         | Ι     | Clock input          | XBUS clock (maximum clock speed is 1/4 of the CPU clock speed).                                                                                                      |

| XCS            | Ι     | Chip select          | Selects the DSP as a target of an external master.                                                                                                                   |

| XHOLD          | I/O/Z | Hold request         | Case 1 (Internal bus arbiter is enabled)<br>XHOLD is asserted by external device to request use of the XBUS.<br>The DSP asserts XHOLDA when control is granted.      |

|                |       |                      | Case 2 (Internal bus arbiter is disabled)                                                                                                                            |

|                |       |                      | The DSP wakes up from reset as slave on the bus.                                                                                                                     |

|                |       |                      | XHOLD is asserted by the DSP to request use of the XBUS. The XBUS arbiter asserts XHOLDA when control is granted.                                                    |

| XHOLDA         | I/O/Z | Hold acknowledge     | Case 1 (Internal bus arbiter is disabled)                                                                                                                            |

|                |       |                      | The DSP wakes up from reset as slave on the bus.                                                                                                                     |

|                |       |                      | The XBUS arbiter asserts XHOLDA when control is granted in response to XHOLD. The bus should not be granted to the DSP unless requested by XHOLD.                    |

|                |       |                      | Case 2 (Internal bus arbiter is enabled)                                                                                                                             |

|                |       |                      | The DSP wakes up from reset as master of the bus.                                                                                                                    |

|                |       |                      | XHOLDA is asserted by the DSP when control is granted in response to XHOLD.                                                                                          |

| XD[31-0]       | I/O/Z | Address/<br>data bus | Data                                                                                                                                                                 |

| XBLAST         | I/O/Z | Burst last           | Signal driven by the current XBUS master to indicate the last transfer<br>in a bus access. Input polarity selected at boot. Output polarity is<br>always active low. |

|  | Table 8. | Signal Description—Synchronous Host Port Mode (Continued | 1) |

|--|----------|----------------------------------------------------------|----|

|--|----------|----------------------------------------------------------|----|

| Signal<br>Name | I/O/Z | Signal<br>Purpose     | Signal Function                                                                                                                                                             |

|----------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XAS            | I/O/Z | Address strobe        | Indicates a valid address and the start of a new bus access. Asserted for the first clock of a bus access.                                                                  |

| XCNTL          | I     | Control signal        | This signal selects between XBD and XBISA.                                                                                                                                  |

|                |       |                       | XCNTL = 0: access is made to the expansion bus data register (XBD).                                                                                                         |

|                |       |                       | XCNTL = 1: access is made to the expansion bus internal slave address register (XBISA).                                                                                     |

| XBE[3-0]/      | I/O/Z | Byte enables          | During host-port accesses these signals operate as $\overline{XBE[3-0]}$ .                                                                                                  |

| XA[5-2]        |       |                       | BE3 byte enable 3: XD[31–24]                                                                                                                                                |

|                |       |                       | BE2 byte enable 2: XD[23–16]                                                                                                                                                |

|                |       |                       | BE1 byte enable 1: XD[15-8]                                                                                                                                                 |

|                |       |                       | BE0 byte enable 0: XD[7-0]                                                                                                                                                  |

|                |       |                       | For XBD access (XCNTL = 0):<br>8-bit data must be byte-aligned<br>16-bit data must be halfword-aligned<br>32-bit data must be word-aligned.                                 |

|                |       |                       | For XBISA access (XCNTL = 1), all $\overline{XBE[3-0]}$ must be active low.                                                                                                 |

| XW/R           | I/O/Z | Read/write            | Read/write enable. Polarity of this signal is configured during boot.                                                                                                       |

| XRDY           | I/O/Z | Ready out<br>Ready in | Active (low) during host-port access. XRDY is an input when the DSP owns the bus. When the DSP does not own the bus, XRDY is not driven until a request is made to the DSP. |

| XBOFF          | I     | Bus back-off          | When asserted, suspends the current access and the DSP releases ownership of the XBUS.                                                                                      |

| XWAIT          | 0     | Wait                  | Ready output when the DSP initiates transfers on the XBUS.                                                                                                                  |

#### 4.1.1 TMS320C62x Master on the Expansion Bus

When the C62x DSP is the master of the XBUS, it can initiate a burst read or write to a peripheral on the bus.

When the DSP controls the bus, data flow is governed in a manner similar to a DMA transfer; however, the XBUS host channel regulates the actual data transfer. The event flow is:

- The DSP must initialize the expansion bus external address register (XBEA), which dictates where data is accessed in the external slave memory map.

- The expansion bus internal master address register (XBIMA) must be set to specify the source or destination address in the DSP memory map where the transaction starts.

- 3) The XFRCT bits of the expansion bus host port interface control register (XBHC) are set to control the number of 32-bit words being transferred.

Note: Only 32-bit transfers are supported by the XBUS when the DSP is the master in synchronous host port mode.

4) The START bits of XBHC are written, controlling whether the external access is a read or write burst.

An interrupt is generated at the completion of the transfer, if specified by the INTSRC bit in XBHC.

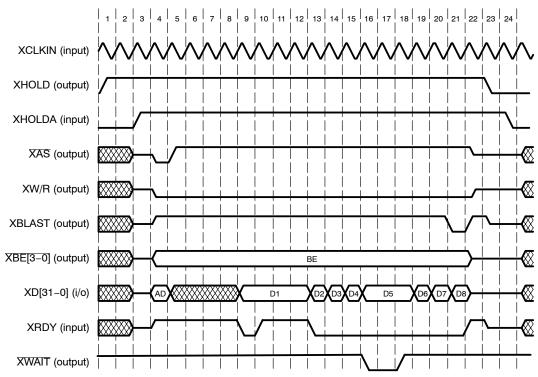

Figure 15 and Figure 16 show examples of timing diagrams for a burst read and write when the DSP is mastering the bus. In this case, internal bus arbiter is disabled (XHOLD is output and XHOLDA is input) and the DSP wakes up from reset as slave on the XBUS.

The  $\overline{XWAIT}$  signal prevents data overflow/underflow when the DSP is a master on the XBUS. The  $\overline{XWAIT}$  signal, which is multiplexed with the  $\overline{XWE}$  signal, can be thought of as a ready output when the DSP initiates transfers on the XBUS. When the DSP has initiated a transaction, the DSP indicates that it is not ready to deliver/receive new data by asserting the  $\overline{XWAIT}$  signal low.

The XWAIT signal is an output only signal in synchronous host port mode.

#### 4.1.1.1 Burst Read Transfer

The timing diagram in Figure 15 can be referenced for a visual description of the steps required to complete a burst read initiated by the DSP and throttled by the  $\overline{XWAIT}$  and XRDY signals.

Figure 15. Read Transfer Initiated by the DSP and Throttled by XWAIT and XRDY Signals (Internal Bus Arbiter Disabled)

Note: XWAIT is an output only signal in synchronous host port mode.

The step-by-step description of the events marked above the waveforms in Figure 15:

- 1) The DSP requests the XBUS by asserting XHOLD output.

- 2) The DSP waits for the XBUS.

- 3) The external bus arbiter asserts the XHOLDA signal, and the DSP starts driving the bus. The XAS, XW/R, XBLAST, XBE[3–0] signals become outputs, and the XRDY signal becomes an input.

D Expansion Bus (XBUS)

- 4) Address phase: During this phase, XAS is asserted and the address is presented on the XBUS.

- 5) Data phase: The external device is not ready to deliver data, as indicated by XRDY high.

- 6) Same as step 5.

- 7) Same as step 5.

- 8) Same as step 5.

- 9) The external device presents requested data (D1), and asserts XRDY.

- 10) The external device is not ready to deliver next data. The XRDY is negated.

- 11) Same as step 10

- 12) Same as step 10

- 13) The external device presents next data (D2), and asserts XRDY.

- 14) The external device presents next data (D3), and XRDY stays asserted.

- 15) The external device presents next data (D4), and XRDY stays asserted.

- 16) The external device presents next data (D5), and XRDY stays asserted. The DSP can not accept the new data (D5), and asserts XWAIT.

- 17) The external device recognizes XWAIT, and keeps the D5 on the XBUS. The XRDY is asserted and indicates that the external device is ready waiting for the DSP to accept the data.

- 18) The DSP deasserts XWAIT, and accepts D5.

- 19) The external device presents next data (D6), and XRDY stays asserted.

- 20) The external device presents next data (D7), and XRDY stays asserted.

- 21) The external device presents the last data (D8), and the DSP asserts the XBLAST.

- 22) The recovery cycle.

- 23) The DSP negates the XBUS request (XHOLD), and turns off the outputs.

### 4.1.1.2 Burst Write Transfer

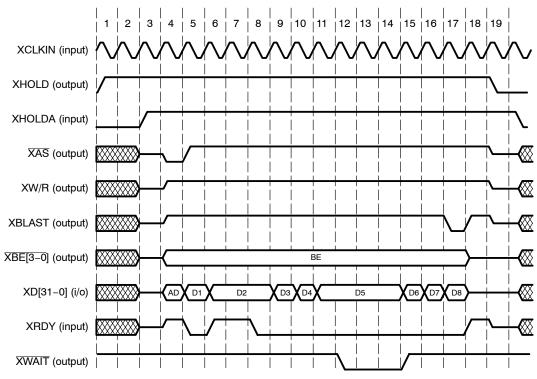

The timing diagram in Figure 16 can be referenced for a visual description of the steps required to complete a burst write initiated by the DSP and throttled by the  $\overline{XWAIT}$  and XRDY signals.

# Figure 16. Write Transfer Initiated by the DSP and Throttled by XWAIT and XRDY Signals (Internal Bus Arbiter Disabled)

Note: XWAIT is an output only signal in synchronous host port mode.

The step-by-step description of the events marked above the waveforms in Figure 16:

- 1) The DSP requests the XBUS (XHOLD asserted).

- 2) The DSP waits for the XHOLDA signal to be asserted by the external arbiter.

- The external bus arbiter asserts the XHOLDA signal, the XAS, XW/R, XBLAST, and XBE[3-0] signals become outputs, and the XRDY signal becomes an input.

32 Expansion Bus (XBUS)

- 4) Address phase: During this phase, the XAS is asserted and the address is presented on the XBUS.

- 5) Data phase: During this phase, data (D1) is presented by the DSP and the external device is ready to accept the data, which is indicated by XRDY being active.

- 6) The DSP presents next data (D2). The external device indicates not ready condition, which is indicated by XRDY being inactive.

- 7) The DSP is holding data D2 on the XBUS since the external device is still not ready.

- 8) External device finally accepts the D2.

- 9) The DSP presents next data (D3). The external device is ready to take D3.

- 10) The DSP presents next data (D4). The external device is ready to take D4.

- 11) The DSP presents next data (D5). The external device is ready to take D5.

- 12) The DSP is not ready to present D6 and asserts XWAIT. The external device is waiting for the DSP to present new data.

- 13) Same as step12.

- 14) Same as step 12.

- 15) The DSP presents next data (D6), and negates XWAIT. The external device is ready to take D6.

- 16) The DSP presents next data (D7). The external device is ready to take D7.

- 17) The DSP presents the last data (D8), and asserts XBLAST. The external device is ready to take D8.

- 18) Recovery cycle

- 19) The DSP removes the bus request (XHOLD), and is turns off the outputs.

To prevent contention on the XBUS, one recovery state between the last data transfer and next address cycle is inserted.

#### 4.1.1.3 Preventing Deadlocks with Backoff

The XBUS has the XBOFF signal to prevent deadlocks while the DSP is performing a master transfer. When asserted, XBOFF suspends the current access and causes the DSP to release ownership of the XBUS. Figure 17 is the timing diagram for the XBOFF signal.

The backoff is only recognized during active master transfers when XRDY indicates a not-ready status and one of the following conditions exists:

1) The external device is requesting the XBUS (XHOLD = 1), when the internal bus arbiter is enabled (XARB = 1).

or

2) The DSP is the XBUS master (XHOLD = 1 and XHOLDA = 1), and the internal bus arbiter is disabled (XARB = 0).

The backoff request is not serviced until all current master transfers are completed internally. This allows read data to be flushed out of the pipeline. The XBOFF signal is not recognized during I/O port transfers.

The timing diagram in Figure 17 can be referenced for a visual description of the steps involved in release of the XBUS ownership as initiated by the XBOFF signal. Figure 17 shows the backoff condition for both internal bus arbiter enabled and internal bus arbiter disabled. The step-by-step description of the events marked above the waveforms in Figure 17:

- 1) The DSP is the XBUS master and initiates address phase of a read transaction. The XAS signal is active and valid address is presented.

- The XRDY signal is high, indicating that the external device is not ready to perform the transaction. Also, the external device drives XHOLD active, indicating a bus request.

- 3) The DSP is still holding the XBUS waiting for XRDY to become low.

- 4) The external device asserts XBOFF, indicating a potential deadlock condition.

- 5) The DSP responds by releasing the XBUS. When the internal bus arbiter is enabled, the DSP asserts XHOLDA. When the internal bus arbiter is disabled the DSP deasserts XHOLD. It can take a several clock cycles before the DSP responds to XBOFF. Figure 17 shows the fastest response time, one cycle.

- 6) The XBUS ownership changes. The new master drives the XBUS. XBOFF is deasserted.

- 7) The external device releases the bus after performing the desired transactions.

- 8) The XHOLDA is removed, and the DSP resumes the XBUS ownership.

- 9) The DSP performs a burst read of four words.

The DSP automatically tries to restart the transfer interrupted by a backoff from the point where the interruption took place. The transfer restart is completely transparent.

#### 4.1.2 TMS320C62x Slave on the Expansion Bus

The external host can access the different expansion bus host port registers by driving the XCNTL signal as follows:

- □ XCNTL = 0; reads or writes the expansion bus data register (XBD).

- XCNTL = 1; reads or writes the expansion bus internal slave address register (XBISA).

Every transaction initiated by the host on the XBUS is a two-step process. First, the host has to set XBISA, and then transfer the data to/from the address pointed by XBISA. Bursts longer than one word must take place with autoincrementing of XBISA. Therefore, the AINC bit must always be cleared to 0.

Initial access made to the expansion bus in host slave mode should be done in the previous order. After reset, the first access from the host should be an XBISA write followed by an XBD read/write. Undefined operation may occur if an XBISA read or an XBD read/write occurs before an XBISA write.

To read/write from the DSP memory space, the host must follow the following sequence:

- 1) The host writes the transfer source/destination address to XBISA and clears the AINC bit.

- The host reads/writes the address specified by XBISA. Read or write is determined by the XBISA XW/R signal. XBISA is autoincremented since bit 1 of XBISA must be cleared by the external host.

- 3) If the transfer is a burst, dictated by the BLAST signal, data is continuously read or written. If a multiword burst is being done, all XBEn signals must be low, because only 32-bit word bursts are allowed. If less than 32 bits are transferred (specified by XBEn signals), then only single element transfers are allowed.

The XWAIT signal is not used in slave mode.

### 4.1.2.1 Cycle Description

Each access initiated by the external host can be broken up into distinct categories:

- ❑ Address phase (Ta): During the address phase, the DSP is selected with the XCS input and the address phase is started with a low pulse on the XAS signal. During this phase, the DSP determines if the external master is doing a read or write cycle (XW/R input) and which XBUS register is being accessed (via the XCNTL input).

- ❑ Wait/data phase (Tw/Td): Immediately after the address phase, the transaction enters either the wait phase or data phase. For a read cycle, there is at least one wait phase before the DSP presents the data to the external host. This is controlled via the XRDY output of the DSP. If the XRDY signal is high, this indicates to the external host that the DSP is not ready to receive data for a write, or is not ready to present data for a read, and is in the wait phase. The data phase is entered when the DSP asserts XRDY signal, indicating that read data should be latched by the external host or that write data has been latched by the DSP.

- Recovery phase (Tr): The recovery phase is entered after the final data phase of a burst access, or after the data phase of a single access. When the DSP is a slave, if the external master has a multiplexed address/data bus, it is recommended that the external master insert at least one recovery phase between a read data phase and a subsequent address phase in order to avoid potential bus contention.

### 4.1.2.2 Burst Write Transfer

The timing diagram in Figure 18 can be referenced for a visual description of the steps required to complete a burst write initiated by an external host and throttled by the XRDY signal.

The boot configuration for XBLAST and XW/R: BLPOL = 0 and RWPOL = 0. See Table 8 (page 27) for more details.

Figure 18. Expansion Bus Master Writes a Burst of Data to the DSP

The step-by-step description of the events marked above the waveforms in Figure 18:

- The XCS and XAS signals are low and the XCNTL signal is high, indicating XBISA as the destination for the following transaction. The XW/R is high, specifying that a write access is taking place.

- 2) The DSP begins driving the XRDY output in response to a transfer initiated by the external host. A high XRDY indicates that the DSP is not ready.

- 3) The data is written to XBISA when the DSP asserts the XRDY output low.

- The DSP inserts one or more not-ready cycles (XRDY = 1) between the address phase and the first data phase.

- 5) The XAS and XCNTL signals are low (and XCS is low), indicating XBD as the destination for the following transaction. The XW/R is high, specifying that a write access is taking place.

- 6) The DSP inserts one not-ready cycle (XRDY = 1).

- 7) The XBUS master presents the valid data. The data is written to XBD on the rising edge of the XCLKIN when XRDY is active-low.

- 8) Same as step 7.

- 9) The DSP is not ready to accept next data, which is indicated by XRDY high.

- 10) Same as step 7.

- The XBUS master indicates that the last write transaction is taking place by asserting the XBLAST signal. The data is written to XBD on the rising edge of the XCLKIN.

The XWAIT signal is not used in slave mode.

### 4.1.2.3 Burst Read Transfer

The timing diagram in Figure 19 can be referenced for a visual description of the steps required to complete a burst read initiated by an external host and throttled by the XRDY signal.

The boot configuration for XBLAST and XRW: BLPOL = 0 and RWPOL = 0. See Table 8 (page 27) for more details.

Figure 19. Expansion Bus Master Reads a Burst of Data From the DSP

The step-by-step description of the events marked above the waveforms in Figure 19:

- The XCS and XAS signals are low and the XCNTL signal is high, indicating XBISA as the destination for the following transaction. The XW/R is high, specifying that a write access is taking place.

- 2) The DSP begins driving the XRDY output in response to a transfer initiated by the external host. A high XRDY indicates that the DSP is not ready.