### TMS320VC5501/5502 DSP Host Port Interface (HPI) Reference Guide

Literature Number: SPRU620D November 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

### Preface

### **Read This First**

#### About This Manual

This manual describes the features and operation of the host port interface (HPI) that is on the TMS320VC5501 and TMS320VC5502 digital signal processors (DSPs) in the TMS320C55x<sup>TM</sup> (C55x<sup>TM</sup>) DSP generation.

#### Notational Conventions

This document uses the following conventions.

□ In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers often are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

☐ If a signal or pin is active low, it has an overbar. For example, the RESET signal is active low.

#### **Related Documentation From Texas Instruments**

The following documents describe the C55x devices and related support tools. Copies of these documents are available on the Internet at www.ti.com. *Tip:* Enter the literature number in the search box provided at www.ti.com.

- **TMS320VC5501 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS206) describes the features of the TMS320VC5501 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320VC5502 Fixed-Point Digital Signal Processor Data Manual** (literature number SPRS166) describes the features of the TMS320VC5502 fixed-point DSP and provides signal descriptions, pinouts, electrical specifications, and timings for the device.

- **TMS320C55x Technical Overview** (literature number SPRU393) introduces the TMS320C55x DSPs, the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features.

- **TMS320C55x DSP CPU Reference Guide** (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x DSPs.

- **TMS320C55x DSP Peripherals Overview Reference Guide** (literature number SPRU317) introduces the peripherals, interfaces, and related hardware that are available on TMS320C55x DSPs.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the TMS320C55x DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- **TMS320C55x DSP Mnemonic Instruction Set Reference Guide** (literature number SPRU374) describes the TMS320C55x DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x Optimizing C/C++ Compiler User's Guide** (literature number SPRU281) describes the TMS320C55x C/C++ Compiler. This C/C++ compiler accepts ISO standard C and C++ source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

- **TMS320C55x DSP Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x DSPs and explains how to write code that uses special features and instructions of the DSPs.

#### Trademarks

4

TMS320C5000, TMS320C55x, and C55x are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

Host Port Interface (HPI)

### Contents

| 1 | ntroduction to the HPI       9         1.1       Summary of the HPI Registers       1 <sup>-1</sup> 1.2       Summary of the HPI Signals       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Jsing the Address Registers (8-Bit Multiplexed Mode Only)182.1Single-HPIA Mode182.2Dual-HPIA Mode19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3 | HPI Operation       19         8.1       Host-HPI Signal Connections       19         8.2       HPI Configuration and Data Flow       20         8.3       HDS2, HDS1, and HCS: Data Strobing and Chip Selection       26         8.4       HCNTL[1:0] and HR/W: Indicating the Cycle Type       27         8.5       HBIL: Identifying the First and Second Bytes in Multiplexed-Mode Transfers       28         8.6       HAS: Forcing the HPI to Latch Control Information Early in the 8-Bit Multiplexed Mode       29         8.7       Performing a Multiplexed Access Without HAS       32         8.8       Single-Byte HPIC Cycle in the 8-Bit Multiplexed Mode       34         8.9       Host Cycles in the 16-Bit Nonmultiplexed Mode       35         8.10       Hardware Handshaking Using the HPI-Ready (HRDY) Signal       36         3.10.1       HRDY Behavior During Multiplexed-Mode Write Operations       37         3.10.2       HRDY Behavior During Nonmultiplexed-Mode Read Operations       36         3.10.3       HRDY Behavior During Nonmultiplexed-Mode Write Operations       36         3.10.4       HRDY Behavior During Nonmultiplexed-Mode Write Operations       37 |

| 4 | Software Handshaking Using the HPI Ready (HRDY) Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

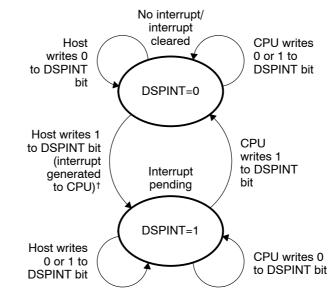

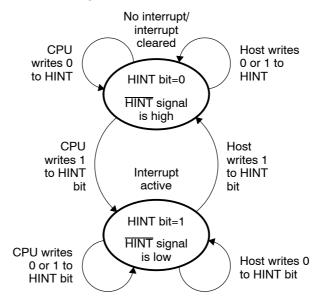

| 5 | nterrupts Between the Host and the CPU445.1DSPINT Bit: Host-to-CPU Interrupts445.2HINT Bit: CPU-to-Host Interrupts46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6 | FIFOs and Bursting (8-Bit Multiplexed Mode Only)       47         6.1       Read Bursting       48         6.2       Write Bursting       48         6.3       FIFO Flush Conditions       50         6.4       FIFO Behavior When a Hardware Reset or an HPI Software Reset Occurs       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

5

#### Contents

| 7  | Using HPI Pins for General-Purpose I/O5 |                                                                                                             |    |  |

|----|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|----|--|

| 8  | Powe                                    | r, Emulation, and Reset Considerations                                                                      | 54 |  |

|    | 8.1                                     | Conserving Power                                                                                            | 54 |  |

|    | 8.2                                     | Emulation Modes                                                                                             | 54 |  |

|    | 8.3                                     | Effects of a Hardware Reset on the HPI                                                                      | 55 |  |

|    | 8.4                                     | HPI Software Reset                                                                                          | 55 |  |

| 9  | HPI R                                   | egisters                                                                                                    | 56 |  |

|    | 9.1                                     | Control Register (HPIC)                                                                                     |    |  |

|    | 9.2                                     | Data Register (HPID)                                                                                        | 61 |  |

|    | 9.3                                     | Address Registers (HPIAR and HPIAW)                                                                         | 62 |  |

|    | 9.4                                     | General-Purpose I/O Enable Register (HGPIOEN)                                                               | 64 |  |

|    | 9.5                                     | General-Purpose I/O Direction Register 1 (HGPIODIR1) and<br>General-Purpose I/O Data Register 1 (HGPIODAT1) | 66 |  |

|    | 9.6                                     | General-Purpose I/O Direction Register 2 (HGPIODIR2) and<br>General-Purpose I/O Data Register 2 (HGPIODAT2) |    |  |

|    | 9.7                                     | General-Purpose I/O Direction Register 3 (HGPIODIR3) and<br>General-Purpose I/O Data Register 3 (HGPIODAT3) |    |  |

|    | 9.8                                     | General-Purpose I/O Interrupt Control Registers<br>(HGPIOINT1 and HGPIOINT2)                                | 73 |  |

|    | 9.9                                     | Power and Emulation Management Register (HPWREMU)                                                           |    |  |

| Re | vision                                  | History                                                                                                     | 77 |  |

# Figures

| 1       | The Position of the HPI in the Host-DSP System                                                                                               |          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2       | Example of Host-DSP Signal Connections in the 16-Bit Nonmultiplexed Mode                                                                     | 20       |

| 3       | Example of Host-DSP Signal Connections When Using the HAS Signal                                                                             |          |

|         | in the 8-Bit Multiplexed Mode                                                                                                                | 21       |

| 4       | Example of Host-DSP Signal Connections When the HAS Signal is Tied High                                                                      | ~~       |

| F       | in the 8-Bit Multiplexed Mode                                                                                                                | 22       |

| 5       | HPI Strobe and Select Logic                                                                                                                  | 20       |

| 6<br>7  | Multiplexed-Mode Host Read Cycle Using HAS         Multiplexed-Mode Host Write Cycle Using HAS                                               | 3U<br>24 |

| 8       | Multiplexed-Mode Host Read Cycle With HAS Tied High                                                                                          |          |

|         | Multiplexed-Mode Host Write Cycle With HAS Tied High                                                                                         |          |

| 9<br>10 | Multiplexed-Mode Single-Byte HPIC Cycle With HAS Tied High Read or Write)                                                                    |          |

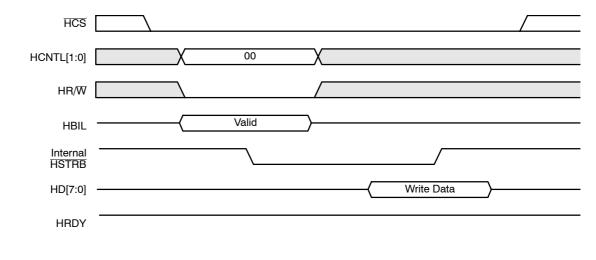

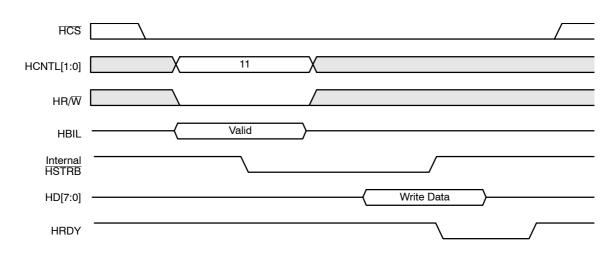

|         | Nonmultiplexed-Mode Host Read Cycle and Host Write Cycle                                                                                     |          |

| 11      | HRDY Behavior During an HPIC or HPIA Read Cycle in the Multiplexed Mode                                                                      |          |

| 12      |                                                                                                                                              | 57       |

| 13      | HRDY Behavior During a Data Read Operation in the Multiplexed Mode<br>Case 1: HPIA Write Cycle Followed by Nonautoincrement HPID Read Cycle) | 37       |

| 14      | HRDY Behavior During a Data Read Operation in the Multiplexed Mode                                                                           | 07       |

| 17      | (Case 2: HPIA Write Cycle Followed by Autoincrement HPID Read Cycles)                                                                        | 38       |

| 15      | HRDY Behavior During an HPIC Write Cycle in the Multiplexed Mode                                                                             | 38       |

| 16      | HRDY Behavior During a Data Write Operation in the Multiplexed Mode                                                                          |          |

|         | (Case 1: No Autoincrementing)                                                                                                                | 39       |

| 17      | UDDV Rehavior During a Data Write Operation in the Multiplayed Made                                                                          |          |

|         | (Case 2: Autoincrementing Selected, FIFO Empty Before Write)                                                                                 | 39       |

| 18      | HRDY Behavior During a Data Write Operation in the Multiplexed Mode                                                                          |          |

|         | (Case 3: Autoincrementing Selected, FIFO Not Empty Before Write)                                                                             | 40       |

| 19      | HRDY Behavior During an HPIC Read Cycle in the Nonmultiplexed Mode                                                                           |          |

| 20      | HRDY Behavior During a Data Read Operation in the Nonmultiplexed Mode                                                                        |          |

| 21      | HRDY Behavior During an HPIC Write Cycle in the Nonmultiplexed Mode                                                                          |          |

| 22      | HRDY Behavior During a Data Write Operation in the Nonmultiplexed-Mode                                                                       |          |

| 23      | Host-to-CPU Interrupt State Diagram                                                                                                          |          |

| 24      | CPU-to-Host Interrupt State Diagram                                                                                                          |          |

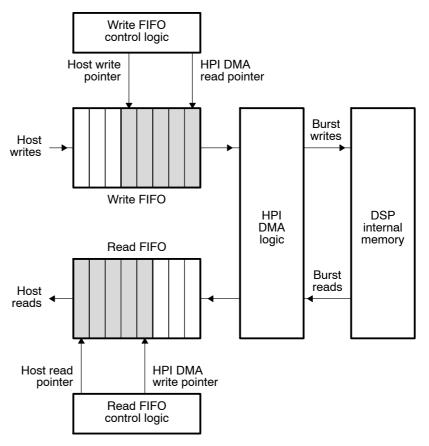

| 25      | FIFOs in the HPI                                                                                                                             |          |

| 26      | Control Register (HPIC)                                                                                                                      |          |

| 27      | Data Register (HPID)                                                                                                                         | 61       |

| 28      | Format of an Address Register (HPIAR or HPIAW) - TMS320VC5501 Device                                                                         | 63       |

| 29      | Format of an Address Register (HPIAR or HPIAW) - TMS320VC5502 Device                                                                         | 63       |

| 30      | General-Purpose I/O Enable Register (HGPIOEN)                                                                                                | 64       |

| 31      | Format of Registers HGPIODIR1 and HGPIODAT1                                                                                                  |          |

| 32      | Format of Registers HGPIODIR2 and HGPIODAT2                                                                                                  |          |

| 33      | Format of Registers HGPIODIR3 and HGPIODAT3                                                                                                  | 12       |

| 34      | Format of Registers HGPIOINT1 and HGPIOINT2                                                                                                  |          |

| 35      | Power and Emulation Management Register (HPWREMU)                                                                                            | /5       |

7

## **Tables**

| 1  | Internal Memory Accessible to Host and Address Bits Required From Host | . 9 |

|----|------------------------------------------------------------------------|-----|

| 2  | Summary of HPI Registers                                               | 12  |

| 3  | Effects of the Parallel/Host Port Mux Mode Bit of XBSR                 | 15  |

| 4  | HPI Signals                                                            | 16  |

| 5  | Options for Connecting Host and HPI Data Strobe Pins                   | 26  |

| 6  | Access Types Selectable With the HCNTL Signals                         | 27  |

| 7  | Cycle Types Selectable With the HCNTL and HR/W Signals                 | 28  |

| 8  | General-Purpose I/O Control of HPI Pins                                | 52  |

| 9  | Registers of the HPI                                                   |     |

| 10 | Control Register (HPIC) Bits                                           | 58  |

| 11 | Internal Memory Accessible to Host and Address Bits Required From Host | 62  |

| 12 | General-Purpose I/O Enable Register (HGPIOEN) Bits                     | 65  |

| 13 | General-Purpose I/O Direction Register 1 (HGPIODIR1) Bits              | 67  |

| 14 | General-Purpose I/O Data Register 1 (HGPIODAT1) Bits                   | 67  |

| 15 | General-Purpose I/O Direction Register 2 (HGPIODIR2) Bits              | 69  |

| 16 | General-Purpose I/O Data Register 2 (HGPIODAT2) Bits                   | 70  |

| 17 | General-Purpose I/O Direction Register 3 (HGPIODIR3) Bits              | 72  |

| 18 | General-Purpose I/O Data Register 3 (HGPIODAT3) Bits                   | 72  |

| 19 | General-Purpose I/O Interrupt Control Register 1 (HGPIOINT1) Bits      | 74  |

| 20 | General-Purpose I/O Interrupt Control Register 2 (HGPIOINT2) Bits      | 74  |

| 21 | Power and Emulation Management Register (HPWREMU) Bits                 | 75  |

This guide describes the host port interface (HPI) on the TMS320VC5501 and TMS320VC5502 digital signal processors (DSPs). The HPI enables an external host processor (host) to directly access memory internal to the DSP using an 8-bit or 16-bit interface.

#### 1 Introduction to the HPI

The HPI provides a parallel port through which an external host processor (host) can access memory internal to the TMS320VC5501 and TMS320VC5502 DSPs (see Table 1). The host cannot access addresses 0000h–005Fh because they are reserved for the memory mapped registers of the CPU. The host does not have direct access to memory that is external to the DSP.

Table 1. Internal Memory Accessible to Host and Address Bits Required From Host

| Device       | Internal Memory<br>Accessible to the Host           | Address Bits Required<br>From Host                                                                                          |

|--------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| TMS320VC5501 | First 16K words,<br>except addresses<br>0000h-005Fh | The host must provide 14-bit<br>addresses to the HPI, where<br>each address points to a word (a<br>16-bit value) in memory. |

| TMS320VC5502 | First 32K words,<br>except addresses<br>0000h-005Fh | The host must provide 15-bit<br>addresses to the HPI, where<br>each address points to a word (a<br>16-bit value) in memory. |

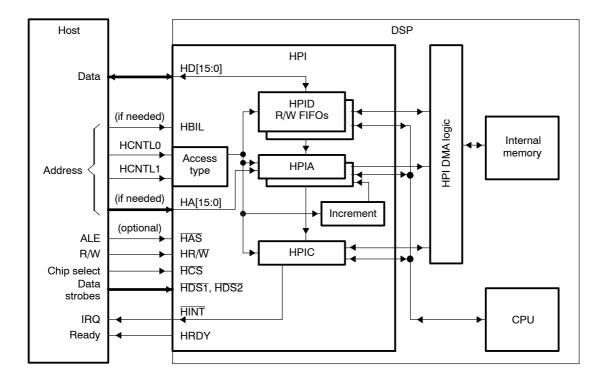

Figure 1 is a high-level block diagram showing how the HPI connects a host (left side of figure) and the DSP internal memory (right side of figure). Host activity is asynchronous to the clock that drives the HPI, which is the fast peripherals clock (SYSCLK1) of the DSP. The host functions as a master to the HPI. When HPI resources are temporarily busy or unavailable, the HPI can communicate this to the host by deasserting the HPI-ready (HRDY) output signal.

Figure 1. The Position of the HPI in the Host-DSP System

The HPI supports two interface modes:

- 8-bit multiplexed mode. This mode is selected if the GPIO6 pin of the DSP is sampled high at reset. In this mode, an 8-bit data bus (HD[7:0]) carries both addresses and data. Each host cycle on the bus consists of two consecutive 8-bit transfers. When the host drives an address on the bus, the address is stored in a 16-bit address register (HPIA) in the HPI, so that the bus can then be used for data. The HPI contains two HPIAs (HPIAR and HPIAW), which can be used as separate address registers for read accesses and write accesses (for details, see section 2 on page 18).

- 16-bit nonmultiplexed mode. This mode is not supported on TMS320VC5501 devices. On TMS320VC5502 devices, this mode is selected if the GPIO6 pin of the DSP is sampled low at reset. In the nonmultiplexed mode, the HPI provides separate address and data buses: a 16-bit address bus (HA[15:0]) and a 16-bit data bus (HD[15:0]). The address registers of the HPI are not used in this mode. Each host cycle on the data bus consists of one 16-bit transfer.

A 16-bit control register (HPIC) is accessible by the DSP CPU and the host. The CPU can use HPIC to send an interrupt request to the host, to clear an interrupt request from the host, and to monitor the HPI. The host can use HPIC to configure and monitor the HPI, to send an interrupt request to the CPU, and to clear an interrupt request from the CPU.

Data flow between the host and the HPI uses a temporary storage register, the 16-bit data register (HPID). Data arriving from the host is held in HPID until the data can be stored elsewhere in the DSP. Data to be sent to the host is held in HPID until the HPI is ready to perform the transfer. When address autoincrementing is used, read and write FIFOs are used to store burst data. If autoincrementing is not used, the FIFO memory acts as a single register (only one location is used).

#### Note:

To manage data transfers between HPID and the internal memory, the DSP contains dedicated HPI DMA logic. The HPI DMA logic is not programmable; it automatically stores or fetches data using the address provided by the host. The HPI DMA logic is independent of the DMA controller included in the DSP. Information on the DMA controller is in the *TMS320VC5501/5502* DSP Direct Memory Access (DMA) Controller Reference Guide (literature number SPRU613).

#### 1.1 Summary of the HPI Registers

Table 2 summarizes the registers inside the HPI, including access permissions and access requirements from the perspective of the host and of the DSP CPU. Section 9 (page 56) gives detailed descriptions of all these registers. Section 2 (page 18) explains why there are two address registers (HPIAW and HPIAR) and describes the two HPIA modes that determine how the registers are used by the host.

The host can access only HPIC, HPIAW, HPIAR, and HPID. By driving specific levels on the HCNTL[1:0] signals, the host indicates whether it is performing an HPIC, HPIA, or HPID access. In the case of an HPID access, the HCNTL signals also indicate whether the HPI should perform an automatic address increment after the access or not increment the address after the access. The effects of the HCNTL[1:0] signals are described in more detail in section 3.4 (page 27). The HR/W signal indicates whether the host is reading or writing.

The DSP CPU cannot access HPID but has limited access to HPIC, HPIAR, and HPIAW. The CPU has full access to the power and emulation management register, which is used to select an emulation mode for the HPI.

To access a register in the HPI, the CPU accesses it at a designated address in the I/O space of the DSP. Table 2 shows the I/O addresses.

#### Table 2. Summary of HPI Registers

|                                                                      |                           | Host Access         | CPU Access                |                   |

|----------------------------------------------------------------------|---------------------------|---------------------|---------------------------|-------------------|

| Register                                                             | Read/Write<br>Permissions | Access Requirements | Read/Write<br>Permissions | I/O<br>Address    |

| Reserved                                                             | -                         | -                   | -                         | A000h to<br>A001h |

| HPWREMU:<br>Power and<br>emulation<br>management register            | None                      | _                   | Read/Write                | A002h             |

| Reserved                                                             | -                         | -                   | -                         | A003h             |

| HGPIOINT1:<br>General-purpose I/O<br>interrupt control<br>register 1 | None                      | _                   | Read/Write                | A004h             |

| HGPIOINT2:<br>General-purpose I/O<br>interrupt control<br>register 2 | None                      | -                   | Read/Write                | A005h             |

| HGPIOEN:<br>General-purpose I/O<br>enable register                   | None                      | -                   | Read/Write                | A006h             |

| Reserved                                                             | -                         | -                   | -                         | A007h             |

| HGPIODIR1:<br>General-purpose I/O<br>direction register 1            | None                      | -                   | Read/Write                | A008h             |

| Reserved                                                             | -                         | -                   | -                         | A009h             |

| HGPIODAT1:<br>General-purpose I/O<br>data register 1                 | None                      | -                   | Read/Write                | A00Ah             |

| Reserved                                                             | -                         | -                   | -                         | A00Bh             |

<sup>†</sup> On TMS320VC5502 devices, HGPIODIR3 and HGPIODAT3 are used when the address pins, HA[15:0], are configured for general-purpose I/O. On TMS320VC5501 devices, these register addresses are reserved because there are no address pins. <sup>‡</sup> The single-HPIA mode and the dual-HPIA mode are described in section 2 (page 18).

Host Port Interface (HPI) 12

|                                                                                          |                           | Host Access                                                                                                                                                   | CPU Acc                                               | ess              |

|------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|

| Register                                                                                 | Read/Write<br>Permissions | Access Requirements                                                                                                                                           | Read/Write<br>Permissions                             | I∕O<br>Address   |

| HGPIODIR2:<br>General-purpose I/O<br>direction register 2                                | None                      | _                                                                                                                                                             | Read/Write                                            | A00Ch            |

| Reserved                                                                                 | -                         | -                                                                                                                                                             | -                                                     | A00Dh            |

| HGPIODAT2:<br>General-purpose I/O<br>data register 2                                     | None                      | -                                                                                                                                                             | Read/Write                                            | A00Eh            |

| Reserved                                                                                 | -                         | -                                                                                                                                                             | -                                                     | A00Fh            |

| HGPIODIR3:<br>General-purpose I/O<br>direction register 3<br>or<br>Reserved <sup>†</sup> | None                      | _                                                                                                                                                             | Read/Write                                            | A010h            |

| Reserved                                                                                 | -                         | -                                                                                                                                                             | -                                                     | A011h            |

| HGPIODAT3:<br>General-purpose I/O<br>data register 3<br>or<br>Reserved <sup>†</sup>      | None                      | -                                                                                                                                                             | Read/Write                                            | A012h            |

| Reserved                                                                                 | -                         | -                                                                                                                                                             | -                                                     | A013h to<br>A017 |

| HPIC:<br>Control register                                                                | Read/Write                | HCNTL1 low<br>HCNTL0 low                                                                                                                                      | Read: All bits<br>Write: HINT and<br>DSPINT bits only | A018h            |

| Reserved                                                                                 | -                         | -                                                                                                                                                             | _                                                     | A019h            |

| HPIAW:<br>Write address register                                                         | Read/Write                | <ul> <li>Multiplexed mode</li> <li>HCNTL1 high<br/>HCNTL0 low</li> <li>Single-HPIA mode, or<br/>Dual-HPIA mode with<br/>HPIAW selected<sup>‡</sup></li> </ul> | Read-only                                             | A01Ah            |

#### Summary of HPI Registers (Continued) Table 2.

<sup>&</sup>lt;sup>†</sup> On TMS320VC5502 devices, HGPIODIR3 and HGPIODAT3 are used when the address pins, HA[15:0], are configured for general-purpose I/O. On TMS320VC5501 devices, these register addresses are reserved because there are no address pins. <sup>‡</sup> The single-HPIA mode and the dual-HPIA mode are described in section 2 (page 18).

|                                 |                           | Host Access                                                                | CPU Ad                    | cess              |

|---------------------------------|---------------------------|----------------------------------------------------------------------------|---------------------------|-------------------|

| Register                        | Read/Write<br>Permissions | Access Requirements                                                        | Read/Write<br>Permissions | I∕O<br>Address    |

| Reserved                        | -                         | -                                                                          | -                         | A01Bh             |

| HPIAR:<br>Read address register | Read/Write                | <ul> <li>Multiplexed mode</li> <li>HCNTL1 high<br/>HCNTL0 low</li> </ul>   | Read-only                 | A01Ch             |

|                                 |                           | Single-HPIA mode, or<br>Dual-HPIA mode with<br>HPIAR selected <sup>‡</sup> |                           |                   |

| Reserved                        | -                         | -                                                                          | -                         | A01Dh to<br>A020h |

| HPID:<br>Data register          | Read/Write                | With autoincrementing:<br>HCNTL1 low<br>HCNTL0 high                        | None                      | None              |

|                                 |                           | No autoincrementing:<br>HCNTL1 high<br>HCNTL0 high                         |                           |                   |

#### Summary of HPI Registers (Continued) Table 2.

<sup>†</sup> On TMS320VC5502 devices, HGPIODIR3 and HGPIODAT3 are used when the address pins, HA[15:0], are configured for general-purpose I/O. On TMS320VC5501 devices, these register addresses are reserved because there are no address pins. <sup>‡</sup> The single-HPIA mode and the dual-HPIA mode are described in section 2 (page 18).

#### 1.2 Summary of the HPI Signals

The external bus selection register (XBSR) in the DSP includes a Parallel/Host Port Mux Mode bit that determines how certain pins are allocated within the DSP. Table 3 describes the effects of this bit on the HPI. At reset, the mux mode selected depends on the GPIO6 pin. If GPIO6 is sampled low at reset, the mux mode bit is forced to 0. If GPIO6 is sampled high at reset, the mux mode bit is forced to 1. For more information about XBSR and GPIO6, see the device-specific data manual: *TMS320VC5501 Fixed-Point Digital Signal Processor Data Manual* (literature number SPRS206) or *TMS320VC5502 Fixed-Point Digital Signal Processor Data Manual* (literature number SPRS166).

Table 3. Effects of the Parallel/Host Port Mux Mode Bit of XBSR

| Device       | Parallel/Host Port Mux Mode Bit = 0<br>(Default if GPIO6 Pin Low at Reset)                                                                                   | Parallel/Host Port Mux Mode Bit = 1<br>(Default if GPIO6 Pin High at Reset)                                                                                       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS320VC5501 | 8-bit multiplexed mode off                                                                                                                                   | 8-bit multiplexed mode on                                                                                                                                         |

|              | The pins HBIL, HAS, and HD[7:0] are not<br>under the control of the HPI. Host<br>accesses are not possible.                                                  | The HPI has control over all pins needed for the 8-bit multiplexed mode.                                                                                          |

| TMS320VC5502 | 16-bit nonmultiplexed mode selected                                                                                                                          | 8-bit multiplexed mode selected                                                                                                                                   |

|              | The HPI has control over all pins needed<br>for the 16-bit nonmultiplexed mode. The<br>unneeded pins, HBIL and HAS, are not<br>under the control of the HPI. | The HPI has control over all pins needed<br>for the 8-bit multiplexed mode. The<br>unneeded pins, HA[15:0] and HD[15:8],<br>are not under the control of the HPI. |

Table 4 summarizes each of the HPI signals. It provides the signal name, the possible states for the signal (input, output, or high-impedance), the connection(s) to be made on the host side of the interface, and a description of the signal's function.

| Signal           | State <sup>†</sup> | Host Connection                                                | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPIENA           | I                  | Static/tied high or low.                                       | HPI enable. To enable the HPI for operation, tie this<br>pin high. If this pin is tied low, the HPI is disabled, and<br>all output pins that are not enabled for<br>general-purpose I/O are placed in the<br>high-impedance state.                                                                                                                                        |

| HCS              | I                  | Chip select pin                                                | HPI chip select. HCS must be low for the HPI to be<br>selected by the host. HCS can be kept low between<br>accesses. HCS normally precedes an active HDS<br>(data strobe) signal, but can be connected to an<br>HDS pin for simultaneous select and strobe activity.                                                                                                      |

| HDS1 and<br>HDS2 | I                  | Read strobe and write<br>strobe pins or any data<br>strobe pin | HPI data strobe pins. These pins are used for<br>strobing data in and out of the HPI (for data strobing<br>details, see section 3.3 on page 25). The direction of<br>the data transfer depends on the logic level of the<br>HR/W signal.                                                                                                                                  |

|                  |                    |                                                                | The HDS signals are also used to latch control information (if HAS is tied high) on the falling edge. During an HPID write access, data is latched into the HPID register on the rising edge of HDS. During read operations, these pins act as output-enable pins of the host data bus.                                                                                   |

| HCNTL[1:0]       | I                  | Address or control pins                                        | HPI access control inputs. The HPI latches the logic<br>levels of these pins on the falling edge of HAS or<br>internal HSTRB (for details about internal HSTRB,<br>see section 3.3 on page 25). The four binary states of<br>these pins determine the access type of the current<br>transfer (HPIC, HPID with autoincrementing, HPIA,<br>HPID).                           |

| HR/W             | I                  | R/W strobe pin                                                 | HPI read/write. On the falling edge of $\overline{\text{HAS}}$ or internal $\overline{\text{HSTRB}}$ , HR/ $\overline{\text{W}}$ indicates whether the current access is to be a read or write operation. Driving HR/ $\overline{\text{W}}$ high indicates the transfer is a read from the HPI, while driving HR/ $\overline{\text{W}}$ low indicates a write to the HPI. |

| HBIL             | I                  | Address or control pins                                        | Byte identification line. In the 8-bit multiplexed mode,<br>the host must use HBIL to identify the first and second<br>bytes of the host cycle. HBIL must be driven low for<br>the first byte and high for the second byte. This signal<br>is ignored when the HPI is operating in the 16-bit<br>nonmultiplexed mode (TMS320VC5502 devices<br>only).                      |

Table 4. HPI Signals

<sup>†</sup> I = Input, O = Output, Z = High impedance

| Signal              | State <sup>†</sup> | Host Connection                                        | Description                                                                                                                                                                                                                                                                                                                                  |

|---------------------|--------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HAS                 | I                  | ALE (address latch<br>enable) or address<br>strobe pin | Address strobe. A host with a multiplexed address/data bus can have HAS connected to its ALE pin. The falling edge of HAS is used to latch the logic levels of the HR/W, HCNTL1, and HCNTL0 pins, which are typically connected to host address lines. When used, the HAS signal must precede the falling edge of the internal HSTRB signal. |

|                     |                    |                                                        | Hosts with separate address/data buses must tie this signal high. In this case, the HPI latches the HR/ $W$ , HCNTL1, and HCNTL0 levels on the falling edge of the internal HSTRB signal.                                                                                                                                                    |

| HA[15:0]            | I                  | Address bus                                            | HPI address bus. In the 16-bit nonmultiplexed mode,<br>the host drives a 15-bit address on this 16-bit bus.<br>HA[14:0] carry the address, and because only 15<br>address bits are needed, the bit on HA15 is a<br>don't care. In the 8-bit multiplexed mode, HA[15:0]<br>are not used.                                                      |

| HD[15:8]<br>HD[7:0] | I/O/Z              | Data bus                                               | HPI data bus. The HPI data bus carries the data to/from the HPI. In the 16-bit nonmultiplexed mode, all 16 lines are used. In the 8-bit multiplexed mode, lines 7 through 0 are used. HD[15:8] are not present on TMS320VC5501 devices.                                                                                                      |

| HRDY                | O/Z                | Asynchronous ready pin                                 | HPI-ready signal. When the HPI drives HRDY high,<br>the host has permission to complete the current host<br>cycle. When the HPI drives HRDY low, the HPI is not<br>ready for the current host cycle to complete.                                                                                                                             |

| HINT                | O/Z                | Interrupt pin                                          | Host Interrupt. The DSP can interrupt the host<br>processor by writing a 1 to the HINT bit of HPIC.<br>Before subsequent HINT interrupts can occur, the<br>host must clear previous interrupts by writing a 1 to<br>the HINT bit. This pin is active-low and inverted from<br>the HINT bit value in HPIC.                                    |

Table 4. HPI Signals (Continued)

<sup>†</sup> I = Input, O = Output, Z = High impedance

#### 2 Using the Address Registers (8-Bit Multiplexed Mode Only)

The HPI contains two 16-bit address registers: one for read operations (HPIAR) and one for write operations (HPIAW). These roles are unchanging from the viewpoint of the HPI DMA logic. In the 8-bit multiplexed mode of the HPI, the HPI DMA logic gets the address from HPIAR when reading from internal memory and gets the address from HPIAW when writing to internal memory.

However, unlike the HPI DMA logic, the host can choose how to interact with the two HPIA registers. Using the DUALHPIA bit of HPIC, the host determines whether HPIAR and HPIAW act as a single 16-bit register (single-HPIA mode) or as two independent 16-bit registers (dual-HPIA mode).

#### 2.1 Single-HPIA Mode

If DUALHPIA = 0 in HPIC, HPIAR and HPIAW become a single HPIA register from the perspective of the host. In this mode:

- A host HPIA write cycle (HCNTL[1:0] = 10b, HR/ $\overline{W}$  = 0) updates HPIAR and HPIAW with the same value.

- Both HPIA registers are incremented during autoincrement read/write cycles (HCNTL[1:0] = 01b).

- An HPIA read cycle (HCNTL[1:0] = 10b, HR/W = 1) returns the content of HPIAR, which should be identical to the content of HPIAW.

To maintain consistency between the contents of HPIAR and HPIAW, the host should always re-initialize the HPIA registers after changing the state of the DUALHPIA bit. In addition, when DUALHPIA = 0, the host must always re-initialize the HPIA registers when it changes the data direction (from an HPID read cycle to an HPID write cycle, or vice versa). Otherwise, the memory location accessed by the HPI DMA logic might not be the location intended by the host.

#### 2.2 Dual-HPIA Mode

The host can take advantage of two independent HPIA registers by choosing the dual-HPIA mode (DUALHPIA = 1 in HPIC). In this mode:

A host HPIA access (HCNTL[1:0] = 10b) reads/updates either HPIAR or HPIAW, depending on the value of the HPIA read/write select (HPIASEL) bit of HPIC. This bit is programmed by the host. While HPIASEL = 1, only HPIAR is read or updated by the host. While HPIASEL = 0, only HPIAW is read or updated by the host. The HPIASEL bit is only meaningful in the dual-HPIA mode.

#### Note:

The HPIASEL bit does not affect the HPI DMA logic. Regardless of the value of HPIASEL, the HPI DMA logic uses HPIAR when reading from memory and HPIAW when writing to memory.

A host HPID access with autoincrementing (HCNTL[1:0] = 01b) causes only the relevant HPIA value to be incremented to the next consecutive memory address. In an autoincrement read cycle, HPIAR is incremented after it has been used to perform the current read from memory. In an autoincrement write cycle, HPIAW is incremented after it has been used for the write operation.

#### 3 HPI Operation

#### 3.1 Host-HPI Signal Connections

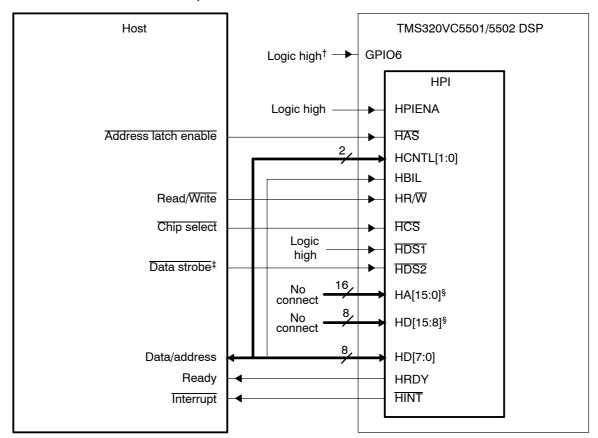

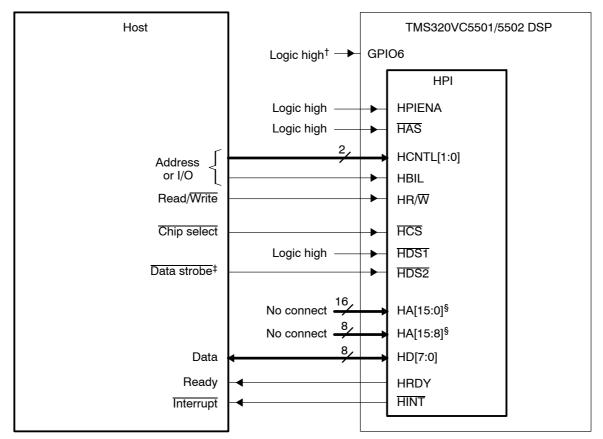

Figure 2 shows an example of signal connections for the 16-bit nonmultiplexed mode. Figure 3 and Figure 4 show a similar examples for the 8-bit multiplexed mode. In Figure 3, the  $\overline{\text{HAS}}$  signal is used as described in section 3.6 (page 29). In Figure 4,  $\overline{\text{HAS}}$  is tied high (not used). The following are key points of comparison between the signal connections in the two interface modes:

- □ The pin GPIO6 of the DSP must be held low at reset for the 16-bit nonmultiplexed mode (TMS320VC5502 devices only) or held high at reset for the 8-bit multiplexed mode.

- ☐ The address strobe (HAS) of the HPI is not used in the 16-bit nonmultiplexed mode and is optional in the 8-bit multiplexed mode.

- ☐ The byte identification line (HBIL) of the HPI is not used in the 16-bit nonmultiplexed mode but is required in the 8-bit multiplexed mode.

- □ The address bus (HA[15:0]) of the HPI is used in the 16-bit nonmultiplexed mode but is not used in the 8-bit multiplexed mode.

| Host                   |                          | TMS320VC5502 DSP                        |    |

|------------------------|--------------------------|-----------------------------------------|----|

|                        | Logic low <sup>†</sup> — | GPIO6                                   |    |

|                        |                          | HP                                      | I  |

|                        | Logic high —             | ► HPIENA                                |    |

|                        | Logic high —             | ► HAS                                   |    |

| Address or I/O         | 2,<br>No connect —       | → HCNTL[1:<br>→ HBIL                    | 0] |

| Read/ <del>Write</del> |                          | ► HR/₩                                  |    |

| Chip select            |                          | ► HCS                                   |    |

| Data strobe‡           | Logic high —             | <ul><li>► HDS1</li><li>► HDS2</li></ul> |    |

|                        | 16                       |                                         |    |

| Address                | · · · ·                  | → HA[15:0]                              |    |

| Data                   | 16                       | → HD[15:0]                              |    |

| Ready                  | -                        | - HRDY                                  |    |

| Interrupt              | -                        | HINT                                    |    |

|                        |                          |                                         |    |

### Figure 2. Example of Host-DSP Signal Connections in the 16-Bit Nonmultiplexed Mode

<sup>†</sup> GPIO6 does not have to be tied high or low. This pin is sampled at reset. On TMS320VC5501 devices, if GPIO6 is sampled low at reset, the HPI is disabled.

<sup>‡</sup> Data strobing options are given in section 3.3 (page 25).

Figure 3. Example of Host-DSP Signal Connections When Using the HAS Signal in the 8-Bit Multiplexed Mode

<sup>†</sup> GPIO6 does not have to be tied high or low. This pin is sampled at reset.

<sup>‡</sup> Data strobing options are given in section 3.3 (page 25).

§ HA[15:0] and HD[15:8] are not present on TMS320VC5501 devices.

## Figure 4. Example of Host-DSP Signal Connections When the HAS Signal is Tied High in the 8-Bit Multiplexed Mode

<sup>†</sup> GPIO6 does not have to be tied high or low. This pin is sampled at reset.

<sup>‡</sup> Data strobing options are given in section 3.3 (page 25).

§ HA[15:0] and HD[15:8] are not present on TMS320VC5501 devices.

#### 3.2 HPI Configuration and Data Flow

The way the host accomplishes accesses varies slightly depending on the selected interface mode. In the 8-bit multiplexed mode:

- The host writes to the control register (HPIC) to properly configure the HPI. Typically, this means programming the byte-order bit (BOB) and the HPIA-related bits (HPIADUAL and HPIASEL). This step is normally performed once before the initial data access. For information on the control bits in HPIC, see section 9.1 on page 57.

- 2) The host writes the desired internal DSP memory address to an address register (HPIAR and/or HPIAW). For an introduction to the two HPIA registers and the two ways the host can interact with them, see section 2 on page 18.

- The host reads from or writes to the data register (HPID). Data transfers between HPID and the internal memory of the DSP are handled by the HPI DMA logic.

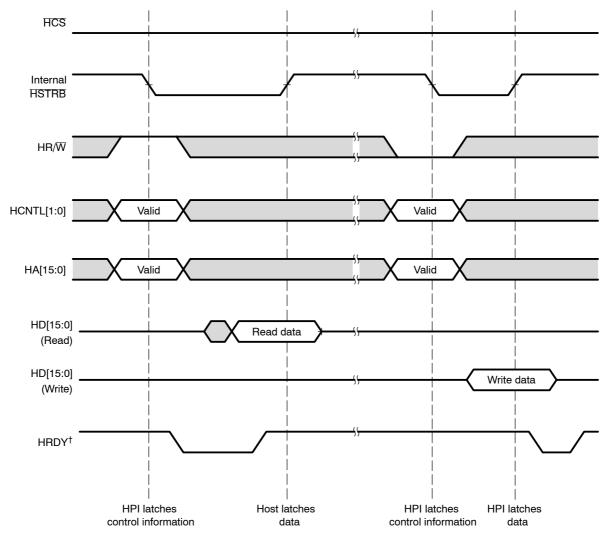

In the 16-bit nonmultiplexed mode (TMS320VC5502 devices only), no HPIC programming is required. The host can immediately read from or write to the data register (HPID). When initiating an HPID read or write cycle, the host drives the memory address on the dedicated address lines, HA[15:0]. Only 15 address bits are needed to access the 32K words of internal memory that are accessible to the HPI; therefore, the MSB of the address (on line HA15) is a don't care. Data transfers between HPID and the internal memory of the DSP are handled by the HPI DMA logic.

Regardless of the chosen interface mode, each step of the access uses the same bus. Therefore, the host must drive the appropriate levels on the HCNTL1 and HCNTL0 signals to indicate which register is to be accessed. The host must also drive the appropriate level on the HR/ $\overline{W}$  signal to indicate the data direction (read or write) and must drive other control signals as appropriate. When HPI resources are temporarily busy or unavailable, the HPI can communicate this to the host by deasserting the HPI-ready (HRDY) output signal.

When performing an access, the HPI first latches the levels on HCNTL[1:0], HR/ $\overline{W}$ , and other control signals. In the 8-bit multiplexed mode, this latching can occur on the falling edge of the internal strobe signal (for details, see section 3.3 on page 25) or the falling edge of HAS (for details, see section 3.6 on page 29). In the 16-bit nonmultiplexed mode, this latching must occur on the falling edge of the internal strobe signal. After the control information is latched, the HPI initiates an access based on the control signals.

If the host wants to read data from the internal memory, the HPI DMA logic reads the memory address from HPIAR and retrieves the data from the addressed memory location. When the data has been placed in HPID, the HPI drives the data onto its HD bus. The HRDY signal informs the host whether the data on the HD bus is valid (HRDY high) or not valid yet (HRDY low). When the data is valid, the host should latch the data and drive the connected data strobe (HDS1 or HDS2) inactive, which, in turn, will cause the internal strobe (internal HSTRB) signal to transition from low to high.

If the host wants to write data to the internal memory, the operation is similar. After the host determines that the HPI is ready to latch the data (HRDY is high), it must cause internal HSTRB to transition from low to high, which causes the data to be latched into HPID. Once the data is in HPID, the HPI DMA logic reads the memory address from HPIAW and transfers the data from HPID to the addressed memory location.

The CPU, the HPI DMA logic, and the DMA controller all can access the internal memory of the DSP. In the case when the CPU and the HPI DMA logic simultaneously request access to the same DARAM block in internal memory, CPU requests always have priority over HPI DMA logic requests. The same is true when the CPU and the DMA controller access the same DARAM block. Both HPI DMA logic and DMA controller requests to a DARAM block are serviced when there are no more CPU requests. If both the HPI DMA logic and the DMA controller access the same half of the on-chip DARAM, the requests from those two modules are serviced in a round-robin fashion. The bottom half of DARAM consists of memory blocks DARAM0–DARAM3, and the top half consists of blocks DARAM4–DARAM7. See the device-specific data manual for the start and end addresses of each DARAM block.

### 3.3 HDS2, HDS1, and HCS: Data Strobing and Chip Selection

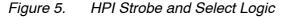

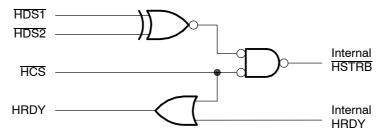

As illustrated in Figure 5, the strobing logic is a function of three key inputs: the chip select pin (HCS) and two data strobe signals (HDS1 and HDS2). The internal strobe signal, which is referred to as internal HSTRB throughout this document, functions as the actual strobe signal inside the HPI. HCS must be low (HPI selected) during strobe activity on the HDS pins. If HCS remains high (HPI not selected), activity on the HDS pins is ignored.

Strobe connections between the host and the HPI depend in part on the number and types of strobe pins available on the host. Table 5 describes some options for connecting to the  $\overline{\text{HDS}}$  pins.

Notice in Figure 5 that HRDY is also gated by HCS. If HCS goes high (HPI not selected), HRDY goes high, regardless of whether the current internal transfer is completed in the DSP.

| Available Host Data Strobe Pins                                | Connections to HPI Data Strobe Pins                                                                                                                                                                                                           |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host has separate read and write strobe pins, both active-low  | Connect one strobe pin to HDS1 and the other to HDS2 <sup>†</sup> . Since such host might not provide a R/W line, take care to satisfy HR/W timings as stated in the device datasheet. This could possibly be done using a host address line. |

| Host has separate read and write strobe pins, both active-high | Connect one strobe pin to HDS1 and the other to HDS2 <sup>†</sup> . Since such host might not provide a R/W line, take care to satisfy HR/W timings as stated in the device datasheet. This could possibly be done using a host address line. |

| Host has one active-low strobe pin                             | Connect the strobe pin to $\overline{\text{HDS1}}$ or $\overline{\text{HDS2}}$ , and connect the other pin to logic level 1.                                                                                                                  |

| Host has one active-high strobe pin                            | Connect the strobe pin to HDS1 or HDS2,<br>and connect the other strobe pin to logic<br>level 0.                                                                                                                                              |

#### Table 5. Options for Connecting Host and HPI Data Strobe Pins

<sup>†</sup> The HR/W signal could be driven by a host address line in this case.

#### Note:

- 1) The HCS input and one HDS strobe input can be tied together and driven with a single strobe signal from the host. This technique selects the HPI and provides the strobe simultaneously. When using this method, be aware that HRDY is gated by HCS as previously described.

- 2) It is not recommended to tie both  $\overline{\text{HDS1}}$  and  $\overline{\text{HDS2}}$  to static logic levels and use  $\overline{\text{HCS}}$  as a strobe.

### 3.4 HCNTL[1:0] and HR/W: Indicating the Cycle Type

The cycle type consists of:

- ☐ The access type that the host selects by driving the appropriate levels on the HCNTL[1:0] pins of the HPI. Table 6 describes the four available access types.

- ☐ The transfer direction that the host selects with the HR/W pin. The host must drive the HR/W signal high (read) or low (write).

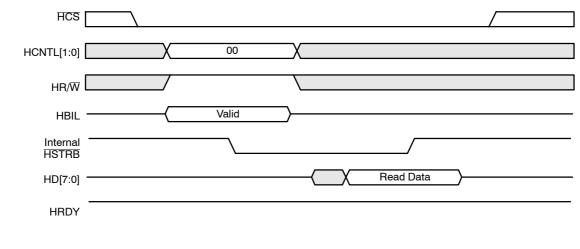

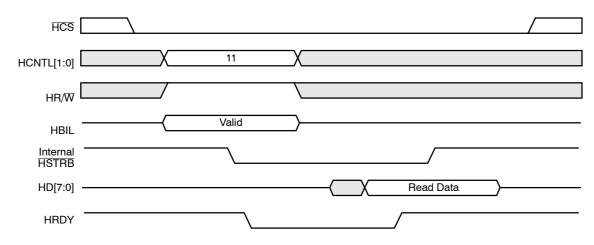

A summary of cycle types is in Table 7. The HPI samples the HCNTL levels either at the falling edge of  $\overline{\text{HAS}}$  (if  $\overline{\text{HAS}}$  is used in the 8-bit multiplexed mode) or at the falling edge of the internal strobe signal  $\overline{\text{HSTRB}}$  (if  $\overline{\text{HAS}}$  is not used and is tied high). In the 16-bit nonmultiplexed mode, the HPIA registers are not used and, therefore, only HPID accesses without autoincrementing and HPIC accesses are valid.

| HCNTL1 | HCNTL0 | Access Type                                                                                                                                                                                                                                                                                   |  |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0      | 0      | HPIC access.<br>The host requests to access the HPI control register<br>(HPIC).                                                                                                                                                                                                               |  |

| 0      | 1      | HPID access with autoincrementing.<br><i>This is only a valid option in the multiplexed mode.</i> The<br>host requests to access the HPI data register (HPID)<br>and to have the appropriate HPI address register<br>(HPIAR and/or HPIAW) automatically incremented by 1<br>after the access. |  |

| 1      | 0      | HPIA access.<br>This is only a valid option in the multiplexed mode. The<br>host requests to access the appropriate HPI address<br>register (HPIAR and/or HPIAW).                                                                                                                             |  |

| 1      | 1      | HPID access without autoincrementing.<br>The host requests to access the HPI data register<br>(HPID) but requests no automatic post-increment of the<br>HPI address register.                                                                                                                 |  |

Table 6. Access Types Selectable With the HCNTL Signals

| HCNTL1 | HCNTL0 | HR/W | Сусіе Туре                                |

|--------|--------|------|-------------------------------------------|

| 0      | 0      | 0    | HPIC write cycle                          |

| 0      | 0      | 1    | HPIC read cycle                           |

| 0      | 1      | 0    | HPID write cycle with autoincrementing    |

| 0      | 1      | 1    | HPID read cycle with autoincrementing     |

| 1      | 0      | 0    | HPIA write cycle                          |

| 1      | 0      | 1    | HPIA read cycle                           |

| 1      | 1      | 0    | HPID write cycle without autoincrementing |

| 1      | 1      | 1    | HPID read cycle without autoincrementing  |

Table 7. Cycle Types Selectable With the HCNTL and HR/W Signals

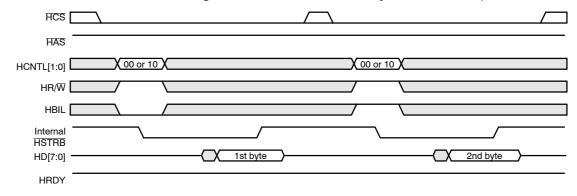

## 3.5 HBIL: Identifying the First and Second Bytes in Multiplexed-Mode Transfers

In the 8-bit multiplexed mode, each host cycle consists of two consecutive byte transfers. For each transfer, the host must specify the cycle type with HCNTL[1:0] and HR/ $\overline{W}$ , and the host must use HBIL to indicate whether the first or second byte is being transferred. For HPID and HPIA accesses, HBIL must always be driven low for the first byte transfer and high for the second byte transfer. Results are undefined if the sequence is broken. For examples of using HBIL, see the figures in sections 3.6 and 3.7. (Section 3.6 begins on page 29.)

When the host sends the two bytes of a 16-bit word in this manner, the host can send the most and the least significant bytes of the word in either order (most significant byte first or most significant byte second). However, the host must inform the HPI of the selected order before beginning the host cycle. This is done by programming the byte order (BOB) bit of HPIC. Although BOB is written at bit 0 in HPIC, it's current value is readable at both bit 0 and bit 8 (BOBSTAT). Thus, the host can determine the current byte-order configuration by checking the least significant bit of either half of HPIC.

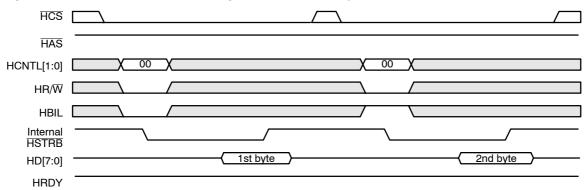

There is one case when the 8-bit multiplexed mode does not require a dual-byte cycle with HBIL low for the first byte and HBIL high for the second byte. Either byte of the HPIC can be accessed with a single-byte cycle. During such a cycle, the host drives HBIL high or low, and as with a dual-byte cycle, the current value of the BOB bit determines which byte of HPIC is accessed. For an example timing diagram of this case, see section 3.8 on page 34.

In the 16-bit nonmultiplexed mode, each host cycle is one word transfer. The HBIL signal is ignored and 16 bits of data are transferred for each active cycle of the internal strobe signal (internal HSTRB).

#### 3.6 HAS: Forcing the HPI to Latch Control Information Early in the 8-Bit Multiplexed Mode

The  $\overline{\text{HAS}}$  signal is only valid in the 8-bit multiplexed mode. This signal is an address strobe that allows control information to be removed earlier in a host cycle, which allows more time to switch bus states from address to data information.

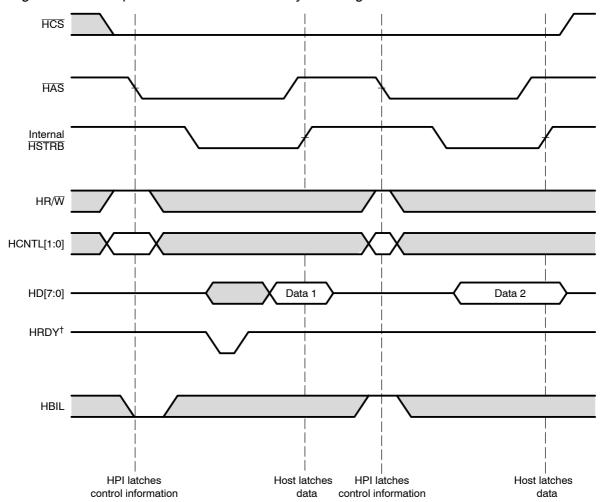

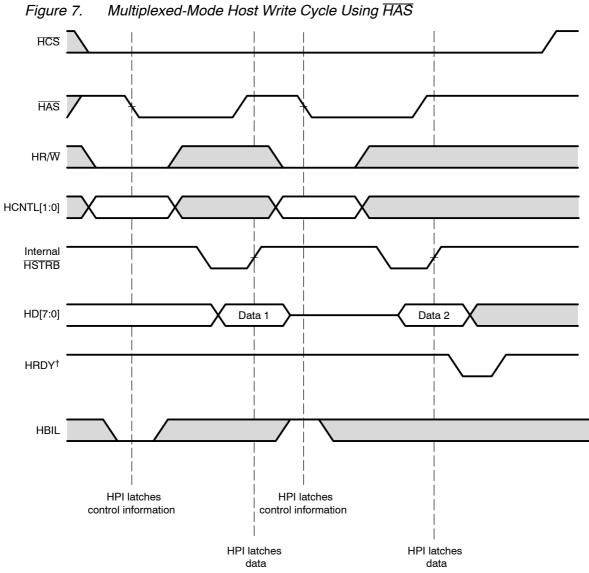

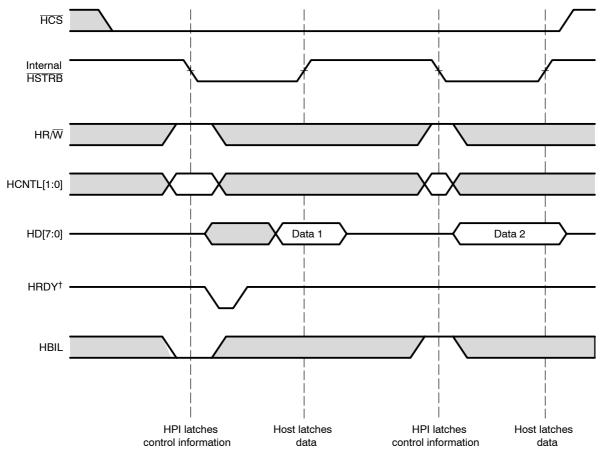

Figure 3 (page 21) shows an example of signal connections when HAS is used for multiplexed transfers. Figure 6 and Figure 7 (following) show typical HPI signal activity when HAS is used.

The process for using HAS is as follows:

1) The host selects the access type.

The host drives the appropriate levels on the HCNTL [1:0] and HR/ $\overline{W}$  signals, and indicates which byte (first or second) will be transferred by driving HBIL high or low.

2) The host drives HAS low.

On the falling edge of  $\overline{\text{HAS}}$ , the HPI latches the states of the HCNTL[1:0], HR/W, and HBIL. The high to low transition of  $\overline{\text{HAS}}$  must precede the falling edge of the internal strobe signal (internal  $\overline{\text{HSTRB}}$ ), which is derived from  $\overline{\text{HCS}}$ ,  $\overline{\text{HDS1}}$ , and  $\overline{\text{HDS2}}$  as described in section 3.3 (page 25).

The  $\overline{\text{HAS}}$  input is not gated by  $\overline{\text{HCS}}$ , therefore allowing time for the host to perform the subsequent access. The  $\overline{\text{HAS}}$  signal may be brought high after internal  $\overline{\text{HSTRB}}$  goes low, indicating that the data access is about to occur. HAS is not required to be driven high at any time during the cycle, but eventually must transition high before the host uses it for another access with different values for HCNTL [1:0], HR/W, and HBIL.

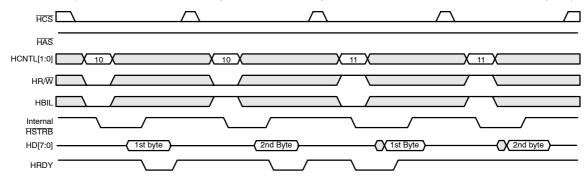

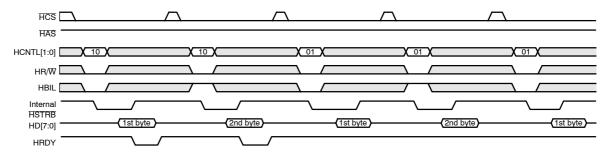

Figure 6. Multiplexed-Mode Host Read Cycle Using HAS

<sup>†</sup> Depending on the type of write operation (HPID without autoincrementing, HPIA, HPIC, or HPID with autoincrementing) and the state of the FIFO, transitions on HRDY may or may not occur. For more information, see section 3.10, *Hardware Handshaking Using the HPI-Ready (HRDY) Signal*, on page 36.

<sup>†</sup> Depending on the type of write operation (HPID without autoincrementing, HPIA, HPIC, or HPID with autoincrementing) and the state of the FIFO, transitions on HRDY may or may not occur. For more information, see section 3.10, Hardware Handshaking Using the HPI-Ready (HRDY) Signal, on page 36.

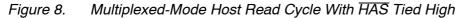

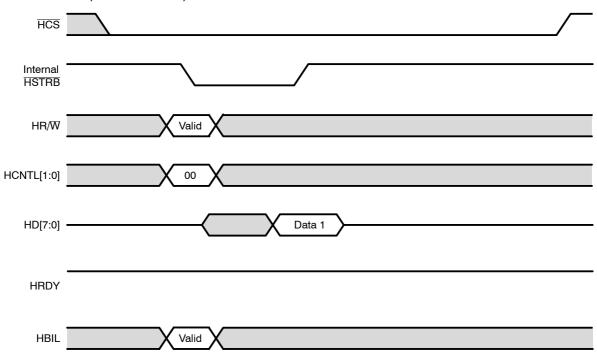

#### 3.7 Performing a Multiplexed Access Without HAS

In cases where the host processor has dedicated signals (address lines or bit I/O) capable of driving the control lines, the  $\overline{\text{HAS}}$  signal is not required. Dedicated pins can be directly connected to HCNTL[1:0], HR/ $\overline{W}$ , and HBIL.

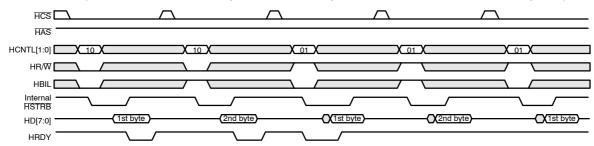

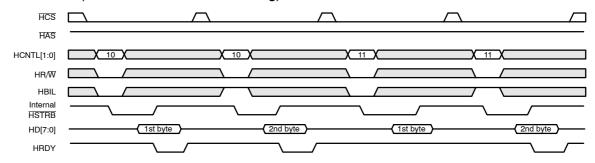

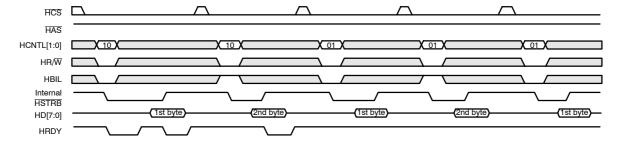

Figure 4 (page 22) shows an example of signal connections when HAS is not used for multiplexed transfers. When HAS is not used, it must be tied high (inactive). Figure 8 and Figure 9 (following) show typical HPI signal activity when HAS is tied high. In these cases, the falling edge of internal HSTRB is used to latch the HCNTL[1:0], HR/ $\overline{W}$ , and HBIL states into the HPI. Internal HSTRB is derived from HCS, HDS1, and HDS2 as described in section 3.3 (page 25).