# OMAP5912 Multimedia Processor OMAP3.2 Subsystem Reference Guide

Literature Number: SPRU749B April 2006

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from TI under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

St Office Box 055505 Dallas, Texas 75205

Copyright © 2006, Texas Instruments Incorporated

# Preface

# **Read This First**

# About This Manual

This document introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

# Notational Conventions

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

# **Related Documentation From Texas Instruments**

Documentation that describes the OMAP5912 device, related peripherals, and other technical collateral, is available in the OMAP5912 Product Folder on TI's website: www.ti.com/omap5912.

# Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

# **Contents**

| Introd | duction              |                                                                                                                                                                                                                                                                                                                                                             | 15                                       |

|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| OMA    | P3.2 Fea             | atures                                                                                                                                                                                                                                                                                                                                                      | 17                                       |

| Traffi | c Contro             | oller                                                                                                                                                                                                                                                                                                                                                       | 21                                       |

| 3.1    | OCP-T                | 1/OCP-T2                                                                                                                                                                                                                                                                                                                                                    | 23                                       |

| 3.2    | EMIFS                | Programming                                                                                                                                                                                                                                                                                                                                                 | 24                                       |

|        | 3.2.1                | General Description                                                                                                                                                                                                                                                                                                                                         | 26                                       |

|        | 3.2.2                | EMIFS CS0 and CS3 Decoding Control                                                                                                                                                                                                                                                                                                                          | 29                                       |

|        | 3.2.3                | EMIFS Miscellaneous Memory Signal Control                                                                                                                                                                                                                                                                                                                   | 29                                       |

|        | 3.2.4                | EMIFS Configuration                                                                                                                                                                                                                                                                                                                                         | 29                                       |

|        | 3.2.5                | EMIFS Abort Control                                                                                                                                                                                                                                                                                                                                         |                                          |

|        | 3.2.6                |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.7                |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.8                | Mode 0—Asynchronous Read Operation                                                                                                                                                                                                                                                                                                                          | 30                                       |

|        | 3.2.9                | Asynchronous Write Operation                                                                                                                                                                                                                                                                                                                                |                                          |

|        | 3.2.10               |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.11               |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.12               |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.13               |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.14               | 8                                                                                                                                                                                                                                                                                                                                                           |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.16               |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        | 3.2.17               | 8                                                                                                                                                                                                                                                                                                                                                           |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 3.3    |                      | 5 S                                                                                                                                                                                                                                                                                                                                                         |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                           |                                          |

|        |                      | , ,                                                                                                                                                                                                                                                                                                                                                         |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        |                      | •                                                                                                                                                                                                                                                                                                                                                           |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

|        |                      |                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 3.4    | OCP-I                | Programming                                                                                                                                                                                                                                                                                                                                                 | 82                                       |

|        | OMA<br>Traffi<br>3.1 | OMAF3.2 Fea<br>Traffic Contro<br>3.1 OCP-T<br>3.2 EMIFS<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17<br>3.2.18<br>3.2.16<br>3.2.17<br>3.2.18<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9 | <ul> <li>3.2 EMIFS Programming</li></ul> |

|   | 3.5   | 3.4.1<br>3.4.2<br>3.4.3<br>Traffic (<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4 | Address and Command Fault Registers<br>Abort Type Register<br>Protection Register<br>Controller Registers<br>OCP-T1/OCT-T2 Registers<br>EMIFS Registers<br>EMIFF Registers<br>OCPI Registers | 84<br>84<br>84<br>85<br>89<br>99 |

|---|-------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |       | 3.5.5                                                                    | TC Abort Management Registers (Applicable To Production Silicon Only) .                                                                                                                      |                                  |

|   | 3.6   | Priority                                                                 | Algorithms                                                                                                                                                                                   | 122                              |

| 4 | Clock | Genera                                                                   | ation and Reset Management                                                                                                                                                                   | 123                              |

|   | 4.1   | Overvie                                                                  | 9W                                                                                                                                                                                           | 123                              |

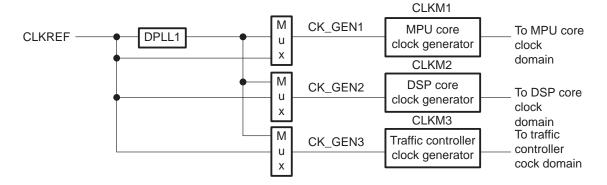

|   | 4.2   | OMAP3                                                                    | 3.2 Clock Generation                                                                                                                                                                         | 124                              |

|   |       | 4.2.1                                                                    | Clock Generation Modes                                                                                                                                                                       | 125                              |

|   |       | 4.2.2                                                                    | DPLL                                                                                                                                                                                         | 127                              |

|   |       | 4.2.3                                                                    | MPU Core Clock Domain                                                                                                                                                                        | 129                              |

|   |       | 4.2.4                                                                    | DSP Core Clock Domain                                                                                                                                                                        | 130                              |

|   |       | 4.2.5                                                                    | Traffic Controller Clock Domain                                                                                                                                                              | 131                              |

|   | 4.3   | Power-                                                                   | Saving Modes and Wake-Up Control                                                                                                                                                             | 132                              |

|   |       | 4.3.1                                                                    | MPU Core Idle Control                                                                                                                                                                        | 132                              |

|   |       | 4.3.2                                                                    | DSP Core Idle Control                                                                                                                                                                        | 133                              |

|   |       | 4.3.3                                                                    | Traffic Controller, System DMA Controller, and MPU Core TIPB<br>Bridges Idle Control                                                                                                         | 135                              |

|   |       | 4.3.4                                                                    | External Device Power Control                                                                                                                                                                | 137                              |

|   |       | 4.3.5                                                                    | DPLL Idle Control                                                                                                                                                                            | 138                              |

|   |       | 4.3.6                                                                    | Chip Idle Mode, Deep Sleep Mode, and Wake-up Control                                                                                                                                         | 138                              |

|   | 4.4   | Registe                                                                  | ers                                                                                                                                                                                          | 140                              |

|   |       | 4.4.1                                                                    | MPU Core Registers                                                                                                                                                                           | 141                              |

|   |       | 4.4.2                                                                    | DSP Core Registers                                                                                                                                                                           | 154                              |

|   |       | 4.4.3                                                                    | DPLL Registers                                                                                                                                                                               | 161                              |

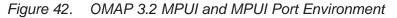

| 5 | MPU   | Core an                                                                  | d MPUI Port                                                                                                                                                                                  | 164                              |

| - | 5.1   |                                                                          |                                                                                                                                                                                              | -                                |

|   | 0     | 5.1.1                                                                    | Access Request                                                                                                                                                                               |                                  |

|   |       | 5.1.2                                                                    | Endian Conversion                                                                                                                                                                            |                                  |

|   |       | 5.1.3                                                                    | MPUI Strobe and Access Factor                                                                                                                                                                |                                  |

|   |       | 5.1.4                                                                    | MPUI Port RAM Access                                                                                                                                                                         |                                  |

|   |       | 5.1.5                                                                    | Peripheral Access                                                                                                                                                                            |                                  |

|   |       | 5.1.6                                                                    | MPUI and DSP Core TIPB Bridge Time-Out                                                                                                                                                       |                                  |

|   |       | 5.1.7                                                                    | Debug                                                                                                                                                                                        |                                  |

|   | 5.2   | -                                                                        | Port                                                                                                                                                                                         |                                  |

|   |       | 5.2.1                                                                    | Access Modes                                                                                                                                                                                 |                                  |

|   |       | 5.2.2                                                                    | Memory Accesses in HOM                                                                                                                                                                       |                                  |

|       | 5.2.3 Memory Accesses in SAM                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 5.2.4 Peripheral Accesses in HOM                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | •                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 5.2.6 Posted Write Mode                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 5.2.7 Bus Error                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 5.2.8 Interrupt                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.3   |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | -                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.4   | DSP Core Endianism Register                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Mailb | boxes                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ••••  | •                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | •                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.2   | Registers                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

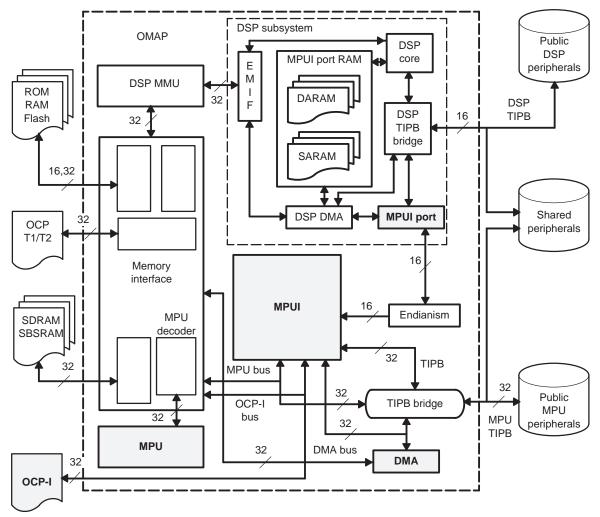

| TIPB  | 3 Bridge                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1   | -                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.2   | Registers                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Revi  | sion History                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | <ul> <li>5.4</li> <li>Mail</li> <li>6.1</li> <li>6.2</li> <li>TIPE</li> <li>7.1</li> </ul> | 5.2.4       Peripheral Accesses in HOM         5.2.5       Peripheral Accesses in SAM         5.2.6       Posted Write Mode         5.2.7       Bus Error         5.2.8       Interrupt         5.3       MPUI Port and MPUI Registers         5.3.1       MPUI Registers         5.4       DSP Core Endianism Register         6.1       Mailboxes         6.1.1       Mailbox Interrupts         6.1.2       Mailbox Software         6.2       Registers         TIPB Bridge         7.1       Functionality         7.1.1       Bus Allocation         7.1.2       Access Permissions         7.1.3       TIPB Strobes and Access Factor         7.1.4       MPU Core Posted Write         7.1.5       Time-Out         7.1.6       Debug |

# Figures

| 1.  | OMAP3.2 Gigacell                                                                                                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

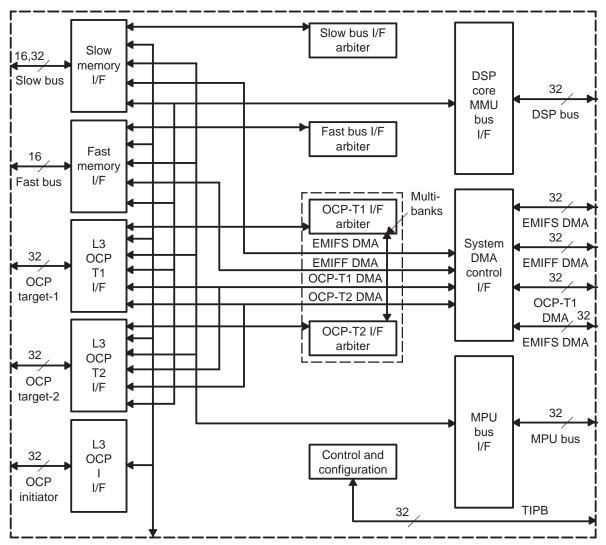

| 2.  | Traffic Controller Functional Block Diagram 23                                                                                                                                             |

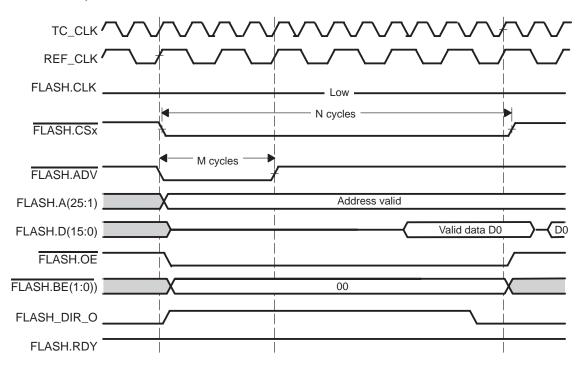

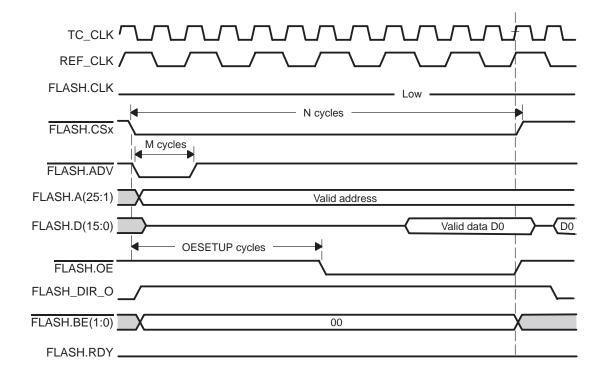

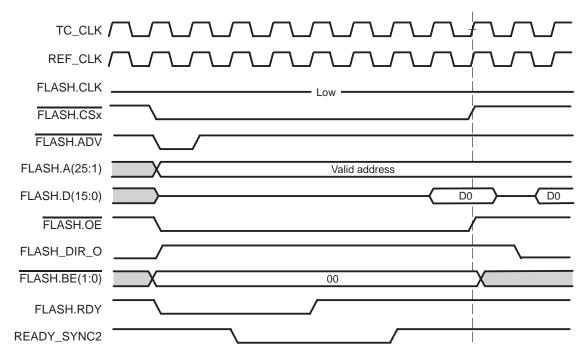

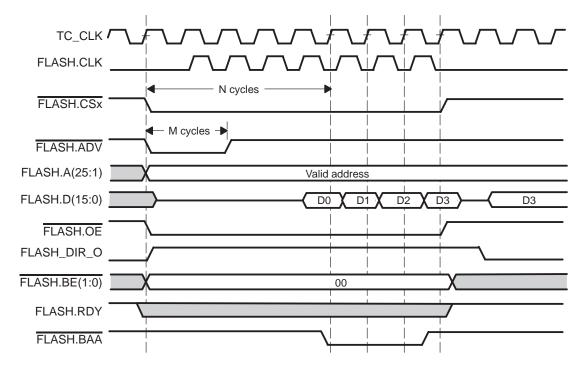

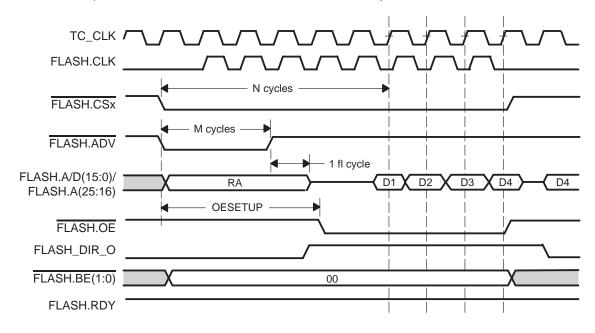

| 3.  | Asynchronous 16-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=4, FCLKDIV=1, OESETUP = 0, OEHOLD = 0, ADVHOLD = 1.<br>Data write-back on the bus after read completion              |

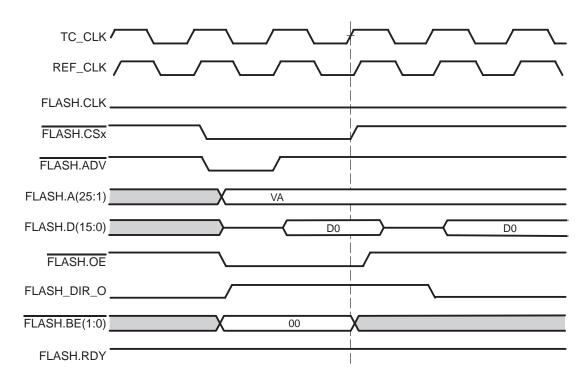

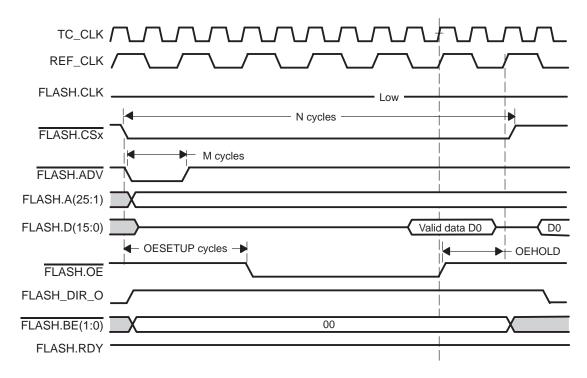

| 4.  | Asynchronous 16-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=0, FCLKDIV=0, OESETUP=0, OEHOLD=0, ADVHOLD=0.<br>Data write-back on the bus after read completion                    |

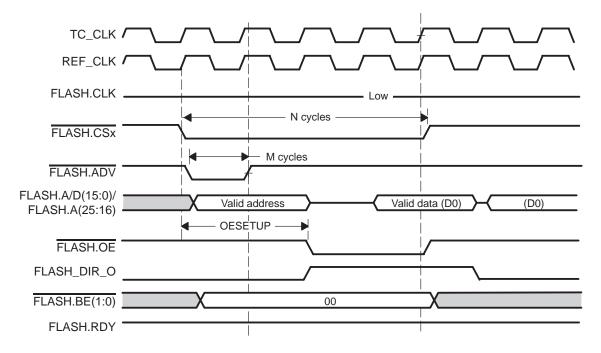

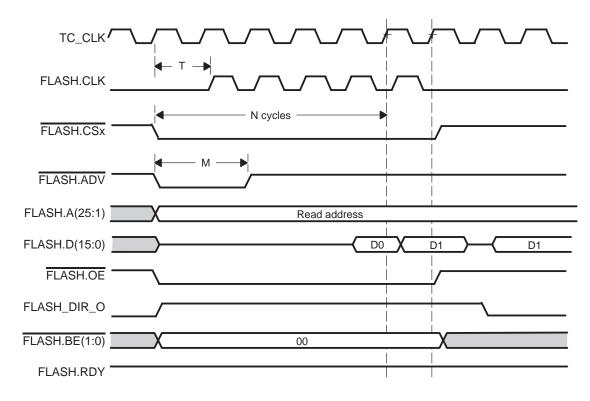

| 5.  | Asynchronous 16-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=4 FCLKDIV=1 OESETUP=3 OEHOLD=0 ADVHOLD=0.<br>Data write-back on the bus after read completion                        |

| 6.  | Asynchronous 16-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=4 FCLKDIV=1 OESETUP = 2 OEHOLD = 1 ADVHOLD = 0.<br>Data write-back on the bus after read completion                  |

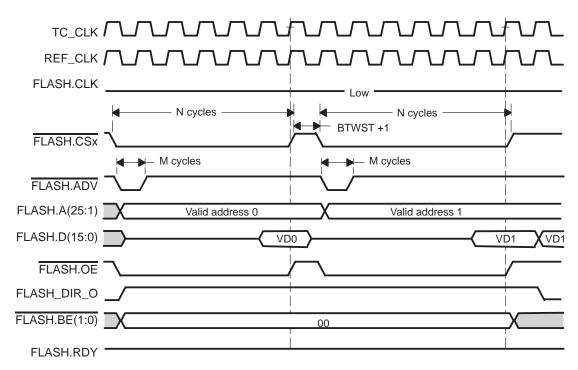

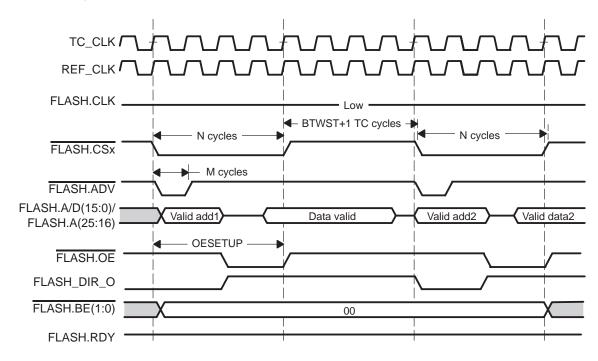

| 7.  | Asynchronous 32-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=4 FCLKDIV=0 OESETUP = 0 OEHOLD = 0 ADVHOLD = 0 BTWST=0<br>BTMODE=0. Data write-back on the bus after read completion |

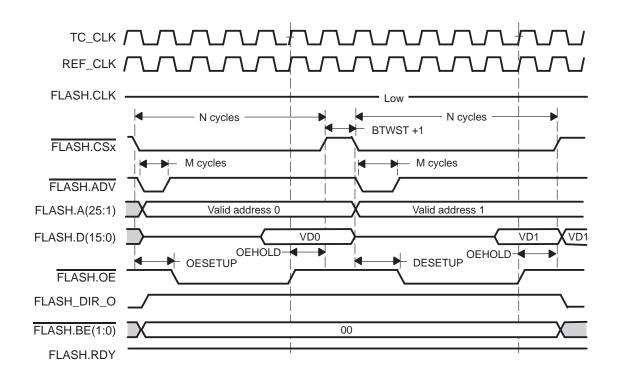

| 8.  | Asynchronous 32-Bit Read Operation on a 16-Bit Width Device.<br>RDWST=4 FCLKDIV=0 OESETUP = 1 OEHOLD = 1 ADVHOLD = 0 BTWST=0<br>BTMODE=0. Data write-back on the bus after read completion |

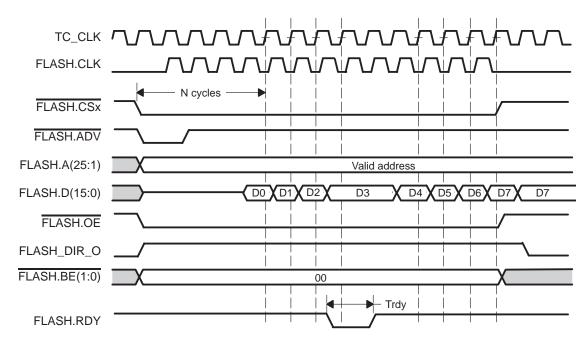

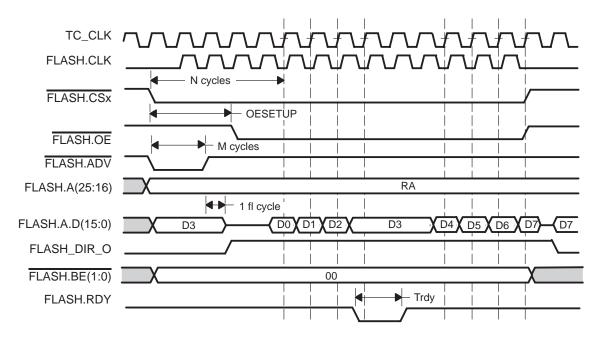

| 9.  | Asynchronous 16-Bit Read Operation with Ready.<br>RDWST=2 FCLKDIV=0 OESETUP = 0 OEHOLD = 0 ADVHOLD = 0.<br>Data write-back on the bus after read completion                                |

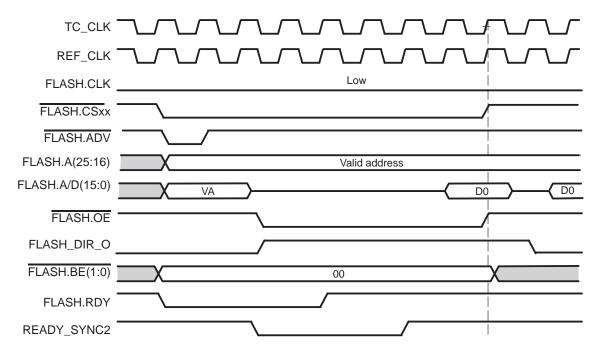

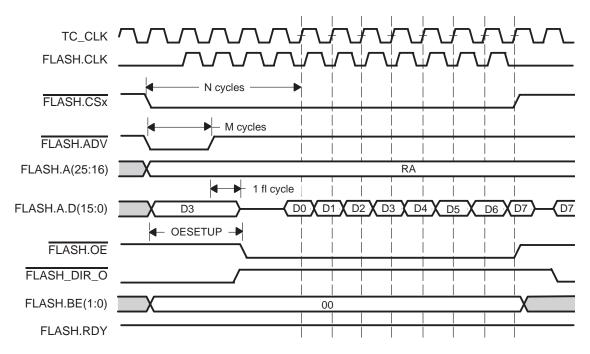

| 10. | Asynchronous 16-Bit Read Operation With Multiplexed Address/Data Bus Memory.<br>RDWST=2 FCLKDIV=0 OESETUP=2 OEHOLD=0 ADVHOLD=0.<br>Data write-back on the bus after read completion        |

| 11. | Asynchronous 32-Bit Read Operation on a 16-Bit Multiplexed Address and Data<br>Memory. RDWST=2 FCLKDIV=0 OESETUP=2 OEHOLD = 0 ADVHOLD = 0                                                  |

| 12. | Asynchronous 16-Bit Read Operation with Ready on 16-Bit Multiplexed<br>Address and Data Memory. RDWST=2 FCLKDIV=0 OESETUP=2<br>OEHOLD = 0 ADVHOLD = 0 BTWST = 0, BTMODE = 0                |

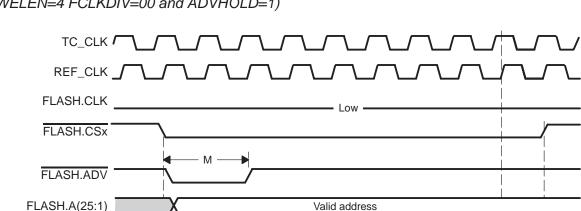

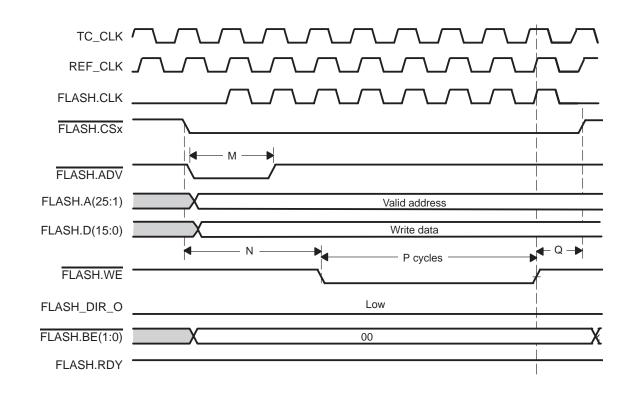

| 13. | Asynchronous 16-Bit Write Operation on a 16-Bit Width Device<br>(WRWST=2, WELEN=4 FCLKDIV=00 and ADVHOLD=1)                                                                                |

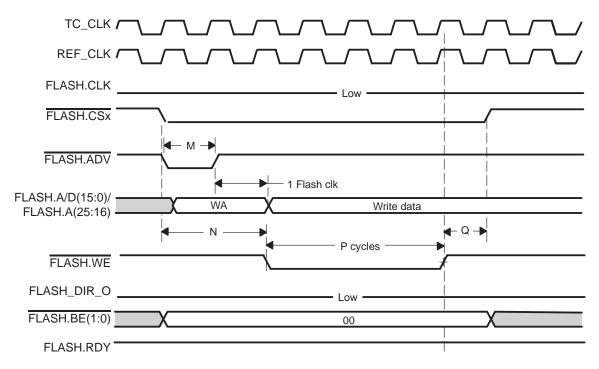

| 14. | Asynchronous 16-Bit Write Operation on a Multiplexed Address/16-Bit Data Bus (WRWST=1, WELEN=3, FCLKDIV=00 and ADVHOLD=0)                                                                  |

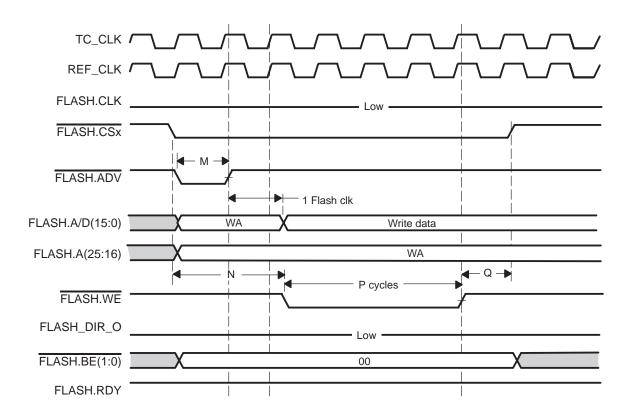

| 15. | Asynchronous 16-Bit Write Operation on a Multiplexed Address/16-Bit Data Bus (WRWST = 1, WELEN = 3, FCLKDIV = 00 and ADVHOLD = 0)                                                          |

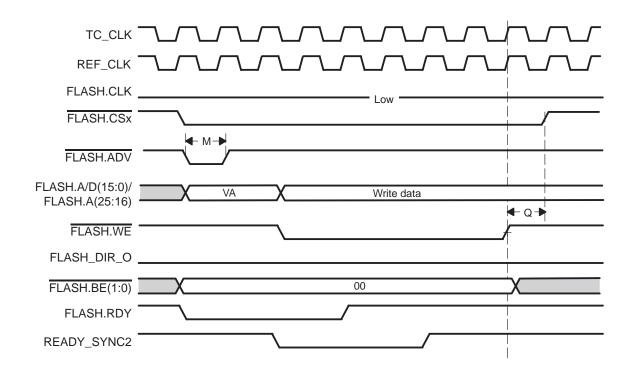

| 16. | Asynchronous 16-Bit Write Operation on 16-Bit Multiplexed Address and Data<br>Memory With Ready (WELEN = 2, WRWST = 0, FCLKDIV = 0)                                                        |

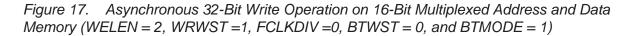

| 17. | Asynchronous 32-Bit Write Operation on 16-Bit Multiplexed Address and Data Memory (WELEN = 2, WRWST = 1, FCLKDIV =0, BTWST = 0, and BTMODE = 1) 46                                         |

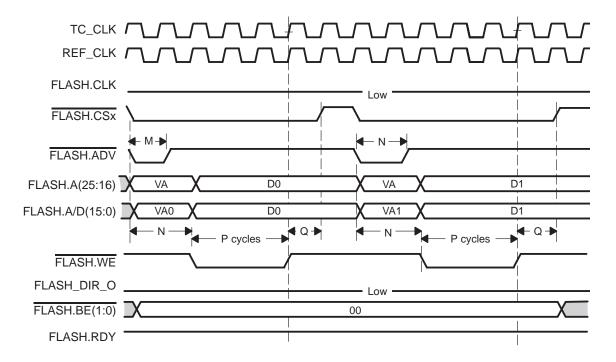

| 18. | Asynchronous Page Mode 4x16-Bit Read Operation on 16-Bit Width Device<br>(RDWST=2, PGWST=0 and FCLKDIV =1, RDMODE=2).<br>Data write-back on the bus after read completion                  |

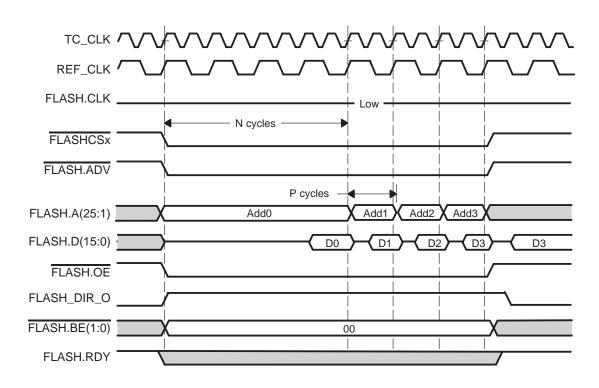

| 19. | Asynchronous Page Mode 8x16-Bit Read With Page Crossing Operation on 16-Bit Width Device (RDWST=2, PGWST=0 FCLKDIV=1, RDMODE=1). Data write-back on the bus after read completion.                                   | 49 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 20. | Mode 4 Synchronous Burst 4x16-Bit Read Operation on 16-Bit Width Device (RDWST=3, FCLKDIV =0, ADVHOLD=0, RDMODE=4). Data write-back on the bus after read completion.                                                | 50 |

| 21. | Mode 5 Synchronous Burst 8x16-Bit Read Operation on 16-Bit Width Device (RDWST=3, FCLKDIV =0, ADVHOLD=0, RDMODE=5). Data write-back on the bus after read completion.                                                |    |

| 22. | Mode 5 Synchronous Burst 2x16-Bit Read Operation on 16-Bit Width Device (RDWST=3, FCLKDIV =0, ADVHOLD=0, RDMODE=5).<br>Data write-back on the bus after read completion                                              | 53 |

| 23. | Mode 5 Synchronous Burst 8x16-Bit Read Operation on Multiplexed<br>Address/Data 16-Bit Width Device (RDWST=2, FCLKDIV =0,<br>ADVHOLD=0, OESETUP = 3, RDMODE=5).<br>Data write-back on the bus after read completion. | 54 |

| 24. | Mode 5 Synchronous Burst 4x16-Bit Read Operation on Multiplexed<br>Address/Data 16-Bit Width Device (RDWST=4, FCLKDIV =0,<br>ADVHOLD=1, OESETUP = 4, RDMODE=5).<br>Data write-back on the bus after read completion. |    |

| 25. | Mode 5 Synchronous Burst 8x16-Bit Read Operation on Multiplexed<br>Address/Data 16-Bit Width Device (RDWST=3, FCLKDIV =0,<br>ADVHOLD=0, OESETUP = 3, RDMODE=5). Data write-back on<br>the bus after read completion. | 56 |

| 26. | Asynchronous 16-Bit Write Operation on a 16-Bit Width Device (RDMODE = 5, WRWST=2, WELEN=4 FCLKDIV=00 and ADVHOLD=1)                                                                                                 |    |

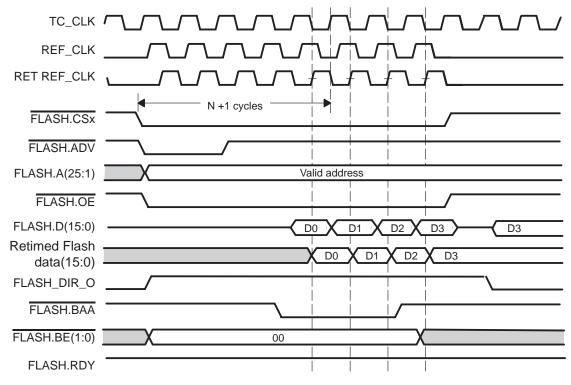

| 27. | Mode 4 Synchronous Burst 4x16-Bit Read Operation on 16-Bit Width Device<br>With Retiming on (RDWST=2, FCLKDIV =0, ADVHOLD=0, RDMODE=4).<br>Data write-back on the bus after read completion.                         | 58 |

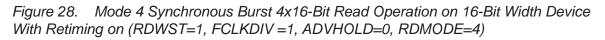

| 28. | Mode 4 Synchronous Burst 4x16-Bit Read Operation on 16-Bit Width Device<br>With Retiming on (RDWST=1, FCLKDIV =1, ADVHOLD=0, RDMODE=4)                                                                               |    |

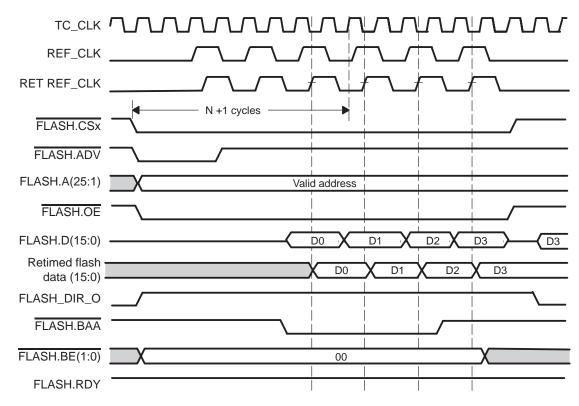

| 29. | Mode 4 Synchronous Burst 4x16-Bit Read Operation on Multiplexed Address/Data 16-Bit Width Device With Retiming on (RDWST=3, FCLKDIV =0, ADVHOLD=0, OESETUP = 3, RMODE=4).                                            | 00 |

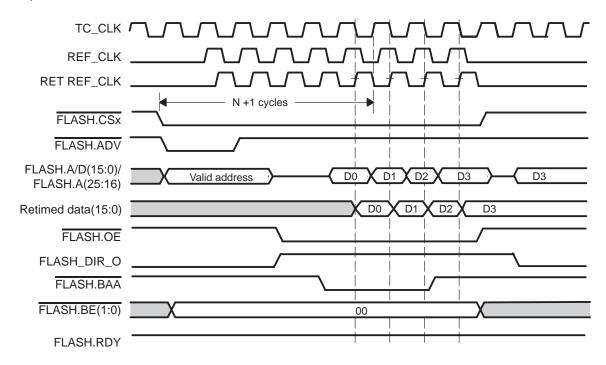

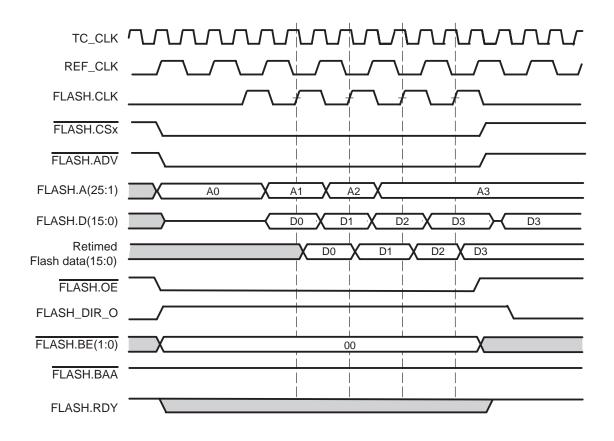

| 30. | Data write-back on the bus after read completion                                                                                                                                                                     |    |

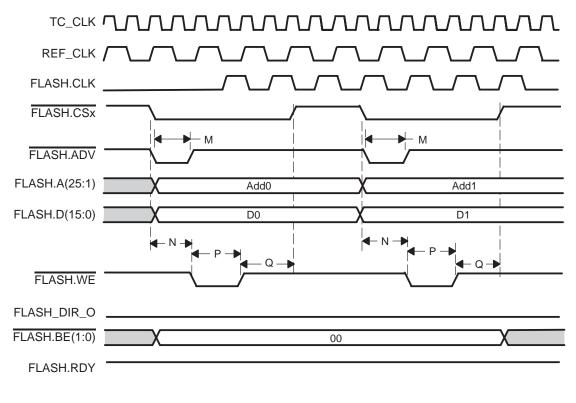

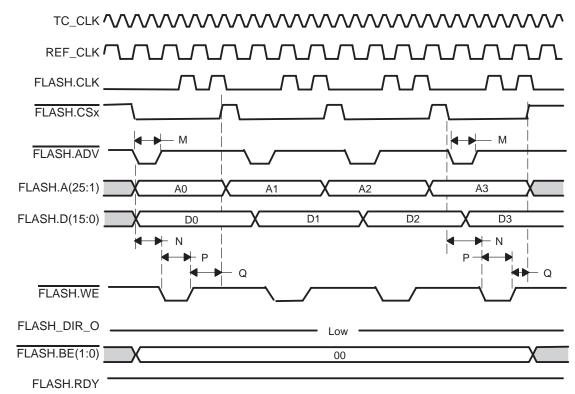

| 31. | Mode 7 Asynchronous Two Successive 16-Bit Write Operations on a<br>16-Bit Width Device (WRWST=0, WELEN=0 FCLKDIV=1 and ADVHOLD=0)                                                                                    |    |

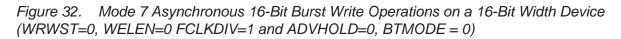

| 32. | Mode 7 Asynchronous 16-Bit Burst Write Operations on a 16-Bit Width Device<br>(WRWST=0, WELEN=0 FCLKDIV=1 and ADVHOLD=0, BTMODE = 0)                                                                                 |    |

| 33. | Mode 7 Asynchronous 16-Bit Burst Write Operations on a 16-Bit Width Device<br>(WRWST=0, WELEN=0 FCLKDIV=1 and ADVHOLD=0,<br>BTMODE = 1 and BTWST = 0)                                                                |    |

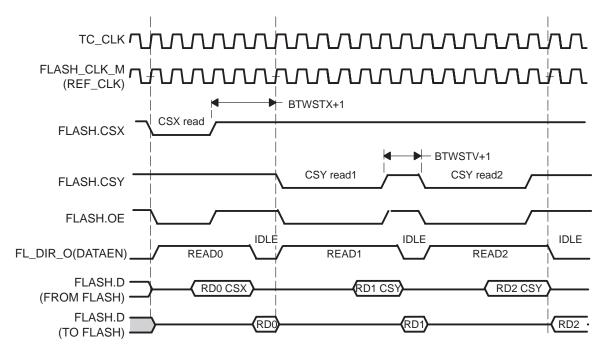

| 34. | Wait States During a Read to Read Operation (BTWST (CSX) = 2 and<br>BTWST (CSY) = 1, BTMODE = 0)                                                                                                                     | 65 |

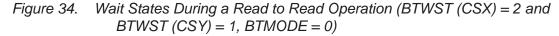

| 35. | Wait States During a Read to Write Transition<br>(BTWST(CSX) = 3 BTWST (CSY) = 2, BTMODE = 0)                                                                                                                        |    |

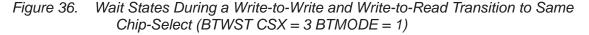

| 36. | Wait States During a Write-to-Write and Write-to-Read Transition to Same<br>Chip-Select (BTWST CSX = 3 BTMODE = 1)                                                                                                   | 67 |

|     |                                                                                                                                                                                                                      |    |

# Figures

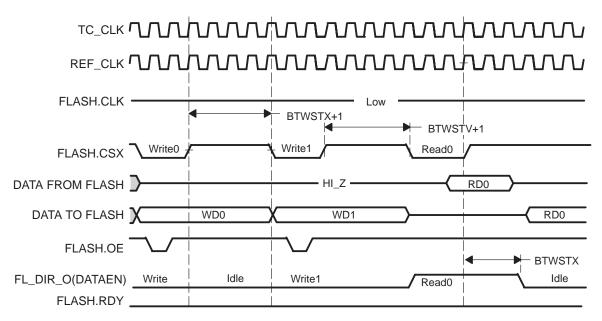

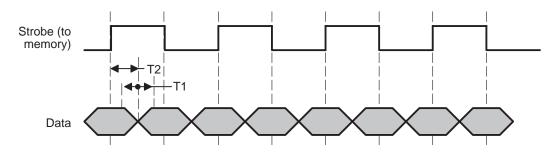

| 37. | EMIFF DDR Data Reads (with respect to DLL)  | 77 |

|-----|---------------------------------------------|----|

|     | EMIFF DDR Data Writes (with respect to DLL) |    |

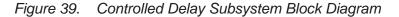

| 39. | Controlled Delay Subsystem Block Diagram    | 78 |

| 40. | OCP-I Block Diagram 8                       | 33 |

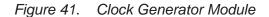

| 41. | Clock Generator Module                      | 25 |

| 42. | OMAP 3.2 MPUI and MPUI Port Environment 16  | 34 |

| 43. | OMAP 3.2 Platform TI Peripheral Bridge 19   | 92 |

# **Tables**

| 1.  | Idle Time Between Different Bus Access Transitions (BTMODE = 0)                          | 65 |

|-----|------------------------------------------------------------------------------------------|----|

| 2.  | Idle Time Between Different Bus Access Transitions (BTMODE = 1)                          | 67 |

| 3.  | CS1 and CS2 Configuration Register Reset Value                                           | 70 |

| 4.  | Command List                                                                             | 74 |

| 5.  | SDRAM AC Parameter Descriptions                                                          | 76 |

| 6.  | EMIF Fast Controlled-Delay Block Programming                                             | 80 |

| 7.  | OCP-T1/OCP-T2 Registers                                                                  |    |

| 8.  | OCP Priority Registers 1 and 2(OCPT1_PRIOR and OCPT2_PRIOR)                              | 85 |

| 9.  | OCP-T1 and OCP-T2 Priority Time-Out Registers 1 (OCPT1_PTOR1 and OCPT2_PTOR1)            | 86 |

| 10. | OCP-T1 and OCP-T2 Priority Time-Out Registers 2 (OCPT1_PTOR2 and OCPT2_PTOR2)            |    |

| 11. | OCP-T1 and OCP-T2 Priority Time-Out Registers 3 (OCPT1_PTOR3 and OCPT2_PTOR3)            |    |

| 12. | OCP-T1 and OCP-T2 Abort Time-Out Registers (OCPT1 ATOR and                               |    |

|     | OCPT2_ATOR)                                                                              | 87 |

| 13. | OCP-T1 and OCP-T2 Abort Address Registers—Access Address (OCPT1_AADDR and OCPT2_AADDR)   | 88 |

| 14. | OCP-T1 and OCP-T2 Abort Type Registers—Access Address<br>(OCPT1_ATYPER and OCPT2_ATYPER) | 88 |

| 15. | OCP Target Configuration Register (OCPT_CONFIG_REG)                                      | 89 |

| 16. | EMIFS Registers                                                                          |    |

| 17. | EMIFS Priority Register (EMIFS_PRIOR)                                                    | 90 |

| 18. | EMIFS Configuration Register (EMIFS_CONFIG)                                              | 91 |

| 19. | EMIFS Chip-Select Configuration Registers (EMIFS_CCS0, EMIFS_CCS1,,EMIFS_CCS3)           | 91 |

| 20. | EMIFS Chip-Select Configuration Register RDMODE Field Definition                         | 94 |

| 21. | EMIFS Time-Out Register 1 (EMIFS_PTOR1)                                                  | 94 |

| 22. | EMIFS Time-Out Register 2 (EMIFS_PTOR2)                                                  | 94 |

| 23. | EMIFS Time-Out Register 3 (EMIFS_PTOR3)                                                  | 94 |

| 24. | EMIFS Dynamic Wait States Control Register (EMIFS_DWS)                                   | 95 |

| 25. | Read and Write Access Handshaking                                                        | 97 |

| 26. | EMIFS Abort Address Register (EMIFS_AADDR)                                               | 97 |

| 27. | EMIFS Abort Type Register (EMIFS_ATYPER)                                                 | 97 |

| 28. | EMIFS Abort Time-Out Register (EMIFS_ATOR)                                               | 98 |

| 29. | Advanced EMIFS Chip-Select Configuration Registers (EMIFS_ACS0, EMIFS_ACS1,,EMIFS_ACS3)  | 98 |

| 30. | EMIFF Registers                                                                          |    |

|     |                                                                                          |    |

Tables

| 31. | EMIFF Enable and Disable TC Doubler Feature EMIFF_DOUBLER            |     |

|-----|----------------------------------------------------------------------|-----|

| 32. | EMIFF Priority Register (EMIFF_PRIOR)                                |     |

| 33. | EMIFF SDRAM Configuration Register (EMIFF_CONFIG)                    |     |

| 34. | EMIFF SDRAM Register Memory/Data Bus Size                            |     |

| 35. | Frequency Range (SDRAM)                                              |     |

| 36. | Frequency Range (Mobile DDR)                                         |     |

| 37. | AC Timing When NEW_SYS_FREQ (bit 3 of EMIFF_CONFIG2) = 0             |     |

| 38. | AC Timing When NEW_SYS_FREQ (bit 3 of EMIFF_CONFIG2) = 1             |     |

| 39. | EMIFF SDRAM MRS Register (legacy for OMAP3.1)                        |     |

| 40. | EMIFF SDRAM Configuration Register 2 (EMIFF_SDRAM_CONFIG_2_REG)      |     |

| 41. | DLL WRD Control Register (EMIFF_DLL_WRD_CTRL)                        |     |

| 42. | DLL WRD Status Register (EMIFF_DLL_WRD_STAT)                         |     |

| 43. | EMIFF SDRAM MRS_NEW Register (EMIFF_MRS_NEW)                         |     |

| 44. | EMIFF DDR SDRAM Register (EMIFF_EMRS0)                               |     |

| 45. | EMIFF Low Power SDRAM Register (EMIFF_EMRS1)                         |     |

| 46. | EMIFF SDRAM Operation Register (EMIFF_OP)                            |     |

| 47. | EMIFF SDRAM Manual Command Register (EMIFF_CMD)                      |     |

| 48. | EMIFF Dynamic Arbitration Priority Time-Out Register 1 (EMIFF_PTOR1) |     |

| 49. | EMIFF Dynamic Arbitration Priority Time-Out Register 2 (EMIFF_PTOR2) |     |

| 50. | EMIFF Dynamic Arbitration Priority Time-Out Register 3 (EMIFF_PTOR3) |     |

| 51. | EMIFF Abort Address Register (EMIFF_AADDR)                           |     |

| 52. | EMIFF Abort Type Register (EMIFF_ATYPER)                             |     |

| 53. | DLL LRD Status Register (EMIFF_DLL_LRD_STAT)                         |     |

| 54. | DLL URD Control Register (EMIFF_DLL_URD_CTRL)                        |     |

| 55. | DLL URD Status Register (EMIFF_DLL_URD_STAT)                         |     |

| 56. | EMIFF SDRAM Register (EMIFF_EMRS2)                                   |     |

| 57. | DLL LRD Control Register (EMIFF_DLL_LRD_CTRL)                        |     |

| 58. | OCP Registers                                                        |     |

| 59. | OCPI Address Fault Register (OCPI_AFR)                               |     |

| 60. | OCPI Master Command Fault Register (OCPI_MCFR)                       |     |

| 61. | Master Command Register Supported Commands                           |     |

| 62. | OCPI Type of Abort Register (OCPI_ATYPER)                            |     |

| 63. | OCPI Protection Register (OCPI_PR)                                   |     |

| 64. | OCPI Dynamic Power Down (DYNAMIC_POWER_DOWN) Register                |     |

| 65. | TC Abort Management Registers                                        | 120 |

| 66. | Reserved Space Fault Type Register (RES_SPC_ATYPER)                  |     |

| 67. | Reserved Space Fault Address Register (RES_SPC_ADDR)                 |     |

| 68. | OMAP 3.2 Hardware Engine Clocking Modes                              | 125 |

| 69. | MPU Core Registers                                                   |     |

| 70. | MPU Core Clock Control Prescaler Selection Register (ARM_CKCTL)      |     |

| 71. | MPU Core Idle Enable Control Register 1 (ARM_IDLECT1)                |     |

| 72. | MPU Core Idle Enable Control Register 2 (ARM_IDLECT2)                | 146 |

| 73. | MPU Core Restore Power Delay Register (ARM_EWUPCT)                   | 148 |

| 74. | Master Software Reset Register (ARM_RSTCT1)                          | 148 |

| 75.  | Peripherals Reset Register (ARM_RSTCT2)                         | 149 |

|------|-----------------------------------------------------------------|-----|

| 76.  | MPU Core Clock Reset Status Register (ARM_SYSST)                |     |

| 77.  | MPU core Clock Out Definition Register (ARM_CKOUT1)             |     |

| 78.  | MPU core Reserved Register (ARM_CKOUT2)                         |     |

| 79.  | MPU core Idle Enable Control Register 3 (ARM_IDLECT3)           |     |

| 80.  | DSP Core Registers                                              |     |

| 81.  | DSP Core Clock Control Prescaler Selection Register (DSP_CKCTL) |     |

| 82.  | DSP Core Idle Enable Control Register 1 (DSP_IDLECT1)           |     |

| 83.  | DSP Core Idle Enable Control Register 2 (DSP_IDLECT2)           |     |

| 84.  | DSP Core Reserved Register 1 (DSP_EWUPCT)                       |     |

| 85.  | DSP Core Reserved Register 2 (DSP_RSTCT1)                       |     |

| 86.  | DSP Core Peripherals Reset Register (DSP_RSTCT2)                |     |

| 87.  | DSP Core Clock Reset Status Register (DSP_SYSST)                |     |

| 88.  | DSP Core Reserved Register 3 (DSP_CKOUT1)                       |     |

| 89.  | DSP Core Reserved Register 4 (DSP_CKOUT2)                       |     |

| 90.  | DPLL Registers                                                  |     |

| 91.  | DPLL1 Control Register (DPLL1_CTL_REG)                          |     |

| 92.  | DPLL2 Control Register (DPLL2_CTL_REG)                          |     |

| 93.  | Data Swap for 32-Bit Access for MPUI Port                       |     |

| 94.  | Data Swap for 16-Bit Access for MPUI Port                       |     |

| 95.  | MPUI Port Registers                                             |     |

| 96.  | MPUI Port Interrupt Register (APIRI)                            |     |

| 97.  | MPUI Port Control/Status Register (APIRS)                       |     |

| 98.  | MPUI Registers                                                  |     |

| 99.  | MPUI Control Register (MPUI_CONTROL)                            |     |

| 100. | Debug Address Register (DEBUG_ADDRESS)                          |     |

| 101. | Debug Data Register (DEBUG_DATA)                                |     |

| 102. | Debug Flag Register (DEBUG_FLAG)                                |     |

| 103. | MPUI Status Register (MPUI_STATUS)                              |     |

| 104. | DSP Core Status Register (DSP_STATUS)                           |     |

| 105. | DSP Core Boot Configuration Register (DSP_BOOT_CONFIG)          |     |

| 106. | MPUI Port RAM Configuration Register (DSP_MPUI_CONFIG)          |     |

| 107. | DSP Core Miscellaneous (DSP_MISC)                               |     |

| 108. | MPUI Enhanced Control Register (MPUI_ENHANCED_CTRL)             |     |

| 109. | DSP Core SARAM Configuration Map                                |     |

| 110. | DSP Core Endianism Register (DSP_ENDIAN_CONV)                   | 185 |

| 111. | Mailbox Registers                                               |     |

| 112. | MPU to DSP Mailbox 1A Register (MPU2DSP1A)                      |     |

| 113. | MPU to DSP Mailbox 1B Register (MPU2DSP1B)                      |     |

| 114. | DSP to MPU Mailbox 1A Register (DSP2MPU1A)                      |     |

| 115. | DSP to MPU Mailbox 1B Register (DSP2MPU1B)                      |     |

| 116. | DSP to MPU Mailbox 2A Register (DSP2MPU2A)                      |     |

| 117. | DSP to MPU Mailbox 2B Register (DSP2MPU2B)                      |     |

| 118. | MPU to DSP Mailbox 1 Flag Register (MPU2DSP1_FLAG)              |     |

| 110. |                                                                 | 100 |

| Tables |  |

|--------|--|

|--------|--|

| 119. | DSP to MPU Mailbox 1 Flag Register (DSP2MPU1_FLAG)  | 190 |

|------|-----------------------------------------------------|-----|

| 120. | DSP to MPU Mailbox 2 Flag Register (DSP2MPU2_FLAG)  |     |

| 121. | MPU to DSP Mailbox 2A Register (MPU2DSP2A)          |     |

| 122. | MPU to DSP Mailbox 2B Register (MPU2DSP2B)          |     |

| 123. | MPU to DSP Mailbox 2 Flag Register (MPU2DSP2_FLAG)  | 191 |

| 124. | TIPB Registers                                      | 195 |

| 125. | TIPB Control Register (RHEA_CNTL)                   | 196 |

| 126. | TIPB Allocation Control Register (RHEA_BUS_ALLOC)   | 197 |

| 127. | MPU Core TIPB Control Register (ARM_RHEA_CNTL)      | 198 |

| 128. | Enhanced TIPB Control Register (ENH_RHEA_CNTL)      | 199 |

| 129. | Debug Address Register (DEBUG_ADDRESS)              | 199 |

| 130. | Debug Data LSB Register (DEBUG_DATA_LSB)            | 199 |

| 131. | Debug Data MSB Register (DEBUG_DATA_MSB)            | 200 |

| 132. | Debug Control Signals Register (DEBUG_CTRL_SIGNALS) | 200 |

| 133. | Access Control Register (ACCESS_CNTL)               | 202 |

| 134. | Document Revision History                           | 204 |

This document introduces and briefly defines the main features of the OMAP3.2 subsystem of the OMAP5912 multimedia processor.

# 1 Introduction

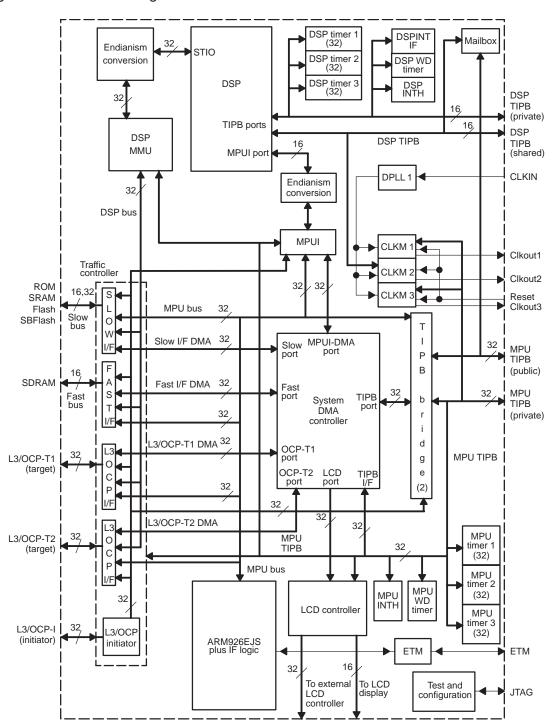

Figure 1 shows the OMAP5912 OMAP3.2 gigacell.

Figure 1. OMAP3.2 Gigacell

OMAP3.2 Subsystem

SPRU749B

16

# 2 OMAP3.2 Features

The OMAP3.2 includes the following features:

- □ ARM926EJS megacell, including:

- ARM926EJS, running at a maximum frequency of 192 MHz

- MMU with translation lookaside buffer (TLBx)

- L1 16K-byte, four-way, set-associative instruction cache

- L1 8K-byte, four-way, set-associative data cache with write buffer

- MPU core interrupt handler level 1

- □ Embedded trace macrocell module, ETM version 2.a, in a 13-bit mode configuration or in a 17-bit demultiplexed mode configuration

- DSP core megacell rev 2.0a+, including:

- Embedded ICE emulator interface through JTAG port

- TMS320C55x (C55x) DSP core rev 2.1, running at a maximum of 192 MHz

- L1 cache (24K bytes)

- 16K-byte, two-way, set-associative instruction cache (on the OMAP5912 prototype, one wait state is introduced in case of discontinuity)

- 2 X 4K-byte RAM set for instruction

- DARAM 64K-byte, zero wait state, 32-bit organization

- SARAM 96K-byte, zero wait state, 32-bit organization

- PDROM (32K bytes)

- DSP/System DMA controller: six physical channels, five ports

- DSP core trace module

- Hardware accelerators motion estimation (ME), discrete/inverse discrete cosine transform (DCT/IDCT), and pixel interpolation (PI)

- DSP core interrupt handler level 1 in the C55x DSP core

- DSP core MMU

- DSP core level 2 interrupt handler, which enables connection to 16 additional interrupt lines outside OMAP. The priority of each interrupt line is controlled by software.

- DSP core interrupt interface, which enables connection to the interrupt lines coming out of the level 2 interrupt handler and the interrupt lines requiring more priority. The outcome interrupt of this module is then connected to the DSP core megacell to be processed by the DSP core. This module mainly ensures that all interrupts going to the DSP core megacell are level-sensitive.

- DSP core peripherals:

- 3 x 16-bit DSP core private timers

- 1 x 16-bit DSP core private watchdog

- Mailboxes:

- Four mailboxes are implemented:

- Two read/write accessible by MPU core, read-only by the DSP core

- Two read/write accessible by the DSP core, read-only by the MPU core

Each mailbox is implemented with 2 x 16-bit registers. When a write is done into a register by one processor, it generates an interrupt, released by the read access of the other processor.

- MPU core peripherals

- 3 x 32-bit private timers; their clock is either the OMAP3.2 reference input clock or the divided MPU core clock.

- 1 x 16-bit private watchdog; can be configured as a 16-bit generalpurpose timer by software. Its clock is the OMAP3.2 reference input clock divided by 14.

- External LCD controller support in addition to the OMAP LCD controller

- LCD controller with its own tearing-effect logic

- Memory traffic controller

- External Memory Interface Fast (EMIFF) is a memory interface that enables 16-bit data SDRAM memory access at 96-MHz maximum frequency. It supports connection to a128M-byte maximum of SDRAM. The address width is 16 bits, and two bank selection bits are also provided. The OMAP5912 chip requires interfacing with a maximum of four banks of 64M x 16-bit SDRAM memory with DDR capability.

External Memory Interface Slow (EMIFS) connects external device memories (such as common flash and SRAM memories) at 80-MHz maximum frequency. This interface is also used internally to connect the boot ROM. This interface enables 16-bit data accesses and provides four chip-selects. Each chip-select is able to support up to 64M bytes of address space through a 25-bit address bus.

#### Note:

At the OMAP5912 level, two chip-selects can be split in half by configuration to provide four chip-selects. This enables OMAP5912 to provide up to six chip-selects, supporting up to 32M bytes of address space on four chip-selects and up to 64M bytes on two chip-selects.