# OMAP5912 Multimedia Processor Display Interface Reference Guide

Literature Number: SPRU764B October 2004

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated

# Preface

# **Read This First**

# About This Manual

This document describes the display interface of the OMAP5912 multimedia processor.

# Notational Conventions

This document uses the following conventions.

□ Hexadecimal numbers are shown with the suffix h. For example, the following number is 40 hexadecimal (decimal 64): 40h.

# **Related Documentation From Texas Instruments**

Documentation that describes the OMAP5912 device, related peripherals, and other technical collateral, is available in the OMAP5912 Product Folder on TI's website: www.ti.com/omap5912.

# Trademarks

OMAP and the OMAP symbol are trademarks of Texas Instruments.

3

# Contents

| 1 | Overv | view   |                                                         |

|---|-------|--------|---------------------------------------------------------|

| 2 | LCD   | Module |                                                         |

|   | 2.1   | LCD C  | ontroller Environment                                   |

|   | 2.2   | LCD C  | ontroller Operation                                     |

|   |       |        | Frame Buffer                                            |

|   |       |        | 16-BPP Mode (TFT)                                       |

|   |       |        | 12-BPP Mode                                             |

|   |       |        | 8-BPP Mode                                              |

|   |       |        | 4-BPP Mode                                              |

|   |       |        | 2-BPP Mode                                              |

|   |       |        | 1-BPP Mode                                              |

|   |       |        | Palette                                                 |

|   |       |        | Dithering Logic                                         |

|   |       |        | The Output FIFO                                         |

|   |       |        | LCD Inputs                                              |

|   |       | 2.2.1  | Control Blocks                                          |

|   |       |        | Timing                                                  |

|   |       |        | Pixel Clock                                             |

|   |       |        | Line Clock (HSYNC)                                      |

|   |       |        | Frame Clock (VSYNC) 32                                  |

|   |       |        | ac-Bias                                                 |

|   |       | 2.2.2  | Interrupts                                              |

|   |       |        | Interrupt Sources                                       |

|   |       |        | Tearing Effect                                          |

|   |       | 2.2.3  | LCD Subpanel Display Support                            |

|   |       |        | Principle                                               |

|   | 2.3   | •      | ers                                                     |

|   |       | 2.3.1  | LCD Control Register (LcdControl) 37                    |

|   |       |        | LCD Enable (LcdEn) 40                                   |

|   |       |        | LCD Monochrome (LcdBW) 40                               |

|   |       |        | LCD Vertical Synchronization Mask (VSYNC_mask) 41       |

|   |       |        | LCD Done Mask (DoneMask) 41                             |

|   |       |        | LCD Loading Mask (LoadMask) 41                          |

|   |       |        | Line Interrupt Mask (line_int_nirq_mask) 42             |

|   |       |        | Line Interrupt Mask (Dedicated Line) (line_int_mask) 42 |

|       | LCD TFT (LcdTFT)                                   | 42 |

|-------|----------------------------------------------------|----|

|       | LCD Control Bit 0 (LCDCB0)                         |    |

|       | Mono 8 Bit Mode (M8B)                              |    |

|       | Line Interrupt Clear Select Bit (line_int_clr_sel) |    |

|       | Gated Pixel Clock (pxl_gated)                      |    |

|       | FIFO DMA Request Delay (FDD)                       |    |

|       | Palette Loading (PLM)                              |    |

|       | LCD Control Bit 1 (LCDCB1)                         |    |

|       | TFT Alternate Signal Mapping (TFT Map)             |    |

|       | 16 BPP STN Mode (565 STN)                          |    |

| 2.3.2 | LCD Timing 0 Register (LcdTiming0)                 |    |

| 21012 | Pixels-Per-Line (PPL)                              |    |

|       | Horizontal Synchronization Pulse Width (HSW)       |    |

|       | Horizontal Front Porch (HFP)                       |    |

|       | Horizontal Back Porch (HBP)                        |    |

| 2.3.3 | LCD Timing 1 Register (LcdTiming1)                 |    |

|       | Lines Per Panel (LPP)                              |    |

|       | Vertical Synchronization Pulse Width (VSW)         |    |

|       | Vertical Front Porch (VFP)                         |    |

|       | Vertical Back Porch (VBP)                          |    |

| 2.3.4 | LCD Timing 2 Register (LcdTiming2)                 |    |

|       | Pixel Clock Divider (PCD)                          |    |

|       | ac-Bias Pin Frequency (ACB)                        |    |

|       | ac-Bias Line Transitions Per Interrupt (ACBI)      |    |

|       | Invert VSYNC (IVS)                                 |    |

|       | Invert HSYNC (IHS)                                 | 59 |

|       | Invert Pixel Clock (IPC)                           | 59 |

|       | Invert Output Enable (IEO)                         | 60 |

|       | HSYNC/VSYNC Rise or Fall Programmable (or not)(RF) | 60 |

|       | HSYNC/VSYNC ON or OFF (ON_OFF)                     | 62 |

| 2.3.5 | LCD Controller Status Register (LcdStatus)         | 63 |

|       | Frame Done (Done) (Read-Only)                      | 64 |

|       | VSYNC Interrupt (VS) (Read/Clear-Only)             |    |

|       | Frame Synchronization Lost (Sync_lost) (Read-Only) |    |

|       | ac-Bias Count Status (ABC) (Read/Clear-Only)       |    |

|       | Line Interrupt (line_int) (Read/Clear-Only)        |    |

|       | FIFO Underflow Status (FUF) (Read-Only)            |    |

|       | Loaded Palette (LP) (Read/Clear-Only)              |    |

| 2.3.6 | LCD Subpanel Display Register (LcdSubpanel)        |    |

|       | Default Pixel Data (DPD)                           |    |

|       | Line-per-Panel Threshold (LPPT)                    |    |

|       | High Or Low Signal (HOLS)                          |    |

|       | Subpanel Enable (SPEN)                             |    |

| 2.3.7 | Line Interrupt Register (LcdLineInt)               |    |

| 2.3.8 | Display Status Register (LcdDisplayStatus)         | 71 |

5

#### Contents

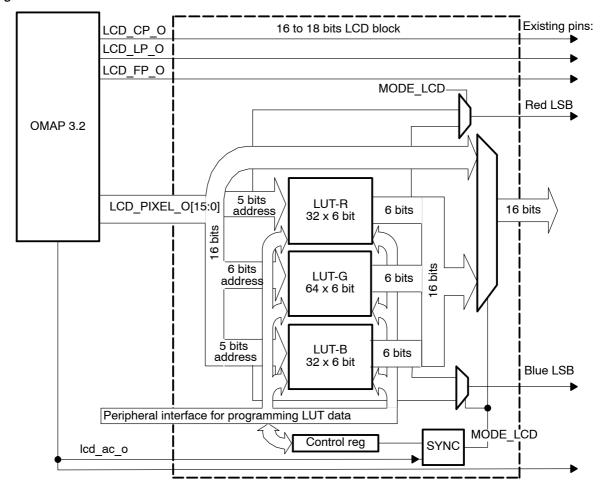

| 3 | LCD I | Data Conversion Module | 72 |

|---|-------|------------------------|----|

|   | 3.1   | Data Conversion        | 73 |

|   | 3.2   | Software Interface     | 76 |

|   | 3.3   | Bus Interface          | 78 |

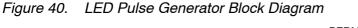

| 4 | LED I | Pulse Generator        | 78 |

|   | 4.1   | Features               | 79 |

|   | 4.2   | LPG Design             | 79 |

|   | 4.3   | LPG Power Management   | 79 |

|   | 4.4   | LPG Registers          | 80 |

# Figures

| 1  | LCD Controller                                                       | 10 |

|----|----------------------------------------------------------------------|----|

| 2  | Data Flow from Microprocessor to Display                             |    |

| 3  | LCD Controller Operation Overview (Passive and Active Display Modes) | 15 |

| 4  | 16-Entry Palette/Buffer Format (1, 2, 4, 12, 16 BPP)                 |    |

| 5  | 256-Entry Palette/Buffer Format (8 BPP)                              |    |

| 6  | 16-BPP Data Memory Organization (TFT Mode Only)—Little Endian        |    |

| 7  | 12-BPP Data Memory Organization—Little Endian                        |    |

| 8  | 8-BPP Data Memory Organization                                       |    |

| 9  | 4-BPP Data Memory Organization                                       |    |

| 10 | 2-BPP Data Memory Organization                                       |    |

| 11 | 1-BPP Data Memory Organization                                       |    |

| 12 | Passive Monochrome Mode                                              |    |

| 12 | Passive Color Mode                                                   |    |

| 13 | LCD Controller Data Paths                                            |    |

| 15 | Input and Output Clocks                                              |    |

| 16 | Active (TFT) Mode Timing                                             |    |

| 17 | Line Interrupt Output Signal Transitions                             |    |

| 18 | LCD Control Register (LcdControl)                                    |    |

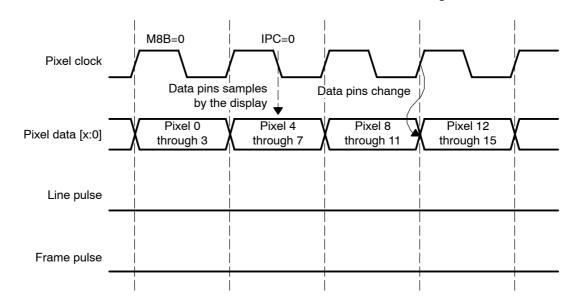

| 19 | Monochrome Passive Mode Pixel Clock and Data Pin Timing              |    |

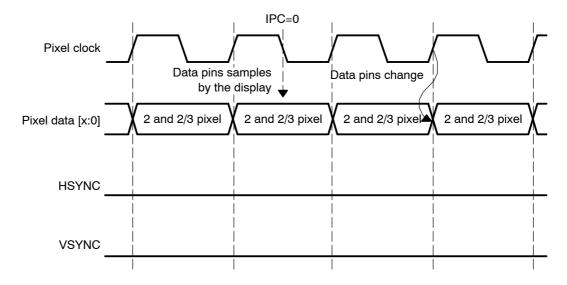

| 20 | Color Passive Mode Pixel Clock and Data Pin Timing                   |    |

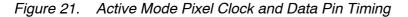

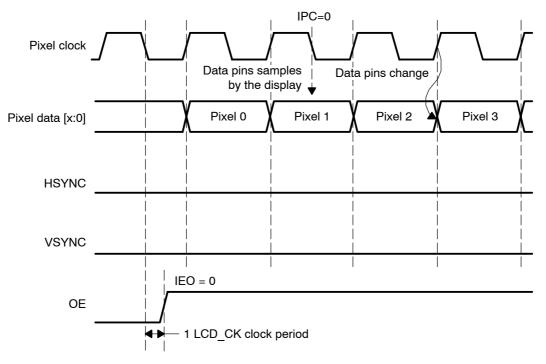

| 21 | Active Mode Pixel Clock and Data Pin Timing                          |    |

| 22 | TFT Alternate Signal Mapping Output                                  |    |

| 23 | 16 BPP STN Mode                                                      |    |

| 24 | LCD Timing 0 Register (LcdTiming0)                                   |    |

| 25 | LCD Timing 1 Register (LcdTiming1)                                   | 51 |

| 26 | Active Matrix Timing                                                 |    |

| 27 | Passive Mode End of Frame Timing                                     |    |

| 28 | Passive Mode Beginning of Frame Timing                               |    |

| 29 | LCD Timing 2 Register (LcdTiming2)                                   |    |

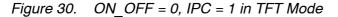

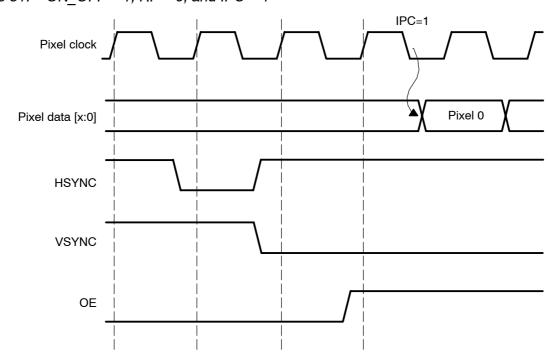

| 30 | ON_OFF = 0, IPC = 1 in TFT Mode                                      |    |

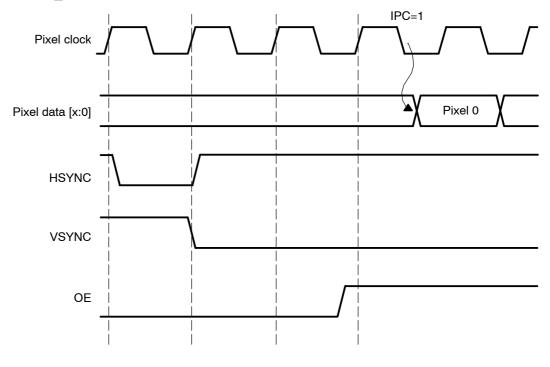

| 31 | ON OFF = 1, RF = 0, and IPC = 1                                      |    |

| 32 | LCD Status Register (LcdStatus)                                      |    |

| 33 | Line Interrupt Path                                                  |    |

| 34 | LCD Subpanel Register (LcdSubpanel)                                  |    |

| 35 | Subpanel Display: SPEN = 1, HOLS = 1                                 |    |

| 36 | Subpanel Display: SPEN = 1, HOLS = 0                                 |    |

| 37 | Line Interrupt Register (LcdLineInt)                                 |    |

| 38 | Display Status Register (LcdDisplayStatus)                           |    |

| 39 | 16-Bit to 18-Bit LCD Data Block                                      |    |

| 40 | LED Pulse Generator Block Diagram                                    | 78 |

# **Tables**

| 1        | Interface to LCD Panel Signal Descriptions                               | 10   |

|----------|--------------------------------------------------------------------------|------|

| 2        | Bits-Per-Pixel Encoding for Palette Entry 0 Buffer                       |      |

| 2        | Frame Buffer Size According to BPP                                       |      |

| 4        | Color/Grayscale Intensities and Modulation Rates                         |      |

| 4<br>5   | Number of Colors/Shades of Gray Available on Screen                      |      |

| 6        | Number of Pixels Displayed per Pixel Clock                               |      |

| 7        | LCD Controller Registers                                                 |      |

| 7<br>8   | LCD Control Register (LcdControl) Bit Descriptions                       |      |

| 9        | LCD Controller Data Pin Utilization for Mono/Color Passive/Active Panels |      |

| 9<br>10  | Control Bit 0 and Control Bit 1 Mapping by Display Types                 |      |

| 11       | 12-Bit STN Data in Frame Buffer                                          |      |

| 12       | 16-Bit STN Data in Frame Buffer                                          |      |

| 12       | LCD Timing 0 Register (LcdTiming0) Bit Descriptions                      |      |

| 13       | LCD Timing 1 Register (LcdTiming0) Bit Descriptions                      |      |

| 14<br>15 |                                                                          |      |

| 15<br>16 | LCD Timing 2 Register (LcdTiming2) Bit Descriptions                      |      |

| 10       |                                                                          |      |

| 18       | LCD Status Register (LcdStatus) Bit Descriptions                         |      |

| 18<br>19 | LCD Subpanel (LcdSubpanel) Bit Descriptions                              |      |

|          | Line Interrupt Register (LcdLine Int) Bit Descriptions                   |      |

| 20       | Line Interrupt Register (LcdDisplayStatus) Bit Descriptions              |      |

| 21       | RGB Lookup Table Size                                                    |      |

| 22       | LCD 16-Bit to 18-Bit Conversion                                          |      |

| 23       | Top Level I/O Signals                                                    |      |

| 24       |                                                                          |      |

| 25       | Control Register (LCDCONV_CONTROL_REG)                                   |      |

| 26       | LPG Functional I/O Signals                                               |      |

| 27       | LED Pulse Generator Receive and Transmit Registers                       |      |

| 28       | LPG Control Register (LCR)                                               |      |

| 29       | LED Blinking Period                                                      |      |

| 30       |                                                                          |      |

| 31       | Power Management Register (PMR)                                          | . 81 |

This document describes the display interface of the OMAP5912 multimedia processor.

### 1 Overview

This document discusses the following components of the display interface:

- LCD module

- LCD data conversion module

- LED pulse generator

- Display interface

# 2 LCD Module

The device includes an LCD controller that interfaces with most industry-standard LCD displays through embedded or discrete timing controllers. The LCD controller operates only in single-panel mode (dual-panel mode is not supported). The module is designed to work with a separate RAM block to provide data to the FIFO at the front end of the LCD controller data path at a rate sufficient to support the chosen display mode and resolution.

The panel size is programmable and can be any width (line length) from 16 to 1024 pixels, in 16-pixel increments. The number of lines is set by programming the total number of pixels in the LCD. The total frame size is programmable up to  $1024 \times 1024$ .

Frame sizes and frame rates supported in specific applications depend on the available memory bandwidth allowed by the application.

The screen is intended to be mapped to the frame buffer as one contiguous block, where each horizontal line of pixels is mapped to a set of consecutive bytes of words in the frame memory.

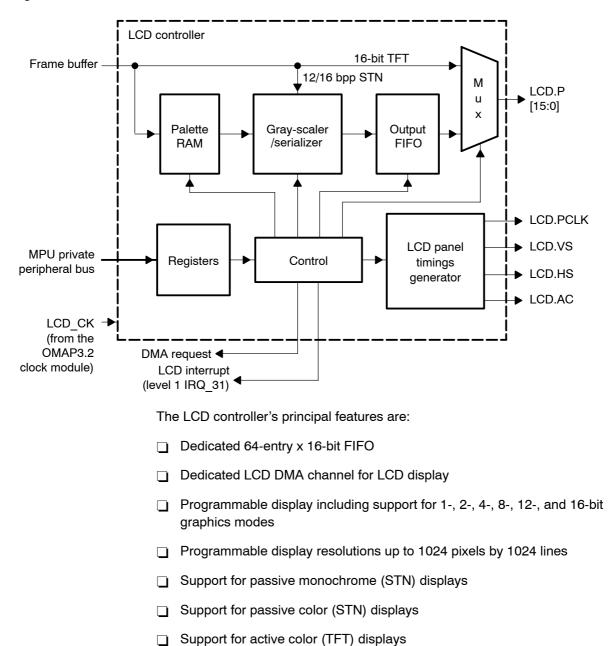

Figure 1 shows the LCD controller in detail.

Figure 1. LCD Controller

Detented dithering algorithm, providing:

- 15 grayscale levels for monochrome passive displays

- 3375 colors for color passive displays

- 65536 colors for active color displays

- 256-entry x 12-bit palette

- Programmable pixel rate

- Pixel clock plus horizontal and vertical synchronization signals

- ac-bias drive signal

- Active display-enable signal

Frame buffer data can be formatted for 1-, 2-, 4-, 8-, 12-, or 16-bit pixel sizes. A 16-entry x 12-bit palette supports the 1-, 2-, and 4-bit pixel sizes, whereas a larger 256-entry x 12-bit palette supports the 8-bit pixel size. The 12-bit and 16-bit pixel sizes provide data that bypasses the palettes. The data is then processed according to the desired type of display.

For passive monochrome panels, the 4-bit value indexed from the least significant bits of the palette is passed to the patented dither logic, where the desired brightness is created using temporal dithering. The pixels are passed to the panel via a 4-wire interface, 4 pixels in parallel per pixel clock.

For passive color panels showing 8-bit color or less, an entry from the palette is transferred simultaneously into three parallel dither engines, one for each of the red, green, and blue colors. These values are converted by the three patented temporal dithering logic blocks to provide up to 256 colors out of a possible 3375 colors ( $15 \times 15 \times 15$ ). The pixels are passed to the panel via an 8-wire interface, 2 2/3 pixels per clock.

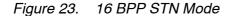

For passive color panels showing 12- or 16-bit color, the data from the frame buffer is passed directly into the dither logic, bypassing the palette. The three parallel dither engines then provide up to 3375 colors. The 16-bit color mode uses only the most significant four bits of each color channel. The pixels are also passed to the panel via an 8-wire interface, 2 2/3 pixels per clock.

For active color panels showing 8-bit color or less, an entry from the palette is expanded from 12 bits to 16 bits and passed to the display, providing up to 256 colors out of a possible 4096 ( $16 \times 16 \times 16$ ) colors. The pixels are passed to the panel via a 16-wire interface, 1 pixel per clock.

For active color panels showing 12-bit color, the data is also expanded from 12 bits to 16 bits to provide up to 4096 colors. The pixels are passed to the panel via a 16-wire interface, 1 pixel per clock.

For active color panels showing 16-bit color, the data is passed directly to the display (bypassing palette and dither logic), providing up to 65536 colors. The pixels are passed to the panel via a 16-wire interface, 1 pixel per clock.

The active color modes can also be used with an external DAC to drive a video monitor. The LCD line clock pin functions as a horizontal synchronization (HSYNC) signal, and the frame clock pin functions as a vertical synchronization (VSYNC) signal.

Table 1 shows the details of the LCD controller signals.

| Name        | Туре | Destination          | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD.P[15:0] | Out  | LCD panel<br>display | I/O pins used to transfer 4, 8, or 16 data values at a time to the<br>LCD display. For monochrome displays, each signal<br>represents a pixel; for passive color displays, groupings of<br>three signals represent one pixel (red, green, and blue).<br>LCD.P[3:0] is used for monochrome displays of 2, 4, and 8<br>BPP; LCD.P[7:0] is used for color STN displays and<br>LCD.P[15:0] is used for active (TFT) mode. |

| LCD.PCLK    | Out  | LCD panel<br>display | Pixel clock used by the LCD display to clock the pixel data into<br>the line shift register. In passive mode, the pixel clock<br>transitions only when valid data is available on the data lines. In<br>active mode, the pixel clock transitions continuously, and the<br>ac-bias pin is used as an output enable to signal when data is<br>available on the LCD pins.                                                |

| LCD.HS      | Out  | LCD panel<br>display | Line clock used by the LCD display to signal the end of a line of pixels that transfers line data from the shift register to the screen and to increment the line pointer(s). Also used by TFT displays as the horizontal synchronization signal.                                                                                                                                                                     |

| LCD.VS      | Out  | LCD panel<br>display | Frame clock used by the LCD display to signal the start of a new frame of pixels. Also used by TFT displays as the vertical synchronization signal.                                                                                                                                                                                                                                                                   |

| LCD.AC      | Out  | LCD panel<br>display | ac-bias used to signal the LCD display to switch the polarity of<br>the power supplies to the row and column axis of the screen to<br>counteract DC offset. Used in TFT mode as the output enable<br>to signal when data is latched from the data pins using the pixel<br>clock.                                                                                                                                      |

Table 1.

Interface to LCD Panel Signal Descriptions

The pixel clock frequency is derived from the clock provided to the LCD controller (LCD\_CK) from the clock management logic and is programmable from OMAP3.2 clock management logic (see the *Multimedia Processor OMAP 3.2 Subsystem Reference Guide (SPRU749)*). Each time new data is supplied to the LCD data pins, the pixel clock is toggled to latch the data into the LCD display serial shifter. The line clock toggles after all pixels in a line have been transmitted to the LCD driver and a programmable number of pixel clock wait states have elapsed both at the beginning and end of each line. In passive mode, the frame clock toggles during the first line of the screen, and the beginning and end of each frame is separated by a programmable number of line-clock wait states. Horizontal front porch (HFP) and horizontal back porch (HBP) must be programmed to zero in passive mode.

In active mode, the frame clock is asserted at the end of a frame after a programmable number of line-clock wait states occurs. In passive display mode, the pixel clock does not transition during wait state insertion or when the line clock is asserted. Finally, the ac-bias (LCD.AC) can be configured to transition each time a programmable number of line clocks occurs.

# 2.1 LCD Controller Environment

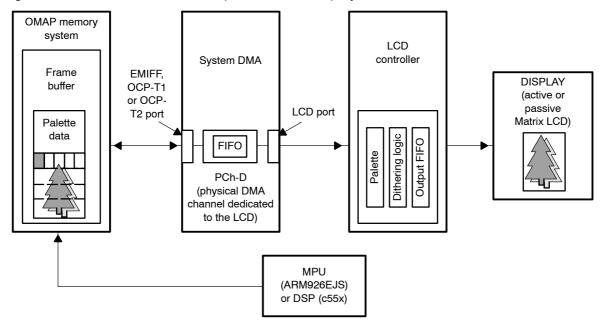

The LCD controller provides the necessary control signals to interface the memory directly to the external display through a dedicated DMA channel, as seen in Figure 2.

Figure 2. Data Flow from Microprocessor to Display

The MPU, or the DSP, stores the image to be displayed in a frame buffer. The frame buffer is used to supply enough encoded pixel values to fill the entire screen at least once.

The palette and the picture data are both in system memory. The palette loading mode (PLM) can be switched around so that only the picture data, only the palette data, or both are loaded at a given time (the palette is loaded only when it changes, then the PLM bit-field returns to picture-only mode).

The working copy of the palette resides in the LCD controller itself. See section 2.2, *LCD Controller Operation,* for descriptions of each block.

A specific system DMA channel dedicated to the LCD controller (LCh-D) is in charge of transferring data from the frame buffer to the LCD controller. Data is fetched, then transits into a 64\*33-bit FIFO. The 33<sup>rd</sup> bit is added for frame-synchronization purposes. However, the internal LCD controller receives 16-bit data from the DMA FIFO with each request.

The following section describes the LCD controller operation in detail.

# 2.2 LCD Controller Operation

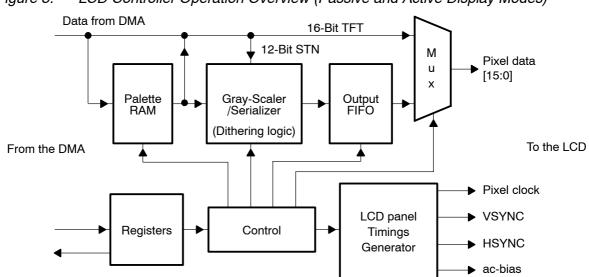

The LCD controller essentially consists of three blocks: a palette RAM, dithering logic, and an output FIFO, all associated with a control block operating through registers and a timing generator.

14 Display Interface

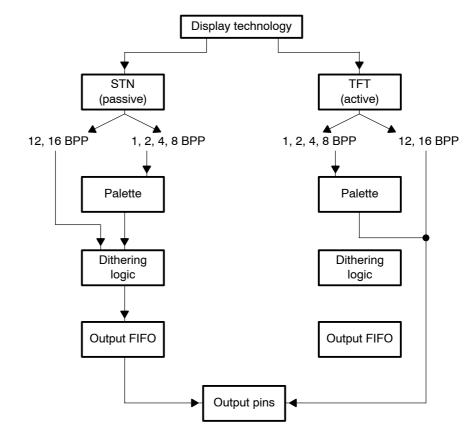

Figure 3 illustrates the LCD controller logic.

Figure 3. LCD Controller Operation Overview (Passive and Active Display Modes)

The LCD controller supports single-panel mode displays with programmable sizes. The display can be any width (line length) from 16 to 1024 pixels in 16-pixel increments (bit pixels per line (PPL) in the LCD timing 0 register). The number of lines is set by programming the lines per panel (LPP) field of the LCD timing 1 register (see section 2.3.3, *LCD Timing 1 Register*). The total video frame size is programmable up to 1024 x1024.

The screen is intended to be mapped to the frame buffer as one continuous block, where each line of pixels is mapped to a set of consecutive bytes or words in the frame buffer.

Two types of display technologies are supported:

- Passive, also known as super-twisted nematic, or STN

- Active, also known as thin film transistor, or TFT panels configured with the LCD TFT bit (LcdTFT) in the control register

See section 2.3.1, *LCD Control Register* for more information. Both monochrome and color modes are supported (LCD monochrome bit (LcdBW) in the control register).

In passive STN mode, a total of 3375 possible colors is available, allowing 16, 256, or 3375 colors to be displayed in each frame, depending on the color depth (number of bits per pixel: BPP). Fifteen grayscale levels are available for monochrome screens. See the *Dithering Logic* section, for information regarding the number of colors displayed versus BPP and screen technology.

In active TFT mode, whatever the color depth, 4096 colors can be displayed, except in the 16 BPP mode, where up to 64K colors are supported. See the *Dithering Logic* section for information regarding the number of colors displayed versus BPP and screen technology.

#### Note:

The active monochrome configuration is intentionally not considered in the remainder of this document.

# Frame Buffer

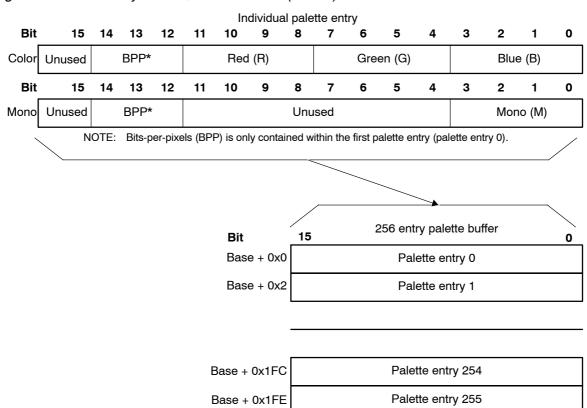

The frame buffer is a memory area used to supply enough encoded pixel values to fill the entire screen one time. It is a part of the memory which is connected either to EMIFF, OCP-T1, or OCP-T2 port. A portion of the LCD controller frame buffer is used as a 32-byte buffer for 1-, 2-, 4-, 12-, and 16-BPP mode operation, or as a 512-byte buffer for 8 BPP mode of operation. The buffer is used to store the current display depth and a look-up palette, which is nonzero-filled for 8BPP and lower modes.

The 32-byte buffer is used to load the 16 entries of the palette for 1-, 2-, 4-, 12-, and 16-BPP encoding, or the 512-byte buffer is used to load the entire 256-entry palette for 8-BPP encoding.

Not all of the 16 entries of the palette are used in 1- and 2-BPP modes. However, all 16 palette entries are loaded regardless. The unused palette entries must be zero-filled.

The palette is not used in 12- or 16-BPP modes, but is still required. The 32 bytes of the palette are zero-filled, except for the first entry, where a 3-bit field provides the information on the number of bits-per-pixel.

Each time a new frame is fetched from the frame buffer, the LCD controller palette is first loaded with data contained within the palette buffer. Normally, this buffer is placed immediately preceding the frame buffer image data to simplify programming of the LCD DMA channel (see *Multimedia Processor Direct Memory Access (DMA) Support Reference Guide (SPRU755)*). However, using the dual-frame feature of the LCD DMA channel, the palette can be placed anywhere within the frame buffer. Separating the palette from the image data is necessary to enable the *pan-and-scan* or *virtual desktop* feature enabled by the LCD DMA channel, and can be useful in other situations. When the palette buffer is in data loading mode only, you do not have to load the palette each time. PLM = 10 in the control register; see subsection *Palette Loading (PLM)*.

| Figure | 4. 16  | -Ent | ry Pa  | alette,  | /Buffe   | ər Foi   | rmat (   | (1, 2,  | 4, 12      | 2, 16     | BPP)     |          |          |         |       |   |

|--------|--------|------|--------|----------|----------|----------|----------|---------|------------|-----------|----------|----------|----------|---------|-------|---|

|        |        |      |        |          |          | In       | dividua  | al pale | tte en     | try       |          |          |          |         |       |   |

| Bit    | 15     | 14   | 13     | 12       | 11       | 10       | 9        | 8       | 7          | 6         | 5        | 4        | 3        | 2       | 1     | 0 |

| Color  | Unused |      | BPP'   | *        |          | Red      | (R)      |         |            | Gree      | en (G)   |          |          | Blu     | e (B) |   |

| Bit    | 15     | 14   | 13     | 12       | 11       | 10       | 9        | 8       | 7          | 6         | 5        | 4        | 3        | 2       | 1     | 0 |

| Mono   | Unused |      | BPP'   | *        |          |          |          | Unu     | ised       |           |          |          |          | Mono    | o (M) |   |

|        | N      | OTE: | Bits-p | per-pixe | els (BPI | P) is on | ly conta | uined w | rithin the | e first p | alette e | ntry (pa | lette en | try 0). |       |   |

|        |        |      |        |          |          |          |          |         |            |           |          |          |          |         |       |   |

|        |        |      |        |          |          | Bit      |          | 15      |            |           | 16 Enti  | y Pale   | tte Buf  | fer     |       | 0 |

|        |        |      |        |          |          | Bas      | e + 0x   | 0       |            |           | Pa       | lette er | ntry 0   |         |       |   |

|        |        |      |        |          |          | Bas      | e + 0x   | 2       |            |           | Pa       | lette er | ntry 1   |         |       |   |

|        |        |      |        |          |          |          |          |         |            |           |          |          |          |         |       |   |

|        |        |      |        |          |          |          |          |         |            |           |          |          |          |         |       |   |

|        |        |      |        |          |          | Base     | + 0x10   | 2       |            |           | Pal      | ette en  | try 14   |         |       |   |

|        |        |      |        |          |          | Base     | + 0x1[   | ≡       |            |           | Pal      | ette en  | try 15   |         |       |   |

|        |        |      |        |          |          |          |          |         |            |           |          |          |          |         |       |   |

Figure 4 and Figure 5 show the palette entry organization.

#### LCD Module

Figure 5. 256-Entry Palette/Buffer Format (8 BPP)

Bits 12, 13, and 14 of the first palette entry select the number of bits-per-pixel to be used in the following frame and thus, the number of palette RAM entries.

The bits-per-pixel (BPP) bit-field is decoded by the LCD to correctly unpack pixel data. It also configures the palette size to 16 or 256 entries.

Table 2 shows the BPP encoding in palette entry 0.

BitNameDescription14:12BPPBits-per-pixel000: 1 BPP000: 1 BPP001: 2 BPP010: 4 BPP010: 4 BPP011: 8 BPP11: 8 BPP1xx: 12 BPP in passive mode (LcdTFT=0 and 565 STN =0),<br/>16 BPP in passive mode (LcdTFT=0 and 565 STN =1),<br/>16 BPP in active mode (LcdTFT=1).

Table 2. Bits-Per-Pixel Encoding for Palette Entry 0 Buffer

Notes: 1) Eight 1-bit pixels, four 2-bit pixels, and two 4-bit pixels are packed into each byte, and 12-bit pixels are right justified on (16-bit) word boundaries (in the same format as palette entry).

2) For 565 STN, see the 16 BPP STN mode bit in the control register section.

The pixel data buffer contains one encoded pixel value for each pixel present on the display. Hence, the number of pixel data values depends on the size of the screen (i.e.,  $1024 \times 768 = 786,432$  encoded pixel values). Again, each pixel data value can be 1, 2, 4, 8, 12, or 16 bits wide.

The following figures show the memory organization within the frame buffer for each pixel encoding size.

The LCD controller is fed with 16-bit data from the LCD DMA channel. In 16and 12-BPP modes, this data is unaffected by LCDCB0 or LCDCB1 configuration bits.

#### 16-BPP Mode (TFT)

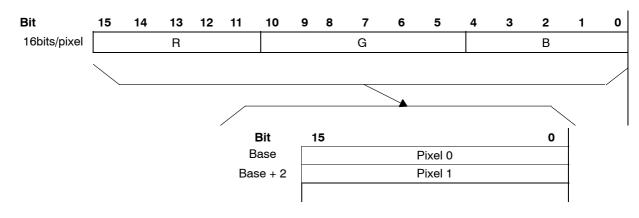

Figure 6 shows one RGB representation in 16-BPP (TFT) mode.

Display Interface 19

# 12-BPP Mode

Figure 7 shows the RGB representation in 12-BPP mode.

| Figure 7. | 12-BPP Data Memory Organization—Little Endian |  |

|-----------|-----------------------------------------------|--|

|-----------|-----------------------------------------------|--|

Unused [15..12] bits are filled with zeroes in TFT mode.

# 8-BPP Mode

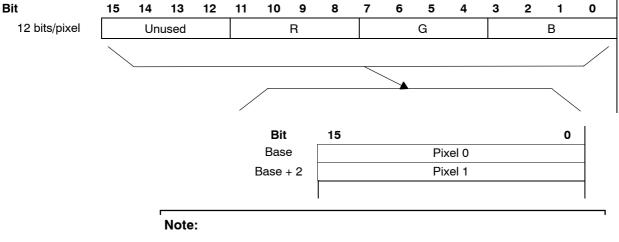

Figure 8 shows the format of the data in 8-BPP mode.

Figure 8. 8-BPP Data Memory Organization

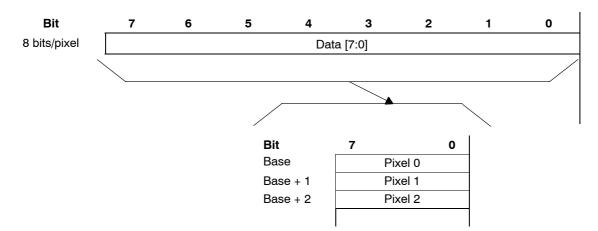

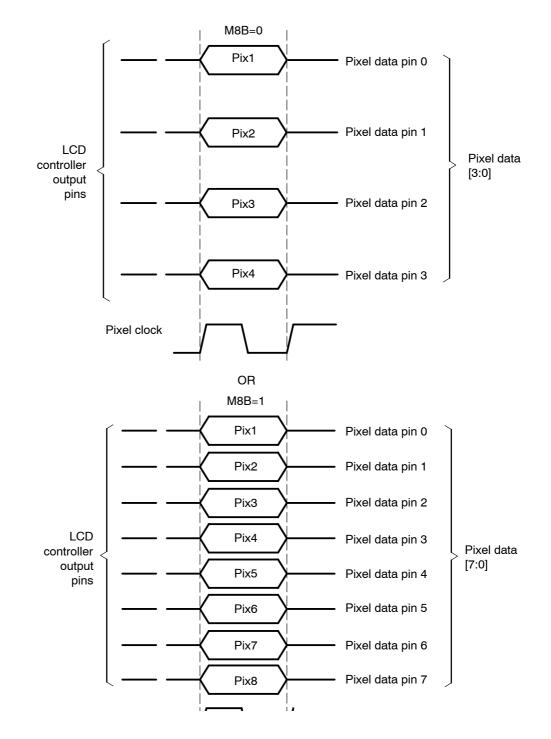

### 4-BPP Mode

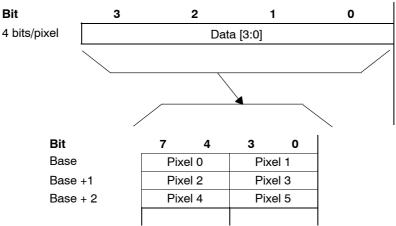

Figure 9 shows the format of the data in 4-BPP mode.

# 2-BPP Mode

Figure 10. 2-BPP Data Memory Organization

| Bit      | 7   | 6    | 5   | 4    | 3    | 2     | 1    | 0     |

|----------|-----|------|-----|------|------|-------|------|-------|

| Base     | Pix | el 0 | Pix | el 1 | Pix  | el 2  | Pix  | el 3  |

| Base + 1 | Pix | el 4 | Pix | el 5 | Pix  | el 6  | Pix  | el 7  |

| Base + 2 | Pix | el 8 | Pix | el 9 | Pixe | el 10 | Pixe | el 11 |

|          |     |      |     |      |      |       |      |       |

## 1-BPP Mode

Figure 11. 1-BPP Data Memory Organization

| Bit      | 7  | 6  | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|----|----|-----|-----|-----|-----|-----|-----|

| Base     | P0 | P1 | P2  | P3  | P4  | P5  | P6  | P7  |

| Base + 1 | P8 | P9 | P10 | P11 | P12 | P13 | P14 | P15 |

|          |    |    |     |     |     |     |     |     |

The top and bottom addresses of the frame buffer (palette entries + pixels data) are programmed in the DMA controller.

The equations shown in Table 3 are used to calculate the total frame buffer size (in bytes) to program in the system DMA, based on varying pixel size encoding and screen sizes.

#### SPRU764B

#### LCD Module

| BPP   | Frame Buffer Size          |

|-------|----------------------------|

| 1     | 32 + (Lines * Columns) / 8 |

| 2     | 32 + (Lines * Columns) / 4 |

| 4     | 32 + (Lines * Columns) / 2 |

| 8     | 512 + (Lines * Columns)    |

| 12/16 | 32 + 2 * (Lines * Columns) |

#### Table 3. Frame Buffer Size According to BPP

It is important to understand that BPP has two different meanings:

- In this section, BPP refers to how pixels are stored in memory. 1, 2, 4, 8, 12, or 16 are the different representations of the pixel within the frame buffer.

- BPP can also refer to how the panel views the pixels. This usage refers to which BPP the panels support (the actual interface, not the memory representation). The supported output panels are:

- 1 BPP for monochrome panels, packed onto 8 (or 4) data lines

- 3 BPP (1 bit each for red, green, and blue) for passive matrix technologies (output of dithering logic), packed onto 8 data lines

- 12 BPP for STN (4, 4, 4) panels

- 16 BPP for TFT (5, 6, 5) panels

#### Palette

The encoded pixel values stored in the frame buffer are used as pointers to index the 16-bit-wide palette. Palette entries are configured differently according to the mode used. See Figure 4 and Figure 5 for details.

The number of colors supported is given by  $2^{number of BPP}$ . These  $2^{number of BPP}$  colors are to choose within the palette that limits them to  $2^4 = 16$  grayscales in monochrome mode, and  $2^{12} = 4096$  colors in color mode, where 4 and 12 are the effective palette width in each case (*effective* meaning dedicated to the monochrome/color scales coding).

16 grayscales and 4096 colors are numbers obtained after passing through the palette. A redundancy introduced at the dithering logic step reduces these numbers when displaying. As the dithering logic is bypassed in active mode, there is no redundancy and 4096 different colors are really available. For more detail, see the section *Dithering Logic*, Table 4, *Color/Grayscale Intensities and Modulation Rates*, and Table 5, *Number of Colors/Grayscales Available on Screen*.

#### Passive Matrix Technology

The palette is bypassed in 12 BPP. In palette plus data or in palette-only modes (PLM = 00 or 01), the first entry is read to acquire the number of BPP. All other entries or useless bits in the first entry are filled with zeroes. But in data-only mode (PLM = 10), the palette is not loaded with every frame.

#### Note:

Henceforth, the palette is said to be *bypassed* in 12- and 16-BPP modes. The 12-bit values are directly supplied to the dither logic when passive mode is enabled, while the 16-bit values are directly sent to the panel when active mode is enabled. The *bypass* term can be misleading in PLM = 00 or 01 configurations, considering that the palette must be read, at least for the first entry that contains the information of the color depth. The rest is zero-filled and not taken into consideration. In PLM = 10 (data-only mode), the palette is bypassed.

#### Active Matrix Technology

The palette is bypassed in 16 BPP, allowing  $2^{16} = 65536 = 64$ K colors to be displayed.

### **Dithering Logic**

#### Passive Matrix Technology

Once a palette entry is selected by the encoded pixel value from the lookup palette, its content is sent to the color/grayscale space/time-based dither generator. The monochrome data, as well as each component, is encoded on 4 bits: red, green, and blue (RGB) in color mode. See individual palette entry in Figure 4 and Figure 5. Each 4-bit value is processed by one dither block. Three separate dither blocks are used in the color mode. These 4-bit values are used to select one of the 16 intensity levels. The gray/color intensity is controlled by turning individual pixels on and off at varying periodic rates. More intense grays/colors are produced by making the average time that the pixel is off longer than the average time that it is on. The dither generator also uses the intensity of adjacent pixels in its calculations to give the screen image a smooth appearance. The proprietary dither algorithm is optimized to provide a range of intensity values that match the eye's visual perception of color/gray gradations.

Table 4 summarizes the duty cycle and resultant intensity level for all 16 color/grayscale levels.

#### LCD Module

| Dither Value<br>(4-Bit Value from Palette) | Intensity<br>(0% is White) | Modulation Rate<br>(Ratio of ON to ON+OFF Pixels) |

|--------------------------------------------|----------------------------|---------------------------------------------------|

| 0000                                       | 0.0%                       | 0                                                 |

| 0001                                       | 11.1%                      | 1/9                                               |

| 0010                                       | 20.0%                      | 1/5                                               |

| 0011                                       | 26.7%                      | 4/15                                              |

| 0100                                       | 33.3%                      | 3/9                                               |

| 0101                                       | 40.0%                      | 2/5                                               |

| 0110                                       | 44.4%                      | 4/9                                               |

| 0111                                       | 50.0%                      | 1/2                                               |

| 1000                                       | 55.6%                      | 5/9                                               |

| 1001                                       | 60.0%                      | 3/5                                               |

| 1010                                       | 66.6%                      | 6/9                                               |

| 1011                                       | 73.3%                      | 11/15                                             |

| 1100                                       | 80.0%                      | 4/5                                               |

| 1101                                       | 88.9%                      | 8/9                                               |

| 1110                                       | 100.0%                     | 1                                                 |

| 1111                                       | 100.0%                     | 1                                                 |

#### Table 4. Color/Grayscale Intensities and Modulation Rates

Two of the 16 dither values (shaded in the table) are identical (most intense), which leads to redundancy in the colors.

This redundancy limits the choice to 15 (instead of 16) grayscales and 3375 (instead of 4096) colors. Note that  $3375 = 15^3$  which means the equivalent of 15 color scales for each component (R, G, and B).

#### Active Matrix Technology

The dithering logic is always bypassed in active displays. Hence, there is no redundancy introduced at this step, still allowing the choice of the  $2^{number of BPP}$  within the whole 4096 colors.

Remember that monochrome mode is deliberately not considered in active mode.

Table 5 lists the number of colors/grayscales available on the screen according to both the display technology and the color depth.

|           | Passive Mode (LcdTFT = 0)                                                                                                |                                                          | Active Mode (LcdTFT = 1)                                  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|--|

| Number of | Monochrome                                                                                                               | Color                                                    | Color Only                                                |  |

| BPP       | (LcdBW = 1)                                                                                                              | (LcdBW = 0)                                              | (LcdBW = 0)                                               |  |

| 1         | 2 palette entries to select<br>within 15 grayscales                                                                      | 2 palette entries to select within 3375 possible colors  | 2 palette entries to select within 4096 possible colors   |  |

| 2         | 4 palette entries to select<br>within 15 grayscales                                                                      | 4 palette entries to select within 3375 possible colors  | 4 palette entries to select within 4096 possible colors   |  |

| 4         | 16 palette entries to select<br>within 15 grayscales                                                                     | 16 palette entries to select within 3375 possible colors | 16 palette entries to select within 4096 possible colors  |  |

| 8         | Not relevant since it would<br>consist of 256 palette<br>entries to select within 15<br>grayscales, but exists<br>anyway | 256 palette entries to select<br>3375 possible colors    | 256 palette entries to select within 4096 possible colors |  |

| 12        | Х                                                                                                                        | 3375 possible colors                                     | 4096 possible colors                                      |  |

| 16        | Х                                                                                                                        | 3375 possible colors<br>(565 STN = 1)                    | Up to 65536 possible colors                               |  |

# The Output FIFO

#### Passive Matrix Technology

The LCD controller contains a 2-entry by 8-bit wide output FIFO that is used to store pixel data before it is driven out to the LCD pins. Each time a modulated pixel value is output from the dither generator, it is placed into a serial shifter. The size of the shifter is controlled by programming the color/ monochrome select bit (LcdBW) in the control register. The shifter can be configured to be 4 or 8 bits wide. Single-panel monochrome screens use either four or eight data lines; single-panel color screens use eight data pins. Once the correct number of pixels has been placed within the shifter, the value is transferred to the top of the output FIFO. The value is then transferred down until it reaches the last empty location within the FIFO. As values reach the bottom of the FIFO, they are driven out one by one onto the LCD data pins on the edge selected by the invert pixel clock (IPC) bit (see subsection *Invert Pixel Clock (IPC)*).

### Active Matrix Technology

The output FIFO is bypassed in TFT mode.

# LCD Inputs

Depending on the type of panel used, the LCD controller is programmed to use either 4-, 8-, 12-, or 16-pixel data output pins. See Table 9, *LCD Controller Data Pin Utilization for Mono/Color Passive/Active Panels.*

# Passive Matrix Technology—Monochrome Mode

Monochrome displays use 4- or 8-bit data lines, according to the mono 8-bit mode (see subsection *Mono 8 Bit Mode (M8B*). Each line represents one pixel (ON or OFF), which means that at each pixel clock, 4 or 8 pixels, respectively, are sent to the screen.

Figure 12 shows the passive monochrome mode (IPC = 0, see IPC bit in section 2.3.4, *LCD Timing 2 Register*).

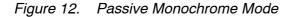

#### Passive Matrix Technology – Color Mode

Color passive displays use eight data input lines. Each line represents one color component (red, green, or blue). 2 2/3 pixels are sent to the screen at each pixel clock.

#### Note:

8 data lines, 1 line per color component, 3 color components per pixel lead to 2 2/3 pixels on 8 data lines.

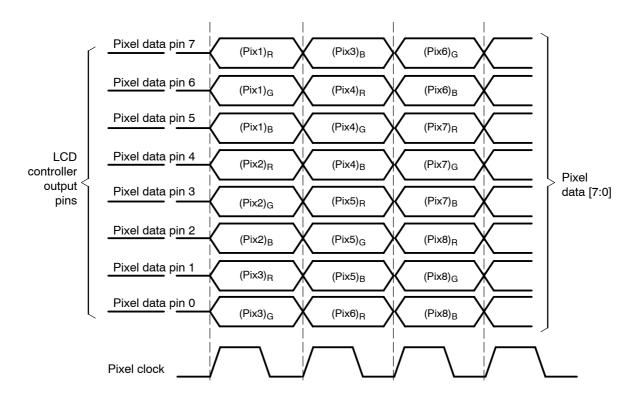

Figure 13 shows the passive color mode (IPC = 0, see IPC bit in section 2.3.4, *LCD Timing 2 Register*).

After the pixel clock toggles three times, the situation returns to its initial state. At the fourth clock cycle, the figure becomes identical to itself, i.e., the number of pixels displayed is an integer.

# Active Matrix Technology

In TFT displays, the dithering logic and the output FIFO are always bypassed. This means that data output from the palette is sent directly to the display. In 16-BPP mode, even the palette is bypassed so that data passes directly from the memory to the panel without being processed.

Consequently, at each pixel clock, only one pixel is sourced to the display.

Table 6 is a summary of the number of pixels displayed on the screen at each pixel clock for the different technologies.

# Table 6. Number of Pixels Displayed per Pixel Clock

| Number of Pixels | Display    |

|------------------|------------|

| 1                | TFT        |

| 2 2/3            | STN color  |

| 4                | Mono 4 bit |

| 8                | Mono 8 bit |

Figure 14 shows the different data paths depending on the screen technology and the color depth.

Figure 14. LCD Controller Data Paths

# 2.2.1 Control Blocks

The previous section explained the data flow from the memory to the LCD panel and the different modules they pass through. The whole process is governed by the registers and timing described in this section.

# Timing

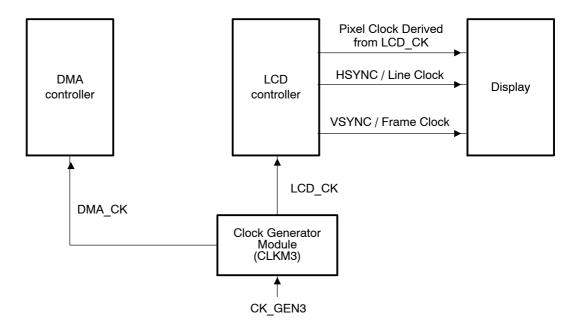

This section details the various clocks and signals. Figure 15 shows input and output LCD controller clocks.

Figure 15. Input and Output Clocks

# **Pixel Clock**

The pixel clock frequency is derived from the LCD clock (LCD\_CK), which belongs to the traffic controller (TC) domain. It is the output of the on-chip PLL: LCD\_CK = (CK\_GEN3/1, 2, 4, or 8). See *Multimedia Processor OMAP 3.2 Subsystem Reference Guide (SPRU749)* and *Multimedia Processor Clocks Reference Guide (SPRU751)*.

You can program the pixel clock from LCD\_CK / 2 to LCD\_CK / 255. The divider is called PCD (see subsection *Pixel Clock Divider*).

In any case, the LCD\_CK frequency must always be lower than or equal to the TC\_CK frequency.

The pixel clock is used by the LCD display to clock the pixel data into the line shift register.

#### Passive Matrix Technology

In passive mode, the pixel clock only transitions when valid data is available on the data lines.

It does not transition during wait state insertion or when the line clock is asserted.

#### Active Matrix Technology

In active mode, the pixel clock transitions continuously as long as the LCD is enabled, depending on the pxl\_gated bit in the LCD Control register (see section 2.3.1, *LCD Control Register*). Setting the pxl\_gated bit to 1 allows the pixel clock to toggle only when there is valid data to display.

### Line Clock (HSYNC)

The line clock toggles after all pixels in a line have been transmitted to the LCD driver and a programmable number of pixel clock wait states has elapsed both at the beginning and end of each line.

For more information, see the section *Horizontal Synchronization Pulse Width*.

#### Active Matrix Technology

The line clock is also used by TFT displays as the horizontal synchronization signal (HSYNC).

The timings of the line clock pins are programmable to support:

- Delay insertion both at the beginning and end of each line. See subsection Horizontal Front Porch (HFP) Bits and subsection Horizontal Back Porch (HBP)Bit.

- Line clock polarity. See subsection Invert HSYNC (IHS) Bit.

- □ Line clock pulse width, driven on rising or falling edge of pixel clock. See subsection Horizontal Synchronization Pulse Width (HSW), subsection HSYNC/VSYNC Rise or Fall Programmable (RF), and subsection HSYNC/VSYNC ON or OFF (ON\_OFF) Bits.

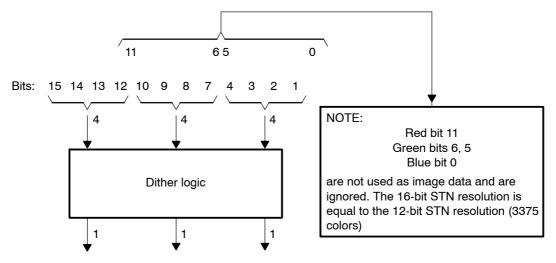

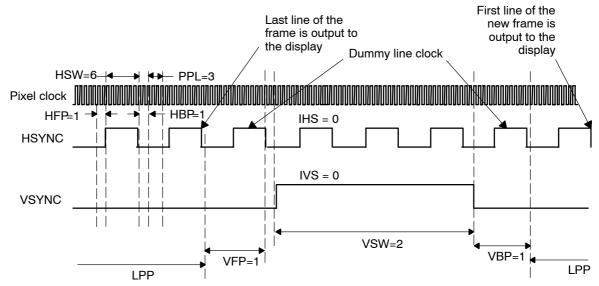

# Frame Clock (VSYNC)

The frame clock toggles after all lines in a frame have been transmitted to the LCD driver and a programmable number of line clock cycles has elapsed both at the beginning and end of each frame.

For more information, see the section Vertical Synchronization Pulse Width.

#### Passive Matrix Technology

In passive mode, the frame clock toggles during the first line of the screen.

32 Display Interface

### Active Matrix Technology

The frame clock occurs between two frames. In active mode, it is asserted at the end of the previous one and after a programmable number of line clock wait states (VFP) has elapsed.

The frame clock is also used by TFT displays as the vertical synchronization signal (VSYNC).

The timings of the frame clock pins are programmable to support:

- □ Delay insertion both at the beginning and end of each frame. See subsection *Vertical Front Porch (VFP) Bits* and subsection *Vertical Back Porch (VBP) Bits*.

- Frame clock polarity. See subsection Invert VSYNC (IVS) Bit.

- Frame clock pulse width, driven on rising or falling edge of pixel clock. See subsection Vertical Synchronization Pulse Width (VSW), subsection Horizontal Synchronization Pulse Width (HSW), subsection HSYNC/VSYNC Rise or Fall Programmable (RF), and subsection HSYNC/VSYNC ON or OFF(ON\_OFF) Bits.

## ac-Bias

The ac-bias signal can be configured to transition each time a programmable number of line clocks occurs.

#### Passive Matrix Technology

To prevent a dc charge within the screen pixels, the power and ground supplies of the display are periodically switched. The LCD controller signals the display to switch the polarity by toggling the ac-bias pin.

#### Active Matrix Technology

Used in TFT mode, it acts as an output enable to signal when data must be latched from the data pins using the pixel clock.

Figure 16 shows the different signals toggling in active mode.

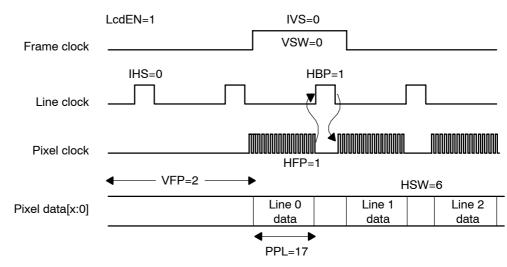

LcdEN=1 | IVS=0. VSW=0 VSYNC OE HFP=1 HSYNC IHS=0 HBP=1 HBP=1 VSW=0 VRP=1 HSW=4 **Pixel Clock** Pixel Data[x:0] Line 0 Line 1 data data PPL=13

Figure 16. Active (TFT) Mode Timing

NOTE: Ensure that HFP, HBP, PPL, and VSW values are programmed to the required value minus 1.

See the register sections, especially sections 2.3.2, *LCD Timing 0 Register*, and 2.3.3, *LCD Timing 1 Register*, for more details on the notations.

# 2.2.2 Interrupts

### Interrupt Sources

Several situations can generate an interrupt:

- Input and output FIFOs underrun errors

- Frame synchronization error

- When the last active frame has completed after the LCD is disabled (maskable)

- After a programmed number of transitions of the ac-bias pin (passive mode)

- □ When the display has reached the user-programmed line number (maskable)

- USYNC interrupt after every end of frame (maskable)

- Palette loading (maskable)

Every hardware-detected event signals an interrupt request to the interrupt controller.

34 Display Interface

Each interrupt is signaled by a bit in the LCD controller status register. Each of the LCD status bits signals an interrupt request as long as the bit is set. Once the bit is cleared, the interrupt is cleared. Read/write bits are called status bits; read-only bits are called flags. Status bits are referred to as "sticky" (that is, once set by hardware, they must be cleared by software). Read-only flags are set and cleared by hardware; writes have no effect.

Some interrupts are also maskable. For masked bits, see section 2.3.1, *LCD Control Register.*

#### Note:

A synchronization interrupt occurs if the LCD display information settings that you programmed, such as pixels-per-line, lines per frame, color/monochrome mode, and bits-per-pixel, are not in accordance with the size of the video buffer size programmed in the DMA.

# **Tearing Effect**

A synchronization mismatch between the frame buffer and the display refreshes can lead to images that appear to be torn on the screen.

To avoid this, a synchronization mechanism is needed between the LCD controller and the logical channel (LCh) that updates the frame buffer. For this purpose, a line comparator is implemented in the LCD controller, which delivers an interrupt when the display reaches a predefined line number. This interrupt is a level signal and stays active during the programmed line of the display.

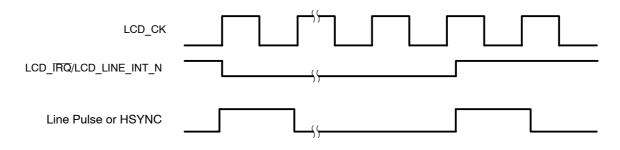

See subsection *Line Interrupt (line\_int*). Figure 17 shows the line interrupt output signal behavior for line\_int\_clr\_sel = 1 (see subsection *Line Interrupt Clear Select Bit (line\_int\_clr\_sel)*).

#### Figure 17. Line Interrupt Output Signal Transitions

#### SPRU764B

Note that lcd\_nirq and lcd\_line\_int\_n have the same behavior and are active low signals.

The line interrupt must be connected as a DMA request line to the system DMA. This can then be used by any generic LCh (LCh 0-15) to synchronize a block transfer (BS).

Since all interrupts and DMA request inputs and outputs are brought out to OMAP top level boundary, the DMA request mapping is not predefined. See the chip top-level specification for the exact DMA request mapping.

# 2.2.3 LCD Subpanel Display Support

# Principle

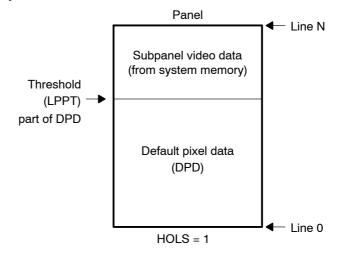

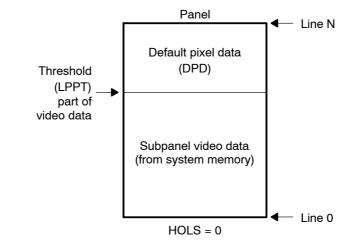

The subpanel display register supports the ability to display only the first or last X lines of the panel and send a fix contents for the others.

This functionality is used for power-saving. To display an image to a small portion of the screen (example: from line 0 to line 15), the data is read from system memory (frame buffer) via the DMA. For line 16 up to line N, where N is the number of lines per panel (LPP), data is read from an LCD register (DPD: default pixel data) instead of through the DMA. By reading into a register, there is no more access to the frame buffer, and power is saved. There is no need to go off-chip and do memory reads. In addition, the DMA can shut off its clocks during this DPD value filling.

For more information on the subpanel functionality, see section 2.3.6, *LCD Subpanel Display Support.*

# 2.3 Registers

The LCD controller contains eight registers:

- Given Four control registers

- Two status registers (including one display status register)

- One register related to the subpanel mode

- One specific register to define the line number where a line interrupt occurs

Table 7 shows the LCD controller registers and their physical addresses.

36 Display Interface

| Name             | Offset | Description                   |

|------------------|--------|-------------------------------|

| LcdControl       | 0x 00  | LCD control register          |

| LcdTiming0       | 0x 04  | LCD timing 0 register         |

| LcdTiming1       | 0x 08  | LCD timing 1 register         |

| LcdTiming2       | 0x 0C  | LCD timing 2 register         |

| LcdStatus        | 0x 10  | LCD status register           |

| LcdSubpanel      | 0x 14  | LCD subpanel display register |

| LcdLineInt       | 0x 18  | Line interrupt register       |

| LcdDisplayStatus | 0x 1C  | Display status register       |

# Table 7. LCD Controller Registers

# 2.3.1 LCD Control Register (LcdControl)

The LCD control register (LcdControl) contains bit-fields to enable/disable the LCD controller to define:

- The height and width of the screen being controlled

- Color or monochrome mode

- Passive or active display

- Polarity of the control lines

- Pulse width of the line and frame clocks

- The pixel clock and ac-bias frequency

- The number of delays to insert before/after each line and after each frame

- Interrupt mask bits

An additional control field exists to tune the DMA performance, based on the type of memory system in which the LCD controller is used. This field controls the placement of a minimum delay between each LCD palette request to ensure that enough bus bandwidth is given to other system accesses (see section *FIFO DMA Request Delay*). This field is only used for palette load.

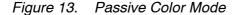

Table 8 describes the LCD control register bits.

| Figure 18. | LCD Control Register (LcdControl) |  |

|------------|-----------------------------------|--|

| 0          | 0 ( /                             |  |

| Offset         | : 0h 0      | 00         |                 | LO            | CD Co            | ntrol: I               | _CD C        | ontrol       | Regis          | ter                        |                    |                      | Rea                    | Read/Write       |           |           |  |

|----------------|-------------|------------|-----------------|---------------|------------------|------------------------|--------------|--------------|----------------|----------------------------|--------------------|----------------------|------------------------|------------------|-----------|-----------|--|

| Bit            | 31          | 30         | 29              | 28            | 27               | 26                     | 25           | 24           | 23             | 22                         | 21                 | 20                   | 19                     | 18               | 17        | 16        |  |

|                |             |            | I               | Reserve       | əd               |                        |              | 565<br>STN   | TFT<br>Map     | LCD<br>CB1                 | PI                 | LM                   |                        | FC               | D         |           |  |

| Reset          | х           | х          | х               | х             | х                | х                      | х            | 0            | 0              | 0                          | 0                  | 0                    | 0                      | 0                | 0         | 0         |  |

| Bit            | 15          | 14         | 13              | 12            | 11               | 10                     | 9            | 8            | 7              | 6                          | 5                  | 4                    | 3                      | 2                | 1         | 0         |  |

|                |             | F          | ĐD              |               | PXL<br>GA<br>TED | LINE<br>CL<br>RS<br>EL | M8B          | LCD<br>CB0   | Lcd<br>TFT     | LINE<br>_INT<br>_MA<br>_SK | LIN E T IR Q A S k | LOA<br>D<br>MAS<br>K | DO-<br>NE-<br>MAS<br>K | VSY<br>NC_<br>MA | LCD<br>BW | LCD<br>EN |  |

| Reset<br>NOTE: | 0<br>The re | 0<br>serve | 0<br>d bits' re | 0<br>set valu | 0<br>Jes are     | 0<br>undefin           | 0<br>ed, but | 0<br>reserve | 0<br>ed bits r | 0<br>eturn 1s              | 0<br>when i        | 0<br>read.           | 0                      | 0                | 0         | 0         |  |

| Table 8. | LCD Control Register (LcdControl) Bit | Descriptions |

|----------|---------------------------------------|--------------|

|          |                                       |              |

| Bit   | Name                 | Description                                                                                                                                                                                                                                                   |

|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24    | 565 STN              | 12-BPP (565) mode<br>0: Off.<br>1: On (16-bit data in frame buffer, but only 12 bits are dithered and sent out).                                                                                                                                              |

| 23    | ТҒТ Мар              | TFT alternate signal mapping<br>0: Output pixel data for 1, 2, 4, 8, and 12 BPP modes is right aligned on pixel data [11:0].<br>1: Output pixel data for 1, 2, 4, 8, and 12 BPP modes is converted to 5,6,5 format and<br>uses pins [15:0].                   |

| 22    | LCDCB1               | LCD control bit 1. Used in conjunction with LCD control bit 0 to control the mapping of pixel data from the frame buffer to the output bus. See Table 10 for the proper settings for this bit.                                                                |

| 21:20 | PLM                  | Palette loading mode<br>00: Palette and data loading<br>01: Palette loading<br>10: Data loading<br>11: Not connected                                                                                                                                          |

| 19:12 | FDD                  | FIFO DMA request delay<br>Encoded value (0-255) used to specify the number of LCD_CK cycles. The input FIFO<br>DMA request must be disabled. The clock count starts after 16 words are read in the<br>input FIFO. Programming FDD=00h disables this function. |

| 11    | PXL_GATED            | Pixel gated (for TFT mode only)<br>0: Pixel clock always toggles.<br>1: Pixel clock only toggles when there is valid data to display.                                                                                                                         |

| 10    | LINE_INT_CLR_S<br>EL | Line interrupt clear select bit<br>0: TIPB should write 0 to clear line interrupt status register.<br>1: Line interrupt status register is reset at the end of the line.                                                                                      |

| Bit | Name               | Description                                                                                                                                                                                                                                                                                                       |

|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | M8B                | <ul> <li>Mono 8-bit mode</li> <li>0: Pixel data [3:0] is used to output four pixel values to the panel at each pixel clock transition.</li> <li>1: Pixel data [7:0] is used to output eight pixel values to the panel at each pixel clock transition.</li> <li>This bit is ignored in all other modes.</li> </ul> |

| 8   | LCDCB0             | LCD control bit 0. Used in conjunction with LCD control bit 1 to control the mapping of pixel data from the frame buffer to the output bus. See Table 10 for the proper settings for this bit.                                                                                                                    |

| 7   | LcdTFT             | LCD TFT<br>0: Passive or STN display operation enabled; dither logic is enabled.<br>1: Active or TFT display operation enabled. External palette and DAC required. Dither<br>logic and output FIFO bypassed. Pin timing changes to support continuous pixel clock,<br>output enable, VSYNC, and HSYNC.            |

| 6   | line_int_mask      | Line interrupt mask (dedicated line)<br>0: Masks the dedicated line interrupt (line_int), which is connected to the lcd_line_int_n<br>dedicated output line.<br>1: Mask not active.                                                                                                                               |

| 5   | line_int_nirq_mask | Line interrupt mask<br>0: The line_int_nirq interrupt is masked.<br>1: The line_int_nirq interrupt is unmasked.                                                                                                                                                                                                   |

| 4   | LoadMask           | Load mask<br>0: Masks the loaded palette interrupt, which is connected to the lcd_nirq shared output<br>line.<br>1: Mask not active.                                                                                                                                                                              |

| 3   | DoneMask           | Done mask<br>0: Masks the frame done (Done) interrupt, which is connected to the Icd_nirq shared<br>output line.<br>1: Mask not active.                                                                                                                                                                           |

| 2   | VSYNC_mask         | LCD VSYNC interrupt mask<br>0: Interrupt to the lcd_nirq is masked.<br>1: Interrupt to the lcd_nirq is unmasked.                                                                                                                                                                                                  |

| 1   | LcdBW              | LCD monochrome<br>0: Color operation enabled.<br>1: Monochrome operation enabled.                                                                                                                                                                                                                                 |

| 0   | LcdEn              | LCD controller enable<br>0: LCD controller disabled.<br>1: LCD controller enabled.                                                                                                                                                                                                                                |

Table 8.

LCD Control Register (LcdControl) Bit Descriptions (Continued)

### LCD Enable (LcdEn)

The LCD enable (LcdEn) bit is used to enable and disable all LCD controller operation: When LcdEn=0, the LCD controller is disabled. When LcdEn=1, the LCD controller is enabled.

#### Note:

You must program all other control bit-fields before setting LcdEn = 1, and must also disable the LCD controller when changing the state of any control bit within the LCD controller.

You can program the LCD control register (LcdControl) last, and configure all twenty-five bit fields at the same time via a word32 write to the register. If you clear LcdEn bit while the LCD controller is enabled, you can complete transmission of the current frame before being disabled. Completion of the current frame is signaled by the LCD controller to the DMA by setting the frame done (Done) bit within the LCD controller status register (see section 2.3.5, *LCD Controller Status Register*), which generates an interrupt request.

If the LCD controller is disabled, the signals on pixel data [15:0] pins are set to 0 and the pixel clock, frame clock, line clock, and ac-bias signals are set to their inactive state. This can be 0 or 1, depending on the inversions programmed in the timing 2 register (see section 2.3.4, *LCD Timing 2 Register*).

# LCD Monochrome (LcdBW)

The color/monochrome select (LcdBW) bit is used to determine whether the LCD controller operates in color or monochrome mode. When LcdBW = 0:

- Color mode is selected.

- Palette entries are 12 bits wide, providing up to 4096 colors in active (TFT) mode and up to 3375 colors in passive (STN) color mode (see *Palette*).

- ☐ All three dither blocks are used (in passive mode only: LcdTFT = 0), one for each color component (R, G, B).

When LcdBW=1:

- Monochrome mode is selected.

- □ Palette entries are 4 bits wide *effective* (15 levels of grayscale, see *Palette*).

- 4 or 8 data lines are enabled, according to the mono 8-bit mode (M8B).

Table 9 shows which set of LCD data pins (Pixel Data [...]) is used for each mode of operation.

| Color/Mono BPP                     | Passive/Active Panel | Pins                                                                                          |

|------------------------------------|----------------------|-----------------------------------------------------------------------------------------------|

| Mono 1, 2, 4                       | Passive              | Pixel data [3:0]                                                                              |

| Mono 8                             | Passive              | Pixel data [7:0]                                                                              |

| Color 1,2,4,8,12, 16 (565 STN = 1) | Passive              | Pixel data [7:0]                                                                              |

| Color 1,2,4,8,12                   | Active               | Pixel data [11:0] or pixel data<br>[15:0] according to TFT map bit in<br>LCD control register |

| Color 16                           | Active               | Pixel data [15:0]                                                                             |

Note:

Unused pixel data bits always remain low.

# LCD Vertical Synchronization Mask (VSYNC\_mask)

The LCD VSYNC\_mask masks the VSYNC interrupt in the status register going to the lcd\_nirq when VSYNC\_mask bit is 0. When it is 1, the VSYNC bit affects the lcd\_nirq. (See subsection *VSYNC Interrupt.*)

# LCD Done Mask (DoneMask)

The LCD done mask (DoneMask) bit masks the path between the frame done interrupt and Icd\_nirq, see subsection *Frame Done (Read-Only)*.

When DoneMask = 0, the frame done interrupt is masked.

When DoneMask = 1, the frame done interrupt is not masked.

# LCD Loading Mask (LoadMask)

The LCD loading mask (LoadMask) bit masks the path between the palette loading interrupt signal in the LCD status register, and Icd\_nirq.

When LoadMask = 0, the loading interrupt is masked.

When LoadMask = 1, the loading interrupt is not masked.

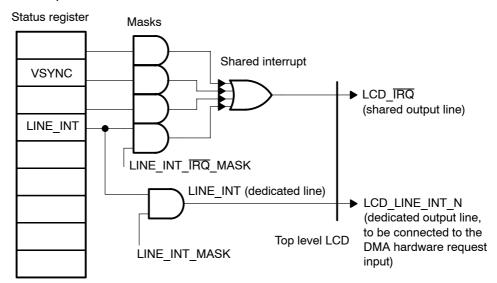

### Line Interrupt Mask (line\_int\_nirq\_mask)

This line\_int\_nirq\_mask bit masks the path going to the shared interrupt (Icd\_nirq).

When line\_int\_nirq\_mask = 0, the path between the line interrupt and lcd\_nirq (shared line) is masked. When line\_int\_nirq\_mask = 1, it is unmasked: any interrupt, among those who share the lcd\_nirq output line, can occur, including the line interrupt when the display reaches the programmed line number.

### Line Interrupt Mask (Dedicated Line) (line\_int\_mask)

This line\_int\_mask bit masks or unmasks the connection to the dedicated top-level entity signal lcd\_line\_int\_n, which is set to 0 when the display reaches the user-programmed line number. (See subsection *Line Interrupt,* and Figure 33, *Line Interrupt Path*).

When line\_int\_mask = 0, the connection is masked.