# TMS320TCI6487/8 Antenna Interface

# User's Guide

Literature Number: SPRUEF4A

December 2006–Revised June 2007

## **Contents**

| Pref | ace      |                                                           | 13  |

|------|----------|-----------------------------------------------------------|-----|

| 1    | Introdu  | uction                                                    | 15  |

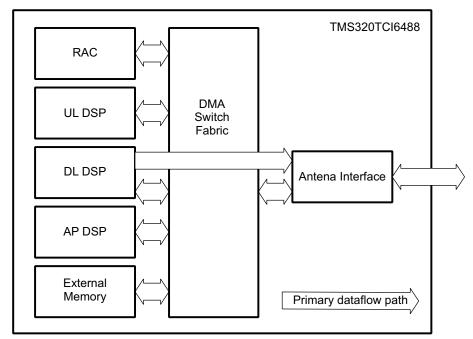

|      | 1.1      | Purpose of the Peripheral                                 | 15  |

|      | 1.2      | Features                                                  | 15  |

| 2    | Overvi   | ew of Antenna Interface Hardware and Software Components  | 17  |

|      | 2.1      | Hardware Component                                        | 17  |

|      | 2.2      | Software Component                                        | 17  |

| 3    | Introdu  | uction to Protocol                                        | 20  |

|      | 3.1      | OBSAI RP3 Protocol                                        | 20  |

|      | 3.2      | CPRI Protocol                                             | 26  |

|      | 3.3      | Systems that Do Not Require Either OBSAI or CPRI Protocol | 44  |

| 4    | Extern   | al Implementation                                         | 45  |

|      | 4.1      | Supported Topologies                                      | 45  |

|      | 4.2      | Clocks                                                    | 46  |

|      | 4.3      | High Speed Serial Interface Implementation                | 51  |

| 5    | Function | onal Description                                          | 53  |

|      | 5.1      | Overview                                                  | 53  |

|      | 5.2      | SERDES                                                    | 54  |

|      | 5.3      | Rx MAC                                                    | 54  |

|      | 5.4      | Tx MAC                                                    | 55  |

|      | 5.5      | RX Protocol Translator                                    | 55  |

|      | 5.6      | TX Protocol Translator                                    | 55  |

|      | 5.7      | Combiner                                                  | 55  |

|      | 5.8      | Decombiner                                                | 55  |

|      | 5.9      | Aggregator                                                | 55  |

|      | 5.10     | Protocol Decoder                                          | 56  |

|      | 5.11     | Protocol Encoder                                          | 56  |

|      | 5.12     | Data Buffer RAM                                           | 57  |

|      | 5.13     | VBUSP DMA Bus Interface                                   | 57  |

|      | 5.14     | VBUSP Configuration Bus Interface                         | 57  |

|      | 5.15     | Exception Event Handler                                   |     |

| 6    | Data T   | ransfer Over the Interfaces                               | 58  |

|      | 6.1      | Circuit-Switched Data Transfers                           |     |

|      | 6.2      | Packet-Switched Data Transfers                            | 65  |

| 7    | Usage    | Details                                                   | 67  |

|      | 7.1      | AIF Configuration                                         |     |

|      | 7.2      | Frame Sync Module Configuration                           | 98  |

|      | 7.3      | Achieving Link Synchronization                            |     |

|      | 7.4      | Setting Up Data Transfers                                 |     |

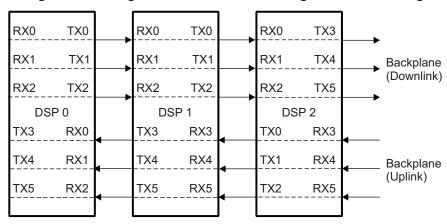

|      | 7.5      | Inter-TMS320TCI6487/8 Communication                       |     |

|      | 7.6      | Error Handling                                            |     |

|      | 7.7      | Debug Capabilities                                        |     |

|      | 7.8      | Special Cases                                             | 153 |

|      | 7.9      | Overview of CSL                                           | 154 |

| 8     | Regist | ers                                                                      | 155 |

|-------|--------|--------------------------------------------------------------------------|-----|

|       | 8.1    | Constant Registers                                                       | 166 |

|       | 8.2    | Configuration Registers                                                  | 167 |

|       | 8.3    | Status Registers                                                         | 231 |

| 9     | VBUS   | P DMA Bus Address Map                                                    | 285 |

| Appen | dix A  | Special Cases                                                            | 286 |

|       | A.1    | Calculating Delta for a Given Pi (Using the Combining/Decombining Block) | 286 |

|       | A.2    | Calculating a Given PE Frame Sync Offset for a Given Delta               | 288 |

|       | A.3    | Minimum Inbound DMA Timing                                               | 288 |

|       | A.4    | Loop Back Test Case Example                                              | 290 |

|       | A.5    | Troubleshooting                                                          | 293 |

## **List of Figures**

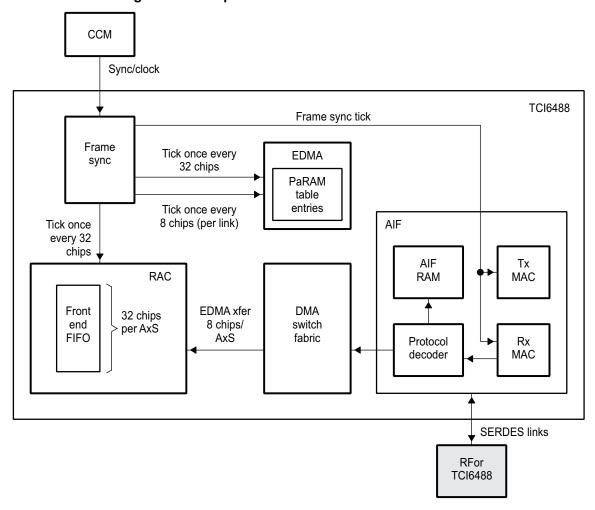

| 1        | TMS320TCI6487/8 Antenna Interface Module Overview                      | 17  |

|----------|------------------------------------------------------------------------|-----|

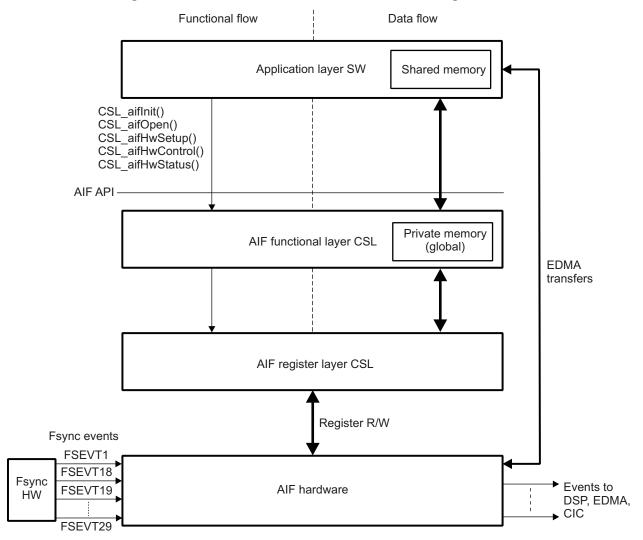

| 2        | Overview of Antenna Interface Software Organization                    | 18  |

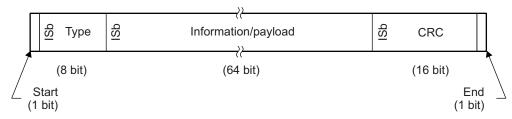

| 3        | Supported OBSAI RP3 Frame Structure                                    | 20  |

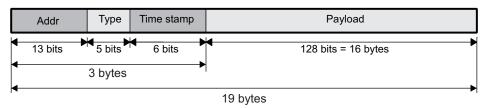

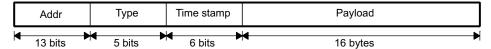

| 4        | OBSAI RP3 Protocol Packet Structure                                    | 21  |

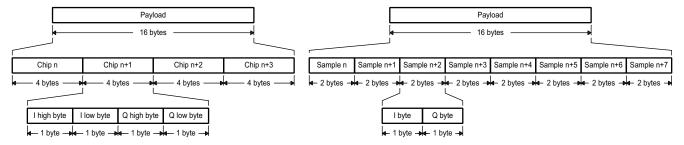

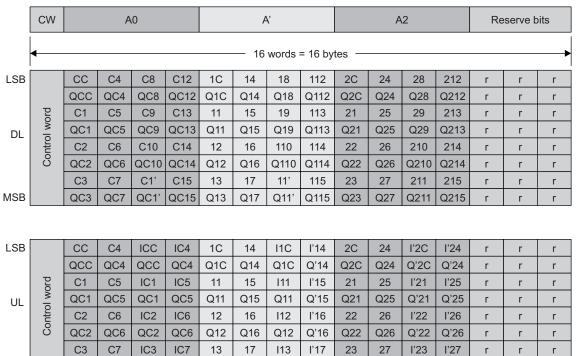

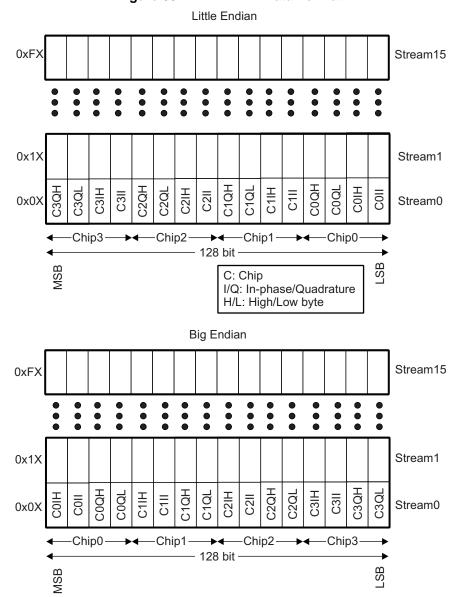

| 5        | DL and UL Data-Mapping to RP3 Message Payload, Respectively            | 23  |

| 6        | Transmission Rules Example for a 4x Link                               | 24  |

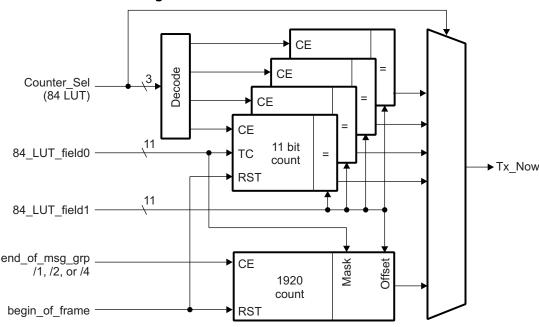

| 7        | Transmission Rule Generation                                           | 26  |

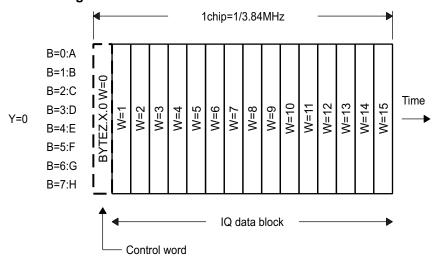

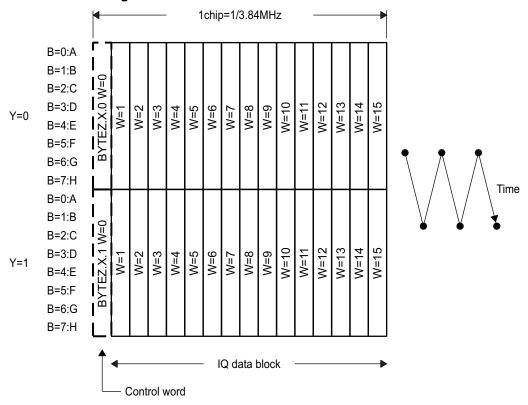

| 8        | CPRI Basic Frame Structure for 1x Link                                 | 28  |

| 9        | CPRI Basic Frame Structure for 2x Link                                 | 28  |

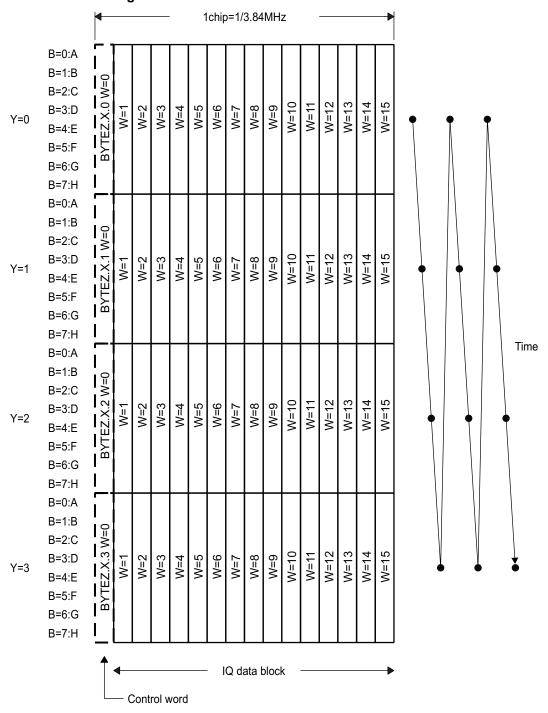

| 10       | CPRI Basic Frame Structure for 4x Link                                 | 29  |

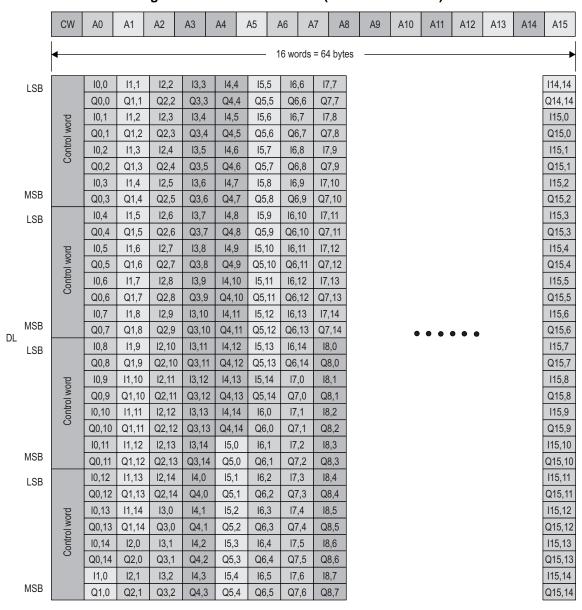

| 11       | CPRI Data Format (1x link - 15 bit DL, 7 bit UL)                       | 31  |

| 12       | CPRI Data Format (2x link - 15 bit DL, 7 bit UL)                       | 32  |

| 13       | CPRI Data Format (4x link - 15 bit DL)                                 |     |

| 14       | CPRI Data Format (4x link - 7 UL)                                      |     |

| 15       | CPRI Data Format (1x link - 16 bit DL, 8 bit UL)                       |     |

| 16       | CPRI Data Format (2x link - 16 bit DL, 8 bit UL)                       |     |

| 17       | CPRI Data Format (4x link - 16 bit DL)                                 |     |

| 18       | CPRI Data Format (4x link - 8 bit UL)                                  |     |

| 19       | CPRI Internal Data Format (1x link - 15 bit DL, 7 bit UL)              |     |

| 20       | CPRI Sub-Channels Within One Hyper Frame                               |     |

| 21       | CPRI L1 Protocol for Sub-Channel Z.130.0                               |     |

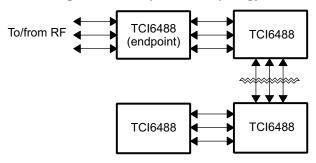

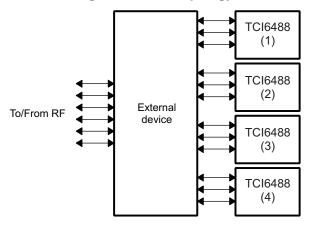

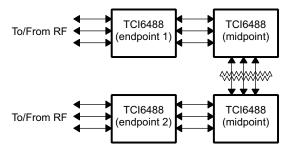

| 22       | Daisy Chain Topology                                                   |     |

| 23       | Star Topology                                                          |     |

| 24       | U-Daisy Chain Topology                                                 |     |

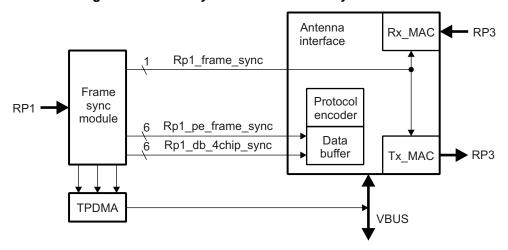

| 25       | RP1 Input Path                                                         |     |

| 26       | RP3 Frame Sync Offset                                                  |     |

| 27       | Synchronization Burst Format                                           |     |

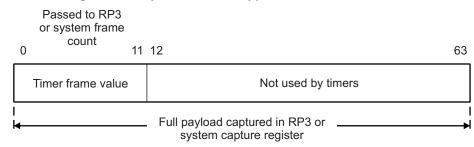

| 28       | Payload Use for Type RP3 and WCDMA FDD.                                |     |

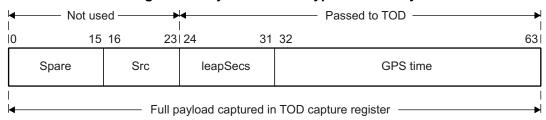

| 29       | Payload Use for Type Time of Day                                       |     |

| 30       | Antenna Interface Block Diagram                                        |     |

| 31       | Byte Data Prior to 8b10b Encoding                                      |     |

| 32       | SERDES Link Transmission Order                                         |     |

| 33       | Downlink Internal Data Flows Via the VBUS                              |     |

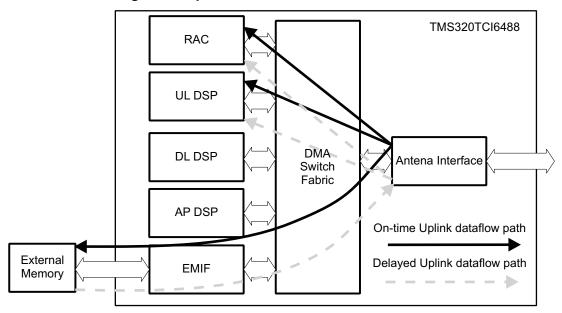

| 34       | Uplink Internal Data Flows Via the VBUS                                |     |

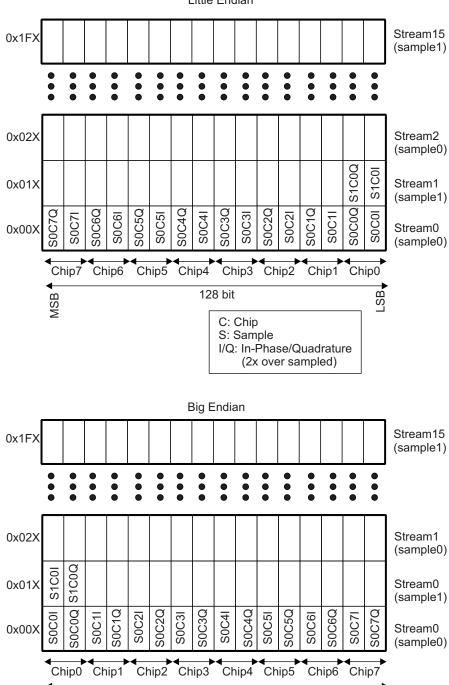

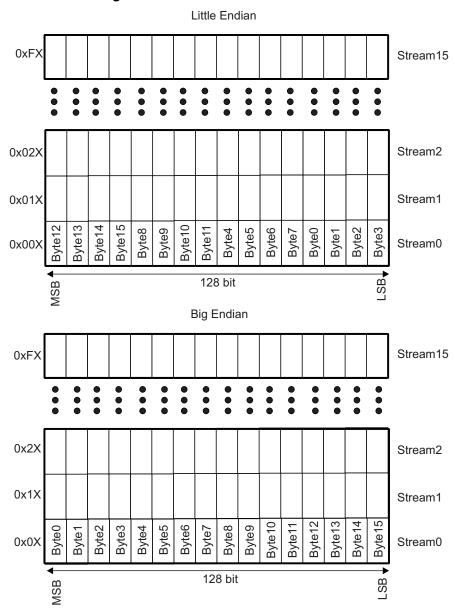

| 35       | DB RAM DL Data Format                                                  |     |

| 36       | DB RAM UL RSA Data Format                                              |     |

| 37       | DB RAM PIC MAI Data Format                                             |     |

| 38       | DB RAM Generic Data Format                                             |     |

| 39       | Packet-Switched Message Format                                         |     |

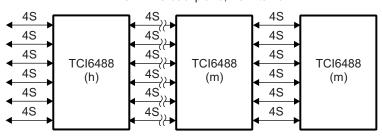

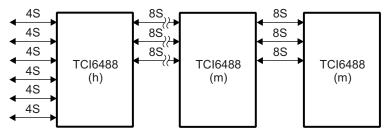

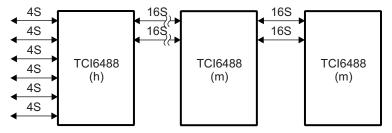

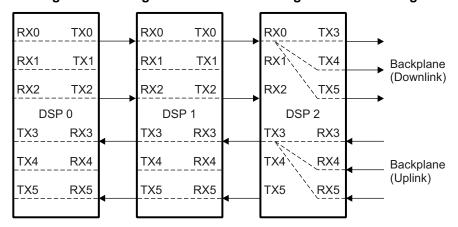

| 40       | DAISY1 - DAISY3 Options                                                |     |

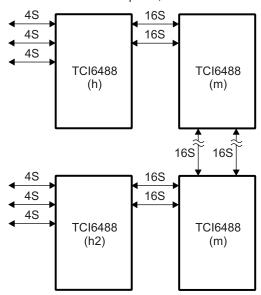

| 41       | UDAISY1 Option, 4S Backplane Links, 16S Internal                       |     |

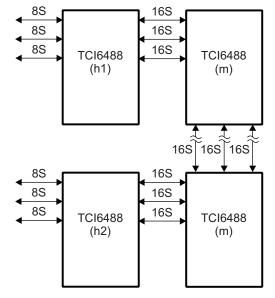

| 42       | UDAISY2 Option, 8S Backplane, 16S Internal                             |     |

| 43       | Configuration Without Combining and Decombining                        |     |

| 44       | Configuration With Combining and Decombining                           |     |

| 45       | PE Data Slot Count Use                                                 |     |

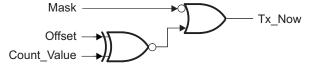

| 46       | Aggregator Configuration Input (1-of-6 links)                          |     |

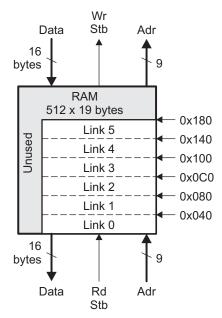

| 40<br>47 | Inbound Packet-Switched Memory Structure                               |     |

| 48       | Packet-Switched RAM Allocation for CPRI Mode                           |     |

|          |                                                                        |     |

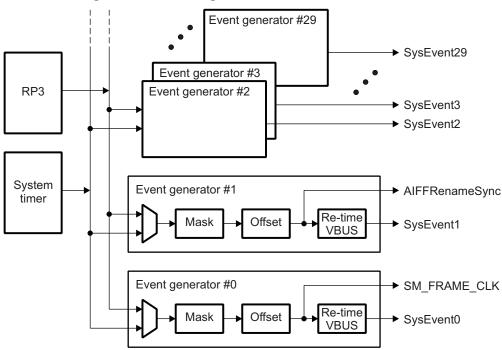

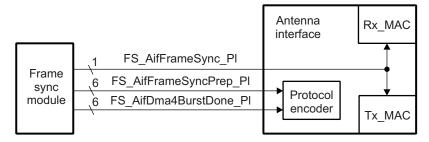

| 49<br>50 | Frame Sync and AIF Module System Events                                |     |

| 50<br>51 | Timer Configuration Concept  Timer Diagram With Event Generator Detail |     |

| 51<br>52 |                                                                        |     |

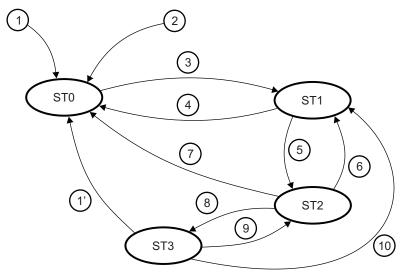

| 52       | RX Synchronization State Diagram                                       | 106 |

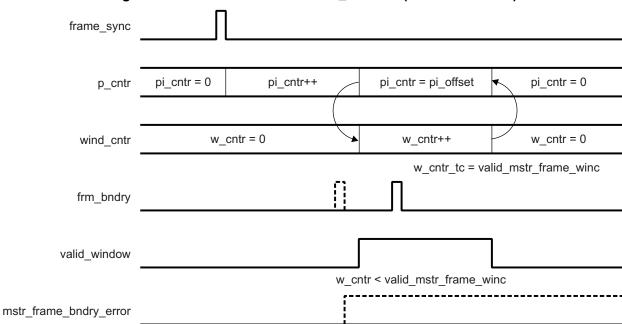

| 53                                                                                                 | Pi Counter for Positive PI_OFFSET (OBSAI and CPRI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 110                                                                                                          |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 54                                                                                                 | Pi Counter for Negative PI_OFFSET (OBSAI only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 111                                                                                                          |

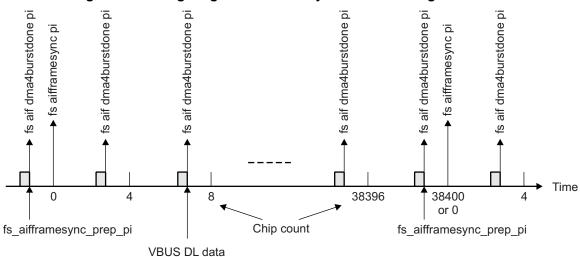

| 55                                                                                                 | Timing Diagram of Frame Synchronization Signals for DL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 111                                                                                                          |

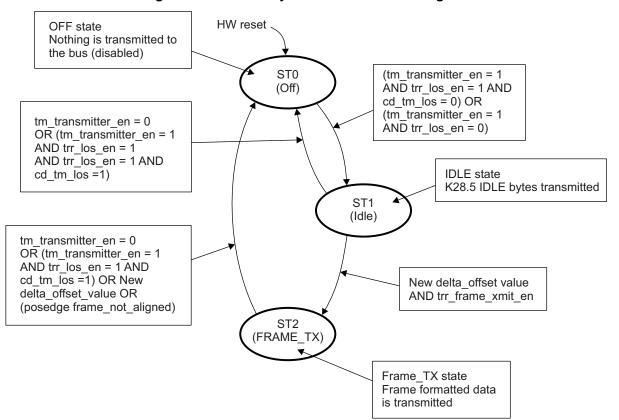

| 56                                                                                                 | Transmit Synchronization State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 113                                                                                                          |

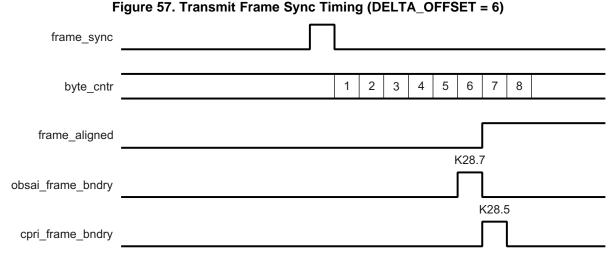

| 57                                                                                                 | Transmit Frame Sync Timing (DELTA_OFFSET = 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

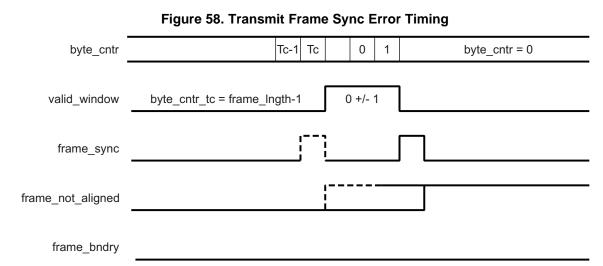

| 58                                                                                                 | Transmit Frame Sync Error Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 115                                                                                                          |

| 59                                                                                                 | Transmit Normal Operation Timing (DELTA_OFFSET = 6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |

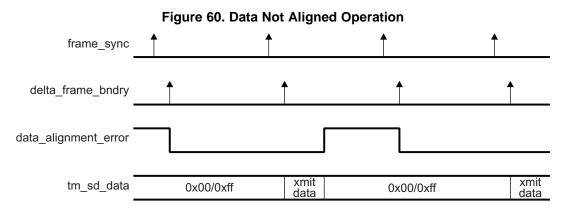

| 60                                                                                                 | Data Not Aligned Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

| 61                                                                                                 | Setup for Outbound Data Transfer from Tx DSP RAM to AIF Outbound RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117                                                                                                          |

| 62                                                                                                 | Memory Organization in Tx DSP Ping Buffer and AIF Outbound RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120                                                                                                          |

| 63                                                                                                 | Outbound DMA Transfer Shown for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 121                                                                                                          |

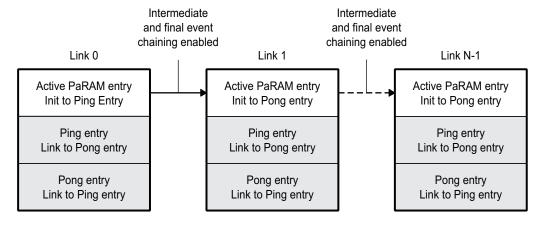

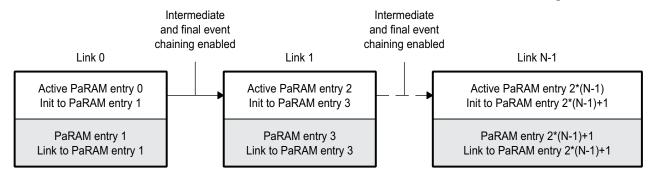

| 64                                                                                                 | Scheme showing event chaining and link updates used for transfer data from Tx DSP L2 RAM to AIF when outbound links have the same timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                                                                                                          |

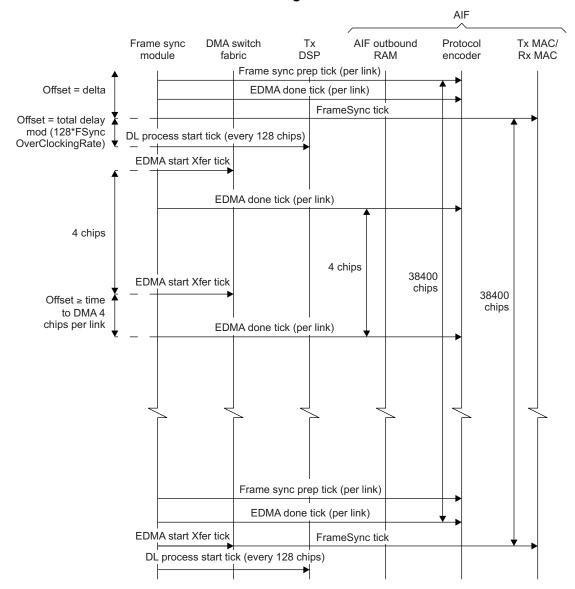

| 65                                                                                                 | Event Timing Relationships Shown for Outbound Transfer from Tx DSP to AIF Outbound RAM for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 124                                                                                                          |

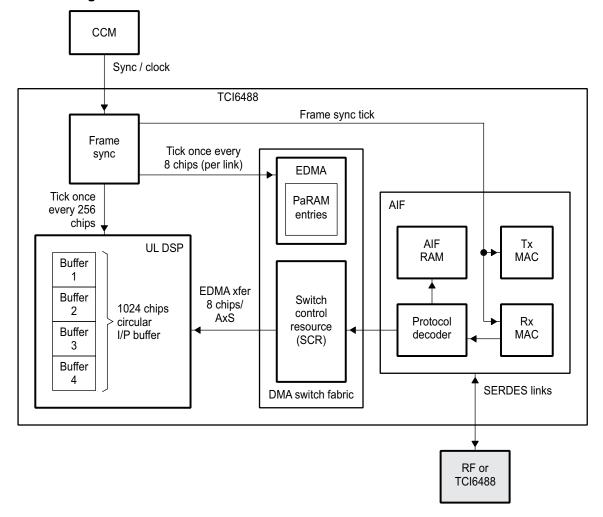

| 66                                                                                                 | Inbound Transfer From AIF Inbound RAM to UL DSP L2 RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 125                                                                                                          |

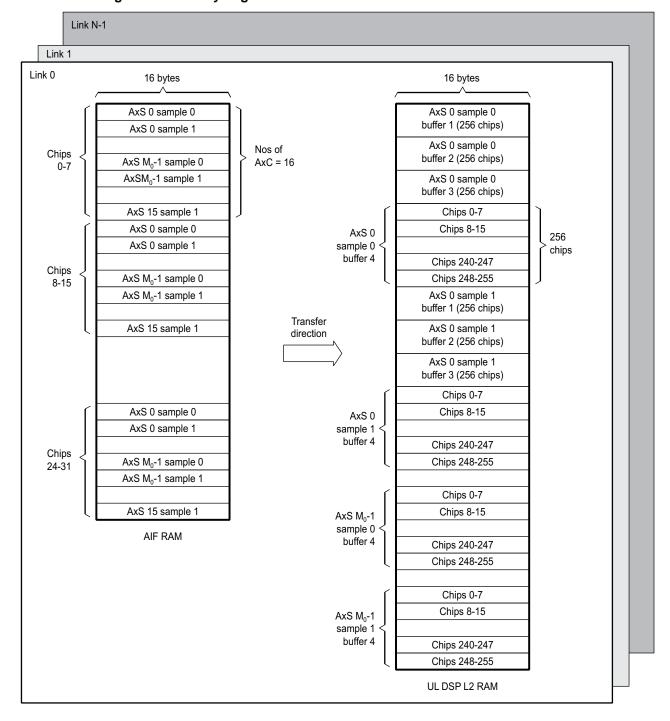

| 67                                                                                                 | Memory Organization in AIF Inbound RAM and UL DSP L2 RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

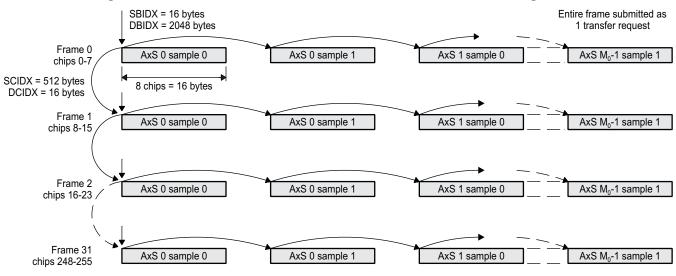

| 68                                                                                                 | Inbound DMA Shown for AIF → UL DSP Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

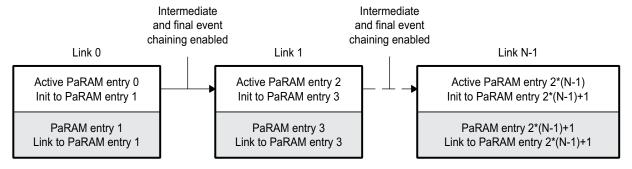

| 69                                                                                                 | Scheme Showing Event Chaining and Link Updates for Transfer Data From AIF Inbound RAM to UL DSP RAM for Inbound Links That Have the Same Inbound Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

| 70                                                                                                 | Rx Buffer Sizing Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

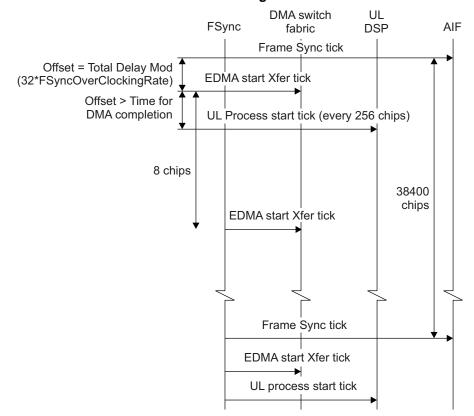

| 71                                                                                                 | Event Timing Relationships Shown for Inbound Transfer from Inbound AIF RAM to UL DSP L2 RAM for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |

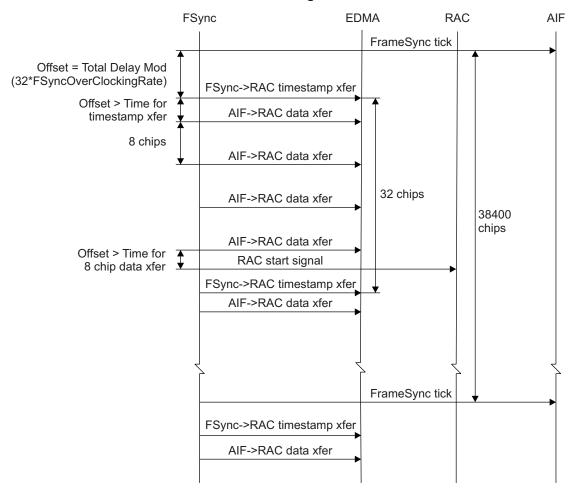

| 72                                                                                                 | Set Up for Inbound Transfer from AIF to RAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| 73                                                                                                 | Memory Organization in RAC FE FIFO and AIF Inbound RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                              |

| 74                                                                                                 | DMA Shown for Inbound AIF RAM → RAC Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| 75                                                                                                 | Scheme Showing Event Chaining and Link Updates for Transferring Data From AIF Inbound RAM to RAC FE FIFO When Inbound Links Have Identical Inbound Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |

| 76                                                                                                 | Event Timing Relationships Shown for Inbound Transfer from AIF Inbound RAM to RAC FE FIFO for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

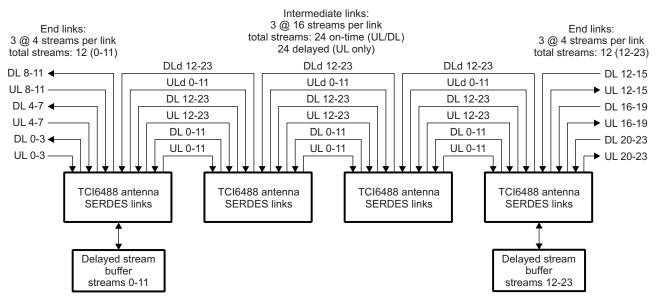

| 77                                                                                                 | Delayed Stream Generation Using Local Memory at End Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

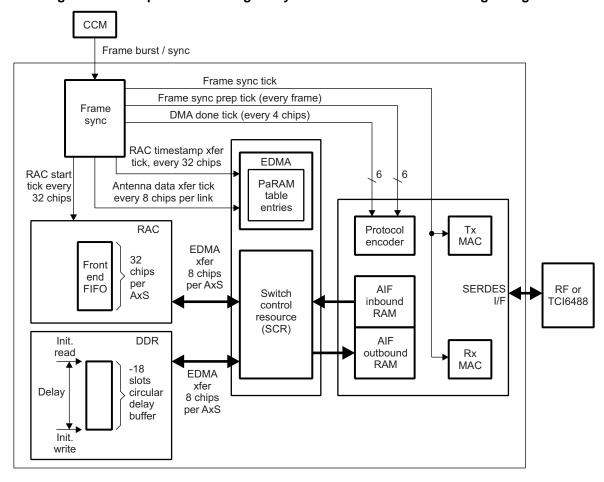

| 78                                                                                                 | Set Up for Generating Delayed Streams and UL Processing Using RAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

| 79                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

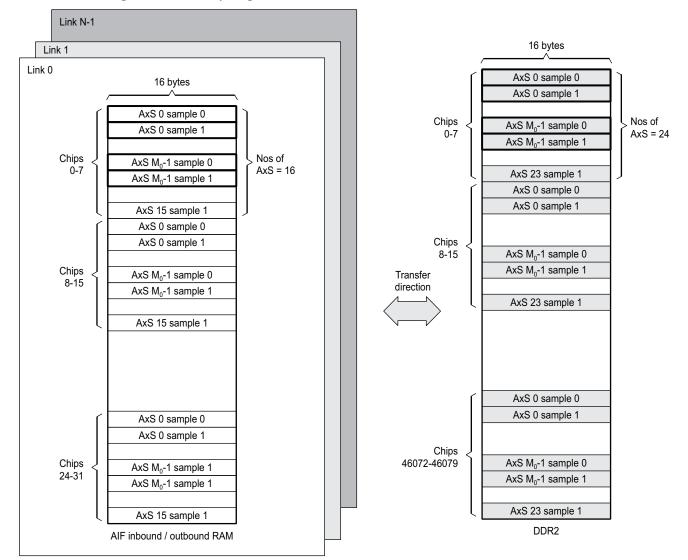

|                                                                                                    | Memory Organization in DDR2 and AIF Indound/Outbound RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 143                                                                                                          |

| 80                                                                                                 | Memory Organization in DDR2 and AIF Inbound/Outbound RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                              |

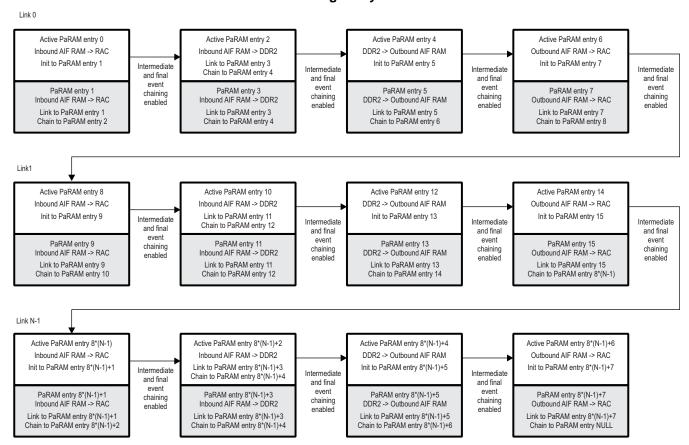

| 80<br>81                                                                                           | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144                                                                                                          |

| 81                                                                                                 | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144<br>145                                                                                                   |

|                                                                                                    | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144<br>145<br>149                                                                                            |

| 81<br>82<br>83                                                                                     | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144<br>145<br>149<br>166                                                                                     |

| 81<br>82<br>83<br>84                                                                               | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144<br>145<br>149<br>166<br>167                                                                              |

| 81<br>82<br>83<br>84<br>85                                                                         | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 144<br>145<br>149<br>166<br>167<br>168                                                                       |

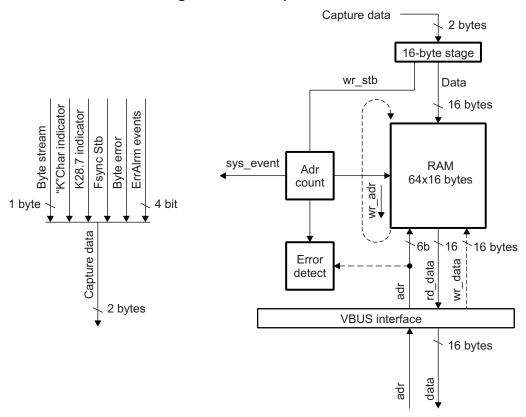

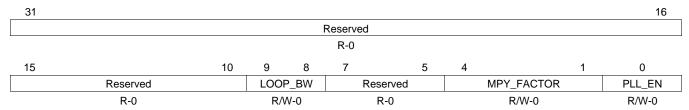

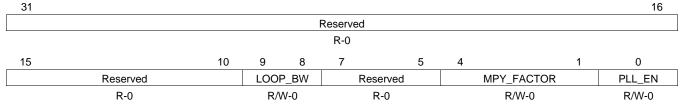

| 81<br>82<br>83<br>84<br>85<br>86                                                                   | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 144<br>145<br>149<br>166<br>167<br>168<br>169                                                                |

| 81<br>82<br>83<br>84<br>85<br>86<br>87                                                             | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 144<br>145<br>149<br>166<br>167<br>168<br>169                                                                |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88                                                       | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)                                                                                                                                                                                                                                                                                                                                                                                                                                 | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170                                                         |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88                                                       | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)                                                                                                                                                                                                                                                                                                                                                                     | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171                                                  |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89                                                 | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers                                                                                                                                                                                                                                                                                                                            | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172                                           |

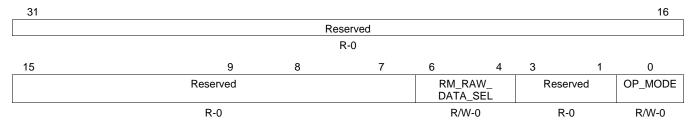

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90                                           | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES1_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers                                                                                                                                                                                                                                                                         | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>175                                    |

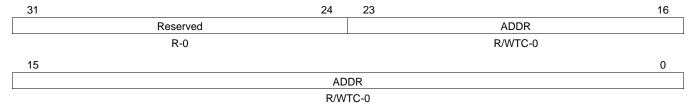

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91                                     | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PI_OFFSET_CFG)                                                                                                                                                                                                           | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>175<br>176                             |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93                         | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PI_OFFSET_CFG)  Rx MAC Links 0-5 LOS Threshold Registers (RM_LINK_LOS_THOLD_CFG)                                                                                                                                          | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>175<br>176                             |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94                   | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PI_OFFSET_CFG)  Rx MAC Links 0-5 LOS Threshold Registers (RM_LINK_LOS_THOLD_CFG)  Rx MAC Common Sync Counter (RM_SYNC_CNT_CFG) Register                       | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>175<br>176<br>177<br>178               |

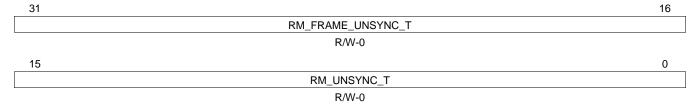

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95             | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PL_OFFSET_CFG)  Rx MAC Common Sync Counter (RM_SYNC_CNT_CFG) Register  Rx MAC Common UnSync Counter (RM_UNSYNC_CNT_CFG) Register                                                                                          | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>172<br>175<br>176<br>177<br>178<br>178        |

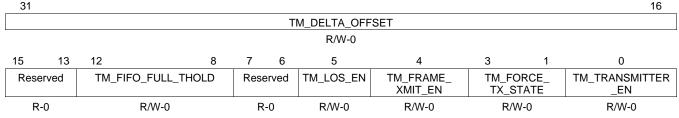

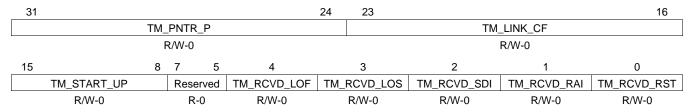

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95             | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams.  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES1_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PI_OFFSET_CFG)  Rx MAC Links 0-5 LOS Threshold Registers (RM_LINK_LOS_THOLD_CFG)  Rx MAC Common Sync Counter (RM_SYNC_CNT_CFG) Register  Rx MAC Common UnSync Counter (RM_UNSYNC_CNT_CFG) Register  Tx MAC Links 0-5 Configuration Registers 0 for CPRI Only (TM_LINK_CFGA) | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>175<br>176<br>177<br>178<br>178               |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90                                           | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer  AIF Peripheral ID Register (AIF_PID)  AIF Global Configuration Register (AIF_GLOBAL_CFG)  AIF Emulation Control Register (AIF_EMU_CNTL)  SERDES 0 PLL Configuration Register (AIF_SERDES0_PLL_CFG)  SERDES 1 PLL Configuration Register (AIF_SERDES1_PLL_CFG)  SERDES 0 Test Configuration Register (AIF_SERDES0_TST_CFG)  SERDES 1 Test Configuration Register (AIF_SERDES1_TST_CFG)  Link Configuration (LINK_CFG) Registers  Rx MAC Link Configuration (RM_LINK_CFG) Registers  Rx MAC Links 0-5 Pi Offset Registers (RM_LINK_PL_OFFSET_CFG)  Rx MAC Common Sync Counter (RM_SYNC_CNT_CFG) Register  Rx MAC Common UnSync Counter (RM_UNSYNC_CNT_CFG) Register                                                                                          | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>175<br>176<br>177<br>178<br>178<br>180        |

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | DMA Shown for Inbound AIF RAM → DDR2 Transfer for a Single Link  Scheme Showing Event Chaining and Link Updates for Performing UL Processing Using RAC and Generating Delayed Streams  Data Capture Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 144<br>145<br>149<br>166<br>167<br>168<br>169<br>170<br>171<br>175<br>176<br>177<br>178<br>178<br>180<br>181 |

| 101 | Combiner Alignment Offset Configuration (CD_CB_OFFSET_CFG) Register                          | 185 |

|-----|----------------------------------------------------------------------------------------------|-----|

| 102 | Combiner Valid Window Configuration (CD_CB_VALID_WIND_CFG) Register                          | 186 |

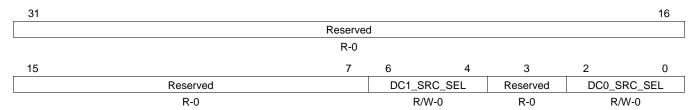

| 103 | Decombiner Source Select Configuration (CD_DC_SRC_SEL_CFG) Register                          | 187 |

| 104 | Decombiner Destination Select Configuration (CD_DC_DST_SEL_CFG) Register                     | 188 |

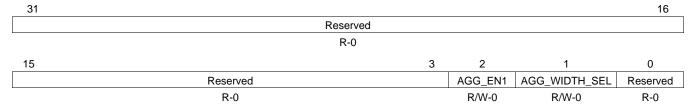

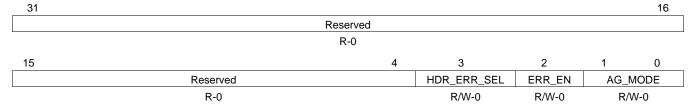

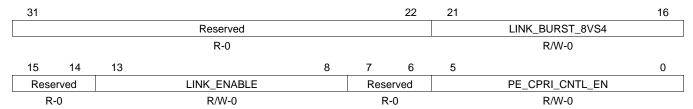

| 105 | Aggregator Configuration Registers Links 0-5 (AG_LINK_CFG)                                   | 190 |

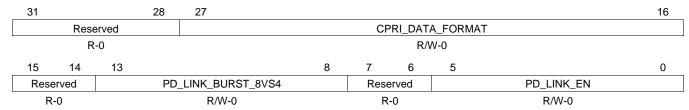

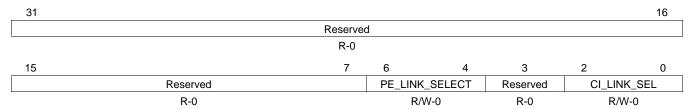

| 106 | CPRI Input Data Format Converter Configuration Registers Links 0-5 (CI_LINK_CFG)             | 192 |

| 107 | CPRI Output Data Format Converter Configuration (CO_LINK_CFG) Registers Links 0-5            | 193 |

| 108 | Protocol Decoder Configuration (PD_0_CFG) Register                                           | 194 |

| 109 | Protocol Decoder Configuration (PD_1_CFG) Register                                           | 195 |

| 110 | Protocol Decoder OBSAI Adr Mux Select (PD_ADR_MUX_SEL_CFG) Register                          | 196 |

| 111 | Protocol Decoder Type CirSw Capture Enable LUT (PD_TYPE_CIR_LUT_CFG) Register                | 198 |

| 112 | Protocol Decoder Type PktSw Capture Enable LUT (PD_TYPE_PKT_LUT_CFG) Register                | 198 |

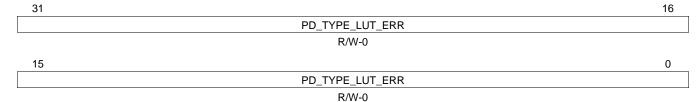

| 113 | Protocol Decoder Type Error (PD_TYPE_ERR_LUT_CFG) Register                                   | 199 |

| 114 | Protocol Decoder Address Look-Up Table (PD_ADR_LUT) Register                                 | 200 |

| 115 | Protocol Decoder 84 Count Look-Up Table Bits [31:0] (PD_LINK_84CNT_LUT0_CFG) Registers Links |     |

|     | 0-5                                                                                          |     |

| 116 | Protocol Decoder 84 Count Look-Up Table (PD_LINK_84CNT_LUT0_CFG) Register bits [63:32]       |     |

| 117 | Protocol Decoder 84 Count Look-Up Table (PD_LINK_84CNT_LUT2_CFG) Register bits [83:64]       | 204 |

| 118 | Protocol Decoder CPRI Stream Index LUT0 (PD_LINK_CPRI_SI_LUT0_CFG) Register                  | 205 |

| 119 | Protocol Decoder CPRI Stream Index LUT 1 (LUT1 PD_LINK_CPRI_SI_LUT1_CFG) Register            | 206 |

| 120 | Protocol Encoder Configuration (PE_CFG) Register                                             |     |

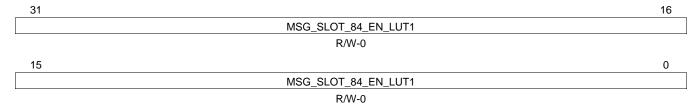

| 121 | Protocol Encoder 84 Count Message Enable Bits [31-0] (PE_LINK_84_EN_LUT0_CFG)                | 208 |

| 122 | Protocol Encoder 84 Count Message Enable Bits [63-32] (PE_LINK_84_EN_LUT1_CFG) register      | 209 |

| 123 | Protocol Encoder 84 Count message Enable bits [83:64] (PE_LINK_84_EN_LUT2_CFG) Register      | 210 |

| 124 | Protocol Encoder Transmission Rule Terminal Count 0 & 1 (PE_LINK_TERM_CNT01_CFG) Register    | 211 |

| 125 | Protocol Encoder Transmission Rule Terminal Count 2 & 3 (PE_LINK_TERM_CNT23_CFG) Register    | 212 |

| 126 | Protocol Encoder 84 Count LUT (PE_LINK_84CNT_LUT) Register                                   |     |

| 127 | Protocol Encoder Identity LUT Part 0 (PE_LINK_ID_LUT0) Register                              |     |

| 128 | Protocol Encoder Identity LUT part 1(PE_LINK_ID_LUT1) register                               | 215 |

| 129 | Data Buffer Configuration (DB_GENERIC_CFG) Register                                          | 216 |

| 130 | Data Buffer DMA Depth Clear (DB_DMA_QUE_CLR_CFG) Register                                    |     |

| 131 | Data Buffer DMA Depth Clear (DB_DMA_CNT_CLR_CFG) Register                                    | 218 |

| 132 | Data Buffer Outbound Packet-Switched FIFO Enable (DB_OUT_PKTSW_EN_CFG) Register              | 219 |

| 133 | Data Buffer Inbound Packet-Switched FIFO Flush (DB_OUT_PKTSW_FLUSH_CFG) Register             | 219 |

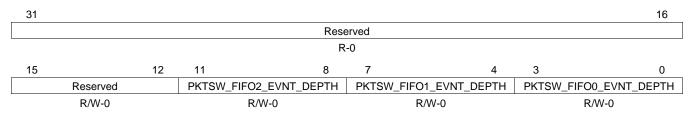

| 134 | Data Buffer Inbound Packet-Switched FIFO Empty_n Event Depth (DB_IN_FIFO_EVNT_CFG) Register  | 220 |

| 135 | Data Buffer Inbound Packet-Switched FIFO Depth (DB_IN_FIFO_SIZE_CFG) Register                | 222 |

| 136 | Data Buffer Force System Events (DB_FORCE_SYSEVENT_CFG) Register                             | 223 |

| 137 | Data Buffer PE Tracker Auto Sync Control (DB_OUTB_TRK_AUTOSYNC_CFG) Register                 | 224 |

| 138 | Data Buffer PD Tracker Auto Sync Control (DB_INB_TRK_AUTOSYNC_CFG) Register                  | 225 |

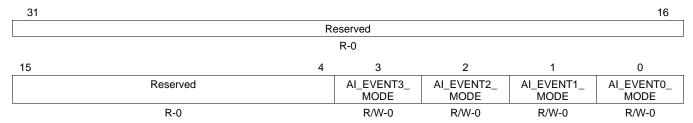

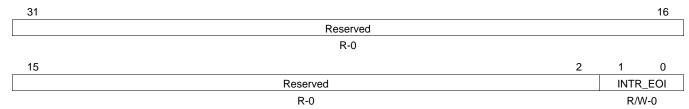

| 139 | EE Configuration (EE_CFG) Register                                                           |     |

| 140 | EE Link Select Register A for AI_EVENT[2] (EE_LINK_SEL_EV2A)                                 | 227 |

| 141 | EE Link Select Register B for AI_EVENT[2] (EE_LINK_SEL_EVB2)                                 | 229 |

| 142 | EE End of Interrupt (EE_INT_END) Register                                                    | 230 |

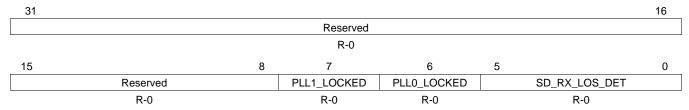

| 143 | SERDES Status (SERDES_STS) Register                                                          | 231 |

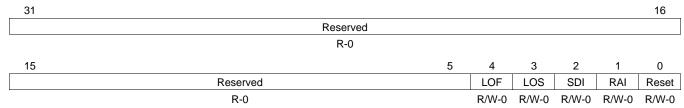

| 144 | Rx MAC Link 0 Status (RM_LINK_STSA) Register 0                                               | 232 |

| 145 | Rx MAC Link 0 Status (RM_LINK_STSB) Register 1                                               | 233 |

| 146 | Rx MAC Link 0 Status (RM_LINK_STSC) Register 2 - CPRI                                        | 234 |

| 147 | Rx MAC Link 0 Status (RM_LINK_STSD) Register 3 - CPRI                                        | 235 |

| 148 | Tx MAC Status (TM_LINK_STS) Registers (Link 0 - Link 5)                                      |     |

| 149 | Combiner / Decombiner Status (CD_STS) Register                                               | 237 |

| 150 | Aggregator Link 0 Status (AG_LINK_STS) Register                                              |     |

| 151 | Aggregator Link 0 Header Error Status (AG_LINK_HDR_ERR_STSA) Register 0                      | 239 |

| 152 | Aggregator Link 0 Header Error Status (AG_LINK_HDR_ERR_STSB) Register 1                      | 240 |

| 153 | Aggregator Link 0 Header Error Status (AG_LINK_HDR_ERR_STSC) Register 2                      | 241 |

| 154 | Aggregator Link 0 Header Error Status (AG_LINK_HDR_ERR_STSD) Register 2                        | 242 |

|-----|------------------------------------------------------------------------------------------------|-----|

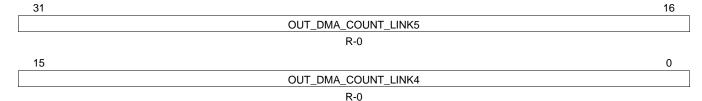

| 155 | Data Buffer Inbound DMA Count 0 (DB_IN_DMA_CNT0_STS) Register                                  | 243 |

| 156 | Data Buffer Inbound DMA Count 1 (DB_IN_DMA_CNT1_STS) Register                                  | 243 |

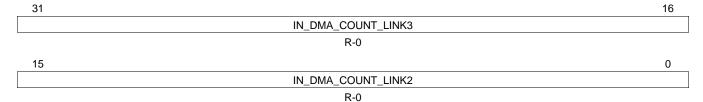

| 157 | Data Buffer Inbound DMA Count 2 (DB_IN_DMA_CNT2_STS) Register                                  | 244 |

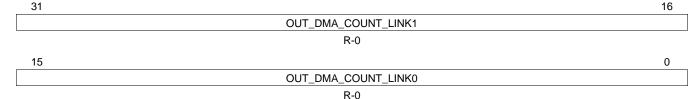

| 158 | Data Buffer Outbound DMA Count 0 (DB_OUT_DMA_CNT0_STS) Register                                | 244 |

| 159 | Data Buffer Outbound DMA Count 1 (DB_OUT_DMA_CNT1_STS) Register                                | 245 |

| 160 | Data Buffer Outbound DMA Count 2 (DB_OUT_DMA_CNT2_STS) Register                                | 245 |

| 161 | Data Buffer Inbound DMA Burst Available (DB_IN_DMA_DEPTH_STS) Register                         | 246 |

| 162 | Data Buffer Outbound DMA Burst Available (DB_OUT_DMA_DEPTH_STS) Register                       | 247 |

| 163 | Data Buffer Outbound Packet-Switched FIFO Status (DB_OUT_PKTSW_STS) Register                   | 248 |

| 164 | Data Buffer Outbound Packet-Switched FIFO Depth (DB_OUT_PKTSW_DEPTH_STS) Register              | 249 |

| 165 | Data Buffer Outbound Packet-Switched FIFO Not Empty (DB_OUT_PKTSW_NE_STS) Register             | 249 |

| 166 | Data Buffer Trace Buffer Status (DB_DATA_TRACE_STS) Register                                   | 250 |

| 167 | Data Buffer Outbound Packet-Switched FIFO Head Pointers #0-14 (DB_OUT_PKTSW_HEAD_STS)          |     |

|     | Register                                                                                       | 251 |

| 168 | Data Buffer Outbound Packet-Switched FIFO Tail Pointers #0-14 (DB_OUT_PKTSW_TAIL_STS) Register | 252 |

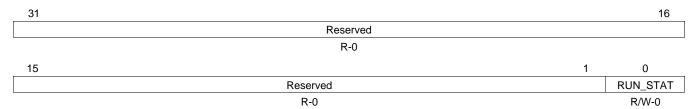

| 169 | EE AIF Run (EE_AI_RUN) Register                                                                |     |

| 170 | EE Link 0 Interrupt Source Raw Status (EE_LINK_IRS_A) Register A                               |     |

| 171 | EE Link 0 Interrupt Source Raw Status (EE_LINK_IRS_B) Register B                               |     |

| 172 | EE Common Interrupt Source Raw Status (EE_COMMON_IRS) Register                                 |     |

| 173 | EE Links 0-5 Interrupt Source Masked Status for Al_EVENT[0] (EE_LINK_IMS_A_EV0) Register A     |     |

| 174 | EE Links 0-5 Interrupt Source Masked Status for AI_EVENT[0] (EE_LINK_IMS_B_EV0) Register B     |     |

| 175 | EE Common Interrupt Source Masked Status for AI_EVENT[3:0] (EE_COMMON_IMS_EV) Register         |     |

| 176 | EE Link 0 Interrupt Source Mask Set A for AI_EVENT[0] (EE_LINK_MSK_SET_A_EV0) Register         |     |

| 177 | EE Link 0 Interrupt Source Mask Set B for AI_EVENT[0] (EE_LINK_MSK_SET_B_EV0) Register         | 266 |

| 178 | EE Common Interrupt Source Mask Set (EE_COMMON_MSK_SET_EV0) Register for AI_EVENT[0]           | 269 |

| 179 | EE Link 0 Interrupt Source Mask Clear (EE_LINK_MSK_CLR_A_EV0) Register A for AI_EVENT[0]       | 272 |

| 180 | EE Link 0 Interrupt Source Mask Clear (EE_LINK_MSK_CLR_B_EV0) Register B for AI_EVENT[0]       | 275 |

| 181 | EE Common Interrupt Source Mask Clear (EE_COMMON_MSK_CLR_EV0) Reg for AI_EVENT[0]              | 277 |

| 182 | EE Interrupt Vector (EE_INT_VECT_EV0-1) Register for AI_EVENT[0-1]                             | 280 |

| 183 | EE Interrupt Vector (EE_INT_VECT_EV2-3) Register for AI_EVENT[2-3]                             | 282 |

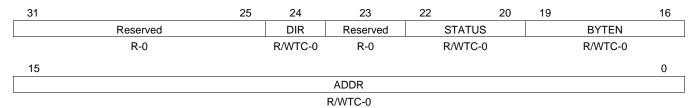

| 184 | VC Bus Error (VC_BUSERR) Register                                                              | 283 |

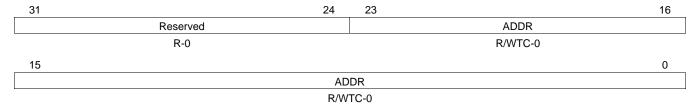

| 185 | VBUSP DMA Bus Interface Status (VD_RD_BUSERR) Registers                                        | 284 |

| 186 | VD Bus Error (VD_WR_BUSERR) Register                                                           | 284 |

| A-1 | Sync Events from Frame Sync Module                                                             | 289 |

### **List of Tables**

| 1  | Abbreviations Used in the TMS320TCI6487/8 Antenna Interface Guide          |     |

|----|----------------------------------------------------------------------------|-----|

| 2  | Content of Type Field                                                      | 22  |

| 3  | Number of Slots and IDLE Bytes in 5.21us                                   | 23  |

| 4  | Transmission Rule Example                                                  | 25  |

| 5  | Link Rate vs. DL/UL Bit Size Reference Table                               | 30  |

| 6  | Supported IQ Sample Widths                                                 |     |

| 7  | (W,B) Address of the First Bit of the AxC Containers for 7-Bit UL          | 30  |

| 8  | CPRI Implementation of Control Words Within One Hyper Frame                | 41  |

| 9  | Synchronization Control Word                                               | 41  |

| 10 | CPRI L1 Protocol for Sub-Channel Z.130.0 Field Descriptions                | 42  |

| 11 | Data Rates for Slow C&M Link                                               | 43  |

| 12 | Data Rates for Fast C&M Link                                               | 43  |

| 13 | Data Rates for Vendor-Specific Link                                        | 44  |

| 14 | Minimum VBUS_CLK Rates vs. BYTE_CLK Rates                                  | 46  |

| 15 | Valid Input OBSAI RP3 Clock Rates vs. PLL Multiply Factors                 | 46  |

| 16 | Valid Input CPRI Clock Rates vs. PLL Multiply Factors                      | 46  |

| 17 | Frame Sync Module Input Options                                            | 47  |

| 18 | AIF Clock Selection                                                        |     |

| 19 | System Timer Clock Selection                                               | 48  |