# **TPS65921 PCB Layout Guidelines**

# **Application Report**

Literature Number: SWCA091A October 2010–Revised March 2012

## Contents

| 1 | Introdu | ction 4                           |

|---|---------|-----------------------------------|

| 2 | TPS659  | 021 Layout Recommendations 4      |

|   | 2.1     | PCB Recommendation for Each Pin 4 |

|   | 2.2     | USB-Specific Recommendation       |

|   | 2.3     | Layout Examples 10                |

| 3 | Revisio | n History 15                      |

### List of Figures

| 1 | Critical Component Placement               | 10 |

|---|--------------------------------------------|----|

| 2 | VIO DCDC Layout Top                        | 11 |

| 3 | VIO DCDC Layout IN1                        | 11 |

| 4 | Power Layer Layout on PMIC Side            | 12 |

| 5 | USB Board Layout Bottom Side               | 13 |

| 6 | USB Board Layout TOP/IN1 Side              | 13 |

| 7 | Reference and 32-kHz Oscillator Layout Top | 14 |

| 8 | Reference and 32-kHz Oscillator Layout IN1 | 14 |

### List of Tables

| 1 | PCB Recommendation for Each Pin | 4  |

|---|---------------------------------|----|

| 2 | REVISION HISTORY                | 15 |

## **TPS65921 PCB Layout Guidelines**

#### ABSTRACT

This document describes how to connect the TPS65921 features during board layout.

#### 1 Introduction

Some TPS65921 features need specific attention during board layout. This document describes how to connect each ball on the PCB and what to do when functions are not used.

#### 2 TPS65921 Layout Recommendations

#### 2.1 PCB Recommendation for Each Pin

| Name                  | Ball | Туре    | I/O <sup>(1)</sup> | Description                                                                                   | PCB Recommendation | Not Used<br>Features <sup>(2)</sup> |

|-----------------------|------|---------|--------------------|-----------------------------------------------------------------------------------------------|--------------------|-------------------------------------|

| JTAG.TDO/GPIO         | L9   | Digital | I/O                | JTAG® test output or<br>GPIO0/card detection 1                                                |                    | Floating                            |

| ADCIN0                | F2   | Analog  | I/O                | General-purpose ADC input                                                                     |                    | Floating                            |

| STAR.ADC/JTAG.T<br>DI | H7   | Digital | I                  | ADC conversion request/JTAG test data input                                                   |                    | GND                                 |

| SDA                   | C4   | Digital | I/O                | General-purpose inter-<br>integrated circuit (I <sup>2</sup> C™)<br>bidirectional data signal |                    | N/A <sup>(3)</sup>                  |

| SCL                   | B3   | Digital | I/O                | General-purpose I <sup>2</sup> C<br>bidirectional clock signal                                |                    | N/A                                 |

| SRI2C_SDA             | D4   | Digital | I/O                | SmartReflex <sup>™</sup> I <sup>2</sup> C bidirectional data signal                           |                    | Floating                            |

| SRI2C_SCL             | A3   | Digital | I/O                | SmartReflex I <sup>2</sup> C bidirectional clock signal                                       |                    | GND                                 |

| PWRON                 | D5   | Digital | I                  | Input detects a control command to start or stop the system.                                  |                    | VBAT                                |

| REGEN                 | G3   | Digital | 0                  | Enable signal for external low-<br>dropout (LDO) regulator.                                   |                    | Floating                            |

| MSECURE               | G8   | Digital | I                  | Security and digital rights management                                                        |                    | IO.1P8                              |

| BOOT0                 | E5   | Digital | I                  | Power-up sequence selection                                                                   |                    | N/A                                 |

| BOOT1                 | F6   | Digital | I                  | Power-up sequence selection                                                                   |                    | N/A                                 |

| NRESPWRON             | E7   | Digital | 0                  | Output control the NRESETN of the application processor                                       |                    | Floating                            |

| NRESWARM              | H8   | Digital | I                  | Warm reset signal                                                                             |                    | GND                                 |

| NSLEEP                | K4   | Digital | I                  | ACTIVE-SLEEP state transition control signal                                                  |                    | GND                                 |

#### Table 1. PCB Recommendation for Each Pin

<sup>(1)</sup> I = Input, O = Output

<sup>(3)</sup> N/A = Not applicable

<sup>&</sup>lt;sup>(2)</sup> This column provides the connection when the associated feature is not used or not connected.

| Name      | Ball                | Туре    | I/O <sup>(1)</sup> | Description                                   | PCB Recommendation                                                                                                                                      | Not Used<br>Features <sup>(2</sup> |

|-----------|---------------------|---------|--------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| INT       | A9                  | Digital | 0                  | Interrupt line output                         |                                                                                                                                                         | Floating                           |

| SYSEN     | B9                  | Digital | 0                  | System enable output                          |                                                                                                                                                         | Floating                           |

| CLKEN     | F10                 | Digital | 0                  | Clock enable                                  |                                                                                                                                                         | Floating                           |

| CLK32KOUT | G6                  | Digital | 0                  | 32-kHz clock output                           |                                                                                                                                                         | Floating                           |

| 32KXOUT   | G11                 | Analog  | 0                  | 32-kHz crystal oscillator                     | Sensitive balls. Route as<br>differential pair. Place<br>crystal as close as possible<br>to balls.                                                      | Floating                           |

| 32KXIN    | H11                 | Analog  | I                  | _                                             |                                                                                                                                                         | N/A                                |

| HFCLKIN   | C8                  | Analog  | I                  | Sine wave or square wave input                | High-speed (HS) clock.<br>Keep away from sensitive<br>signals.                                                                                          | N/A                                |

| HFCLKOUT  | K8                  | Digital | 0                  | 50% duty cycle square wave output             | HS clock. Keep away from sensitive signals.                                                                                                             | Floating                           |

| VREF      | G10                 | Analog  | 0                  | Reference voltage                             | Very sensitive, connect capacitor close ball                                                                                                            | N/A                                |

| GND_AGND  | K7                  | Analog  | I/O                | Substrate ground                              | Connect to a clean ground.                                                                                                                              | GND                                |

| AGND      | H10                 | Analog  | I/O                | Reference ground                              | Connect to a clean ground<br>same as 32-kHz oscillator<br>foot capacitor ground and<br>VREF capacitor ground.                                           | GND                                |

| DGND      | B8                  | Power   | I/O                | Digital ground                                | Do not connect with<br>DCDC/charge pump<br>ground.                                                                                                      | GND                                |

| IO.1P8    | A10                 | Power   | I                  | Supply for input/output (I/O) buffers (VDDIO) |                                                                                                                                                         | N/A                                |

| VBACKUP   | G9                  | Power   | I                  | Must be shorted to GND                        |                                                                                                                                                         | GND                                |

| VDD1.IN   | E9,<br>E10,<br>E11  | Power   | I                  | VDD1 DCDC input                               | High current (≈2.5-A peak)<br>and noisy balls. Place input<br>capacitor close to balls.<br>Connect input capacitor<br>ground to VDD1.GND.               | VBAT                               |

| VDD1.GND  | A11,<br>B10,<br>B11 | Power   | I/O                | VDD1 DCDC power ground                        | High current (≈2.5-A peak)<br>pin. Connect to separate<br>GND plane. Connect<br>separate plane to main<br>plane in a single point to<br>avoid GND loop. | GND                                |

| VDD1.L    | C10,<br>C11,<br>D10 | Power   | 0                  | VDD1 DCDC switched output                     | High current (≈2.5-A peak)<br>and noisy balls. Connect<br>with shortest shape to<br>inductor.                                                           | Floating                           |

| VDD1.FDBK | D11                 | Analog  | I                  | VDD1 feedback voltage<br>(output)             | Sensitive signal. Keep<br>away from noisy signals as<br>VDD1.L. Connect output<br>capacitor ground to<br>VDD1.GND.                                      | GND                                |

| VDD2.IN   | K10,L1<br>0         | Power   | I                  | VDD2 DCDC input                               | High current (≈1.2-A peak)<br>and noisy balls. Place input<br>capacitor close to<br>balls. Connect input<br>capacitor ground to<br>VDD2.GND.            | VBAT                               |

| VDD2.GND  | J10,<br>J11         | Power   | I/O                | VDD2 DCDC power ground                        | High current (≈1.2-A peak)<br>pin. Connect to separate<br>GND plane. Connect<br>separate plane to main<br>plane in a single point to<br>avoid GND loop. | GND                                |

| Table 1. PCB | Recommendation | for | Each | Pin | (continued) |

|--------------|----------------|-----|------|-----|-------------|

|--------------|----------------|-----|------|-----|-------------|

| Name        | Ball        | Туре   | I/O <sup>(1)</sup> | Description                                         | PCB Recommendation                                                                                                                                   | Not Used<br>Features <sup>(2)</sup> |

|-------------|-------------|--------|--------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| VDD2.L      | K11,<br>L11 | Power  | 0                  | VDD2 DCDC switched output                           | High current (≈1.2-A peak)<br>and noisy balls. Connect<br>with shortest shape to<br>inductor.                                                        | Floating                            |

| VDD2.FDBK   | H9          | Analog | I                  | VDD2 feedback voltage<br>(output)                   | Sensitive signal. Keep<br>away from noisy signals as<br>VDD2.L. Connect output<br>capacitor ground to<br>VDD2.GND.                                   | GND                                 |

| VIO.IN      | K2, L2      | Power  | I                  | VIO DCDC input                                      | High current (≈1.4-A peak)<br>and noisy balls. Place input<br>capacitor close to balls.<br>Connect input capacitor<br>ground to VIO.GND.             | VBAT                                |

| VIO.GND     | J1, J2      | Power  | I/O                | VIO DCDC power ground                               | High current pin (≈1.4-A<br>peak). Connect to<br>separate GND plane.<br>Connect with main plane in<br>a single point to avoid GND<br>loop.           | GND                                 |

| VIO.L       | K1, L1      | Power  | 0                  | VIO DCDC switched output                            | High current (≈1.4-A peak)<br>and noisy balls. Connect<br>with shortest shape to<br>inductor.                                                        | Floating                            |

| VIO.FDBK    | H1          | Analog | I                  | VIO feedback voltage (output)                       | Sensitive signal. Keep<br>away from noisy signals as<br>VIO.L. No current, route<br>with thin net. Connect<br>output capacitor ground to<br>VIO.GND. | GND                                 |

| VAUX12S.IN  | F1          | Power  | I                  | VAUX LDO input                                      | 100-mA trace. Place capacitor close to ball.                                                                                                         | VBAT                                |

| VAUX.OUT    | G1          | Power  | 0                  | VAUX regulator output                               | 100-mA trace. Place capacitor close to ball.                                                                                                         |                                     |

| VPLLA3R.IN  | A6          | Power  | I                  | VPLL//VRTC LDO input                                | 70-mA trace. Place capacitor close to ball.                                                                                                          | VBAT                                |

| VPLL1.OUT   | A8          | Power  | 0                  | VPLL LDO output                                     | 40-mA trace. Place capacitor close to ball.                                                                                                          | Floating                            |

| VRTC.OUT    | B5          | Power  | 0                  | VRTC internal LDO output<br>(internal use only)     | Place capacitor close to ball.                                                                                                                       | N/A                                 |

| VINT.IN     | A7          | Power  | I                  | VINTDIG LDO input                                   | 100-mA trace. Place capacitor close to ball.                                                                                                         | VBAT                                |

| VINTANA1    | D1          | Power  | 0                  | VINTANA1 internal LDO output<br>(internal use only) | Place capacitor close to ball.                                                                                                                       | N/A                                 |

| VINTANA2    | A2          | Power  | 0                  | VINTANA2 internal LDO output<br>(internal use only) | Place capacitor close to ball.                                                                                                                       | N/A                                 |

| VDAC.IN     | C1          | Power  | I                  | VDAC/VINTANA1/VINTAN2<br>LDO input                  | 370-mA trace. Place capacitor close to ball.                                                                                                         | VBAT                                |

| VDAC.OUT    | E1          | Power  | 0                  | VDAC LDO output                                     | 70-mA trace. Place capacitor close to ball.                                                                                                          | Floating                            |

| VINTDIG.OUT | B7          | Power  | 0                  | VINTDIG internal LDO output<br>(internal use only)  | Place capacitor close to ball.                                                                                                                       | N/A                                 |

| VMMC.IN     | B1          | Power  | I                  | VMMC Input LDO                                      | 220-mA trace. Place capacitor close to ball.                                                                                                         | VBAT                                |

| VMMC1.OUT   | A1          | Power  | 0                  | VMMC LDO output                                     | 220-mA trace. Place capacitor close to ball.                                                                                                         | Floating                            |

| VBAT.USB    | K6          | Power  | I                  | VUSB1P8, VUSB1P5, and VUSB3P1 regulators input      | Place capacitor close to ball.                                                                                                                       | VBAT                                |

Table 1. PCB Recommendation for Each Pin (continued)

| Name        | Ball | Туре       | I/O <sup>(1)</sup> | Description                                      | PCB Recommendation                                                                                                    | Not Used                       |

|-------------|------|------------|--------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|

| VUSB.3P1    | L6   | Power      | 0                  | VUSB.3P1 LDO output                              | Place capacitor close to ball.                                                                                        | Features <sup>(2)</sup><br>N/A |

| VUSB1P8.OUT | J6   | Power      | 0                  | VUSB1P8 LDO output (internal use only)           | Place capacitor close to ball.                                                                                        | Floating                       |

| VUSB1P5.OUT | J5   | Power      | 0                  | VUSB1P5 LDO output (internal use only)           | Place capacitor close to ball.                                                                                        | Floating                       |

| TESTV1      | H2   | Analog     | IO                 | Analog test pin 1                                |                                                                                                                       | Floating                       |

| TESTV2      | C9   | Analog     | IO                 | Analog test pin 2                                |                                                                                                                       | Floating                       |

| TEST        | D3   | Digital    | IO                 | Selection between JTAG mode and application mode |                                                                                                                       | Floating                       |

| AVSS1       | F3   | Power      | I/O                | Analog ground                                    |                                                                                                                       | GND                            |

| AVSS2       | H6   | Power      | I/O                | Analog ground                                    |                                                                                                                       | GND                            |

| AVSS3       | F9   | Power      | I/O                | Analog ground                                    |                                                                                                                       | GND                            |

| AVSS4       | A4   | Power      | I/O                | Analog ground                                    |                                                                                                                       | GND                            |

| VBUS        | K5   | Power      |                    | VBUS power rail                                  | 100-mA trace                                                                                                          | N/A                            |

| DP          | L7   | Analog     | I/O                | USB differential data line                       | See Section 2.2 of the USB PCB recommendation.                                                                        | N/A                            |

| DM          | L8   | Analog     | I/O                | USB differential data line                       | ] [                                                                                                                   | N/A                            |

| ID          | J7   | Digital    | I/O                | USB ID                                           |                                                                                                                       | Floating                       |

| UCLK        | D6   | Digital    | I/O                | HS USB clock                                     |                                                                                                                       | Floating                       |

| STP         | E6   | Digital    | I/O                | HS USB stop                                      |                                                                                                                       | Floating                       |

| DIR         | A5   | Digital    | I/O                | HS USB direction                                 |                                                                                                                       | Floating                       |

| NXT         | C5   | Digital    | I/O                | HS USB next                                      |                                                                                                                       | Floating                       |

| DATA0       | B6   | Digital    | I/O                | HS USB Data0                                     |                                                                                                                       | Floating                       |

| DATA1       | C6   | Digital    | I/O                | HS USB Data1                                     |                                                                                                                       | Floating                       |

| DATA2       | C7   | Digital    | I/O                | HS USB Data2                                     |                                                                                                                       | Floating                       |

| DATA3       | D7   | Digital    | I/O                | HS USB Data3                                     |                                                                                                                       | Floating                       |

| DATA4       | F8   | Digital    | I/O                | HS USB Data4                                     |                                                                                                                       | Floating                       |

| DATA5       | F11  | Digital    | I/O                | HS USB Data5                                     |                                                                                                                       | Floating                       |

| DATA6       | E8   | Digital    | I/O                | HS USB Data6                                     |                                                                                                                       | Floating                       |

| DATA7       | D9   | Digital    | I/O                | HS USB Data7                                     |                                                                                                                       | Floating                       |

| CP_IN       | L4   | Power      | I/O                | Charge pump input voltage                        | 200-mA trace. Noisy ball.<br>Place input capacitor close<br>to balls. Connect input<br>capacitor ground to<br>CP_GND. | VBAT                           |

| CP_GND      | J3   | Power GND  | I/O                | Charge pump ground                               | Connect to separate GND<br>plane. Connect separate<br>plane to main plane in a<br>single point to avoid GND<br>loop.  | GND                            |

| CP_CAPP     | L5   | Analog     | I/O                | Charge pump flying capacitor P                   | Place fly capacitor as close as possible to balls.                                                                    | Floating                       |

| CP_CAPM     | L3   | Analog     | I/O                | Charge pump flying capacitor M                   |                                                                                                                       |                                |

| KPD.C0      | B4   | Open-drain | 0                  | Keypad column 0                                  |                                                                                                                       | Floating                       |

| KPD.C1      | D2   | Open-drain | 0                  | Keypad column 1                                  |                                                                                                                       | Floating                       |

| KPD.C2      | E2   | Open-drain | 0                  | Keypad column 2                                  |                                                                                                                       | Floating                       |

| KPD.C3      | B2   | Open-drain | 0                  | Keypad column 3                                  |                                                                                                                       | Floating                       |

| KPD.C4      | C2   | Open-drain | 0                  | Keypad column 4                                  |                                                                                                                       | Floating                       |

| KPD.C5      | E4   | Open-drain | 0                  | Keypad column 5                                  |                                                                                                                       | Floating                       |

| KPD.C6      | E3   | Open-drain | 0                  | Keypad column 6                                  |                                                                                                                       | Floating                       |

| Table 1. PCB | Recommendation | for Eac | h Pin | (continued) |

|--------------|----------------|---------|-------|-------------|

|              |                |         |       | (001111100) |

| Name          | Ball | Туре       | I/O <sup>(1)</sup> | Description                                    | PCB Recommendation                                             | Not Used<br>Features <sup>(2)</sup> |

|---------------|------|------------|--------------------|------------------------------------------------|----------------------------------------------------------------|-------------------------------------|

| KPD.C7        | F4   | Open-drain | 0                  | Keypad column 7                                |                                                                | Floating                            |

| KPD.R0        | H5   | Digital    | I                  | Keypad row 0                                   |                                                                | Floating                            |

| KPD.R1        | G4   | Digital    | I                  | Keypad row 1                                   |                                                                | Floating                            |

| KPD.R2        | H4   | Digital    | I                  | Keypad row 2                                   |                                                                | Floating                            |

| KPD.R3        | G5   | Digital    | I                  | Keypad row 3                                   |                                                                | Floating                            |

| KPD.R4        | J4   | Digital    | I                  | Keypad row 4                                   |                                                                | Floating                            |

| KPD.R5        | J8   | Digital    | I                  | Keypad row 5                                   |                                                                | Floating                            |

| KPD.R6        | G7   | Digital    | I                  | Keypad row 6                                   |                                                                | Floating                            |

| KPD.R7        | F5   | Digital    | I                  | Keypad row 7                                   |                                                                | Floating                            |

| VBAT          | K3   | Power      | I/O                | Battery input voltage                          | Battery sense pin, very sensitive. Connect to a clean Vsystem. | VBAT                                |

| CLKREQ        | D8   | Digital    | I                  | Clock request                                  |                                                                | GND                                 |

| TEST.RESET    | J9   | Digital    | I                  | Reserved                                       |                                                                | GND                                 |

| VPROG         | H3   | Analog     | I                  | Reserved                                       |                                                                | GND                                 |

| JTAG.TCK      | F7   | Digital    | I                  | JTAG clock input                               |                                                                | GND                                 |

| JTAG.TMS/GPIO | К9   | Digital    | I/O                | JTAG test mode state or GPIO1/card detection 2 |                                                                | Floating                            |

| TEST2/GPIO2   | G2   | Digital    | I                  | Digital test pin/GPIO2                         |                                                                | Floating                            |

| Table 1. PCB Recommendation | for Each Pin | (continued) |

|-----------------------------|--------------|-------------|

|-----------------------------|--------------|-------------|

#### 2.2 USB-Specific Recommendation

#### 2.2.1 General Considerations

- USB design requires symmetrical termination and symmetrical components placement along DP and DM paths.

- Place the USB host controller and major components on the unrouted board first.

- Place the USB host controller as close as possible to the transceiver device; for example, ULPI traces as short as possible.

- Route the HS clock and HS USB. Route differential pairs first.

- Maintain the maximum possible distance between HS clocks/periodic signals to the HS USB differential pairs and any connector leaving the PCB (such as I/O connectors, control and signal headers, and power connectors).

- The maximum TI-recommended external capacitance on DP (or DM) lines is 4 pF.

- This capacitance is the sum of all external discrete components; that is, the total capacitance on DP/DM lines, including trace capacitance, can be larger than 4 pF.

- All discrete components must be placed as close as possible to the USB receptacle.

- Place low-capacitance ESD protections as close as possible to the USB receptacle, with no other external devices in between.

- Common mode chokes degrade signal quality; thus, they must be used only if EMI performance enhancement is necessary.

- Place common mode chokes (if required to improve EMI performance) as close as possible to the USB receptacle, but after the ESD device(s).

#### 2.2.2 USB Interface (DP/DM)

- Route the USB receptacle ground pin to the analog ground plane of the device with multiple vias connections.

- Route the DP/DM trace pair together.

- For HS-capable devices, route the DP/DM signals from the device to the USB receptacle with the optimum trace length of 5 cm, and the maximum trace length 1-way delay of 0.5 ns (7.5 cm for 67 ps/cm in FR-3).

- Match DP/DM trace lengths. The maximum mismatch allowed is 150 mils (~0.4 cm).

- Route DP/DM signals with 90-Ω differential impedance, and 22.5~30-Ω common-mode impedance (the objective is to have Zodd ~= Z0 = Zdiff/2 = 45 Ω)

- Use an impedance calculator to determine the trace width and spacing required for the specific board stackup being used.

- Keep the maximum possible distance between DP/DM signals from other platform clocks, power sources, and digital/analog signals.

- Do not route DP/DM signals over/under crystals, oscillators, clock synthesizers, magnetic devices, and ICs that use clocks.

- Avoid changing the routing layer for DP/DM traces; if unavoidable, use multiple vias.

- Minimize bends and corners on DP/DM traces.

- When it becomes necessary to turn 90 degrees, use two 45-degree turns or an arc instead of one 90degree turn. This reduces reflections on the signal by minimizing impedance discontinuities.

- Avoid creating stubs on DP/DM traces, because stubs cause signal reflections and affect global signal quality.

- If stubs are unavoidable, they must be lower than 200 mils (~0.5 cm).

- Route DP/DM signals over continuous VCC or GND planes without interruption, avoiding crossing antietch (plane splits), which increases inductance and radiation levels by introducing a greater loop area.

- Route DP/DM signals at least 25 mils (~0.65 mm) away from any plane splits.

- Follow the 20 \* h rule of thumb by keeping traces at least 20 \* (height above the plane) away from the edge of the plane (VCC or GND, depending on the plane the trace is over).

- Changing signal layers is preferable to crossing plane splits if a choice must be made.

- If crossing a plane split is unavoidable, proper placement of stitching caps can minimize the adverse effects on EMI and signal quality performance caused by crossing the split.

- Avoid anti-etch on the ground plane.

#### 2.2.3 ULPI Interface

- Route the ULPI 12-pin bus as a 50- $\Omega$  single-ended nonterminated adapted bus.

- Route the ULPI 12-pin bus with minimum trace lengths and a strict maximum of 50 mm, to ensure timing. Match 12 ULPI signal trace lengths.

- Route the ULPI 12-pin bus as clock signals and set a minimum spacing of three times the trace width (S < 3W).</li>

www.ti.com

#### 2.3 Layout Examples

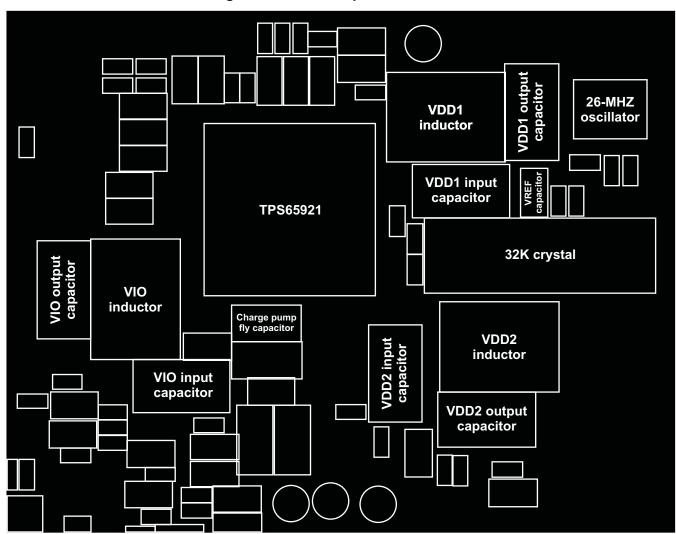

#### 2.3.1 Critical Component Placement

**Figure 1. Critical Component Placement**

SWCA091-001

#### 2.3.2 DCDC Layout:VIO

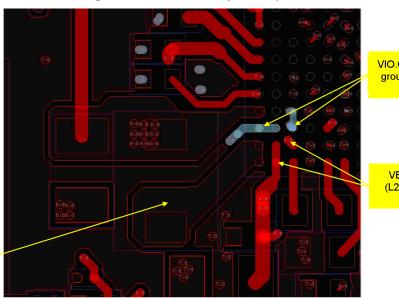

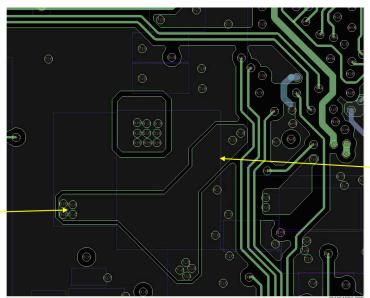

Figure 2. VIO DCDC Layout Top

VIO.GND ground and other ground are not connected together.

VBAT (K3) and VIO.IN (L2, K2) have separated power supply

Shape between VIO.L and inductor

Figure 3. VIO DCDC Layout IN1

Dedicated ground shape connecting VIO.GND, input capacitor ground, and output capacitor ground only

Vias connecting output capacitor ground to VIO dedicated ground shape and dedicated ground to main ground on one point

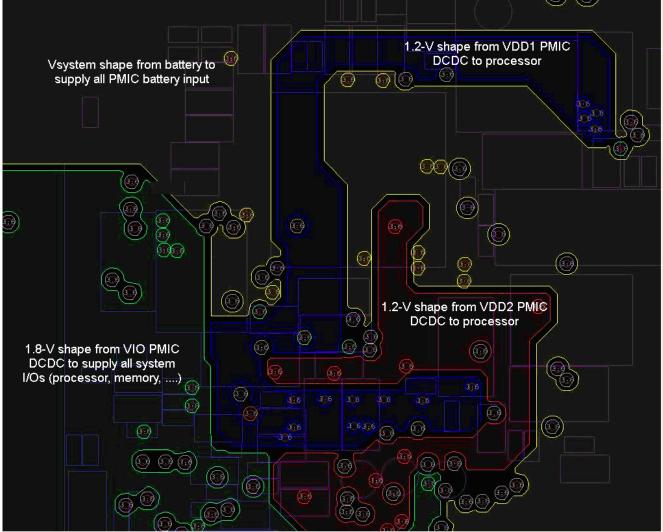

#### 2.3.3 Power Supply Layout

A layer must be used for system power. Use shape for Vsystem and a DCDC-to-processor connection to minimize the loss of power in the PCB (see Figure 4).

#### Figure 4. Power Layer Layout on PMIC Side

SWCA091-004

www.ti.com

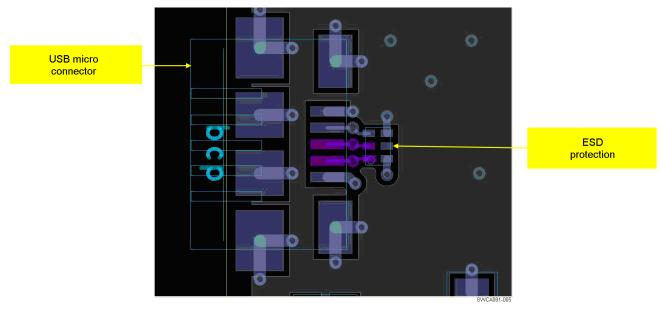

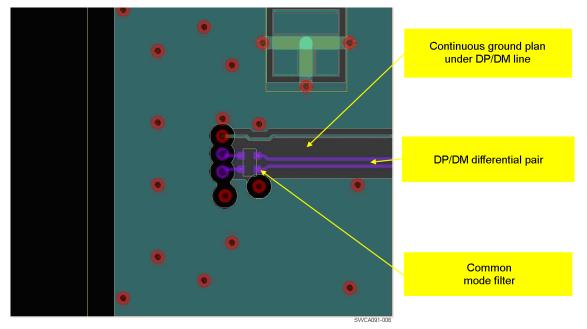

#### 2.3.4 USB Connector Layout

#### Figure 5. USB Board Layout Bottom Side

Figure 6. USB Board Layout TOP/IN1 Side

www.ti.com

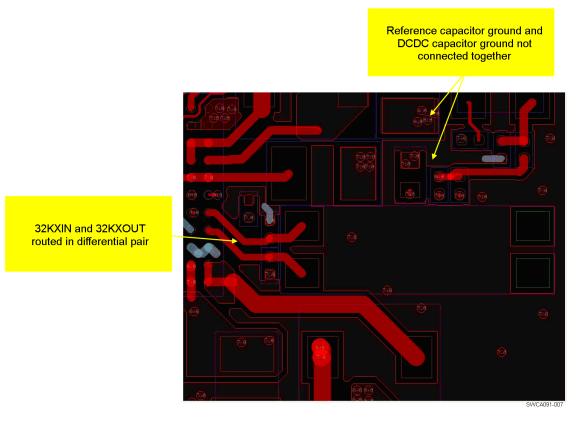

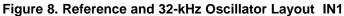

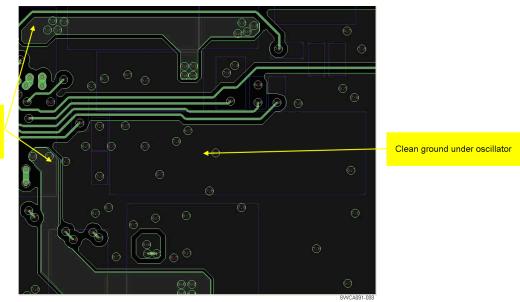

#### 2.3.5 32-kHz and Reference Layout

#### Figure 7. Reference and 32-kHz Oscillator Layout Top

Noisy ground (DCDC ground) not connected to reference or oscillator ground

#### 3 Revision History

#### Table 2. REVISION HISTORY

| Version | Literature Number | Date         | Notes                |

|---------|-------------------|--------------|----------------------|

| *       | SWCA091           | October 2010 | See <sup>(1)</sup> . |

| А       | SWCA091           | March 2012   | See <sup>(2)</sup>   |

<sup>(1)</sup> TPS65921 PCB Layout Guidelines, SWCA091 - Initial release.

<sup>(2)</sup> TPS65921 PCB Layout Guidelines, SWCA091A - Table 1: Swap and update ground desctions

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

. . ..

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers             | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters        | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products          | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                    | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers      | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface              | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                  | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt             | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 |                               |                                   |

#### TI E2E Community Home Page

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2012, Texas Instruments Incorporated