# TIDA-00588

# TI Designs Energy Harvester Booster Pack

# 🤄 Texas Instruments

### **TI Designs**

TI Designs provide the foundation that you need including methodology, testing and design files to quickly evaluate and customize the system. TI Designs help you accelerate your time to market.

#### **Design Resources**

<u>TIDA-00588</u> <u>bq25570</u> TPS61220

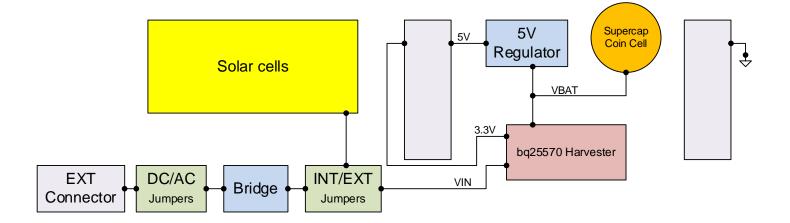

#### **Block Diagram**

### **Design Features**

- Energy harvesting booster pack designed for any low power Launchpad

- Converter/Charger that manages energy harvesting current sources

- Efficient nano-power buck converter

- Programmable Dynamic MPPT (Maximum Power Point Tracking)

- Super cap or coin cell storage to 50mA

- On board solar cells or external current source

- 3.3Vdc from the bq25570 to power the Launchpad

- 5V boost to power support circuitry

- Stackable design allows for creating a complete solution

### **Featured Applications**

- Factory Automation and Process Control

- Sensors and Field Transmitters

- Building Automation

- Portable Instruments

- IoT (Internet of Things)

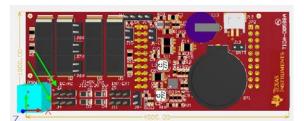

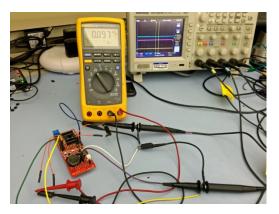

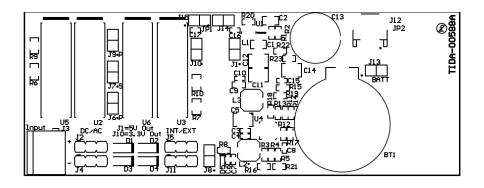

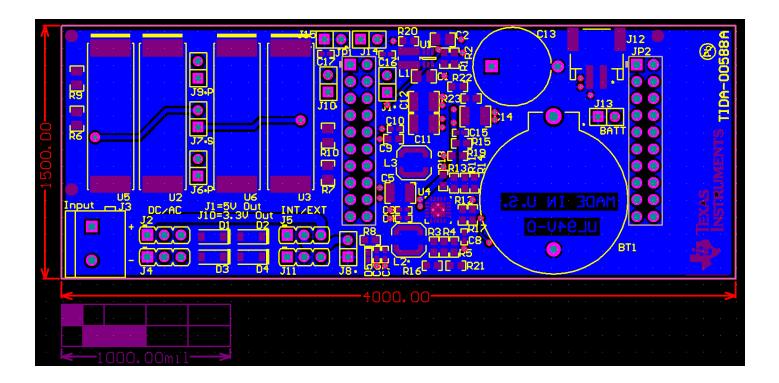

### **Board Image**

Energy Harvester Booster Pack

# **1 Key System Specifications**

| bq25570     | Value   |     | Description                                                                                                                                       |

|-------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| VINmins     | 0.33    | Vdc | Minimum Startup input voltage                                                                                                                     |

| VINminr     | 0.1     | Vdc | Minimum operating input voltage                                                                                                                   |

| I_INmin     | 280     | uA  | Minimum required current to startup the bq25570 with 5V boost                                                                                     |

| P_INmin     | 0.00009 | W   | Power to startup the bq25570 with the 5V regulator (there is no minimum power requirement to startup with the 5V regulator removed for operation) |

| VBAT_OK_on  | 3.51    | Vdc | VBAT threshold Turn On                                                                                                                            |

| VBAT_OK_off | 3.42    | Vdc | VBAT threshold Turn Off                                                                                                                           |

| Vout_3      | 3.322   | Vdc | Buck output of the bq25570                                                                                                                        |

| lout_3_c    | 50      | mA  | Max current output of the regulator with a coin cell                                                                                              |

| lout_3_s    | 0.8     | mA  | Max current output of the regulator with a super cap                                                                                              |

| V_ch        | 4.188   | Vdc | Battery charge voltage                                                                                                                            |

| TPS61220    |         |     |                                                                                                                                                   |

| Vout_5      | 5.09    | Vdc | Boost output of the 5V regulator                                                                                                                  |

| lout_5_c    | 10      | mA  | Max current output of the regulator with a coin cell                                                                                              |

| lout_5_s    | 0.5     | mA  | Max current output of the regulator with a supercap                                                                                               |

| I_q         | 18      | uA  | Quiescent Current                                                                                                                                 |

| I_std       | 4.7     | uA  | Standby current                                                                                                                                   |

| Freq        | 1.25    | MHZ | Idle current PWM frequency                                                                                                                        |

| LIR2032     |         |     |                                                                                                                                                   |

| MAX_V       | 4.2     | Vdc | Max charge voltage                                                                                                                                |

| NOM_V       | 3.6     | Vdc | Nominal Voltage                                                                                                                                   |

| MIN_V       | 2.8     | Vdc | Minimum Voltage                                                                                                                                   |

| CH_CUR      | 30      | mA  | Max charge current                                                                                                                                |

| C_rate      | 50      | mA  | Max continuous current                                                                                                                            |

| I_max       | 60      | mA  | Max peak current                                                                                                                                  |

# 2 System Description

This is an Energy Harvester Booster Pack and is designed with the flexibility to support a variety of current source inputs and energy storage elements. Use this booster pack with your favorite TI Launchpad development board to power your design from a local source of energy.

There are jumpers on the board that will allow the use of the internal 4 cell solar array that can be operated in 4s or in a 2s2p parallel mode. The user can set the jumpers to use the internal or an external current source. There is a bridge diode to convert AC to DC if needed. Most systems will typically need some type of energy storage element such as a rechargeable battery, super capacitor, or conventional capacitor. This system has an on board Super capacitor, a socket for an LIR2032 coin cell and a connector that can be used to add your own lithium storage element. To prevent damage to the storage element, both maximum and minimum voltages are monitored against the internally set under-voltage (UV) and user programmable over-voltage (OV) levels.

To further assist users in the strict management of their energy budgets, the bq25570 toggles the battery good (VBAT\_OK) flag to signal an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a pre-set critical level. This should trigger the reduction of load currents to prevent the system from entering an under voltage condition. There is also independent enable signals to allow the system to control when to run the regulated output or even put the whole IC into an ultra-low quiescent current sleep state.

In addition to the boost charging front end, the bq25570 provides the system with an externally programmable regulated supply via the buck converter. The regulated output has been optimized to provide high efficiency across low output currents (< 10  $\mu$ A) to high currents (~110 mA). The buck converter on the bq25570 will provide 3.3Vdc for the Launchpad power and an additional switching boost converter will supply 5V to run accessories.

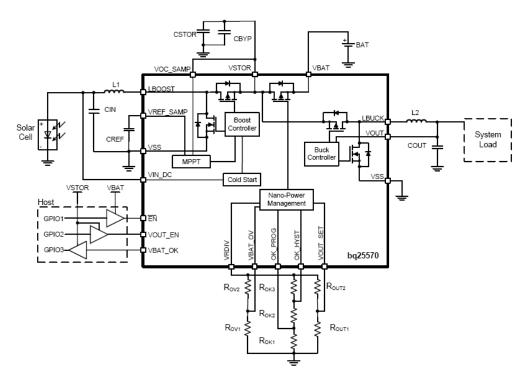

# 2.1 Bq25570

The bq25570 device is a highly integrated energy harvesting Nano-Power management solution that is well suited for meeting the special needs of ultra-low-power applications. The product is specifically designed to efficiently acquire and manage the microwatts ( $\mu$ W) to milliwatts (mW) of power generated from a variety of DC sources like photovoltaic (solar) or thermal electric generators targeted toward products and systems, such as wireless sensor networks (WSN) which have stringent power and operational demands. The main boost charger is powered from the boost output, VSTOR. Once the VSTOR voltage is above VSTOR\_CHGEN (1.8 V typical), for example, after a partially discharged battery is attached to VBAT, the boost charger can effectively extract power from low voltage output harvesters such as TEGs or single or dual cell solar panels outputting voltages down to VIN(DC) (100 mV minimum). When starting from VSTOR=VBAT < 100 mV, the cold start circuit needs at least VIN(CS), 330 mV typical, to charge VSTOR up to 1.8 V.

The bq25570 also implements a programmable maximum power point tracking sampling network to optimize the transfer of power into the device. The fraction of open circuit voltage that is sampled and held can be controlled by pulling VOC\_SAMP high or low (80% or 50% respectively) or by using external resistors. This sampled voltage is maintained via internal sampling circuitry and held with an external capacitor (CREF) on the VREF\_SAMP pin. For example, solar cells typically operate with a maximum power point (MPP) of 80% of their open circuit voltage. Connecting VOC\_SAMP to VSTOR sets the MPPT threshold to 80% and results in the IC regulating the voltage on the solar cell to ensure that the VIN\_DC voltage does not fail below the voltage on CREF which equals 80% of the solar panel's open circuit voltage. Alternatively, an external reference voltage can be provided by a MCU to produce a more complex MPPT algorithm.

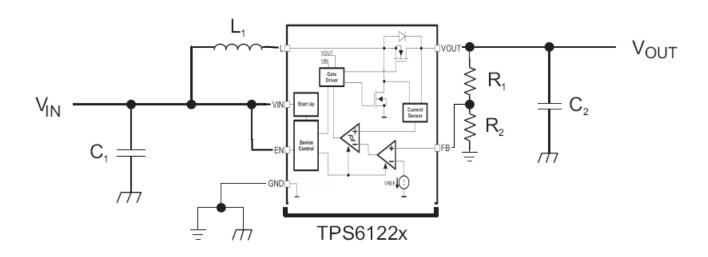

# 2.2 TI TPS61220

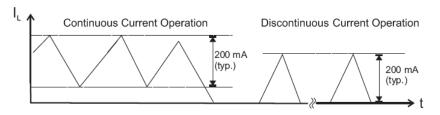

The TPS6122x is a high performance, high efficient family of switching boost converters. To achieve high efficiency, the power stage is realized as a synchronous-boost topology. For the power switching, two actively controlled low-RDSon power MOSFETs are implemented.

The device is controlled by a hysteretic current mode controller. This controller regulates the output voltage by keeping the inductor ripple current constant in the range of 200 mA and adjusting the offset of this inductor current depending on the output load. If the required average input current is lower than the average inductor current defined by this constant ripple current, the inductor current becomes discontinuous to keep the efficiency high under low-load conditions.

The output voltage VOUT is monitored via the feedback network which is connected to the voltage error amplifier. To regulate the output voltage, the voltage error amplifier compares this feedback voltage to the internal voltage reference and adjusts the required offset of the inductor current accordingly. In fixed output voltage devices, an internal feedback network is used to program the output voltage. In adjustable versions an external resistor divider is required. The self-oscillating hysteretic current mode architecture is inherently stable and allows fast response to load variations. This architecture also allows using a wide range of inductor and capacitor values.

# **3 Getting Started**

The Energy Harvester Booster Pack can be a great addition to you design development. Having a good understanding of some of the key features is very important. Before you start, take the time to understand these important concepts.

# 3.1 Coin Cell

The coin cell is a LIR2032 Lithium Battery. The max charge current is 30mA. The max constant current is 50mA and the max peak current is 60mA. These specifications come from the battery manufacture. You should become familiar with this battery and it's limitations before using it in a design.

There is no adjustable current limit setting on the bq25570. This IC is capable of charging up to 100mA. It is up to the designer to measure and understand the capabilities of the current source they are using. For example the IXYS KXOB22-04X3L has a short circuit current of 15mA, and therefore will never be capable of charging at a current that is above the maximum current capability of the LIR2032. If you use an external current source that has more than 30mA short circuit current you may damage the coin cell battery. You may need to use an external battery that can handle the higher charge current.

# 3.2 Solar Cell

The solar cell is an IXYS KXOB22-04X3L. The typical efficiency is 22%. This cell has a very good response over a wide wavelength range and therefore can be used in both indoor and outdoor applications.

A standard desk lamp has a 400-800 LUX value. When using this solar cell indoors you can expect between 5uW to 40uW of power. This is not a lot of energy so when using any energy harvesting circuit create your design for low power and remember to use sleep mode techniques to minimize your power requirements and plan accordingly. When used properly energy harvesting can run you design for many years without needing batteries.

# 3.3 Super Capacitor

This circuit has a 47mF super capacitor on board. A simple low power circuit can run on this super cap without batteries. The biggest difference between a battery and a supercap besides the capacity is that a battery has a minimum charge voltage that is usually between 2.5Vdc and 3.0Vdc. This means that the battery will always have a small amount or energy stored at all times. The super cap does not have a minimum voltage and also has a high leakage current (usually a few micro amps, this is a lot compared to most batteries). What this means is that when starting your energy harvester the super cap voltage will most likely be zero volts. The bq25570 will start up with 300mV input from the current source and will charge the super cap in a reduced cold start mode until the supercap voltage reaches 1.8Vdc. The bq25570 will then begin normal charging. Under normal room lighting the light level can be 150-800 LUX. This means that the super cap has to be charged to 3.5Vdc before anything will turn on. This can take several hours to startup the super cap. This time can be reduced by increasing the light level. Sun light can start up the super cap in a few minutes. Using a super cap as your only method of storage is usually meant for very low power and intermittent circuits that never turn off and can afford the occasional long start up time.

Note: Having a battery in circuit will mean that your device will start up almost immediately if the battery voltage is above 3.4Vdc

# 3.4 External Battery

The use of an external battery is possible with the external battery connector supplied on the board. There are a few design concerns when using an external battery. First it is the responsibility of the designer to provide battery protection for your design. The max charge current from the bq25570 is 100mA and the max charge voltage is 4.2Vdc. The max charge voltage is resister programmable, so if you are using other battery chemistries you mush reprogram the bq25570 to meet the required manufactures specifications. With an external battery with a cRate above 200mAh the 3.3V regulator and the 5V regulator can supply up to 100mA each.

# 3.5 3.3V and 5.0V regulators

The bq25570 has an internal buck regulator. The output voltage is resister programmed for 3.3Vdc. This regulator can supply up to 100mA of current, however the coin cell can only supply 50mA, so it is up to the user to make sure that there circuit does not draw more than the maximum current that the battery can supply. The 5V regulator is a boost circuit. It runs off of the energy storage device (Super cap, coin cell or battery). The quiescent current of the 5V regulator is about 5uA.When starting a super cap from zero volts, and the light level is very low, the bq25570 start up current may be below the 5V regulator quiescent current and may never start up. It is recommended to disconnect the 5V regulator when using a super cap with low light levels. The 3.3Vdc buck will not turn on until the VBAT reaches 3.5Vdc. The quiescent current of the buck is about 450nA. Startup is possible with as little as 5uW of harvested input power.

# 3.6 Jumpers

This section will help the user to set up and configure the energy harvester for basic and custom applications

# 3.6.1 Solar cells configuration

J6 and J9 (Green Arrows) will place the 4 solar cells into a 2s2p (2 cells in series and 2 series cell string in parallel. The benefit is a higher current in higher light levels.

J7 will place all of the solar cells in series. The benefit is a higher operating voltage in lower light level applications.

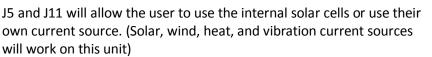

# 3.6.2 Internal and external current sources

Move both jumpers J5 (Positive) and J11 (Negative) to the left to use the onboard solar cells and move both jumpers to the right to use the input connector J3 to connect your own current source

# 3.6.3 DC\AC operations

TEXAS

J2 (positive) and J4 (negative) jumpers will allow the user to connect a DC or AC current source to the energy harvester.

Move J2 and J4 to the left will bypass the bridge rectifier and for DC applications. Move J2 and J4 to the right for AC current sources (Wind generators and vibration current sources)

# 3.6.4 Regulators

J13 and J8 are test pins. They are the connectors with the blue arrows. Never place a jumper across these connectors as it will be a direct short.

J15 is a 2 pin ground connection used for connecting test equipment

J14 is the enable pin for the 5V Regulator. Remove this jumper and the 5V Regulator will not start up. (It will draw 5uA in quiescent current in this mode)

J1 will disconnect the output of the 5V regulator from the header pins. These pins can also be used to measure current out of the 5V regulator by adding a current shunt or meter in series

J10 will disconnect the output of the 3.3V regulator from the header pins. These pins can also be used to measure current out of the 3.3V regulator by adding a current shunt or meter in series.

R22 is a zero Ohm resister and can be removed to fully disconnect the 5V input from the energy storage. This will also remove the quiescent current of the regulator. Add a current shunt or meter in series with the pads of this part to measure current in and out of the 5V regulator. To fully isolate the 5V regulator, also remove J1 and J14.

R23 is a zero Ohm resister and can be removed to isolate all of the storage devices. Add a current shunt or meter in series with the pads of this part to measure current in and out of the storage elements.

# 4 Test Setup

Description of the test setup

Test equipment:

- TDS2024B Tektronix Scope

- 189 Fluke Multi-meter

- 2400 Keithley Source Meter

- DI-158U Dataq Data Acquisition Module

- 2 1 Ohm 1% 5W Precision shunts

The use of a precision multi-meter along with a 1 Ohm shunt will make a great current measuring solution. Set the meter to the DC milli-volt scale and read the current as milli and micro Amps. Example: 1mV = 1mA

The source meter was used to supply a current limited source input for the startup cycles. This was better than attempting to find light sources that would provide the different currents needed to demonstrate startup at different currents.

The data acquisition module has an adjustable gain that will allow measuring in the micro volts range. 1 channel was used with the shunt to measure the input current and the other 3 channels were used to measure Voltage in, VBAT and VSTOR. After the cycle was finished the data was saved as a CSV file and imported into Excel for processing and plotting.

After the startup sequences all measured test results are in the <u>Key System</u> <u>Specifications</u> section of this document.

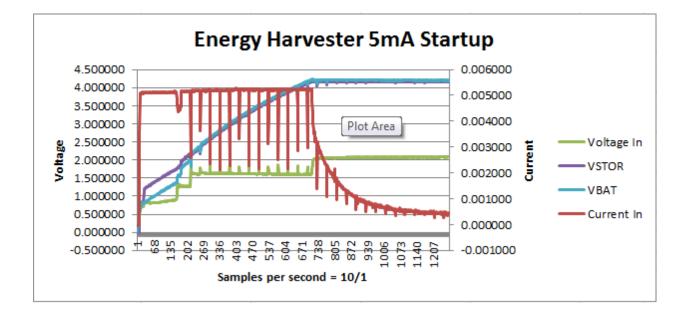

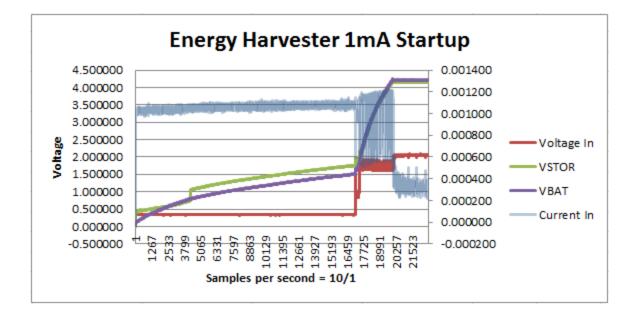

# 5 Test Data

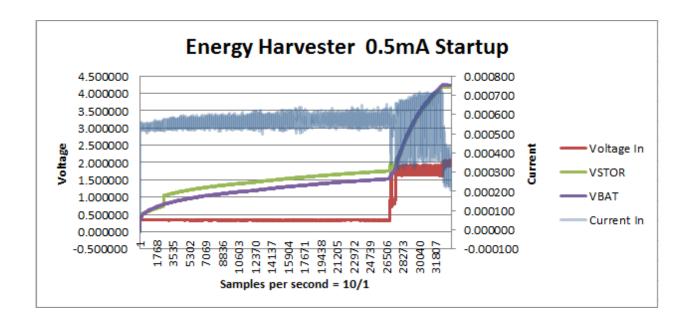

The following description explains the test plots that show the process of a cold start from zero volts to the 1.8V threshold where the bq25570 changes over to charge mode thru the voltage out max setting of 4.2Vdc. This is the complete cycle. When starting at zero volts the bq25570 will enter into a cold start mode. The cold start circuit's goal is to charge VSTOR higher than VSTOR\_CHGEN so that the main boost charger can operate. When a depleted storage element is initially attached to VBAT the harvester can provide a voltage > VIN(CS) and total power at least > PIN(CS), assuming no system load or leakage at VSTOR and VBAT, the cold start circuit can charge VSTOR above VSTOR\_CHGEN. Once the VSTOR voltage reaches the VSTOR CHGEN threshold, the IC goes thru the next three steps.

1. First it performs an initialization pulse on VRDIV to reset the feedback voltages,

Then disables the charger for 32 mS (typical) to allow the VIN\_DC voltage to rise to the harvester's open circuit voltage which will be used as the input voltage regulation reference voltage until the next MPPT sampling cycle.

Lastly performs its first feedback sampling using VRDIV, approximately 64 mS after the initialization pulse.

The energy harvester must supply sufficient power for the IC to exit cold start. Due to the body diode of the PFET connecting VSTOR and VBAT, the cold start circuit must charge both the capacitor on CSTOR up to the VSTOR\_CHGEN

and the storage element connected to VBAT up to VSTOR\_CHGEN less a diode drop. When a rechargeable battery with an open protector is attached, the initial charge time is typically short due to the minimum charge needed to close the battery's protector FETs. When large, discharged super capacitors with high DC leakage currents are attached, the initial charge time can be significant.

When the VSTOR voltage reaches VSTOR\_CHGEN, the main boost charger starts up. When the VSTOR voltage rises to the VBAT\_UV threshold, the PMOS switch between VSTOR and VBAT turns on. This provides additional loading on VSTOR and could result in the VSTOR voltage dropping below both the VBAT\_UV threshold and the VSTOR\_CHGEN voltage, especially if system loads on VSTOR or VBAT are active during this time. Therefore, it is not uncommon for the VSTOR voltage waveform to have incremental pulses (for example, stair steps) as the IC cycles between cold-start and main boost charger operation before eventually maintain VSTOR above VSTOR\_CHGEN.

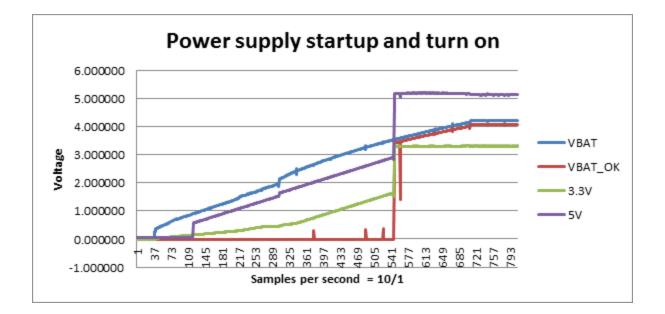

The last plot shows the proper turn on of the 3.3V and 5V supplies when the VBAT voltage reaches 3.5V. While discharging the VBAT\_OK line will turn off when the VBAT voltage reaches 3.4V. This will prevent further discharging of the batter and the loss of regulation in the 3.3V supply.

Note: To maximize the use of the energy stored you can run your micro controller at a lower voltage2.8V – 3.0V. You can reprogram the bq25570 output regulator to provide 2.8V with a turn on of 3.0V and a turn off of 2.9V.

# 5.1 5mA start up

# 5.2 1mA start up

# 5.3 0.5mA start up

# 5.4 3.3V and 5V start up Plot

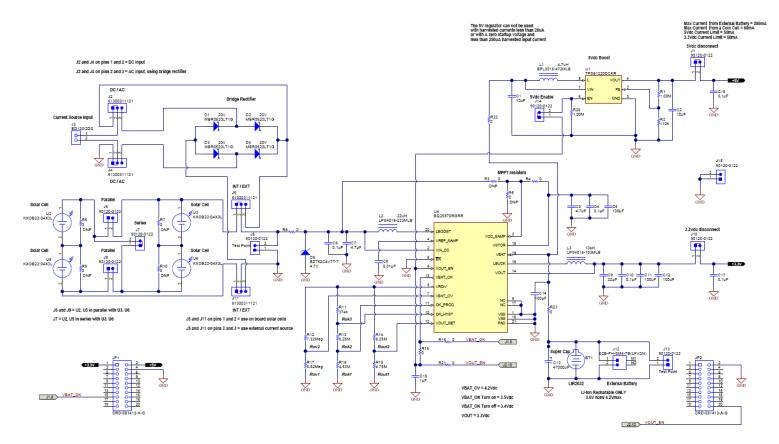

# 6 Design Files

# 6.1 Schematics

To download the Schematics for each board, see the design files at http://www.ti.com/tool/TIDA-00588

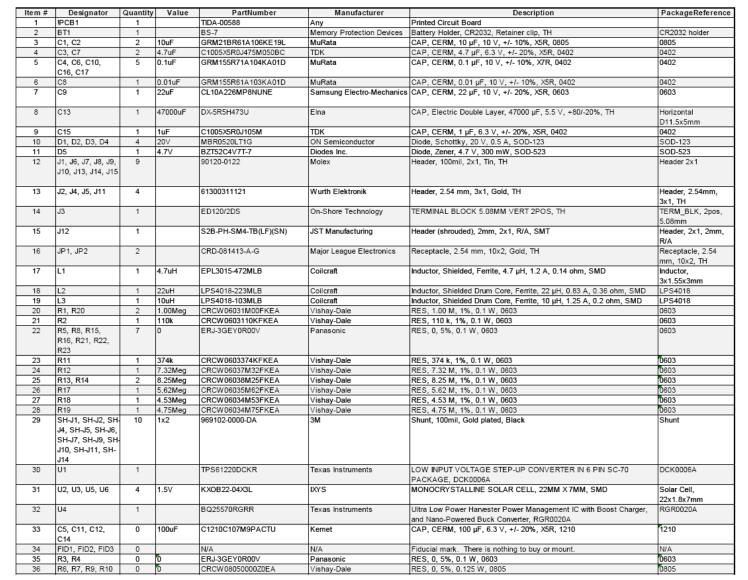

# 6.2 Bill of Materials

Variant: 001 Generated: 6/4/2015 8:28:44 AM TID #: TIDA-00588

### TIDA-00588 REV A Bill of Materials

Texas

INSTRUMENTS

# 6.3 PCB Layout Recommendations

### **Layout Guidelines**

As for all switching power supplies, the PCB layout is an important step in the design, especially at high peak currents and high switching frequencies. If the layout is not carefully done, the boost charger and buck converter could show stability problems as well as EMI problems. Therefore, use wide and short traces for the main current path and for the power ground paths. The input and output capacitors as well as the inductors should be placed as close as possible to the IC. For the boost charger, first priority are the output capacitors, including the 0.1uF bypass capacitor (CBYP), followed by CSTOR, which should be placed as close as possible between VSTOR, pin 19, and VSS, pin 1. Next, the input capacitor, CIN, should be placed as close as possible between VIN DC, pin 2, and VSS, pin 1. Last in priority is the boost charger's inductor, L1, which should be placed close to LBOOST, pin 20, and VIN\_DC, pin 2. For the buck converter, the output capacitor COUT should be placed as close as possible between VOUT, pin 14, and VSS, pin 15. The buck converter inductor (L2) should be placed as close as possible between the switching node LBUCK, pin 16, and VOUT, pin 14. It is best to use vias and bottom traces for connecting the inductors to their respective pins instead of the capacitors. To minimize noise pickup by the high impedance voltage setting nodes (VBAT OV, OK PROG, OK HYST, VOUT SET), the external resistors should be placed so that the traces connecting the midpoints of each divider to their respective pins are as short as possible. When laying out the non-power ground return paths (for example, from resistors and CREF), it is recommended to use short traces as well, separated from the power ground traces and connected to VSS pin 15. This avoids ground shift problems, which can occur due to superimposition of power ground current and control ground current. The PowerPAD should not be used as a power ground return path. The remaining pins are either NC pins that should be connected to the PowerPAD as shown below or digital signals with minimal layout restrictions. See the EVM user's guide for an example layout (SLUUAA7). In order to maximize efficiency at light load, the use of voltage level setting resistors > 1 M $\Omega$  is recommended. In addition, the sample and hold circuit output capacitor on VREF\_SAMP must hold the voltage for 16s. During board assembly, contaminants such as solder flux and even some board cleaning agents can leave residue that may form parasitic resistors across the physical resistors/capacitors and/or from one end of a resistor/capacitor to ground, especially in humid, fast airflow environments. This can result in the voltage regulation and threshold levels changing significantly from those expected per the installed components. Therefore, it is highly recommended that no ground planes be poured near the voltage setting resistors or the sample and hold capacitor. In addition, the boards must be carefully cleaned, possibly rotated at least once during cleaning, and then rinsed with de-ionized water until the ionic

contamination of that water is well above 50 MOhm. If this is not feasible, then it is recommended that the sum of the voltage setting resistors be reduced to at least 5X below the measured ionic contamination.

# **Thermal Considerations**

Implementation of integrated circuits in low-profile and fine-pitch surface-mount packages typically requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below.

- Improving the power-dissipation capability of the PCB design

- Improving the thermal coupling of the component to the PCB

- Introducing airflow in the system

For more details on how to use the thermal parameters in the dissipation ratings table please check the Thermal <u>Characteristics Application Note (SZZA017)</u> and the <u>IC Package Thermal Metrics Application Note (SPRA953)</u>.

# 6.4 Layout Prints

To download the Layout Prints for each board, see the design files at http://www.ti.com/tool/TIDA-00588

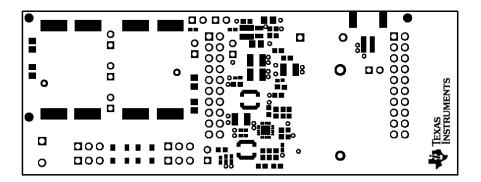

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588 | REV: A      | SUN REV: | Not In VersionControl |

|----------------------------------|---------------------|-------------|----------|-----------------------|

| LAYER NAME = Top Overlay         |                     |             |          |                       |

| PLOT NAME = Top Overlay          | GENERATED : 6/4/20  | 015 8:36:42 | AM       | TEXAS INSTRUMENTS     |

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588  | REV: A    | SUN REV: | Not In VersionControl |

|----------------------------------|----------------------|-----------|----------|-----------------------|

| LAYER NAME = Top Solder          |                      |           |          |                       |

| PLOT NAME = Top Solder Mask      | GENERATED : 6/4/2015 | 5 8:36:43 | AM       | TEXAS INSTRUMENTS     |

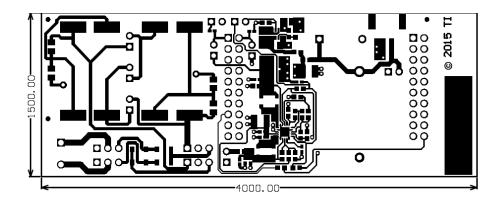

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588 | REV: A      | SUN REV: No | t In VersionControl |

|----------------------------------|---------------------|-------------|-------------|---------------------|

| LAYER NAME = Top Layer           |                     |             |             |                     |

| PLOT NAME = Top Layer            | GENERATED : 6/4/20  | 015 8:36:44 | AM          | TEXAS INSTRUMENTS   |

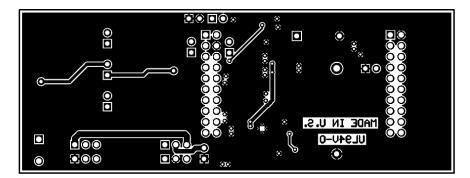

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588 | REV: A      | SUN REU: | Not In VersionControl |

|----------------------------------|---------------------|-------------|----------|-----------------------|

| LAYER NAME = Bottom Layer        |                     |             |          |                       |

| PLOT NAME = Bottom Layer         | GENERATED : 6/4/20  | 015 8:36:44 | AM       | TEXAS INSTRUMENTS     |

| o | 00000       |  |

|---|-------------|--|

|   | <b>0</b> 00 |  |

| 0 | 000         |  |

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588 | REV: A      | SUN REU | Not In VersionControl |

|----------------------------------|---------------------|-------------|---------|-----------------------|

| LAYER NAME = Bottom Solder       |                     |             |         |                       |

| PLOT NAME = Bottom Solder Mask   | GENERATED : 6/4/20  | 015 8:36:45 | AM      | TEXAS INSTRUMENTS     |

| ALL ARTWORK VIEWED FROM TOP SIDE | BOARD #: TIDA-00588 | REV: A      | SVN REV | : Not In VersionControl |

|----------------------------------|---------------------|-------------|---------|-------------------------|

| LAYER NAME = Bottom Overlay      |                     |             |         |                         |

| PLOT NAME = Bottom Overlay       | GENERATED : 6/4/20  | 015 8:36:46 | AM      | TEXAS INSTRUMENTS       |

### 6.5 Booster Pack Pins

The Booster Pack pin configuration is in the table below

| Energy H | arvester Ba | oster Pack 40Pi | n        |          |     |     |          |          |          |     |     |          |          |          |     |     |                |          |          |

|----------|-------------|-----------------|----------|----------|-----|-----|----------|----------|----------|-----|-----|----------|----------|----------|-----|-----|----------------|----------|----------|

| Pin      | J29         | Pin Name        | Function | IC Pin # | Pin | J29 | Pin Name | Function | IC Pin # | Pin | J30 | Pin Name | Function | IC Pin # | Pin | J30 | Pin Name       | Function | IC Pin # |

| 1        | A1          | 3.3V_Main       |          |          | 2   | C1  | 5V       |          |          | 1   | D20 |          |          |          | 2   | B20 | GND            |          |          |

| 3        | A2          | Analog In       |          |          | 4   | C2  | GND      |          |          | 3   | D19 |          |          |          | 4   | B19 | PWM/GPIO       |          |          |

| 5        | A3          | UART/RX         |          |          | 6   | C3  |          |          |          | 5   | D18 |          |          |          | 6   | B18 | SPI CS/GPIO    |          |          |

| 7        | A4          | UART/TX         |          |          | 8   | C4  |          |          |          | 7   | D17 |          |          |          | 8   | B17 | GPIO           |          |          |

| 9        | A5          | GPIO            |          |          | 10  | C5  |          |          |          | 9   | D16 |          |          |          | 10  | B16 | RESET          | RST      |          |

| 11       | A6          | Analog In       |          |          | 12  | C6  |          |          |          | 11  | D15 |          |          |          | 12  | B15 | SPI/MOSI       |          |          |

| 13       | A7          | SPI CLK         |          |          | 14  | C7  |          |          |          | 13  | D14 |          |          |          | 14  | B14 | SPI/MISO       |          |          |

| 15       | A8          | GPIO            | VBAT OK  |          | 16  | C8  |          |          |          | 15  | D13 |          |          |          | 16  | B13 | SPI/CS/DISPLAY |          |          |

| 17       | A9          | I2C/SCL         |          |          | 18  | C9  |          |          |          | 17  | D12 |          |          |          | 18  | B12 | SPI/CS/Other   |          |          |

| 19       | A10         | I2C/SDA         |          |          | 20  | C10 |          |          |          | 19  | D11 |          |          |          | 20  | B11 | GPIO           | VOUT EN  |          |

# 6.6 Altium Project

To download the Altium project files for each board, see the design files at http://www.ti.com/tool/TIDA-00588

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers ("Buyers") who are developing systems that incorporate TI semiconductor products (also referred to herein as "components"). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer's systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. **TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.** TI may make corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER'S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer's safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use.

Only those TI components that TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have **not** been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2015, Texas Instruments Incorporated