# TI Designs TIDA-00845: Reference Design of Two-Port Automotive USB 2.0 Hub with Short-to-Battery Protection

# Texas Instruments

# 0.1 Design Overview

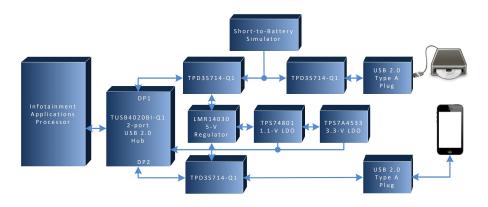

TIDA-00845 is comprised of the TUSB4020BI-Q1, a two-port USB 2.0 hub, with short-to-battery (STB), and short-circuit protection on both downstream ports provided by the TPD3S714-Q1. Downstream Port 1 (DP1) includes a STB tester for applying 18-V DC, using two TPD3S714-Q1s to protect both the hub and a peripheral, for easily demonstrating pre-test and post-test functionality. Downstream Port 2 (DP2) represents a best practice design.

# 0.2 Design Resources

| TIDA-00845  | Design Folder  |

|-------------|----------------|

| TPD3S714-Q1 | Product Folder |

| TUSB4020BI  | Product Folder |

| TPS7A4533   | Product Folder |

| TPS74801    | Product Folder |

| LMR14030    | Product Folder |

# 0.3 Design Features

- Fully Functional USB Hub With Built-In Short-to-Battery Test Simulator on Downstream Port 1

- Supports USB 2.0 High-Speed Data Rates

- Short-to-Battery Protection (up to 18 V) on V<sub>BUS\_CON</sub>, VD+, VD-

- Short-to-Ground Protection on V<sub>BUS\_CON</sub> for Downstream Port 2

- Over-Current Protection Current Limit: 550 mA

(min)

- IEC 61000-4-2 (Level 4) System Level ESD Protection at V<sub>BUS\_CON</sub>, VD+, VD-

# 0.4 Featured Applications

Remote USB ports where short to battery is a concern such as Media Connection modules and Head Units with remote USB ports

PowerPAD is a trademark of Texas Instruments.

1

#### Key System Specifications

2

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 Key System Specifications

# **Table 1. Key System Specifications**

| PARAMETER               | SPECIFICATION                                                           | DETAILS           |

|-------------------------|-------------------------------------------------------------------------|-------------------|

| STB Response Time       | TPD3S714-Q1 shuts off in 2 µs to protect the system from up to 18-V STB | See Section 3.1   |

| ESD Protection          | ±8-kV contact and ±15-kV air-gap per IEC 61000-4-2                      | See Section 3.1   |

| Built-in STB Tester     | Built-in demonstration of the STB protection on DP1                     | See Section 4.1.3 |

| Over-Current Protection | TPD3S714-Q1 limits current on $V_{\mbox{\scriptsize BUS}}$ to 550 mA    | See Section 3.1   |

# 2 Automotive USB 2.0 Hub with Short-to-Battery and Short-Circuit Protection

This automotive USB 2.0 hub has short-to-battery (STB), short-circuit, IEC 61000-4-2 ESD Level 4, and over-current protection. The USB 2.0 hub is the TUSB4020BI-Q1. The downstream ports (DP) are protected by the TPD3S714-Q1. DP1 includes a STB tester for demonstrating the protection from shorting the USB lines to 18-V DC. DP2 represents a best practice design for protecting a USB 2.0 hub with the TPD3S714-Q1. The upstream port (UP) has IEC 61000-4-2 Level 4 ESD protection provided by the TPD1E05U06.

# 2.1 TPD3S714-Q1

The TPD3S714-Q1 is a single-chip solution for automotive STB, short-circuit, IEC 61000-4-2 ESD, and over-current protection for USB 2.0 interfaces. The integrated data switches provide best-in-industry bandwidth for minimal signal degradation in USB 2.0 STB applications.

The STB protection protects against shorts up to 18 V, in both hot-plug and DC events. The over-voltage protection reacts very quickly, shutting off the switches and protecting the upstream transceiver from harmful voltage and current spikes. The integrated ESD protection provides system-level IEC 61000-4-2 Level 4 protection. The over-current protection automatically limits current to 550 mA, preventing the voltage from drooping below specification of the upstream V<sub>BUS</sub> rail.

# 2.2 TUSB4020BI-Q1

The TUSB4020BI-Q1 is a two-port USB 2.0 hub. It provides USB high-speed/full-speed connections on the UP, and provides high-speed, full-speed, or low-speed connections on the two DPs. When the UP is connected to an electrical environment that supports high-speed and full-speed/low-speed connections, high-speed and full-speed/low-speed USB connectivity is enabled on the DPs. When the UP is connected to an electrical environment that only supports full-speed/low-speed connections, high-speed connectivity is disabled on the DPs.

# 2.3 LMR14030-Q1

The LMR14030-Q1 is a 40-V, 3.5-A step down regulator with an integrated high-side MOSFET. Featuring a wide input range from 4 V to 40 V, the LMR14030-Q1 is suitable for various applications from industrial to automotive, for power conditioning from unregulated sources. The regulator's quiescent current is 40  $\mu$ A in sleep-mode, suitable for battery-powered systems. An ultra-low 1- $\mu$ A current, while in shutdown mode, can further prolong battery life. A wide adjustable switching-frequency range allows either efficiency or external component size to be optimized. Internal loop compensation means the user is free from the tedious task of loop-compensation design. This feature also minimizes the external components of the device. A precision-enable input allows simplification of regulator control and system-power sequencing. The device also has built-in protection features such as cycle-by-cycle current limit, thermal sensing and shutdown due to excessive power dissipation, and output over-voltage protection.

# 2.4 TPS7A4533

The TPS7A4533 device is a low-dropout (LDO) regulator optimized for a fast transient response. The device can supply 1.5 A of output current with a dropout voltage of 300 mV. Operating quiescent current is 1 mA, dropping to less than 1  $\mu$ A in shutdown mode. Quiescent current is well controlled; it does not rise in dropout as with many other regulators. In addition to fast transient response, the TPS7A45xx regulators have very low-output noise, making them ideal for sensitive RF supply applications.

The output voltage is 3.3 V. The TPS7A4533 regulator is stable with an output capacitance as low as 10  $\mu$ F. Small ceramic capacitors can be used without the necessary addition of ESR, as is common with other regulators. Internal-protection circuitry includes reverse-battery protection, current limiting, thermal limiting, and reverse-current protection.

3

#### Automotive USB 2.0 Hub with Short-to-Battery and Short-Circuit Protection

# 2.5 TPS74801-Q1

The TPS74801-Q1 LDO linear regulator provides an easy-to-use, robust, power-management solution for a wide variety of applications. The user-programmable soft-start minimizes stress on the input-power source by reducing the capacitive inrush current on start-up. The soft-start is monotonic and well-suited for powering many different types of processors and ASICs. The enable input and power-good output allow easy sequencing with external regulators. This complete flexibility permits the user to configure a solution that meets the sequencing requirements of FPGAs, DSPs, and other applications with special start-up requirements.

A precision reference and an error amplifier deliver 2% accuracy over load, line, temperature, and process. The device is stable with any type of capacitor greater than or equal to 2.2  $\mu$ F, and is fully specified from -40°C to 105°C for the DRC package, and from -40°C to 125°C for the RGW package. The TPS74801-Q1 is offered in a small 3-mm × 3-mm SON-10 package, yielding a highly compact, total solution size. It is also available in a 5 × 5 QFN-20 for compatibility with the TPS74401.

# 2.6 TPD1E05U06

4

The TPD1E05U06 is a unidirectional transient voltage suppressor (TVS) based ESD protection diode with ultra-low capacitance. The TPD1E05U06 can dissipate ESD strikes above the maximum level specified by the IEC 61000-4-2 Level 4 international standard. The TPD1E05U06's ultra-low loading capacitance makes it ideal for protecting any high-speed signal pins.

# 3 Block Diagram

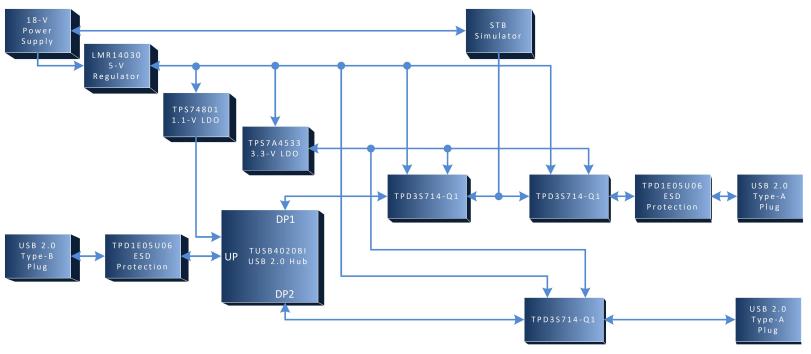

This automotive USB 2.0 hub with STB protection has two DPs. DP1 has two TPD3S714-Q1s arranged so that when the STB simulator is engaged, applying 18 V to either  $V_{BUS}$  or the data lines, both the upstream hub and downstream peripheral are protected from the over-voltage. To accomplish this, the TPD3S714-Q1 protecting the peripheral attached to the USB 2.0 Type-A plug has the connector-side pins facing the hub, and the system-side data line pins facing the connector. The system-side data pins are not rated for IEC 61000-4-2 ESD, but for AEC-Q100 Classification H3 HBM of ±4 kV. To maintain IEC 61000-4-2 Level 4 ESD protection on the DP1, additional ESD protection has been added in the form of the TPD1E05U06, an IEC 61000-4-2 Level 4 rated ESD protection device. Despite the additional TPD3S714-Q1 and TPD1E05U06 on the DP1, the device is still capable of high-speed communication at 480 Mbps.

Figure 1. TIDA-00845 Functional Block Diagram

Block Diagram

www.ti.com

A single TPD3S714-Q1 protects the DP2, providing STB, short-to-ground, ESD, and over-current protection for the TUSB4020BI-Q1 USB 2.0 two-port hub. DP2 represents the reference design for a TPD3S714-Q1 protecting a USB 2.0 hub.

An external 18-V DC power supply provides power to the STB circuit and USB 2.0 hub circuitry. A stepdown (Buck) regulator, LMR14030-Q1, steps down the 18 V to provide a 5-V rail for the two LDOs and  $V_{BUS}$  for the two DPs. The LDO TPS7A4533 provides the 3.3-V rail, and the LDO TPS74801-Q1 provides the 1.1-V rail.

# 3.1 TPD3S714-Q1

- AEC-Q100 Qualified (Grade 1)

- 40°C to 125°C Operating Temperature Range

- STB Protection, up to 18 V, on V<sub>BUS\_CON</sub>, VD+, VD-

- Short-to-Ground Protection on V<sub>BUS\_CON</sub>

- Short-to-Bus Protection on VD+, VD-

- ESD Protection on V<sub>BUS\_CON</sub>, VD+, VD-

- ±8 kV Contact Discharge (IEC 61000-4-2)

- ±15 kV Air-Gap Discharge (IEC 61000-4-2)

- Low R<sub>ON</sub> nFET V<sub>BUS</sub> Switch

- High-Speed Data Switches

- Hiccup Current Limit

- 550 mA Over-Current Limit (minimum)

- Integrated Input Enable for V<sub>BUS</sub> and Data Lines

- Fault Output Signal

- Thermal Shutdown Feature

- 16-Pin DBQ Package (3.9 mm × 4.94 mm)

- STB Response Time of 2  $\mu s$  (Typ) for  $V_{\scriptscriptstyle BUS},$  and 200 ns for the Data Path

# 3.2 TUSB4020BI-Q1

- Two-Port USB 2.0 Hub

- USB 2.0 Hub Features:

- Multi-Transaction Translator (MTT) Hub: Two Transaction Translators

- Four Asynchronous Endpoint Buffers per Transaction Translator

- Per Port or Ganged Power Switching, and Over-Current Notification Inputs

- OTP ROM, Serial EEPROM, or I<sup>2</sup>C or SMBus Slave Interface for Custom Configurations:

- VID and PID

- Port Customization

- Manufacturer and Product Strings (not by OTP ROM)

- Serial Number (not by OTP ROM)

- Application Feature Selection Using Terminal Selection, EEPROM/ or I<sup>2</sup>C or SMBus Slave Interface

- Provides 128-Bit Universally Unique Identifier (UUID)

- Supports On-Board and In-System OTP or EEPROM Programming Through the USB 2.0 UP

- Single Clock Input, 24-MHz Crystal or Oscillator

- No Special Driver Requirements; Works Seamlessly on any Operating System With USB Stack Support

- 48-Pin HTQFP Package (PHP)

Block Diagram

#### www.ti.com

# 3.3 LMR14030-Q1

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: -40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H1C

- Device CDM ESD Classification Level C4A

- 4-V to 40-V Input Range

- 3.5-A Continuous Output Current

- Ultra-low 40-µA Operating Quiescent Current

- 90-mΩ High-side MOSFET

- Minimum Switch-On Time: 75 ns

- Adjustable Switching Frequency from 200 kHz to 2.5 MHz

- Frequency Synchronization to the External Clock

- Spread-Spectrum Option for Reduced EMI

- Internal Compensation for Ease of Use

- High-Duty Cycle Operation Supported

- Precision-Enable Input

- 1-µA Shutdown Current

- External Soft-Start

- Thermal, Over-voltage, and Short Protection

- 8-Pin HSOIC with PowerPAD<sup>™</sup> Package

# 3.4 TPS7A4533

- Optimized for Fast Transient Response

- Output Current: 1.5 A

- High Output Voltage Accuracy: 1% at 25°C

- Dropout Voltage: 300 mV

- Low Noise: 35  $\mu$ V<sub>RMS</sub> (10 Hz to 100 kHz)

- High Ripple Rejection: 68 dB at 1 kHz

- 1-mA Quiescent Current

- Controlled Quiescent Current in Dropout

- Less Than 1-µA Quiescent Current in Shutdown

- Stable With 10-µF Ceramic Output Capacitor

- Reverse-Battery Protection

- Reverse-Current Protection

# 3.5 TPS74801-Q1

- Qualified for Automotive Applications

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 1: -40°C to 125°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level H2

- Device HBM ESD Classification Level C4B

- V<sub>OUT</sub> Range: 0.8 V to 3.6 V

- Ultra-low V<sub>IN</sub> Range: 0.8 V to 5.5 V

- V<sub>BIAS</sub> Range 2.7 V to 5.5 V

- Low Dropout: 60-mV typ at 1.5 A, V<sub>BIAS</sub> = 5 V

- 2% Accuracy Over Line, Load, and Temperature

Block Diagram

8

- Programmable Soft-Start Provides Linear-Voltage Startup

- V<sub>BIAS</sub> Permits Low V<sub>IN</sub> Operation with Good Transient Response

- Stable with Any Output Capacitor ≥ 2.2 µF

- Available in Small 3-mm × 3-mm × 1-mm SON-10, and 5 × 5 QFN-20 Packages ٠

#### 3.6 **TPD1E05U06**

- IEC 61000-4-2 Level 4 ESD Protection

- ±12-kV Contact Discharge

- ±15-kV Air-Gap Discharge

- IEC 61000-4-4 EFT Protection •

- 80 A (5/50 ns)

- IEC 61000-4-5 Surge Protection

- 2.5 A (8/20 µs)

- IO Capacitance of 0.42 pF (Typ) ٠

- DC Breakdown Voltage 6.5 V (minimum) ٠

- Ultra-low Leakage Current of 10 nA (maximum) and 0.1 nA (typ) ٠

- Low ESD Clamping Voltage ٠

- Industrial Temperature Range: -40°C to +125°C ٠

- Easy Routing Package •

# 4 System Design Theory

The TIDA-00845 two-port automotive USB 2.0 hub with STB and short-circuit protection highlights the TPD3S714-Q1, providing USB 2.0 DP protection against STB, short-circuit, IEC 61000-4-2 ESD Level 4, and over-current. To facilitate easy demonstration of the protection by the TPD3S714-Q1, a built-in STB tester can be used for live demonstrations of the STB on the DP1. By pressing either the S1, S2, or S3 switch, all together or individually, while the hub is attached to a personal computer with a peripheral (such as a webcam) and operating on the DP1, the functionality maintained after 18 V is applied to  $V_{BUS}$ , and-or the data lines demonstrate the capabilities of the TPD3S714-Q1. Equipment, such as an oscilloscope, can be optionally attached to record the STB event.

# 4.1 Downstream Port 1 (DP1)

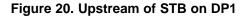

# 4.1.1 TPD3S714-Q1 Upstream from Short-To-Battery Test

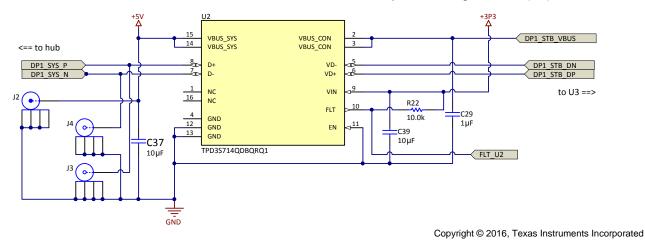

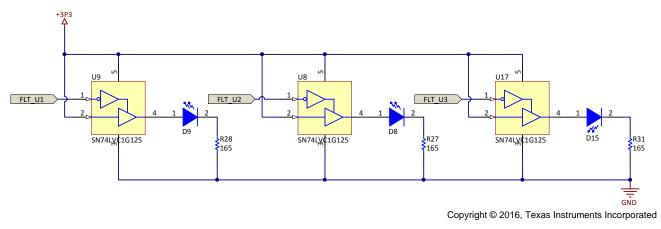

Figure 2 shows the TPD3S714-Q1 (U2) connected to the TUSB4020BI-Q1, following the data sheet guidelines of the TPD3S714-Q1. Additionally, test points for measuring system-side voltages on  $V_{BUS}$ , and the data lines during STB tests are provided by the SMB (J2) and high-impedance probe (J3 and J4) connectors. The SN74LVC1G125 (U8, see Figure 27) single-bus buffer gate compares the FLT pin logic of the TPD3S714-Q1 to the 3.3-V rail, and indicates a fault by illuminating the LED (D8).

Figure 2. TPD3S714-Q1 Protecting Hub from STB on DP1

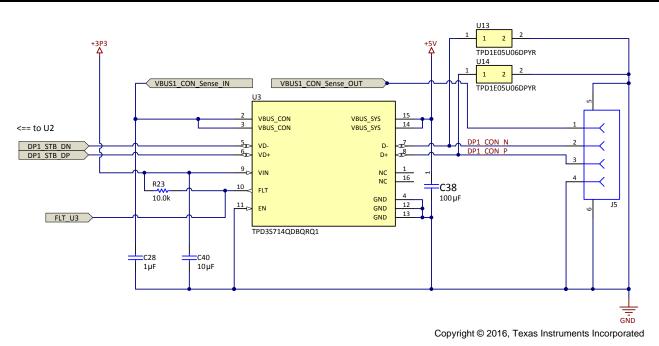

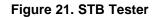

# 4.1.2 TPD3S714-Q1 Downstream from Short-to-Battery Test

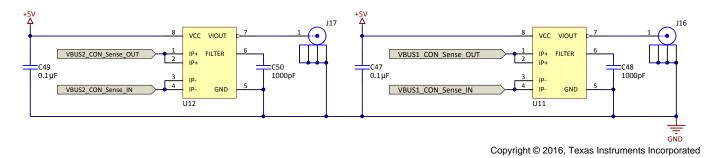

Figure 3 shows downstream from U2 (previously discussed), another TPD3S714-Q1 (U3) for protecting any peripheral attached to the DP1 USB port during the STB demonstrations. Because, for demonstration purposes, the system-side data lines of U3 connect to the USB port, the TPD1E05U06 (U13 and U14) adds additional ESD protection to the data lines. The  $V_{BUS}$  line follows the data sheet in that the VBUS\_CON pin connects to the USB port and the VBUS\_SYS pin connects to the 5-V rail supplied by the LMR14030 (U5 not shown here, see Section 4.4). The  $V_{BUS}$  line passes through a hall-effect current sensor (U11 not shown here, see Figure 26) for easily observing the current during tests. The SN74LVC1G125 (U17, see Figure 27) single-bus buffer gate compares the FLT pin logic of the TPD3S714-Q1 to the 3.3-V rail, and indicates a fault by illuminating the LED (D15).

9

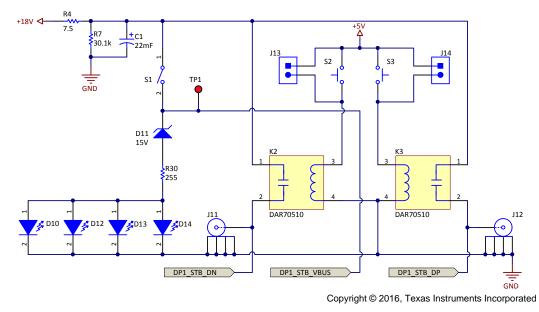

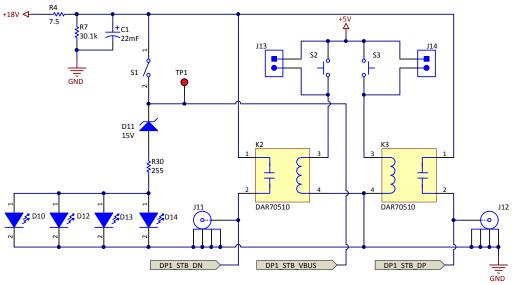

# 4.1.3 Short-To-Battery Tester

Figure 4 shows a built-in STB tester implemented to facilitate on-board STB tests. Using a high-current switch (S1), 18 V can be applied to the  $V_{BUS}$  rail protected by the TPD3S714-Q1 (U2). The 18 V is stored in a large electrolytic, low-ESR capacitor (C1). Users can observe the over-voltage by connecting a high-impedance probe of an oscilloscope to the test-point (TP1). Four LEDs (D10, D12, D13, and D14) indicate when S1 completes the circuit, and applies 18 V to  $V_{BUS}$ .

Using switch S2 or S3, either of the high-voltage low-capacitance relays (K2 and K3) can apply, respectively, 18-V STB to either DP1- or DP1+. Two-pin headers (J13 and J14) are placed parallel with S2 and S3 for attaching external switches to operate K2 or K3, respectively.

Figure 4. STB Test Circuit

By design, any peripheral attached to the DP1 USB port is also protected during STB tests. This feature makes it simple to install the USB 2.0 hub to a computer, and demonstrate the USB 2.0 hub and peripheral functionality before and after a STB demonstration.

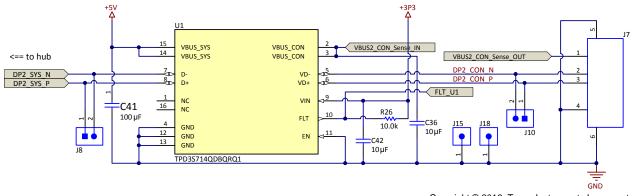

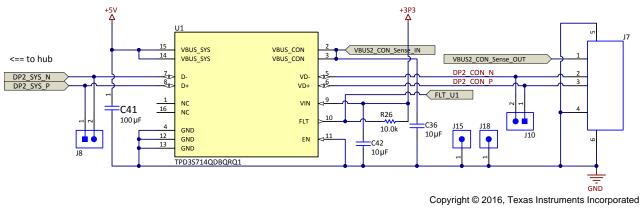

# 4.2 Downstream Port 2

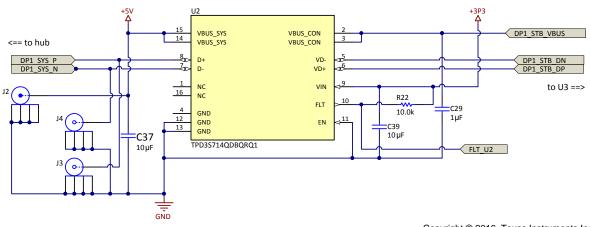

Figure 5 shows the TPD3S714-Q1 (U4) connected to the TUSB4020BI-Q1, following the data sheet guidelines of the TPD3S714-Q1. Additionally, test points (J8 and J10) for measuring ESD clamping voltages are included with the ground pins J15 and J18.

The SN74LVC1G125 (U9, see Figure 27) single-bus buffer gate compares the FLT pin logic of the TPD3S714-Q1 to the 3.3-V rail, and indicates a fault by illuminating the LED (D9).

# Figure 5. TPD3S714-Q1 in DP2

# 4.3 TUSB4020BI-Q1

The TUSB4020BI-Q1 is a two port USB 2.0-compliant hub device. It provides high-speed and full-speed connections on the UP. The TUSB4020BI-Q1 also supports high, full, or low-speed connections on the DPs. When the UP connects to an environment that supports only full and low-speed connections, high-speed is disabled on the DPs. The hub's individual port power switching is not used due to the TPD3S714-Q1 over-current limiter, providing the two-port protection scheme. The USB 2.0 hub is configured with the de-assertion of RESET.

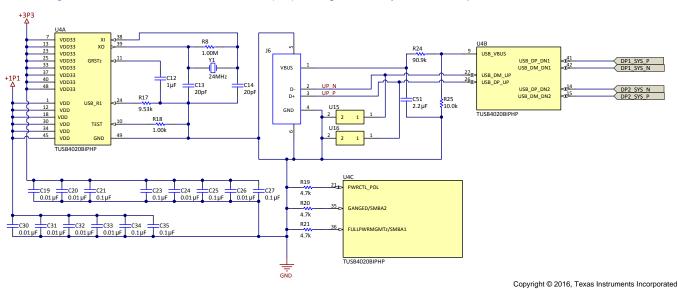

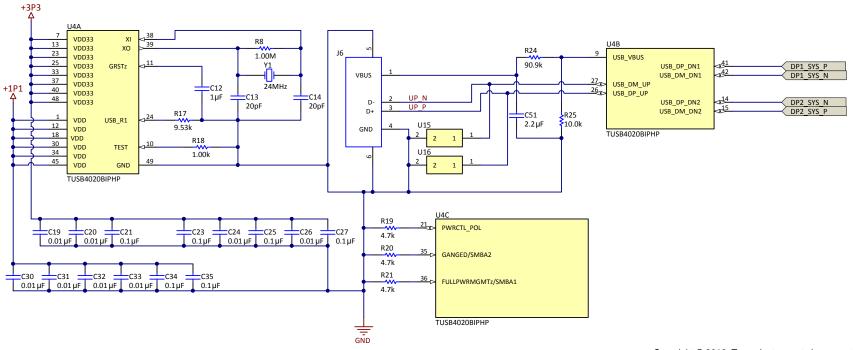

Figure 6, shows the TUSB4020BI-Q1 (U4) configured. Only connected pins are shown.

Figure 6. TUSB4020BI-Q1 Schematic

System Design Theory

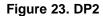

# 4.4 LMR14030-Q1

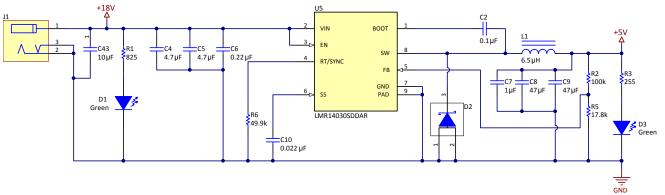

Figure 7 shows the LMR14030-Q1 (U5) configured for a 5-V output capable of 3.5 A. An 18-V external AC-DC converter supplies the input power. The 5-V output rail supplies the 3.3-V LDO TPS7A4533 and 1.1-V LDO TPS74801. An LED diode (D3) indicates when the power rail becomes active.

Copyright © 2016, Texas Instruments Incorporated

Figure 7. LMR14030 Step Down (Buck) Regulator Schematic

### 4.4.1 Output Voltage Selection

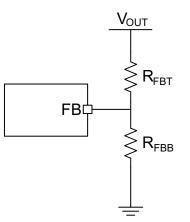

The internal voltage reference produces a precise 0.75-V (typical) voltage reference over the operating temperature range. The output voltage is set by a resistor divider from the output voltage to the FB pin. It is recommended to use divider resistors with 1% tolerance or better, and a temperature coefficient of 100 ppm or less. Select the high-side resistor  $R_{FBT}$  (R2) for the desired divider current, and use Equation 1 to calculate low-side  $R_{FBB}$  (R5). Larger value divider resistors are good for efficiency at light load. However, if the values are too high the regulator is more susceptible to noise, and voltage errors from the FB input current may become noticeable.  $R_{FBB}$  in the range from 10 k $\Omega$  to 100 k $\Omega$  are recommended for most applications.

Figure 8. Output Voltage Setting

$$R_{FBB} = 0.75 / V_{OUT} - .75 \times R_{FBT}$$

Choosing  $R_{FBT}$  = 100 k $\Omega$  and  $V_{OUT}$  = 5 V, gets  $R_{FBB}$  = 17,647 $\Omega$ . Choose a standard value of 17.8 k $\Omega$ .

# 4.4.2 Switching Frequency

For a desired frequency, use Equation 2 to calculate the required value for  $R_T$  (R6).  $R_T(K\Omega) = 42904 \times f_{sw}$ (kHZ)<sup>-1.088</sup>

This design uses a switching frequency of 500 kHz. For 500 kHz, the calculated  $R_{\tau}$  is 49.66 k $\Omega$ , and a standard value of 49.9 k $\Omega$  can be used to set the switching frequency at 500 kHz.

(1)

(2)

(5)

(6)

## 4.4.3 Output Inductor Selection

The most critical parameters for the inductor are the inductance, saturation current, and the RMS current. The inductance is based on the desired peak-to-peak ripple current,  $\Delta i_L$ . Because the ripple current increases with the input voltage, the maximum input voltage is always used to calculate the minimum inductance,  $L_{MIN}$ . Use Equation 4 to calculate the minimum value of the output inductor.  $K_{IND}$  is a coefficient that represents the amount of inductor ripple current relative to the maximum output current. A reasonable value of  $K_{IND}$  should be 20%-40%. During an instantaneous short or over-current operation event, the RMS and peak inductor current can be high. The inductor current rating should be higher than the current limit.

$$\Delta i_{L} = V_{OUT} \times (V_{IN\_MAX} - V_{OUT}) / V_{IN\_MAX} \times L \times f_{SW}$$

$$L_{MIN} = V_{IN\_MAX} - V_{OUT} / I_{OUT} \times K_{IND} \times V_{OUT} / V_{IN\_MAX} \times f_{SW}$$

(3)

(4)

In general, it is preferable to choose lower inductance when switching power supplies, because it usually corresponds to a faster transient response, smaller DCR, and reduced size for more compact designs. However, too low of an inductance can generate too large of an inductor current ripple, to where overcurrent protection at the full load could be falsely triggered. Lower inductance also generates more conduction loss since the RMS current is slightly higher. Larger inductor current ripple also implies larger output voltage ripple with the same output capacitors. With peak current mode control, it is not recommended to have too small of an inductor current ripple. A larger peak current ripple improves the comparator signal-to-noise ratio. For this design example, choose  $K_{IND} = 0.4$ , the minimum inductor value is calculated to be 6.12 µH, and the nearest standard value above that is chosen 6.5 µH. Use a standard 6.5-µH ferrite inductor (L1) with a capability of 5-A RMS current and 7-A saturation current.

#### 4.4.4 Output Capacitor Selection

The output capacitor(s),  $C_{OUT}$  (C7, C8, C9), should be carefully chosen since it directly affects the steadystate output voltage ripple, loop stability, and the voltage overshoot and undershoot during load current transients. The output ripple is essentially composed of two parts. One part is caused by the inductor current ripple going through the Equivalent Series Resistance (ESR) of the output capacitors:

$$\Delta V_{OUT\_ESR} = \Delta i_L \times ESR = K_{IND} \times I_{OUT} \times ESR$$

The other part is caused by the inductor current ripple charging and discharging the output capacitors:

$$V_{OUT C} = \Delta i_L / 8 \times f_{SW} \times C_{OUT} = K_{IND} \times I_{OUT} / 8 \times f_{SW} \times C_{OUT}$$

The two components in the voltage ripple are not in phase, so the actual peak-to-peak ripple is smaller than the sum of the two peaks. Output capacitance is usually limited by transient performance specifications if the system requires tight voltage regulation with the presence of large current steps and fast slew rate. When a fast large load increase happens, output capacitors provide the required charge before the inductor current can slew up to the appropriate level. The regulator's control loop usually needs three or more clock cycles to respond to the output voltage droop. The output capacitance must be large enough to supply the current difference for the three clock cycles to maintain the output voltage within the specified range.

Equation 7 shows the minimum output capacitance needed for a specified output undershoot. When a sudden large load decrease happens, the output capacitors absorb energy stored in the inductor. The catch diode can't sink current so the energy stored in the inductor results in an output voltage overshoot. Equation 8 calculates the minimum capacitance required to keep the voltage overshoot within a specified range.

$$C_{OUT} > 3 \times (I_{OH} - I_{OL}) / (f_{SW} \times V_{US}$$

$$C_{OUT} > I_{OH}^2 - I_{OL}^2 / (V_{OUT} - V_{OS})^2 - V_{-OUT}^2$$

(8)

where:

- $K_{IND}$  = ripple ratio of the inductor ripple current ( $\Delta iL$  / IOUT)

- I<sub>OL</sub> = low-level output current during load transient

- I<sub>OH</sub> = high-level output current during load transient

- V<sub>US</sub> = target output-voltage undershoot

- V<sub>os</sub> = target output-voltage overshoot

#### System Design Theory

For this design example, the target output ripple is 50 mV. Presuppose  $\Delta V_{OUT\_ESR} = \Delta V_{OUT\_C} = 50$ -mV, and chose  $K_{IND} = 0.4$ . Equation 5 yields ESR no larger than 35.7 m $\Omega$  and Equation 6 yields  $C_{OUT}$  no smaller than 7  $\mu$ F. For the target over and undershoot range of this design,  $V_{US} = V_{OS} = 5\% \times V_{OUT} = 250$  mV. The  $C_{OUT}$  can be calculated to be no smaller than 75.6  $\mu$ F and 30.8  $\mu$ F by Equation 7 and Equation 8 respectively. In summary, the most stringent criteria for the output capacitor is 75.6  $\mu$ F. Two 47- $\mu$ F, 16-V, X7R ceramic capacitors (C8 and C9) with 5-m $\Omega$  ESR are used in parallel. A 1- $\mu$ F, X7R, capacitor (C7) is also used for high-frequency filtering, placed as close as possible to the device pins.

### 4.4.5 Schottky Diode Selection

The preferred breakdown voltage rating of the diode is 25% higher than the maximum input voltage. The current rating for the diode should be equal to the maximum output current for the best reliability in most applications. In cases where the input voltage is much greater than the output voltage, the average diode current is lower. In this case it is possible to use a diode with a lower average current rating, approximately  $(1-D) \times I_{OUT}$ , however the peak current rating should be higher than the maximum load current. A 4-A to 5-A rated diode is a good starting point. For this design example, a 5-A 60-V Schottky diode (D2) was chosen.

#### 4.4.6 Input Capacitor Selection

The LMR14030-Q1 device requires high-frequency input decoupling capacitor(s) and a bulk-input capacitor, depending on the application. The typical recommended value for the high-frequency decoupling capacitor is from 4.7  $\mu$ F to 10  $\mu$ F. A high-quality ceramic capacitor, type X5R or X7R, with a sufficient voltage rating is recommended. To compensate the derating of ceramic capacitors, a voltage rating of twice the maximum input voltage is recommended. Additionally, some bulk capacitance can be required, especially if the LMR14030-Q1 circuit is not located within approximately 5-cm from the input voltage source. This capacitor is used to provide damping to the voltage spike due to the lead inductance of the cable or the trace. For this design, two 4.7- $\mu$ F, X7R ceramic capacitors, rated for 50 V, are used. A 0.22- $\mu$ F, X7R ceramic capacitor (C6), rated for 50 V, is also used for high-frequency filtering, placed as close as possible to the device pins.

### 4.4.7 Bootstrap Capacitor Selection

Every LMR14030-Q1 design requires a bootstrap capacitor, CBOOT (C2). The recommended capacitor is 0.1  $\mu$ F and rated 16 V or higher, the values used in this design. The bootstrap capacitor is located between the SW pin and the BOOT pin. The bootstrap capacitor must be a high-quality ceramic type, with an X7R or X5R grade dielectric for temperature stability. This design uses X7R.

### 4.5 TPS7A4533

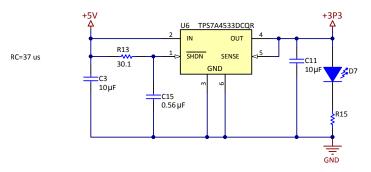

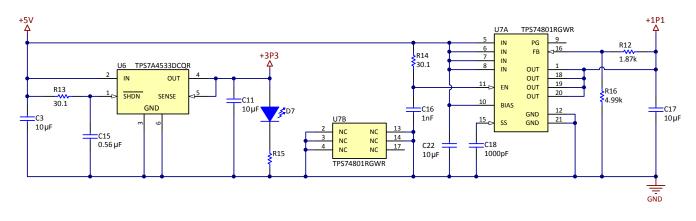

Figure 9 shows the TPS7A4533 (U6) configured in this design. The LMR14030-Q1 supplies the  $V_{IN}$ .  $V_{OUT}$  is the VDD33 supply rail for the USB 2.0 hub TUSB4020BI-Q1 and the TPD3S714-Q1. An LED diode (D7) indicates when the power rail becomes active.

Copyright © 2016, Texas Instruments Incorporated

### Figure 9. TPS7A4533 3.3-V Low Dropout Regulator Schematic

# 4.5.1 Start-up Timing

The USB 2.0 hub TUSB4020BI-Q1 requires that the VDD33 supply (TPS704533 in this design) be stable before at least 10-µs before the VDD supply (TPS74801-Q1 in this design) powers on. To accomplish this, an RC circuit (R13 and C15) adds a 37-µs startup delay to the SHDN pin with the VDD33 supply, and a 66-µs startup delay for the VDD supply. The difference of 29 µs meets this requirement.

### 4.5.2 Output Capacitor Selection

Extra consideration must be given for the use of ceramic capacitors. Ceramic capacitors are manufactured with a variety of dielectrics, each with different behaviors over temperature and applied voltage. The most common dielectrics used are Z5U, Y5V, X5R, and X7R. The Z5U and Y5V dielectrics are good for providing high capacitances in a small package, but exhibit strong voltage and temperature coefficients. When used with a 5-V regulator, a 10- $\mu$ F Y5V capacitor can exhibit an effective value as low as 1  $\mu$ F to 2  $\mu$ F over the operating temperature range. The X5R and X7R dielectrics result in more stable characteristics and are more suitable for use as the output capacitor. The X7R type has better stability across temperature, while the X5R is less expensive and is available in higher values. This design uses a 10- $\mu$ F capacitor (C11) with an X5R rating.

# 4.6 TPS78401-Q1

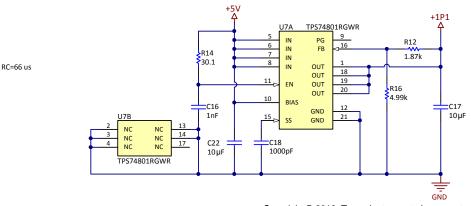

Figure 10 shows the TPS78401-Q1 (U7) configured in this design. The LMR14030-Q1 supplies the IN voltage-supply pin. The OUT pin is the VDD supply rail for the USB 2.0 hub TUSB4020BI-Q1.

Copyright © 2016, Texas Instruments Incorporated

Figure 10. TPS78401-Q1 1.1-V Low Dropout Regulator Schematic

### 4.6.1 Output Voltage Selection

For an output voltage of 1.1 V, the resistor divider (R12 and R16) on the FB pin was set by Equation 9 where R16 should be  $\leq$  4.99 k $\Omega$ . A value for R16 of 4.99 k $\Omega$  was chosen to minimize the FB pin input current. This yields a value of 1.87 k $\Omega$  for R12.

$$V_{OUT} = 0.8 \times (1 + R_{12} / R_{16})$$

(9)

# 4.6.2 Input, Output, and Bias Capacitor Requirements

The device is designed to be stable for all available types and values of output capacitors  $\ge 2.2 \ \mu\text{F}$ . The device is also stable with multiple capacitors in parallel, which can be of any type or value. The capacitance required on the IN and BIAS pins strongly depends on the input supply source impedance. To counteract any inductance in the input, the minimum recommended capacitor for  $V_{\text{IN}}$  and  $V_{\text{BIAS}}$  is 1  $\mu$ F. If  $V_{\text{IN}}$  and  $V_{\text{BIAS}}$  are connected to the same supply, the recommended minimum capacitor for  $V_{\text{BIAS}}$  is 4.7  $\mu$ F. Good quality, low ESR capacitors should be used on the input, ceramic X5R and X7R capacitors are preferred. These capacitors should be placed as close to the pins as possible for optimum performance. For this design,  $C_{\text{OUT}}$  (C17) is a 10- $\mu$ F capacitor with an X5R rating. Since the IN and BIAS pins are connected to the same supply,  $C_{\text{IN}}$  (C22) is a 22- $\mu$ F capacitor with an X5R rating.

#### System Design Theory

www.ti.com

## 4.6.3 Programmable Soft-Start

The TPS74801-Q1 features a programmable, monotonic, voltage-controlled soft-start that is set with an external capacitor (CSS or C18). This feature is important for many applications because it eliminates power-up initialization problems when powering FPGAs, DSPs, or other processors. The controlled voltage ramp of the output also reduces peak inrush current during start-up, minimizing start-up transient events to the input power bus. To achieve a linear and monotonic soft-start, the TPS74801-Q1 error amplifier tracks the voltage ramp of the external soft-start capacitor until the voltage exceeds the internal reference. The soft-start ramp time depends on the soft-start charging current (ISS), soft-start capacitance (CSS), and the internal reference voltage (VREF), and can be calculated using Equation 10:

$t_{ss} = (V_{REF} \times C_{ss}) / I_{ss}$

(10)

- where:

- V<sub>REF</sub> = 0.8 V

- I<sub>ss</sub> = 440 nA

This design uses a  $C_{ss}$  (C18) of 1000 pF for  $t_{ss}$  = 1.82 ms. This measure, along with the 66-µs RC (R14 and C16) circuit on the EN pin, ensures the VDD stabilizes after VDD33 for the TUSB4020BI-Q1 timing requirement.

# 5 Test Data

### 5.1 Short-to-Battery

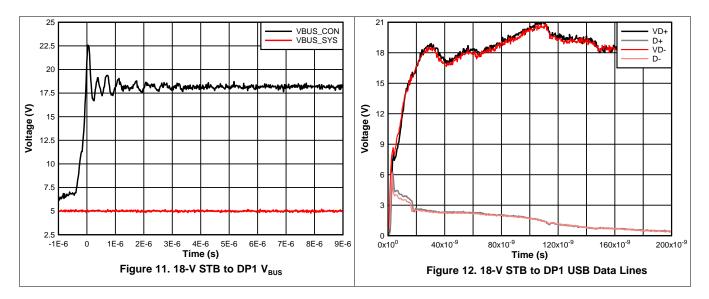

Once a voltage above the  $V_{OVP}$  threshold is detected by the device, the TPD3S714-Q1 shuts off all FETs and asserts a fault on the FLT pin. When the excessive voltage is removed, the device automatically reenables and the FLT de-asserts.

# 5.2 IEC 61000-4-2 ±8-kV Clamping Waveforms on USB Data Lines

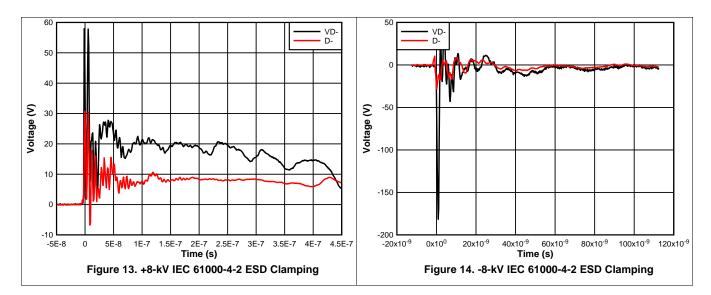

The protected pins (VBUS\_CON, VD+, VD-) are tested to pass the IEC 61000-4-2 ESD standard up to Level 4 ESD protection. Additionally, these pins are tested against ISO 10605 with the 330-pF and 330- $\Omega$  equivalent network. This guarantees passing of at least ±8-kV contact discharge, and ±15-kV air-gap discharge according to both standards.

# 5.3 Short to Ground

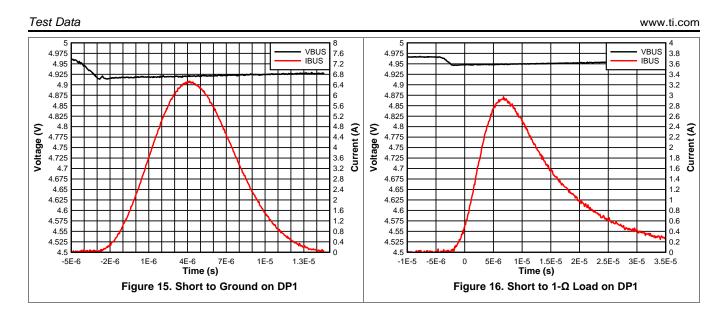

When a voltage on VBUS\_CON is detected as too low (below the V<sub>SHRT</sub> threshold) after the device is enabled, the device enters a short-circuit protection mode and asserts the  $\overline{FLT}$ . The device sources the I<sub>SHRT</sub> current until it detects the voltage rising above the V<sub>SHRT</sub> threshold, then it resumes standard operating mode and de-asserts  $\overline{FLT}$ .

17

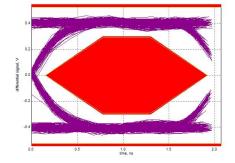

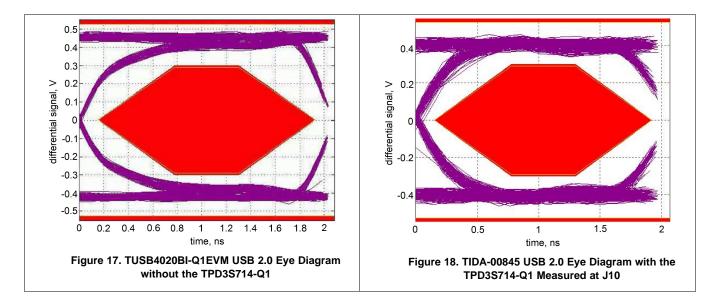

5.4 USB 2.0 High-Speed Downstream Near-End Eye Diagram

# 6 Design Files

## 6.1 Schematics

To download the schematics for each board, see the design files at: http://www.ti.com/tool/TIDA-00845.

Figure 19. USB 2.0 Hub

Copyright © 2016, Texas Instruments Incorporated

Figure 25. VDD33 and VDD Power Rails

# 6.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-00845.

Table 2. BOM

| Designator | Quantity | Value    | Description                             | PackageReference | PartNumber   | Manufacturer   |

|------------|----------|----------|-----------------------------------------|------------------|--------------|----------------|

| !PCB1      | 1        |          | Printed Circuit Board                   |                  | ISE4002      | Any            |

| !Enclosure | 1        |          | Electrical Enclosure Box                |                  | PN-1327-C    | Bud Industries |

| C1         | 1        | 22000 uF | CAP, AL, 10000 µF, 6.3<br>V, ± 20%, SMD | MNO              | B41231B5229M | EPCOS (TDK)    |

Design Files

# Table 2. BOM (continued)

|                                           |   |          | •                                                      | •            |                          |                     |

|-------------------------------------------|---|----------|--------------------------------------------------------|--------------|--------------------------|---------------------|

| C2                                        | 1 | 0.1 uF   | CAP, CERM, 0.1 µF, 16<br>V, ± 10%, X7R, 0603           | 603          | GRM188R71C104KA01D       | MuRata              |

| C3, C11, C17, C22                         | 4 | 10 uF    | CAP, CERM, 10 μF, 16<br>V, ± 20%, X5R, 0805            | 805          | 0805YD106MAT2A           | AVX                 |

| C4, C5                                    | 2 | 4.7 uF   | CAP, CERM, 4.7 μF, 50<br>V, ± 10%, X7R, 1210           | 1210         | GRM32ER71H475KA88L       | MuRata              |

| C6                                        | 1 | 0.22 uF  | CAP, CERM, 0.22 μF, 50<br>V, ± 10%, X7R, 0805          | 805          | GRM21BR71H224KA01L       | MuRata              |

| C7                                        | 1 | 1 uF     | CAP, CERM, 1 μF, 25 V,<br>± 10%, X7R, 0805             | 805          | GRM21BR71E105KA99L       | MuRata              |

| C8, C9                                    | 2 | 47 uF    | CAP, CERM, 47 μF, 16<br>V, ± 20%, X5R, 1210            | 1210         | GRM32ER61C476ME15<br>L   | MuRata              |

| C10                                       | 1 | 0.022 uF | CAP, CERM, 0.022 μF,<br>16 V, ± 10%, X7R, 0402         | 402          | GRM155R71C223KA01D       | MuRata              |

| C12                                       | 1 | 1 uF     | CAP, CERM, 1 μF, 6.3 V,<br>± 20%, X7R, 0402            | 402          | GRM155R70J105MA12D       | MuRata              |

| C13, C14                                  | 2 | 20 pF    | CAP, CERM, 20 pF, 50<br>V, ± 5%, C0G/NP0, 0402         | 402          | GRM1555C1H200JA01D       | MuRata              |

| C15                                       | 1 | 0.56 uF  | CAP, CERM, 0.56 μF, 25<br>V, ± 10%, X7R, 1206          | 1206         | C1206C564K5RACTU         | AVX                 |

| C16, C18                                  | 2 | 1000 pF  | CAP, CERM, 1000 pF,<br>2000 V, ± 10%, X7R,<br>1206_190 | 1206_190     | 202R18W102KV4E           | Johanson Technology |

| C19, C20, C24, C26,<br>C30, C31, C32, C33 | 8 | 0.01 uF  | CAP, CERM, 0.01 μF, 50<br>V, ± 10%, X7R, 0402          | 402          | GRM155R71H103KA88D       | MuRata              |

| C21, C23, C25, C27,<br>C34, C35           | 6 | 0.1 uF   | CAP, CERM, 0.1 µF, 25<br>V, ± 20%, X7R, 0402           | 402          | TMK105B7104MV-FR         | Taiyo Yuden         |

| C28, C29                                  | 2 | 1 uF     | CAP, CERM, 1 μF, 50 V,<br>± 10%, X7R, 0603             | 603          | UMK107AB7105KA-T         | Taiyo Yuden         |

| C36, C43                                  | 2 | 10 uF    | CAP, CERM, 10 μF, 100<br>V, ± 20%, X7R,<br>6x5x5mm     | 6 × 5 x 5 mm | CKG57NX7R2A106M500<br>JH | TDK                 |

| C37, C38, C41                             | 3 | 100 uF   | CAP, CERM, 100 µF, 10<br>V, ± 20%, X5R, 1210           | 1210         | C1210C107M8PACTU         | Wurth Elektronik    |

| C39, C40, C42                             | 3 | 10 uF    | CAP, CERM, 10 μF, 6.3<br>V, ± 20%, X7R, 0805           | 805          | C2012X7R0J106M125AB      | TDK                 |

| C47, C49                                  | 2 | 0.1 uF   | CAP, CERM, 0.1 µF, 25<br>V, ± 5%, X7R, 0603            | 603          | 06033C104JAT2A           | AVX                 |

| C48, C50                                  | 2 | 1000 pF  | CAP, CERM, 1000 pF, 25 V, ± 10%, X7R, 0402             | 402          | 8.85012E + 11            | Wurth Elektronik    |

| C51                                       | 1 | 2.2 uF   | CAP, CERM, 2.2 µF, 6.3<br>V, ± 20%, X5R, 0402          | 402          | JMK105BJ225MV-F          | Taiyo Yuden         |

24 TIDA-00845: Reference Design of Two-Port Automotive USB 2.0 Hub with Short-to-Battery Protection

| D1, D3, D7                         | 3 | Green     | LED, Green, SMD                                                           | LED_0805                                          | LTST-C171GKT         | Lite-On               |

|------------------------------------|---|-----------|---------------------------------------------------------------------------|---------------------------------------------------|----------------------|-----------------------|

| D2                                 | 1 | 60 V      | Diode, Schottky, 60 V, 5<br>A, PowerDI5                                   | PowerDI5                                          | PDS560-13            | Diodes Inc.           |

| D8, D9, D10, D12, D13,<br>D14, D15 | 7 | Super Red | LED, Super Red, SMD                                                       | LED, 1 × .35 × .5 mm                              | VLMS1500-GS08        | Vishay-Semiconductor  |

| D11                                | 1 | 15 V      | Diode, Zener, 15 V, 500<br>mW, SMA                                        | SMA                                               | 1SMA5929BT3G         | ON Semiconductor      |

| FID1, FID2, FID3                   | 3 |           | Fiducial mark. There is nothing to buy or mount.                          | Fiducial                                          | N/A                  | N/A                   |

| H1, H2, H3, H4                     | 4 |           | Screw Pan Head M3                                                         | Screw M3                                          | 29311                | Keystone              |

| H5, H6, H7, H8                     | 4 |           | HEX STANDOFF M3<br>BRASS 5 MM                                             | HEX STANDOFF M3<br>BRASS 5MM                      | R30-3000502          | Harwin                |

| J1                                 | 1 |           | Connector, DC Jack 2.1<br>× 5.5 mm, TH                                    | Conn, DC Jack, pin 2-<br>mm Dia.                  | PJ-202AH             | CUI Inc.              |

| J2, J16, J17                       | 3 |           | Connector, SMB,Vertical<br>RCP 0-4GHz, 50 Ω, TH                           | 236 × 293 × 236 mil                               | 131-3701-261         | Emerson Network Power |

| J3, J4, J11, J12                   | 4 |           | Compact Probe Tip<br>Circuit Board Test Points,<br>TH, 25 per             | TH Scope Probe                                    | 131-5031-00          | Tektronix             |

| J5                                 | 1 |           | Connector, Receptacle,<br>USB Type A, R/A, Top<br>Mount TH                | USB Type A right angle                            | 292303-4             | TE Connectivity       |

| J6                                 | 1 |           | Connector, Receptacle,<br>USB TYPE B, R/A, Top<br>Mount TH                | USB Type B Receptacle                             | 67068-8000           | Molex                 |

| J7                                 | 1 |           | Connector, Receptacle,<br>USB TYPE A, 4POS<br>SMD                         | USB TYPE A<br>CONNECTOR<br>RECEPTACLE 4POS<br>SMD | 896-43-004-00-000000 | Mill-Max              |

| J8, J10                            | 2 |           | Header, 100 mil, 2 × 1,<br>TH                                             | Header, 2 × 1, 100 mil,<br>TH                     | 800-10-002-10-001000 | Mill-Max              |

| J13, J14                           | 2 |           | Header, 2.54 mm, 2 × 1,<br>Vertical, TH                                   | Header, 2.54 mm, 2x1,<br>TH                       | 22-23-2021           | Molex                 |

| J15, J18                           | 2 |           | Header, 2.54 mm, 1 × 1,<br>Gold, TH                                       | Header, 2.54 mm, 1x1,<br>TH                       | 61300111121          | Wurth Elektronik      |

| K2, K3                             | 2 |           |                                                                           | 60.0 × 15.8 mm                                    | DAR70510             | Cynergy 3             |

| L1                                 | 1 | 6.5 uH    | Inductor, Shielded Drum<br>Core, Superflux, 6.5 μH,<br>6 A, 0.0225 Ω, SMD | 6.9 × 4.8 × 6.9 mm                                | 744314650            | Wurth Elektronik      |

| R1                                 | 1 | 825       | RES, 825, 1%, 0.063 W, 0402                                               | 402                                               | CRCW0402825RFKED     | Vishay-Dale           |

Design Files

| R2            | 1 | 100 k    | RES, 100 k, 0.5%, 0.063<br>W, 0402                              | 402                                   | CRCW0402100KDHEDP | Vishay-Dale    |

|---------------|---|----------|-----------------------------------------------------------------|---------------------------------------|-------------------|----------------|

| R3, R30       | 2 | 255      | RES, 255, 1%, 0.063 W, 0402                                     | 402                                   | CRCW0402255RFKED  | Vishay-Dale    |

| 74            | 1 | 7.5      | RES, 7.5, 5%, 10 W,<br>RES 48 × 9.5 × 9 mm                      | RES 0.620" L × 0.195" W               | TEH100M7R50FE     | Ohmite         |

| २5            | 1 | 17.8 k   | RES, 17.8 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW040217K8FKED  | Vishay-Dale    |

| 86            | 1 | 49.9 k   | RES, 49.9 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW040249K9FKED  | Vishay-Dale    |

| 87            | 1 | 30.1 k   | RES, 30.1 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW040230K1FKED  | Vishay-Dale    |

| 88            | 1 | 1.00 Meg | RES, 1.00 M, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW04021M00FKED  | Vishay-Dale    |

| R12           | 1 | 1.87 k   | RES, 1.87 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW04021K87FKED  | Vishay-Dale    |

| R13, R14      | 2 | 30.1     | RES, 30.1, 1%, 0.063 W, 0402                                    | 402                                   | CRCW040230R1FKED  | Vishay-Dale    |

| R15           | 1 | 330      | RES, 330, 5%, 0.063 W, 0402                                     | 402                                   | CRCW0402330RJNED  | Vishay-Dale    |

| R16           | 1 | 4.99 k   | RES, 4.99 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW04024K99FKED  | Vishay-Dale    |

| R17           | 1 | 9.53 k   | RES, 9.53 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW04029K53FKED  | Vishay-Dale    |

| R18           | 1 | 1.00 k   | RES, 1.00 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW04021K00FKED  | Vishay-Dale    |

| R19, R20, R21 | 3 | 4.7 k    | RES, 4.7 k, 5%, 0.063 W, 0402                                   | 402                                   | CRCW04024K70JNED  | Vishay-Dale    |

| R22, R23, R26 | 3 | 10.0 k   | RES, 10.0 k Ω, 1%, 0.1W, 0603                                   | 603                                   | CRCW060310K0FKEA  | Vishay-Dale    |

| R24           | 1 | 90.9 k   | RES, 90.9 k, 1%, 0.063<br>W, 0402                               | 402                                   | CRCW040290K9FKED  | Vishay-Dale    |

| 25            | 1 | 10.0 k   | RES, 10.0 k, 0.5%, 0.063<br>W, 0402                             | 402                                   | CRCW040210K0DHEDP | Vishay-Dale    |

| R27, R28, R31 | 3 | 165      | RES, 165, 1%, 0.063 W, 0402                                     | 402                                   | CRCW0402165RFKED  | Vishay-Dale    |

| 51            | 1 |          | SWITCH PUSH SPST-<br>NO 10 A 125 V                              | For example: 0603, used in PnP report | GPB527C202BR      | CW Industries  |

| S2, S3        | 2 |          | Switch, Normally open,<br>2.3-N force, 200-k<br>operations, SMD | KSR                                   | KSR221GLFS        | C&K Components |

| TP1         | 1 | Red | Test Point, Miniature,<br>Red, TH                                                                                                                                                            | Red Miniature Testpoint | 5000              | Keystone                 |

|-------------|---|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|--------------------------|

| U1, U2, U3  | 3 |     | AUTOMOTIVE USB 2.0<br>Interface Protection with<br>Short-to-Battery and<br>Short-to-Ground<br>Protection, DBQ0016A                                                                           | DBQ0016A                | TPD3S714QDBQRQ1   | Texas Instruments        |

| U4          | 1 |     | 400-Mbps IEEE 1394a<br>One-Port Cable<br>Transceiver / Arbiter, 3.3<br>V, 0 to 70 degC, 48-Pin<br>HTQFP (PHP), Green<br>(RoHS & no Sb/Br)                                                    | PHP0048C                | TUSB4020BIPHP     | Texas Instruments        |

| U5          | 1 |     | SIMPLE SWITCHER 40<br>V 3.5 A, 2.2-MHz Step-<br>Down Converter with 40-<br>µA IQ, DDA0008E                                                                                                   | DDA0008E                | LMR14030SDDAR     | Texas Instruments        |

| U6          | 1 |     | Single Output Fast<br>Transient Response<br>LDO, 1.5 A, Fixed 3.3-V<br>Output, 2.1 to 20-V Input,<br>6-pin SOT-223 (DCQ), -<br>40 to 125 degC, Green<br>(RoHS & no Sb/Br)                    | DCQ0006A                | TPS7A4533DCQR     | Texas Instruments        |

| U7          | 1 |     | Single Output LDO, 1.5<br>A, Adjustable 0.8 to 3.6-V<br>Output, 0.8 to 5.5-V<br>Input, with Programmable<br>Soft Start, 20-pin VQFN<br>(RGW), -40 to 125 degC,<br>Green (RoHS & no<br>Sb/Br) |                         | TPS74801RGWR      | Texas Instruments        |

| U8, U9, U17 | 3 |     | Single Bus Buffer Gate<br>With 3-State Output,<br>DCK0005A                                                                                                                                   | DCK0005A                | SN74LVC1G125DCKR  | Texas Instruments        |

| U11, U12    | 2 |     | Fully Integrated, Hall<br>Effect-Based Linear<br>Current Sensor IC with<br>2.1-kVRMS Isolation and<br>a Low-Resistance<br>Current Conductor,<br>SOIC-8                                       | SOIC-8                  | ACS712ELCTR-05B-T | Allegro Microsystems Inc |

Design Files

| U13, U14, U15, U16 | 4 | with 10<br>and 6-\<br>Channe<br>degC, 2 | D-pF Capacitance<br>V Breakdown, 1<br>iel, -40 to +125<br>2-pin X2SON<br>, Green (RoHS & | DPY0002A                      | TPD1E05U06DPYR  | Texas Instruments |

|--------------------|---|-----------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|-----------------|-------------------|

| Y1                 | 1 | Crystal<br>pF, SM                       |                                                                                          | Crystal,<br>XTAL_2_SM_197X126 | 445C25D24M00000 | CTS Freq Controls |

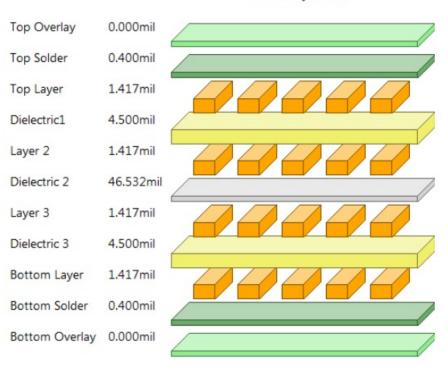

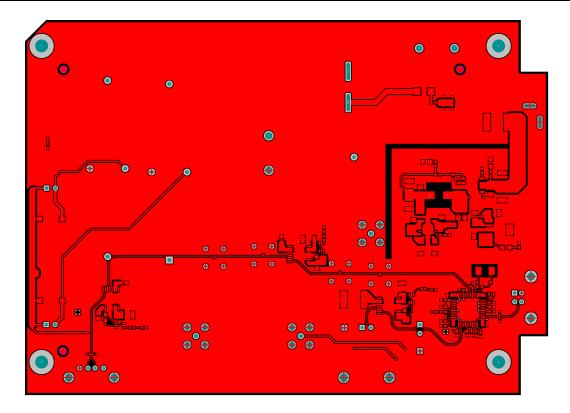

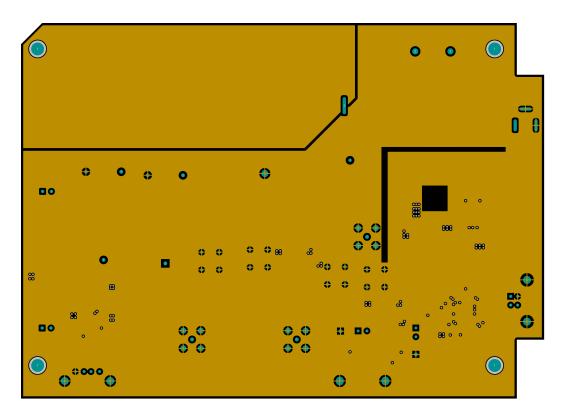

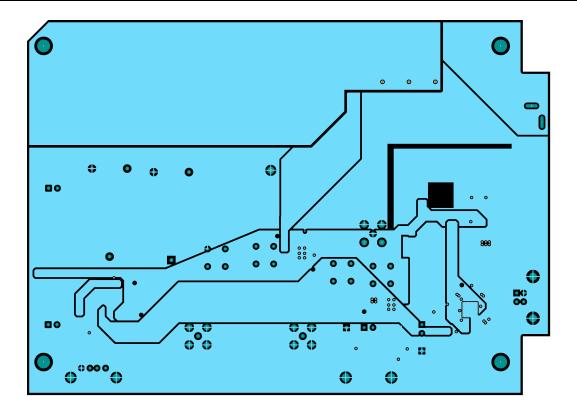

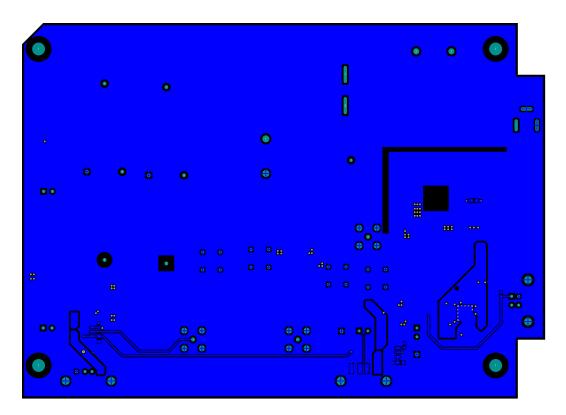

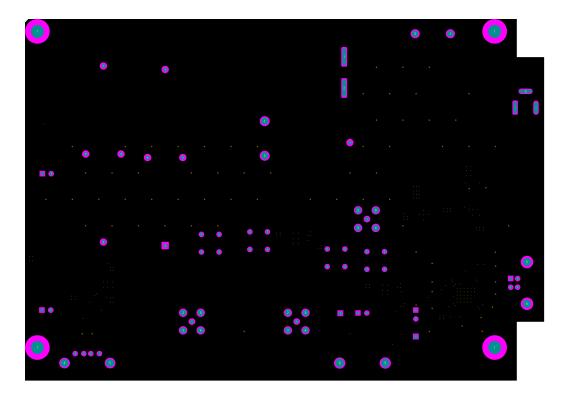

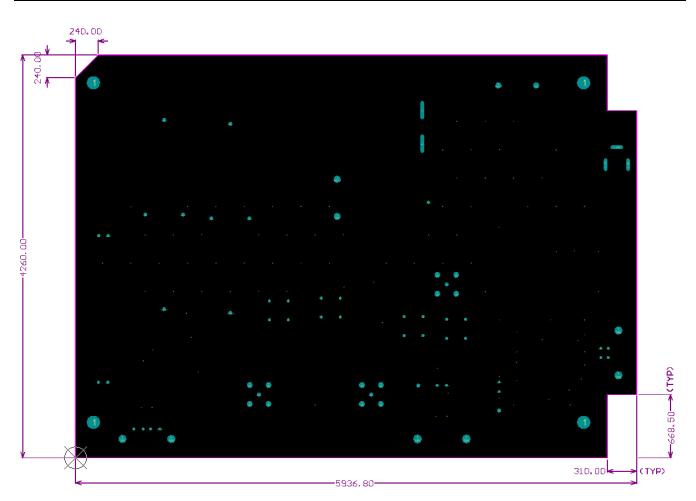

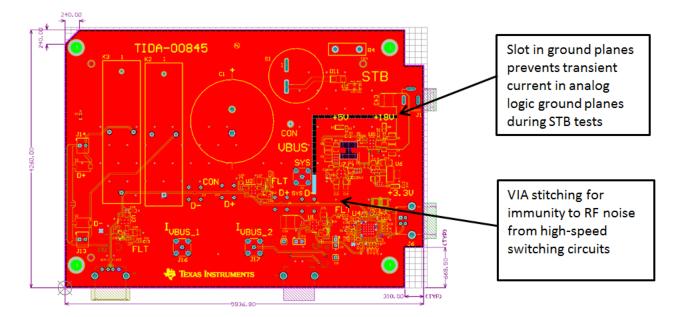

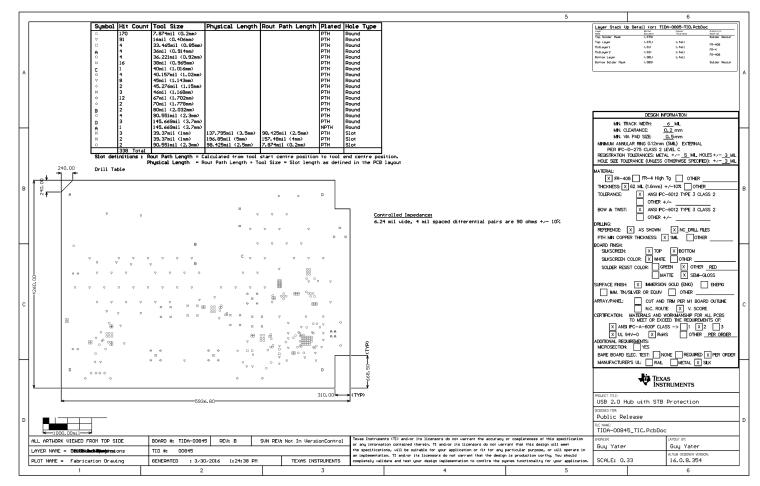

# 6.3 PCB Layout Recommendations

TIDA-00845 is a 4-Layer printed-circuit board (PCB). The board thickness is 0.062". Figure 28 shows the PCB stack-up. The core material for dielectric1 and dielectric3 is FR-408HR. Due to the 5.7" long traces of the DP1 data lines, and their capacitive loading by 3 transient voltage suppressors and reed relays (K1 or K2), FR-408HR, a dielectric with a low loss tangent, was selected to help maintain the signal integrity.

Board Layer Stack

Figure 28. TIDA-00845 PCB Stack-Up

Route all USB 2.0 lines as controlled impedance, high-speed differential pairs. Minimize the use of VIAs and 90-degree corners in the routing of the high-speed lines. Assure the high-speed lines reference a solid ground plane and the plane is void of cuts and splits, to prevent impedance discontinuities. ESD connection points must be placed in-line with the high-speed signal traces to reduce reflections caused by routing discontinuities.

Design Files

www.ti.com

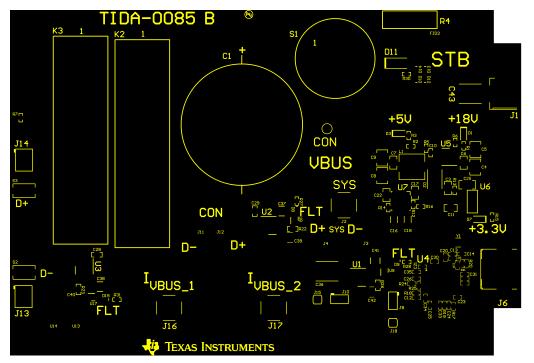

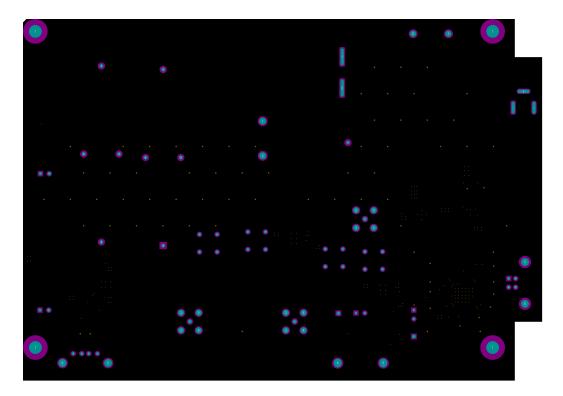

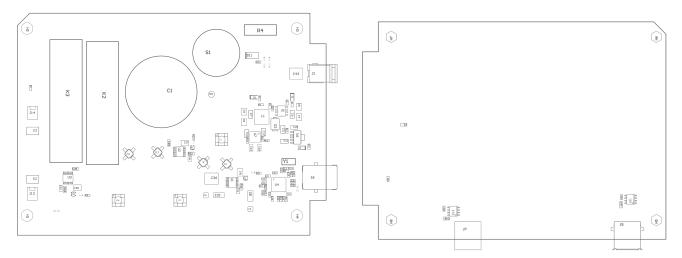

# 6.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-00845.

Figure 29. Top Silkscreen

Figure 30. Top Solder Mask

Figure 31. Top Layer

# Figure 32. Ground Plane Layer 2

Figure 33. PWR Plane Layer 3

# Figure 34. Bottom Layer

Design Files

Figure 35. Bottom Solder Mask

# Figure 36. Bottom Silkscreen

Figure 37. Mechanical Dimensions

# 6.4 Altium Project

To download the Altium project files, see the design files at TIDA-00845.

Figure 38. TIDU-00845 Altium

Design Files

#### 6.5 Layout Guidelines

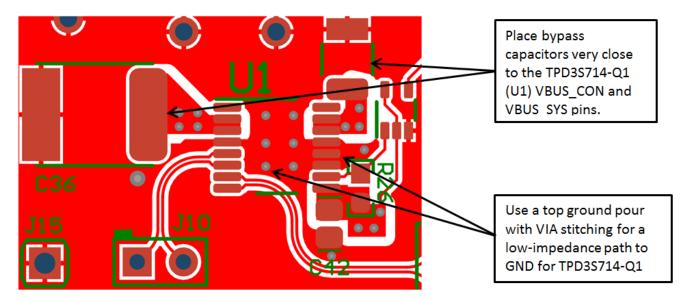

#### 6.5.1 TPD3S714-Q1

Figure 39. TPD3S714-Q1

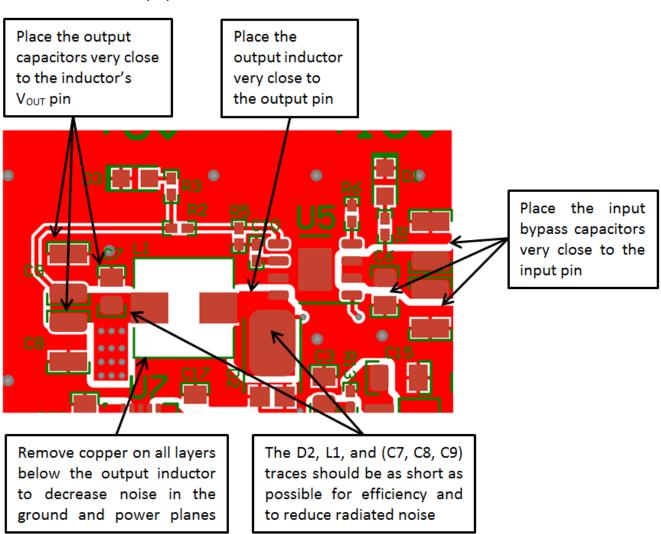

# 6.5.2 LMR14030-Q1 (U5)

Figure 40. LMR14030-Q1 (U5)

Design Files

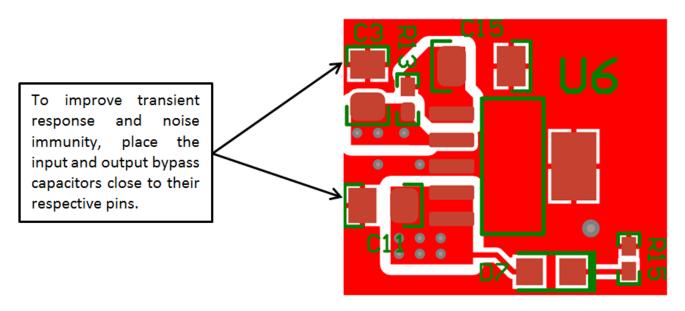

# 6.5.3 TPS7A4533 (U6)

Figure 41. TPS7A4533 (U6)

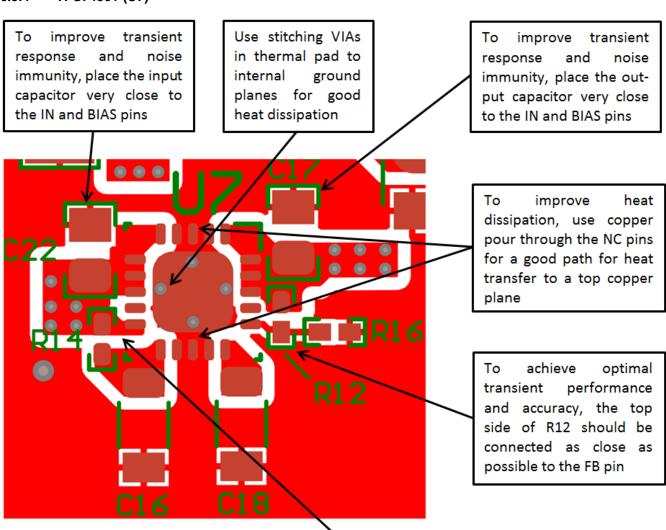

To minimize the voltage drop on the BIAS pin during transient conditions, the trace length between the BIAS pin and the  $V_{\rm IN}$  node should be minimized. This also improves the turn-on response

Figure 42. TPS74801 (U7)

Design Files

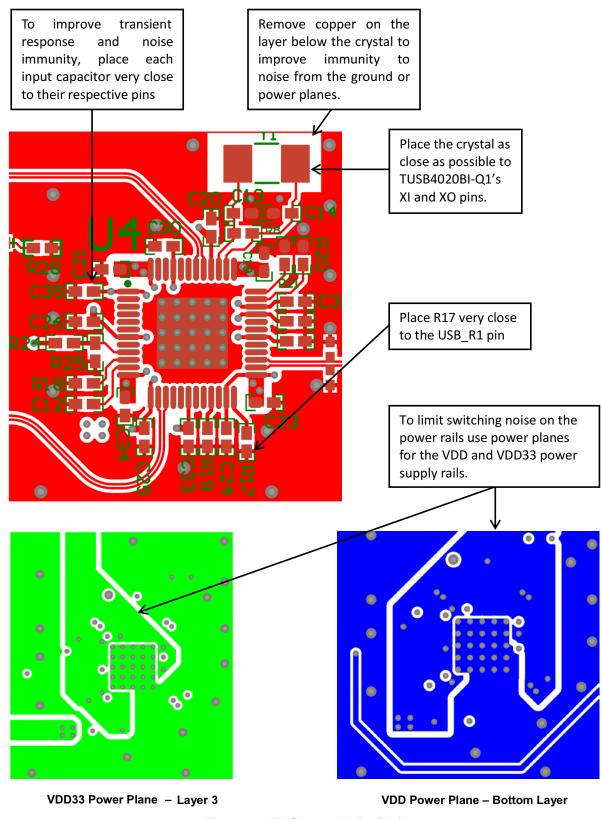

#### 6.5.5 TUSB4020BI-Q1 (U4)

# 6.6 Gerber Files

To download the Gerber files, see the design files at TIDA-00845.

Figure 44. TIDA-00845 Gerber Files

Design Files

www.ti.com

#### 6.7 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-00845.

Figure 45. Top Assembly Drawing

Figure 46. Bottom Assembly Drawing

# 7 References

1. Designing USB for Short-to-battery Tolerance in Automotive Environments, SLLY019, 2016

References

- 2. ESD Protection Layout Guide, SLVA680, 2015

- 3. LDO Noise Demystified, SLAA412, 2008

- 4. Texas Instruments WEBENCH® Design Center, http://www.ti.com/webench

- 5. Texas Instruments E2E Community, http://e2e.ti.com/

# 8 Terminology

- STB Short to battery

- DP Downstream port

- UP Upstream port

# 9 About the Author

**GUY YATER** is an Applications Engineer at Texas Instruments, where he is responsible for developing reference design solutions for the industrial, automotive, and consumer interface transient-voltage protection segment. Guy brings to this role his extensive experience in high-speed digital, low-noise analog, and system-level transient-voltage protection design expertise. Guy earned his Bachelors of Science in Electrical Engineering (BSEE) from the University of Texas at Dallas in Richardson, TX. Guy is a current member of the Institute of Electrical and Electronics Engineers (IEEE).

Revision History

www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Original (May 2016) to A Revision Page |     |  |  |  |  |  |

|---|----------------------------------------------------|-----|--|--|--|--|--|

| • | Changed IO Capacitance to 0.42 pF (Typ)            | . 8 |  |  |  |  |  |

| • | Updated PCB Layout Recommendations Section         | 29  |  |  |  |  |  |

#### **IMPORTANT NOTICE FOR TI REFERENCE DESIGNS**

Texas Instruments Incorporated ('TI') reference designs are solely intended to assist designers ("Designer(s)") who are developing systems that incorporate TI products. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design.

TI's provision of reference designs and any other technical, applications or design advice, quality characterization, reliability data or other information or services does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such reference designs or other items.

TI reserves the right to make corrections, enhancements, improvements and other changes to its reference designs and other items.

Designer understands and agrees that Designer remains responsible for using its independent analysis, evaluation and judgment in designing Designer's systems and products, and has full and exclusive responsibility to assure the safety of its products and compliance of its products (and of all TI products used in or for such Designer's products) with all applicable regulations, laws and other applicable requirements. Designer represents that, with respect to its applications, it has all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. Designer agrees that prior to using or distributing any systems that include TI products, Designer will thoroughly test such systems and the functionality of such TI products as used in such systems. Designer may not use any TI products in life-critical medical equipment unless authorized officers of the parties have executed a special contract specifically governing such use. Life-critical medical equipment is medical equipment where failure of such equipment would cause serious bodily injury or death (e.g., life support, pacemakers, defibrillators, heart pumps, neurostimulators, and implantables). Such equivalent classifications outside the U.S.

Designers are authorized to use, copy and modify any individual TI reference design only in connection with the development of end products that include the TI product(s) identified in that reference design. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of the reference design or other items described above may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS AND OTHER ITEMS DESCRIBED ABOVE ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY DESIGNERS AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS AS DESCRIBED IN A TI REFERENCE DESIGN OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

TI's standard terms of sale for semiconductor products (http://www.ti.com/sc/docs/stdterms.htm) apply to the sale of packaged integrated circuit products. Additional terms may apply to the use or sale of other types of TI products and services.

Designer will fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of Designer's noncompliance with the terms and provisions of this Notice.

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated