## Test Report For PMP15012 04/05/2016

# TEXAS INSTRUMENTS

#### **1. Design Specifications**

| Vin Min                    | 18VDC  |

|----------------------------|--------|

| Vin Max                    | 36VDC  |

| Vout                       | -15VDC |

| Iout                       | 200mA  |

| Target Switching Frequency | 500kHz |

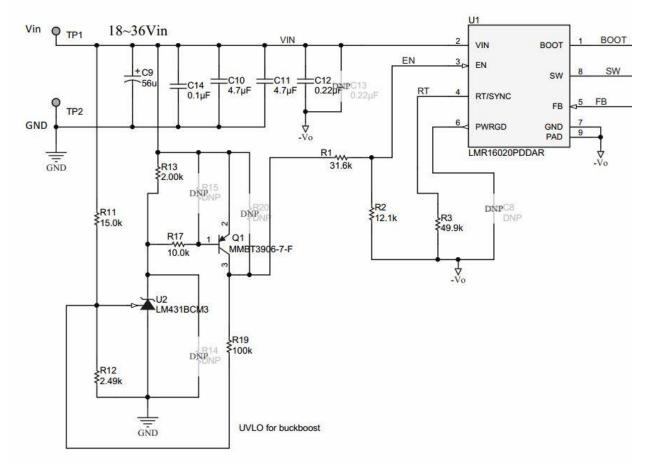

#### 2. Circuit Description

PMP15012 is buck-boost solution which accepts an input voltage of 18 to  $36V_{IN}$  and provides negative 15V/200mA output to the load. This reference design adds an external UVLO circuit to narrow the UVLO hysteresis because buck-boost converter is hard to shut down. This LMR16020 buck-boost reference design can be used for supplying the DAC/ADC/OA in industrial application.

#### 3. External UVLO Circuit Principle

The detail UVLO circuit is as below.

1) In usual situation (connect R<sub>20</sub>), start up voltage is

$$\frac{V_{in1}}{R_1 + R_2} \cdot R_2 = V_{EN} \tag{1}$$

Shut down voltage is

$$\frac{V_{in2} - V_o}{R_1 + R_2} \cdot R_2 = V_{EN}$$

(2)

The UVLO hysteresis is

$$V_{hvs} = V_{in1} - V_{in2} = -V_o \tag{3}$$

In this situation, the UVLO hysteresis is relative to output voltage, if the Vout is high, the hysteresis will be large, which is not reasonable in real application.

2) Add the external UVLO circuit (disconnect  $R_{20}$ ). In this situation, start up voltage is decided by  $R_{11}$  and  $R_{12}$ . Once  $V_{IN}$  exceeds 2.5( $R_{11}+R_{12}$ )/ $R_{12}$ , output of LM431 goes low and  $Q_1$  conducts. Collector voltage of  $Q_1$  is equal to  $V_{IN}$  so IC start up as usual buck converter. Once  $V_{IN}$  decreases below 2.5( $R_{11}+R_{12}$ )/ $R_{12}$ , output of LM431 goes high and  $Q_1$  disabled. The UVLO divide path is  $R_{11}$ -  $R_{12}$ -  $R_{19}$ -  $R_1$ -  $R_2$ . Choosing a large  $R_{19}$  could shut down the IC immediately. Adjusting  $R_{13}$  and  $R_{17}$  could adjust the DC operate point of  $Q_1$ .

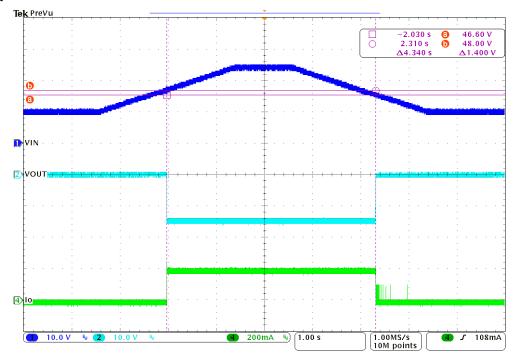

The startup and shut down waveform is as below. Test condition is:  $V_{IN}$ : 10V-24V-10V,  $I_0$ =200mA, the UVLO hysteresis is about 1.4V.

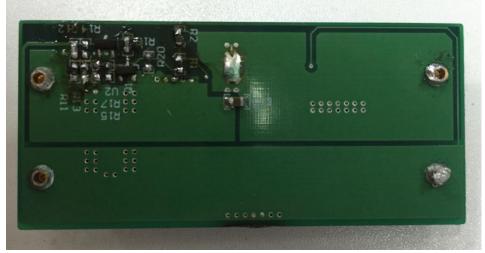

#### 4. Board Photos

**Top** (66.29x33.48mm<sup>2</sup>)

Bottom (66.29x33.48mm<sup>2</sup>)

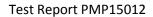

### 5. Thermal Data

IR thermal image taken at steady state at 200mA load and  $V_{IN}$  = 18V for two minutes with no airflow (4 Layer board, 1 Oz copper layer)

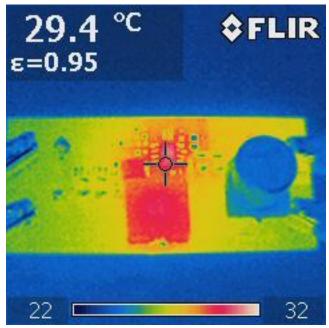

IR thermal image taken at steady state at 200mA load and VIN = 36V for two minutes with no airflow (4 Layer board, 1 Oz copper layer)

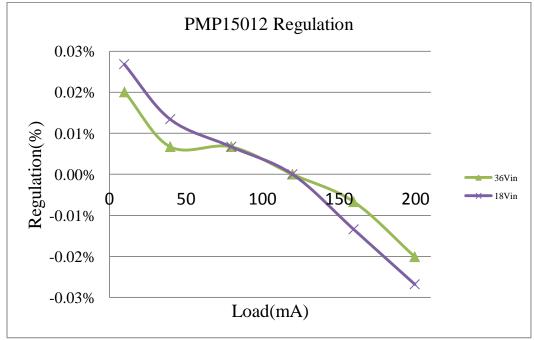

#### 6. Efficiency and Regulation

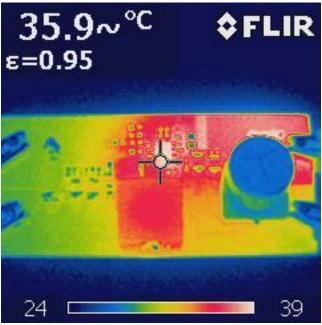

#### **6.1 Efficiency Chart**

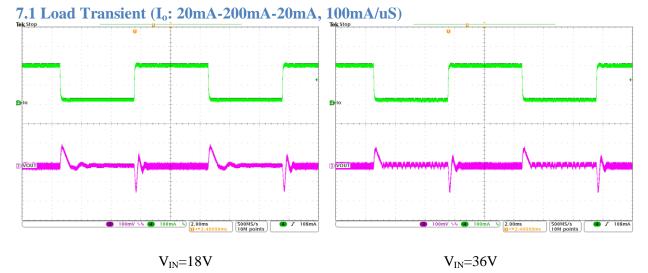

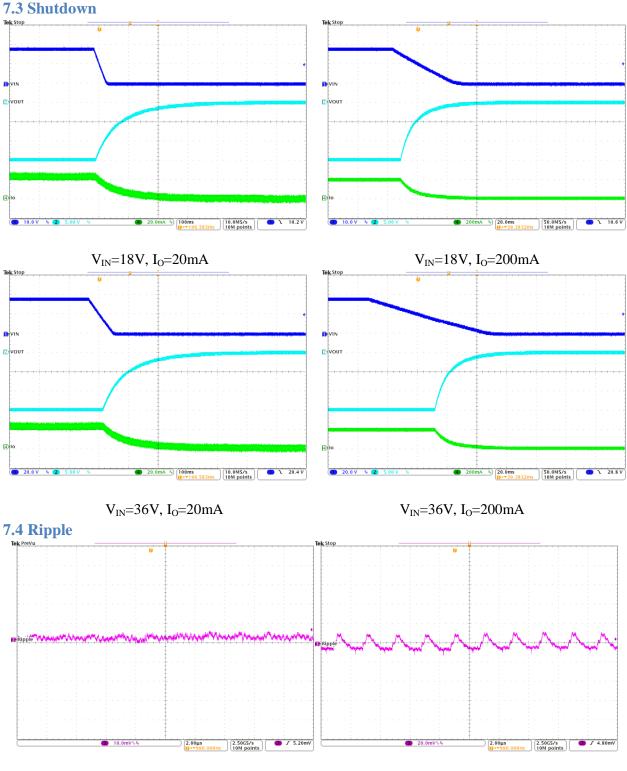

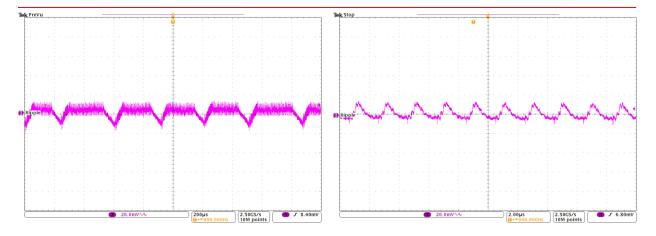

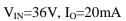

#### 7. Waveform

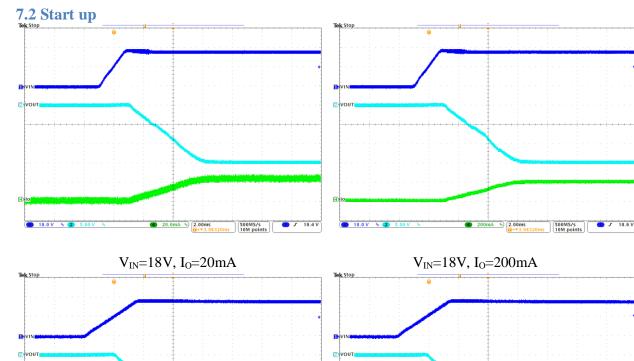

(1) 20.0 V 🔖 (2) 5.00 V 🐐

V<sub>IN</sub>=36V, I<sub>0</sub>=20mA

V<sub>IN</sub>=36V, I<sub>0</sub>=200mA;

200mA → 2.00ms

1.98320ms

500MS/s

10M points

7 22.0 V

7

1 20.0 V 🐐 (2) 5.00 V

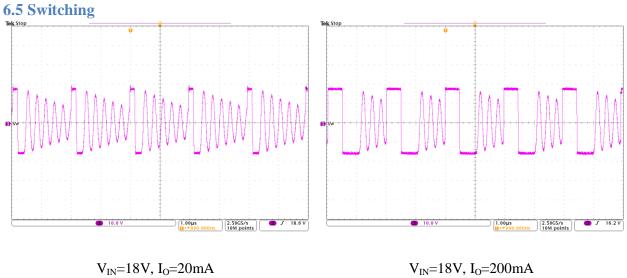

$V_{IN}$ =18V,  $I_O$ =20mA

V<sub>IN</sub>=18V, I<sub>0</sub>=200mA

Test Report PMP15012

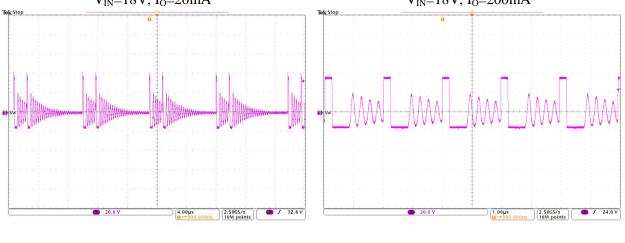

$V_{IN}$ =36V,  $I_O$ =20mA

V<sub>IN</sub>=36V, I<sub>0</sub>=200mA

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated