## TI Designs: TIDA-01420 Basic Isolated Three-Phase Compact Power Stage Reference Design for Industrial Drives

# Texas Instruments

## Description

This three-phase, compact power stage reference design uses a gate driver with basic isolation (UCC53xx) to cater to the isolation requirements of systems using dual controllers. The capacitive isolation of the gate driver offers a longer lifetime and better propagation delay match over optocouplers to minimize the inverter deadband distortions and losses. If required, another level of basic isolation can be used between the controllers to achieve reinforced isolation at the system level. This approach optimizes the isolation cost of the system as well as helps achieve compactness. This design also demonstrates the interlocking feature of the UCC53xx gate driver, which protects the IGBTs during shoot-through. This reference design uses the F28379D Delfino<sup>™</sup> control card to generate PWM signals for controlling the threephase inverter.

## Resources

| TIDA-01420     |

|----------------|

| UCC5350MCD     |

| UCC5390ECD     |

| LM3480         |

| TLV704         |

| TLV1117-33     |

| SN74LVC1G17    |

| TMDSCNCD28379D |

Design Folder Product Folder Product Folder Product Folder Product Folder Product Folder Product Folder Tool Folder

ASK Our E2E Experts

#### Features

- Basic Isolated 200- to 480-V AC Three-Phase Power Stage With Direct PWM CMOS Interface to MCU for Hot-Side Control

- Low Pin Count Gate Driver UCC53xx Enables Compact Solution and Increased Flexibility of Gate Driver Placement

- Short (72 ns Typical) Propagation Delay and Very Small Skew Between Propagation Delays Optimizes Deadband Distortion and Losses

- Gate Driver Supports Option for PWM Interlock

Protection to Avoid Shoot-Through

- Option to Populate Three Variants of Gate Drivers: Miller Clamp to Avoid Parasitic Turnon Effect; UVLO With Reference to Emitter to Provide Robust Protection of IGBT Against Operation in Linear Region; and Split Output to Control Rise and Fall Times

- Built-in Bootstrap-Based Unipolar Power Supply for High-Side Drivers and Option to Feed External Bipolar Voltage Rails

- Gate Driver With High Drive Strength of 17-A Sink/Source Currents Enables Driving High-Current IGBTs Without External Buffer

## Applications

- AC Inverter and VF Drives

- Industrial Power Supplies

- Servo Drives

- Solar inverters

1

Basic Isolated Three-Phase Compact Power Stage Reference Design for Industrial Drives

#### System Description

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

## 1 System Description

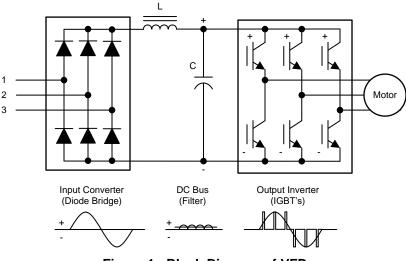

A variable frequency drive (VFD) is a type of motor controller that drives an electric motor by varying the frequency and voltage supplied to the electric motor. As the application changes, the motor speed requirements changes; the VFD can simply increase or reduce the motor speed to meet the speed requirement. In addition, the VFD can reduce the system's average energy consumption. Figure 1 shows the block diagram demonstrating a VFD. The basic components of a VFD are:

- · Input section, which draws AC electric power from the utility and converts the AC into DC power

- Inverter section, which converts DC back into a controllable AC waveform

In the inverter section, insulated gate bipolar transistors (IGBTs) can be used as semiconductor switches to convert the DC bus voltage to AC. IGBTs have advantages such as high input impedance as the gate is insulated, a rapid response ability, good thermal stability, simple driving circuit, good ability to withstand high voltage, snubber-less operation, and controllability of switching behavior to provide reliable short-circuit protection.

Figure 1. Block Diagram of VFD

Although various induction motor control techniques are in practice today, the most popular control technique is by generating variable frequency supply, which has a constant voltage to frequency ratio. This technique is popularly known as VF control. VF control is simple to implement and cost effective. The base speed of the induction motor is directly proportional to the supply frequency and the number of poles of the motor. Because the number of poles is fixed by design, the best way to vary the speed of the induction motor is by varying the supply frequency. The torque developed by the induction motor is directly proportional to the ratio of the applied voltage and the frequency of supply. By varying the voltage and the frequency, but keeping their ratio constant, the torque developed can be kept constant throughout the speed range. This is exactly what VF control tries to achieve.

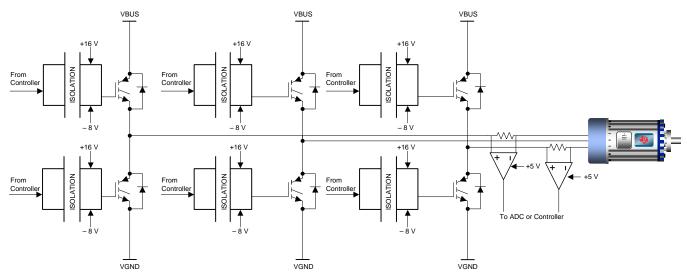

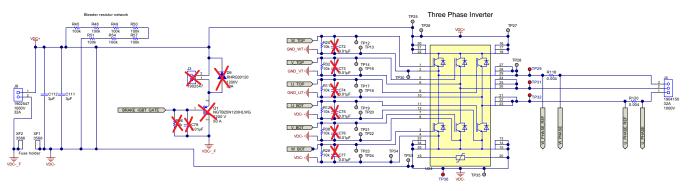

The three-phase induction motor is connected to a three-phase inverter bridge as shown in Figure 2. The power inverter has six switches that are controlled to generate three-phase AC output from the DC bus. PWM signals generated from the microcontroller (MCU) control these six switches through an isolated gate driver. The amplitude of phase voltage is determined by the duty cycle of the PWM signals. The switching produces a rectangular shaped output waveform that is rich in harmonics. The inductive nature of the motor's stator windings filters this supplied current to produce a three-phase sine wave with negligible harmonics.

To prevent the DC bus supply from being shorted, the upper and lower switches of the same half bridge must not be switched on at the same time. A dead time is given between switching off one switch and switching on the other. This dead time ensures that both switches are not conductive at the same time as each one change states. The UCC53xx used in this design supports an interlocking function, thereby avoiding shoot-through. For more about this feature, see Section 2.3.3.

IEC safety standards mandate to isolate the high-voltage inverter section from the low-voltage controller section accessible by the operator to protect from electric shock. Depending upon the system architecture and voltage levels, either basic isolation, reinforced isolation, or a combination of the two are used.

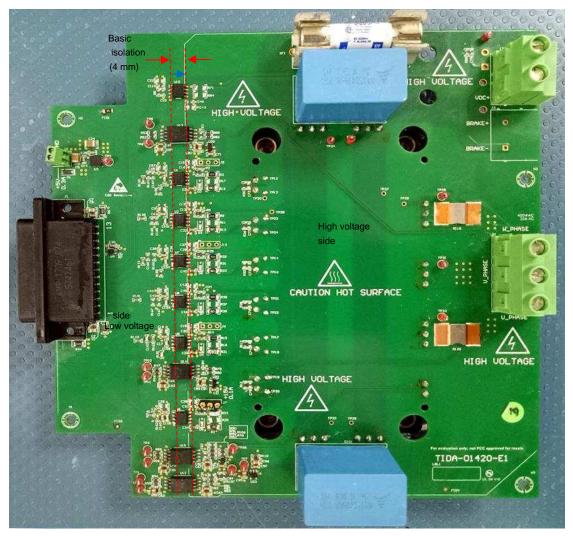

Figure 2. Three-Phase Power Stage With Isolated Gate Driver

The isolation between the high-voltage side and the low-voltage side MCU can be either basic or reinforced. Basic isolation protects against high voltage as long as the barrier is intact. To protect from and safely withstand high voltage surges that would damage equipment or harm humans, reinforced isolation is required, which is equivalent to two basic isolation in series. Reinforced isolation by itself is sufficient as a safety barrier against high voltage. Reinforced isolation requires a creepage of 8 mm whereas the creepage requirement for basic isolation is 4 mm for systems powered from a 480-V AC grid. A three-phase AC inverter necessitates the use of six gate drivers and a minimum of two current sensors, whose space can be optimized by adopting basic isolation. So the overall PCB area reduces in case of basic isolated gate drivers. To provide a compact and cost-effective solution in the power stage, this reference design uses basic isolation. Another level of basic isolation can be included in the system to obtain reinforced isolation.

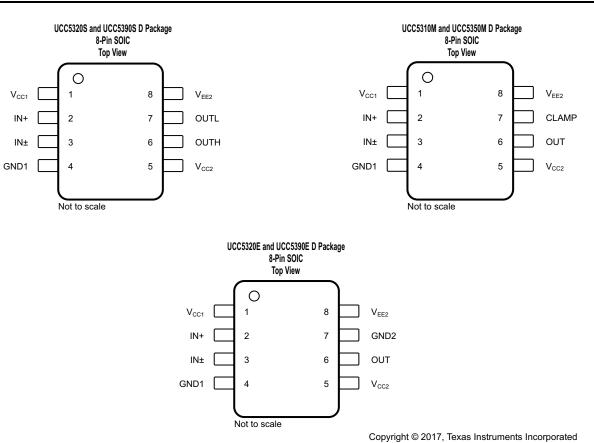

This reference design consists of a  $3\phi$  power stage using UCC53XXDWV basic isolated gate drivers intended to drive motors for various industrial applications. As shown in Figure 3, the UCC53XXDWV is available in three versions:

- The UCC53x0S: This device provides a split output that can be used to control the rise and fall times of the driver.

- The UCC53x0M: This device connects the gate of the transistor to an internal clamp to prevent false turnon caused by Miller current.

- The UCC53x0E: This device has its UVLO2 referenced to GND2, which facilitates bipolar supplies.

Figure 3. Pin Diagram of UCC53xx

This reference design characterizes the Miller clamp and UVLO versions of the gate drivers using the UCC5350MCD and UCC5390ECD, respectively. The IGBTs used to test these gate drivers are as follows:

UCC5350MCD: CM100TX-24S •

4

UCC5390ECD: 6MI180VB-120-50 •

1.1

## Key System Specifications

| Table 1 | . Key | System | <b>Specifications</b> |

|---------|-------|--------|-----------------------|

|---------|-------|--------|-----------------------|

| PARAMETER                            | SPECIFICATIONS                                                                                                                                                                                                         | DETAILS                                                                                                                                                                                                              |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DC link voltage                      | 280- to 900-V DC<br>280- to 900-V DC                   |                                                                                                                                                                                                                      |  |

| IGBT module                          | 6MBI180VB-120-50, 1200-V DC, 150<br>A                                                                                                                                                                                  | 6MBI180VB-120-50 is used with UCC5390E<br>and CM100TX-24S is used with UCC5350M                                                                                                                                      |  |

|                                      | CM100TX-24S 1200-V DC, 100 A                                                                                                                                                                                           |                                                                                                                                                                                                                      |  |

| Isolation                            | Basic                                                                                                                                                                                                                  |                                                                                                                                                                                                                      |  |

| Clearance                            | 4 mm                                                                                                                                                                                                                   | _                                                                                                                                                                                                                    |  |

| Gate driver package                  | 8 pin SOIC(D)                                                                                                                                                                                                          | —                                                                                                                                                                                                                    |  |

| Source/sink current rating (Minimum) | UCC5390E: 12 Apk/12 Apk                                                                                                                                                                                                |                                                                                                                                                                                                                      |  |

|                                      | UCC5350M: 10 Apk/5 Apk                                                                                                                                                                                                 | —                                                                                                                                                                                                                    |  |

| Switching frequency                  | 4 to 16 kHz                                                                                                                                                                                                            | _                                                                                                                                                                                                                    |  |

| Dead time(minimum)                   | 25 ns (gate driver max skew) + dead time for specific IGBT module                                                                                                                                                      | Inverter tested with a 1-µs deadband; can be varied as long as there is no overlap between VGE signals of top and bottom IGBT switches                                                                               |  |

| РСВ                                  | 4 layer, 1-oz copper, high Tg FR4, 1.6<br>mm thick                                                                                                                                                                     | _                                                                                                                                                                                                                    |  |

| Primary side supply                  | 5 V ± 5%, 500 mA                                                                                                                                                                                                       | —                                                                                                                                                                                                                    |  |

|                                      | UCC5390E: 15-V / -8 V bipolar                                                                                                                                                                                          |                                                                                                                                                                                                                      |  |

| Secondary side supply                | UCC5350M: 15-V unipolar                                                                                                                                                                                                | —                                                                                                                                                                                                                    |  |

| PCB size                             | 167 mm × 178 mm                                                                                                                                                                                                        |                                                                                                                                                                                                                      |  |

| PCB thickness                        | 1.6 mm                                                                                                                                                                                                                 |                                                                                                                                                                                                                      |  |

| Ambient Temperature                  | 0°C to 55°C                                                                                                                                                                                                            | Components selected support the industrial<br>temperature range of 85°C and the reference<br>design can operate outside the mentioned<br>temperature range with sufficient derating.<br>Tested only from 0°C to 55°C |  |

| Microcontroller Interface            | 7 PWM signals, current sense<br>modulator bit streams for two motor<br>phases, DC-link voltage sense<br>modulator bit stream, temperature<br>sense modulator bit stream, clock<br>signal, 5 V for the controller board | _                                                                                                                                                                                                                    |  |

5

## 2 System Overview

The UCC53xx isolated gate driver is available in an 8-pin SOIC (D) package. This package has a creepage and clearance of 4 mm and can support isolation voltage up to 3 kV<sub>RMS</sub>, which is good for applications where basic isolation is needed. The maximum isolation working voltage (V<sub>IOWM</sub>) for the UCC53xx is 700 V<sub>RMS</sub>. The UCC53x0 family has lower part-to-part skew, lower propagation delay, higher operating temperature, and higher common mode transient immunity (CMTI).

## 2.1 Block Diagram

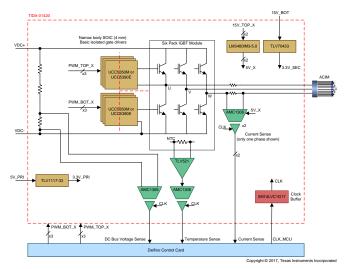

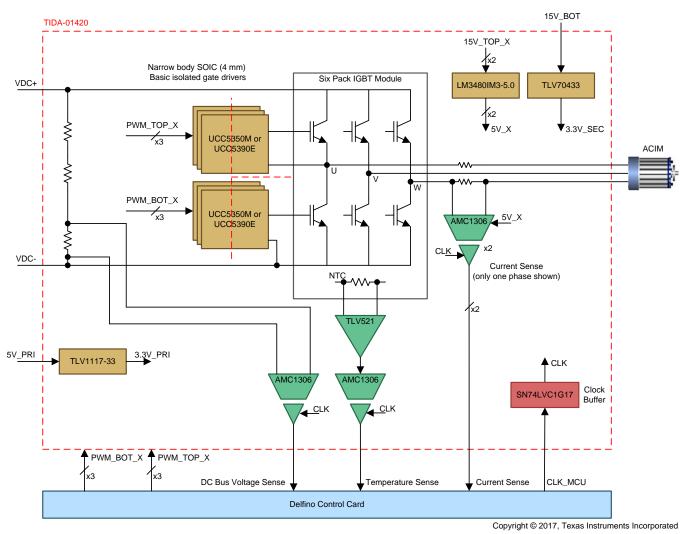

Figure 4 shows the system block diagram of the basic isolated three-phase inverter with in-line precision phase current sensing with a shunt resistor. The TIDA-01420 reference design is highlighted with a red dashed box.

Figure 4. TIDA-01420 Block Diagram

The inverter section is composed of a six-pack IGBT module that contains three half bridges. Each IGBT of the module is driven by a basic isolated gate driver. Two different PCBs are fabricated to characterize the two versions of the gate driver: the Miller clamp version (UCC5350MCD) and the UVLO version (UCC5390ECD).

The UCC5350MCD uses a unipolar 15-V power supply for driving the IGBT gates. The low-side gate drivers are powered externally using a 15-V supply. The high-side gate drivers are powered up using a bootstrap supply.

6

The UCC5390ECD uses a bipolar 15-V and –8-V power supply for driving the gates of the IGBTs. The low-side gate drivers are powered externally using a 15-V/–8-V single bipolar supply. The standard method for bootstrapping a positive gate voltage cannot be extended to negative voltages without increasing the complexity. Therefore, in this reference design, the three high-side gate drivers are powered externally using three different power supplies.

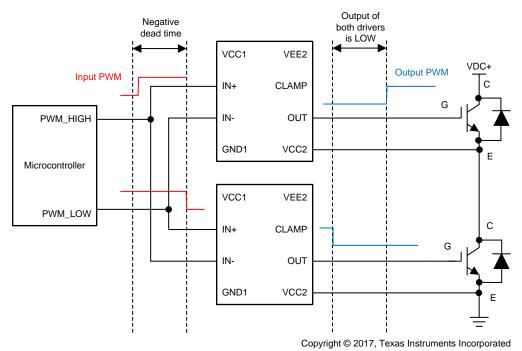

A primary-side 3.3-V supply is derived from the 5-V input through the LDO regulator TLV1117-33. The PWM input signals for the gate drivers are routed to a D-SUB 25-pin female connector, which is connected to the Delfino control card TMDSCNCD28379D through an adapter board. Interlocking is present as an optional protection feature in this design at the input of the gate driver. When single gate drivers are used in half-bridge configuration, they usually allow cross conduction instead of preventing it in case of wrong input signals coming from the controller device. This limitation is due to the fact that each driver does not have the possibility to know the status of the input signal of the other companion driver in the same leg. The availability of two input pins with opposite polarity allows implementing an hardware interlocking that prevents cross conduction even in case of wrong input signals generated by the control unit. This can be achieved by making connections as shown in Figure 5.

Figure 5. Hardware Cross-Connection Prevention Using Interlocking

The output of the gate driver is connected to the gate of the IGBT through an external resistor, which can control the source and sink currents provided by the gate driver.

## 2.2 Highlighted Products

## 2.2.1 UCC5350M and UCC5390E

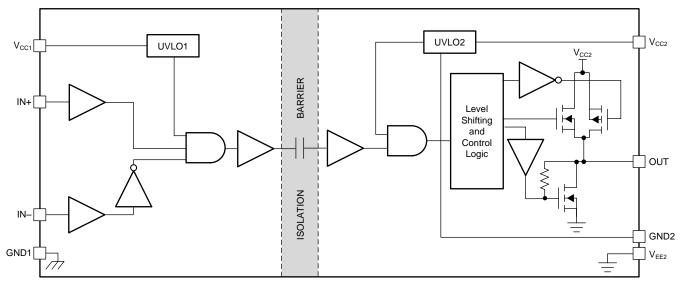

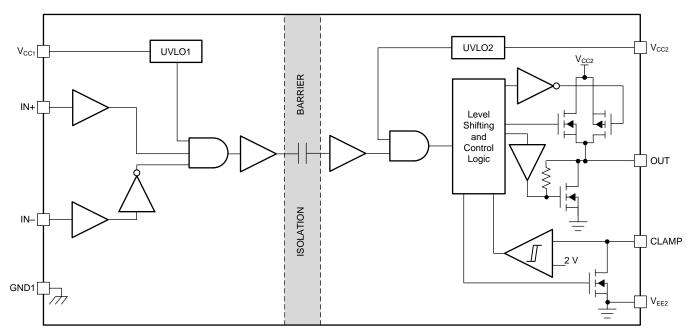

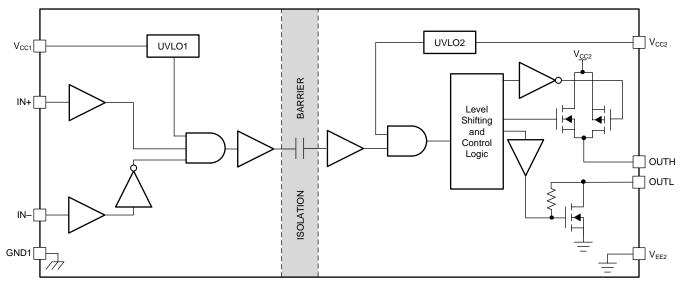

The UCC53xx is a family of compact, single-channel, isolated IGBT, SiC and MOSFET gate drivers with superior isolation ratings and includes variants for pinout configuration, drive strength, and package. The UCC53xxMCD option connects the gate to an internal clamp to prevent false turnon caused by Miller current. The UCC53xxECD option has its UVLO2 referenced to GND2; it is recommended to connect this pin to the IGBT emitter. Compared to an optocoupler, the UCC53xx family has superior insulation voltage, lower power consumption, quiescent current, and CMTI. Figure 6, Figure 7, and Figure 8 show the functional block diagrams of UCC5390ECD and UCC5350MCD. Table 2 shows the drive strength capabilities of different gate drivers.

System Overview

| Table 2. Drive Strength | Capabilities of Different Versions of UCC53xx |

|-------------------------|-----------------------------------------------|

|                         |                                               |

| PART NUMBER | MINIMUM SOURCE AND SINK CURRENT | DESCRIPTION                         |

|-------------|---------------------------------|-------------------------------------|

| UCC5310M    | 2.4 A and 1.1 A                 | Miller clamp                        |

| UCC5320S    | 2.4 A and 2.2 A                 | Split output                        |

| UCC5320E    | 2.4 A and 2.2 A                 | A UVLO with respect to IGBT emitter |

| UCC5350M    | 5 A and 5 A                     | Miller clamp                        |

| UCC5390S    | 10 A and 10 A                   | Split output                        |

| UCC5390E    | 10 A and 10 A                   | A UVLO with respect to IGBT emitter |

Figure 6. Functional Block Diagram of UCC5320E and UCC5390E

Figure 7. Functional Block Diagram of UCC5310M and UCC5350M

Figure 8. Functional Block Diagram of UCC5320S and UCC5390S

## 2.3 System Design Theory

## 2.3.1 DC to Three-Phase AC Inverter Subsystem

In this reference design, IGBT module CM100TX-24S is used to characterize the UCC5350MCD. The CM100TX-24S is a 1200-V, 100-A IGBT module that has an internal gate resistance of 0  $\Omega$ , which allows direct measurement of the Miller induced gate voltage by measuring the voltage drop across the external gate resistor. The IGBT module 6MI180VB-120-50 is used with the UCC5390ECD to convert the DC bus voltage into a three-phase AC. The 6MI180VB-120-50 is a 1200-V, 180-A IGBT with a gate charge of 1500 nC. The typical source/sink currents that can be provided by the UCC5390ECD is 17 A, which can quickly charge the input capacitance of the IGBT.

A schematic of the three-phase inverter stage is shown in Figure 9.

Copyright © 2017, Texas Instruments Incorporated

Figure 9. Schematic of DC to Three-Phase AC Inverter

9

#### System Overview

www.ti.com

R20, R32, R112, R12, R38, and R26 are 10-k $\Omega$  resistors used to ensure that the IGBTs remain off in case the gate drivers get disconnected due to system malfunction. C72 to C77 are provisions for additional external gate-to-emitter capacitance. R118 and R120 are shunt resistors used for U- and W-phase current sensing. Terminal block J8 is the DC bus voltage input connector. C112 and C111 are localized highfrequency DC bus decoupling capacitors. This reference design uses 3- $\mu$ F, 1300-V film capacitors. XF2 and XF1 are fuse holders. A 30-A, 1-kV DC cartridge fuse with dimensions of 10.3 mm × 38 mm must be placed within the fuse holders. To facilitate the discharge, bleeder resistors R45, R48, R49, R50, R51, R54, and R57 are added across the DC link capacitors. Provision is given to connect brake resistor to the DC bus. In case of motor regeneration, if the DC bus voltage goes above a specified threshold, the brake chopper can be initiated. J3 is the terminal block used to connect the braking resistor. D9 is the freewheeling diode connected across the braking resistor to prevent overshoots at the collector of brake chopping IGBT power switch Q1.

## 2.3.2 Gate Driver Power Supply

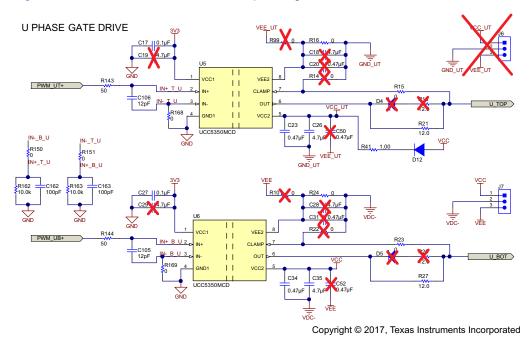

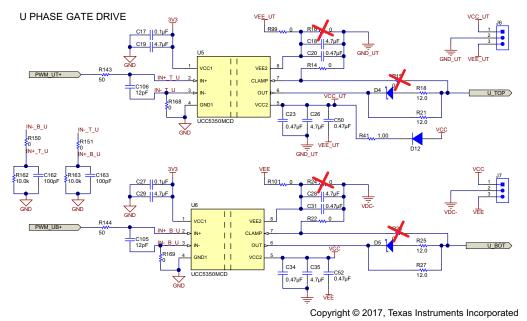

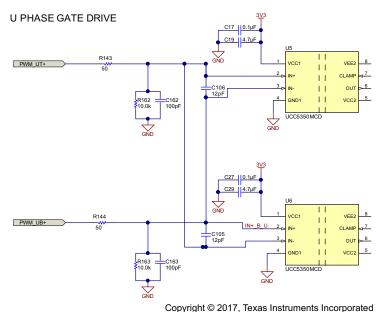

VCC1 and GND1 are the supply pins for the input side of the UCC53xx. The supply voltage at VCC1 can range from 3 to 15 V with respect to GND1, thus supporting the direct interface to 3.3-V low-power controllers as well as legacy 5-V controllers. A 4.7- $\mu$ F bulk capacitor C1 is placed close to the IC power supply to provide a stable supply to the primary side of the gate driver. VCC2 and VEE2 are the supply pins for the output side of the UCC5350MCD. A positive V<sub>GE</sub> of typically 15 V is required to switch the IGBT well into saturation. In this reference design, VCC2 is fed with external 15 V for the low-side gate driver to ensure that IGBT is in full saturation. A bootstrap supply is used to power up the high-side gate driver. Figure 10 shows the schematic of the U-phase gate driver, UCC5350MCD.

Figure 10. Schematic of Gate Driver UCC5350MCD

The UCC5390ECD has three power pins on the secondary side: VEE2, VCC2, and GND2. VEE2 is the supply return for the output driver and GND2 is the reference for the logic circuitry. The supply voltage at VCC2 can range from 13.2 V up to 33 V with respect to VEE2. In this reference design, a bipolar supply of 15 V/–8 V is used to power the UCC5390ECD. Figure 11 shows the schematic of the U-phase gate driver, UCC5350ECD.

Figure 11. Schematic of Gate Driver UCC5390ECD

#### 2.3.3 Designing IN+/IN– Input Filter and Interlocking

A small input RIN-CIN filter can be used to filter out the ringing introduced by non-ideal layout or long PCB traces. Such a filter must use an RIN in the range of 0 to 100  $\Omega$  and a CIN from 10 to 100 pF. In this reference design, an RIN = 50  $\Omega$  and a CIN = 12 pF are selected. When selecting these components, pay attention to the trade-off between good noise immunity and propagation delay.

This reference design also features interlocking between the top and the bottom IGBT gate drivers as shown in Figure 12, so that the positive deadband at the input is converted into negative deadband at the output. This safety feature ensures that the high-side and low-side IGBTs do not turn on at the same time. A parallel RC circuit with R = 10k and C = 100 pF is used at the input pin IN+ and IN– of the gate driver to avoid the gate driver from going into an unknown state.

Figure 12. Schematic of Interlocking Feature

#### 2.3.4 Source and Sink Currents of Gate Driver

To turn on IGBTs and FETs, an initial source peak current must be injected into the gate (up to several amps for larger power devices), and then a holding voltage is required to keep the device on. To turn off, a similar peak sink current opposite the polarity current is required to discharge the gate capacitance, and then a zero or (preferably) negative holding voltage is required to keep the device off.

The source and sink currents of the gate drivers can be controlled by the external gate resistor as shown in Equation 1:

Peak Gate Current

$$(I_G) = \frac{V_{G(on)} - V_{G(off)}}{R_G + R_{G(int)}}$$

(1)

## 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Required Hardware

## 3.1.1 PCB Overview

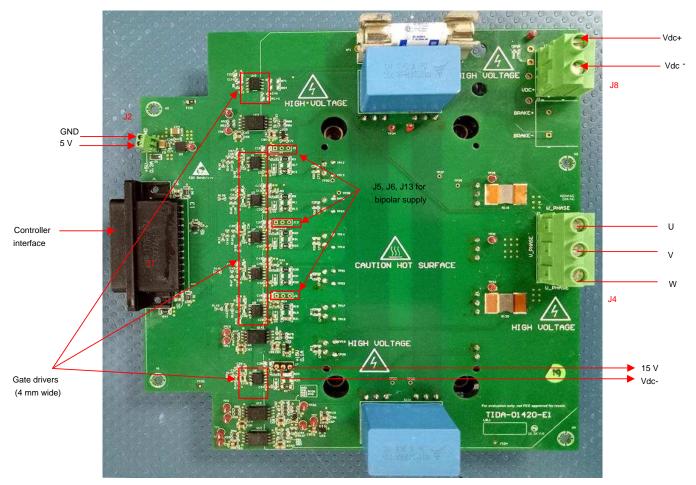

Figure 13 shows the top view of the PCB. The DC bus input connector J8 and the three-phase motor output connector J4 are indicated. Provision is given to add a connector J3 for connecting an external brake resistor to the DC bus. J1 is a female 25-pin D-SUB connector for interfacing to the controller. The primary-side 5-V power supply is connected to J2, and the secondary side isolated 15-V power supply is connected to J7. For giving bipolar supply as is required for the UCC5390ECD, connectors J5, J6, and J13 are provided to supply the top three gate drivers with 15 V/–8 V and ground connection. For giving a unipolar supply for the UCC5350MCD, J5, J6, and J13 can be disconnected or left open.

Figure 13. Top View of TIDA-01420 Board

Figure 14 indicates the primary low-voltage side, the secondary high-voltage side, and the basic isolation barrier in between.

Figure 14. Primary Side, Secondary Side, and Basic Isolation Barrier

sense

#### Hardware, Software, Testing Requirements, and Test Results

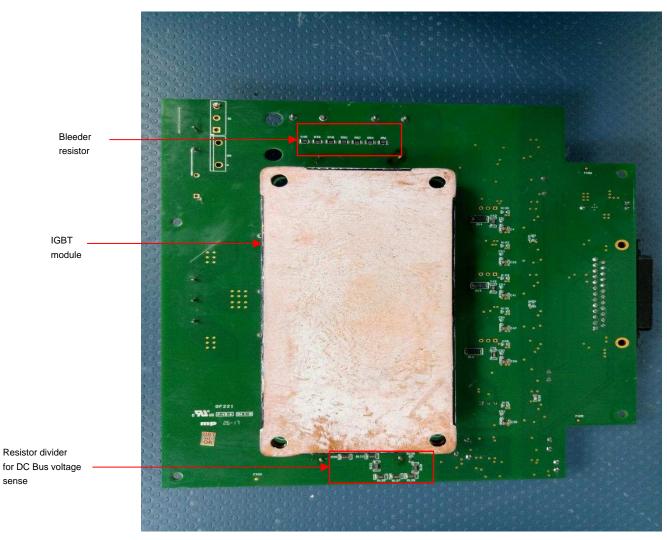

Figure 15 shows the bottom view of the PCB. Provision is given for adding brake chopper IGBT Q1 and freewheeling diode D9. The pad of the IGBT module must be connected to a heat sink. The thermal compound must be used between the pad and the heat sink, and the module must be rigidly screwed to the heat sink. Choose an appropriate heat sink based on the maximum continuous power to be dissipated.

Figure 15. Bottom View of TIDA-01420 Board

## 3.1.2 Controller Interface Connector

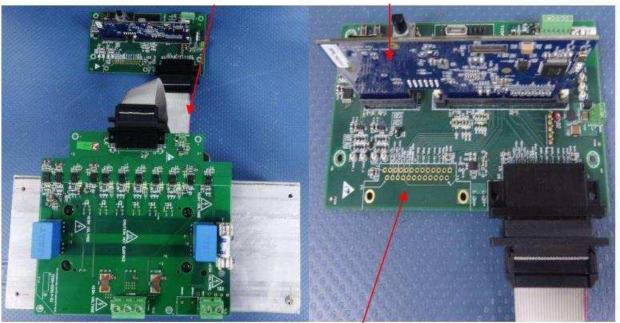

The Delfino control card is connected to J1 on the TIDA-001420 board through an adaptor PCB as shown in Figure 16. A ribbon cable is used to connect the two. The pin functions are described in Table 3.

Interfaced together with ribbon cable

TMDSCNCD28379D Delfino Control Card

Adapter PCB

Figure 16. Interface of TIDA-01420 Board With Control Card

Hardware, Software, Testing Requirements, and Test Results

## Table 3. Connector Pin Description

| PIN NUMBER | PIN NAME   | I/O          | DESCRIPTION                                                    |

|------------|------------|--------------|----------------------------------------------------------------|

| 1          | 5V0        | Power        | 5-V input to the primary side of the power stage               |

| 2          | PWM_UB+    | 3.3-V input  | Phase U low-side gate driver PWM input                         |

| 3          | PWM_UT+    | 3.3-V input  | Phase U high-side gate driver PWM input                        |

| 4          | PWM_VB+    | 3.3-V input  | Phase V low-side gate driver PWM input                         |

| 5          | PWM_VT+    | 3.3-V input  | Phase V high-side gate driver PWM input                        |

| 6          | PWM_WB+    | 3.3-V input  | Phase W low-side gate driver PWM input                         |

| 7          | PWM_WT+    | 3.3-V input  | Phase W high-side gate driver PWM input                        |

| 8          | PWM_BRAKE+ | 3.3-V input  | PWM input to brake IGBT gate driver                            |

| 9          | NC         | NA           | N/A                                                            |

| 10         | MDATA_U    | 3.3-V output | U phase current measurement data from $\Delta\Sigma$ modulator |

| 11         | NC         | NA           | N/A                                                            |

| 12         | MDATA_W    | 3.3-V output | W phase current measurement data from $\Delta\Sigma$ modulator |

| 13         | 5V0        | Power        | 5-V input to the primary side of the power stage               |

| 14         | GND        | Power        | Primary-side ground                                            |

| 15         | GND        | Power        | Primary-side ground                                            |

| 16         | GND        | Power        | Primary-side ground                                            |

| 17         | GND        | Power        | Primary-side ground                                            |

| 18         | GND        | Power        | Primary-side ground                                            |

| 19         | GND        | Power        | Primary-side ground                                            |

| 20         | GND        | Power        | Primary-side ground                                            |

| 21         | NC         | NA           | N/A                                                            |

| 22         | CLK        | 3.3-V input  | Clock input to TIDA-01420 from the control card                |

| 23         | MDATA_VDC  | 3.3-V output | DC bus voltage measurement data from $\Delta\Sigma$ modulator  |

| 24         | MDATA_TMP  | 3.3-V output | Temperature measurement data from $\Delta\Sigma$ modulator     |

| 25         | GND        | Power        | Primary-side ground                                            |

## 3.2 Testing and Results

## 3.2.1 Test Setup

The focus of the tests is to evaluate the functionality and performance of the basic isolated gate drivers UCC5350MCD and UCC5390ECD. The IGBT used for testing UCC5350MCD is CM100TX-24S whereas the IGBT used for testing UCC5390ECD is 6MI180VB-120-50.

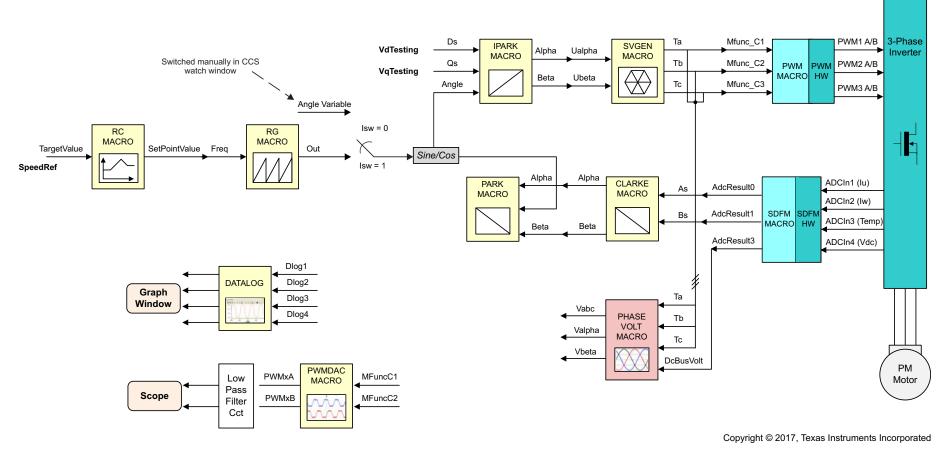

#### 3.2.2 Software

This reference design is tested using software modified from the application report Sensorless Field Oriented Control of 3-Phase Permanent Magnet Synchronous Motors Using TMS320F2833x. The incremental build level 2 shown in Figure 17 is modified. A switch is added to connect either the OUT signal coming from the RG MACRO or the angle variable to the sine cos block. Connecting OUT enables the design to pump sinusoidal current into the motor. Connecting the angle variable, which is made zero, enables driving DC current into the motor

Figure 17. PWM Control and Current Sense Software

## 3.2.3 Test Results for UCC5350MCD

## 3.2.3.1 UVLO Protection

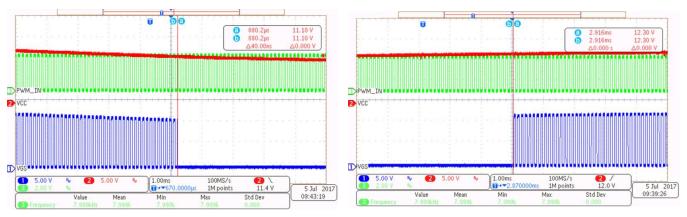

Figure 18 shows the UVLO protection feature of the gate driver. The IGBT is turned off if the secondary side supply voltage of the UCC5350MCD, VCC2, drops below 11.10 V irrespective of IN+, IN– RST until VCC2 goes above 12.30 V.

Figure 18. UVLO Protection Feature of UCC5350MCD Gate Driver

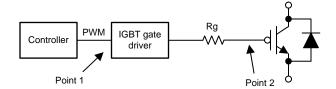

## 3.2.3.2 Propagation Delay

Figure 19 shows the line diagram where the measurements are taken for the propagation delay.

Figure 19. Propagation Delay Measurement Points

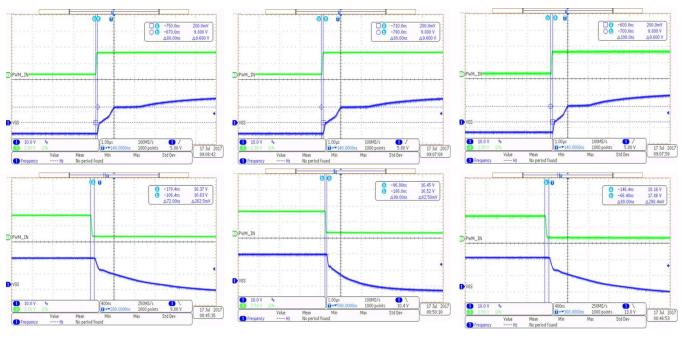

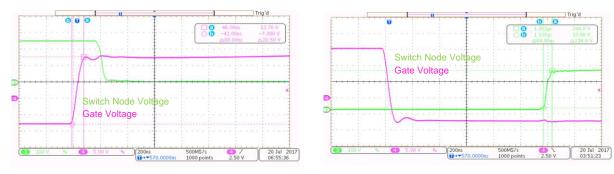

Figure 20 shows the propagation delays measured for the three low-side gate drivers at rising and falling edges for the UCC5350MCD. Table 4 lists down the propagation delays of the bottom gate drivers. For these figures, the green waveform is the probing point 1, and the blue waveform is the probing point 2. Table 4 summarizes the test results of propagation delay.

| PARAMETER              | U2    | U4    | U6    |

|------------------------|-------|-------|-------|

| Rising edge (turnon)   | 70 ns | 60 ns | 70 ns |

| Falling edge (turnoff) | 60 ns | 60 ns | 50 ns |

Note that the maximum skew between the propagation delay is 10 ns. Low propagation delay allows the design to achieve high switching speeds.

Figure 20. Propagation Delay of Bottom Gate Drivers (UCC5350MCD)

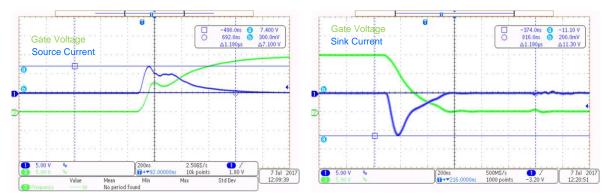

## 3.2.3.3 Source/Sink Currents

The source and sink current waveforms have been captured for the bottom IGBTs by measuring the voltage drop across the gate resistors. Figure 21 shows the source and sink currents provided by the UCC5350MCD for charging the gate of the IGBT at DC bus voltage of 565 V. The external gate resistor used in this case is 12  $\Omega$ , which is in accordance to the recommendation specified in the IGBT datasheet.

Figure 21. Source and Sink Currents With IGBT Module at DC Bus Voltage of 565 V With UCC5350MCD

Source Current =

$$\frac{\text{Voltage drop across external resistor during IGBT turnon}}{\text{Value of external resistor}} = \frac{7.1 \text{ V}}{12 \Omega} = 0.591 \text{ A}$$

(2)

Sink Current =  $\frac{\text{Voltage drop across external resistor during IGBT turnoff}}{\text{Value of external resistor}} = \frac{11.3 \text{ V}}{12 \Omega} = 0.941 \text{ A}$  (3)

#### Hardware, Software, Testing Requirements, and Test Results

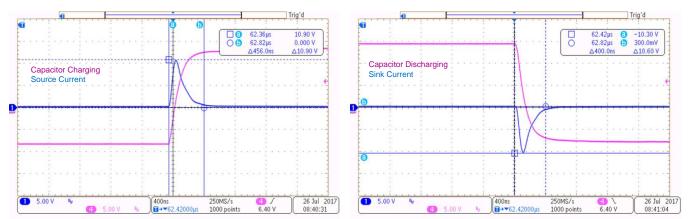

However, the source and sink capabilities of the device is greater than these specified values. The UCC5350MCD can easily drive an IGBT of a high-input capacitance value. This has been verified by replacing the IGBT modules with an external capacitor of 56 nF and measuring the source and sink currents as shown in Figure 22. The value of external gate resistor used for making these measurements is 1  $\Omega$  with the UCC5350MCD. Equation 4. Equation 5 shows the sourcing and sinking capability of gate drivers when the external capacitor is used.

Source Current =

$$\frac{\text{Voltage drop across external resistor during IGBT turnon}}{\text{Value of external resistor}} = \frac{7 \text{ V}}{1.5 \Omega} = 4.67 \text{ A}$$

(4)

Sink Current =  $\frac{\text{Voltage drop across external resistor during IGBT turnoff}}{\text{Value of external resistor}} = \frac{8.2 \text{ V}}{1.5 \Omega} = 5.47 \text{ A}$  (5)

## 3.2.3.4 Turn on and Turn off of IGBT

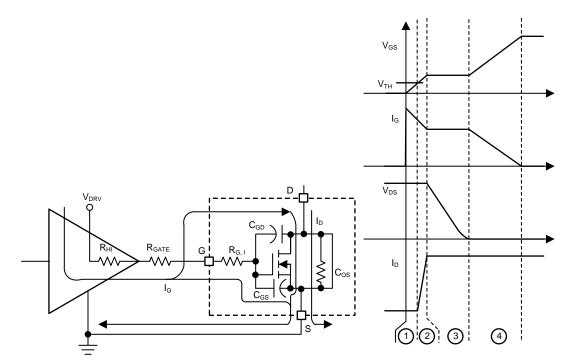

Figure 23 and Figure 24 show the IGBT turnon and turnoff time intervals. A crude estimate of the IGBT charging and discharging times can be calculated using simplified linear approximations of the gate drive current, drain current, and drain voltage waveforms during periods 2 and 3 of the switching transitions.

Equation 6 and Equation 7 show the charging times:

$$lg1 + lg2_on = \frac{V_{DRV} - 0.5 \times V_{Miller}}{R_Total}$$

$$t1 + t2_on = CISS \times \frac{V_{Miller}}{lg1 + lg2}$$

(6)

(7)

Equation 8 and Equation 9 show the discharging times:

$$Ig3\_off = \frac{V_{DRV} - V_{Miller}}{R\_Total}$$

$$t3\_off = CRSS \times \frac{V_{DS,off}}{L}$$

(8)

$$\frac{13}{193}$$

(9)

Hardware, Software, Testing Requirements, and Test Results

Figure 23. IGBT Turnon Time Intervals

Figure 24. IGBT Turnoff Time Intervals

Table 5 shows the theoretical values of turnon and turnoff times currents at DC bus voltage of 250 V and 565 V as calculated from Equation 6 to Equation 9:

Hardware, Software, Testing Requirements, and Test Results

| PARAMETER                   | UCC5350MCD (250 V) | UCC5350MCD (565 V) |

|-----------------------------|--------------------|--------------------|

| R_external                  | 12 Ω               | 12 Ω               |

| R_internal_igbt             | 0 Ω                | 0 Ω                |

| R_on_driver                 | 1.36 Ω             | 1.36 Ω             |

| R_off_driver                | 0.26 Ω             | 0.26 Ω             |

| IGBT module used            | CM100TX-24S        | CM100TX-24S        |

| CISS of IGBT                | 10 nF              | 10 nF              |

| CRSS of IGBT                | 0.1 nF             | 0.06 nF            |

| Supply voltage VCC2         | 15 V               | 15 V               |

| Turnon current (lg1+lg2_on) | 0.823 A            | 0.823 A            |

| Turnoff current (Ig2_off)   | 0.56 A             | 0.56 A             |

| Turnon time (t1+t2_on)      | 98.5 ns            | 98.5 ns            |

| Turnoff time (t2_off)       | 44.64 ns           | 60.53ns            |

## Table 5. Theoretical Values of Turnon and Turnoff Times for UCC5350MCD

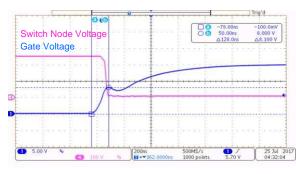

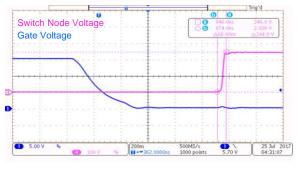

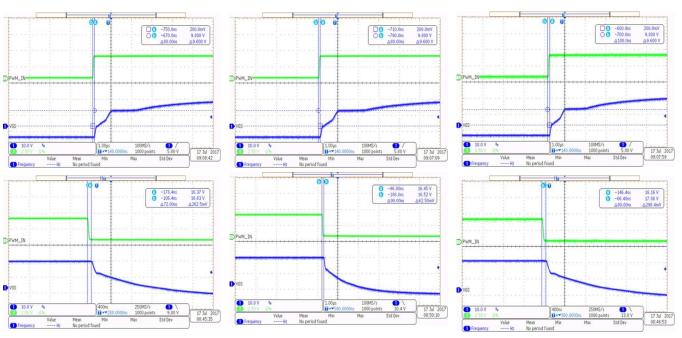

Figure 25 and Figure 26 show the experimental values of the corresponding calculated results for the UCC5350MCD. The experiment is carried out for two different sets of DC Bus voltages, 250 V and 565 V:

Figure 25. Turnon and Turnoff Times of IGBT at 250-V Bus Voltage Using IGBT CM100TX-24S With UCC5350MCD

Figure 26. Turnon and Turnoff Times of IGBT at 565-V Bus Voltage Using IGBT CM100TX-24S With UCC5350MCD

Table 6 summarizes the experimental results as follows:

## Table 6. Experimental Values of Turnon and Turnoff Times of IGBTs

| PARAMETER              | UCC5350MCD (250 V) | UCC5350MCD (565 V) |

|------------------------|--------------------|--------------------|

| IGBT used              | CM100TX-24S        | CM100TX-24S        |

| Turnon time (t1+t2_on) | 128 ns             | 128 ns             |

| Turnoff time (t2_off)  | 66 ns              | 70 ns              |

#### 3.2.3.5 Suppression of Miller Induced Gate Voltage

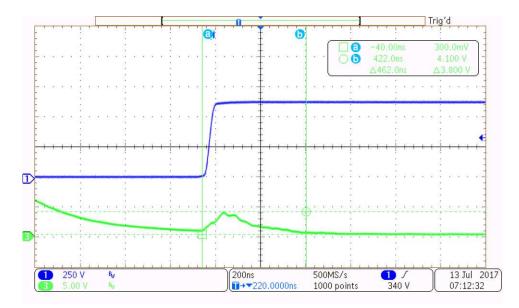

The UCC5350M features an active Miller-clamp function that prevents false turnon of the power switches caused by Miller current in applications where unipolar power supply is used. Figure 27 and Figure 28 show the Miller induced gate voltage when the Miller clamp pin of the UCC5350MCD is disconnected from the circuit.

When  $dV/dt = 4.79 \text{ kV/}\mu\text{s}$ , the induced voltage is 3 V. As dV/dt increases to 8.47 kV/ $\mu$ s, the corresponding induced voltage at the gate goes up to 3.8 V.

Figure 27. Miller Induced Gate Voltage of 3.0 V at dV/dt = 4.79 kV/µs With Miller Pin Disconnected

Figure 28. Miller Induced Gate Voltage of 3.8 V at dV/dt = 8.47 kV/µs With Miller Pin Disconnected

Hardware, Software, Testing Requirements, and Test Results

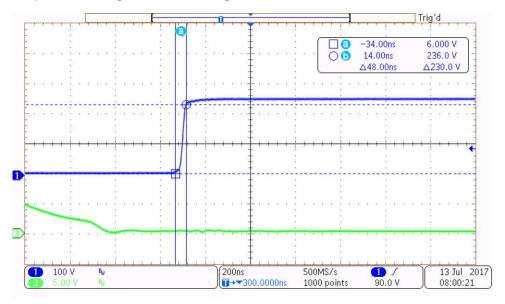

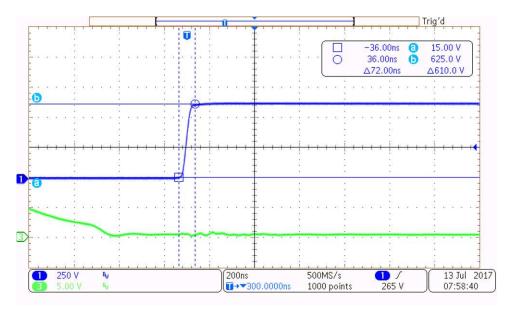

Figure 29 and Figure 30 show the same set of test results when the Miller clamp pin is reconnected to the circuit. The induced voltage is suppressed as the Miller current sinks through the low impedance path between the power switch gate terminal and ground, VEE2.

Figure 29. No Voltage Induced at dV/dt = 4.79 kV/µs With Miller Pin Connected

Table 7 summarizes the test results as follows:

## Table 7. Summary of Miller Induced Gate Voltages at Different dV/dt

| MILLER PIN STATUS | dV/dt MILLER INDUCTED (kV/µs) | GATE VOLTAGE (V) |

|-------------------|-------------------------------|------------------|

| Disconnected      | 4.8                           | 3.0              |

| Connected         | 4.8                           | 0                |

| Disconnected      | 8.5                           | 3.8              |

| Connected         | 8.5                           | 0                |

#### 3.2.3.6 Power Supply Rail for High-Side Gate Drivers (Bootstrap Supply)

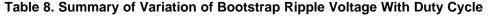

Figure 31 shows the ripple on the bootstrap voltage and the switch node voltage. The bus voltage applied while taking these measurements is 50 V. The bus voltage had to be limited to 50 V during the experiment due to the constraint put by the common-mode rejection ratio of the oscilloscope. The duty cycle of the PWM signal is varied to see the variations in the power supply ripple voltage. Table 8 summarizes the results.

| DUTY CYCLE | RIPPLE VOLTAGE on POWER SUPPLY (mV) |

|------------|-------------------------------------|

| 90%        | 440                                 |

| 50%        | 840                                 |

| 10%        | 1320                                |

Figure 31. Variation of Bootstrap Supply Ripple With Change in Duty Cycle

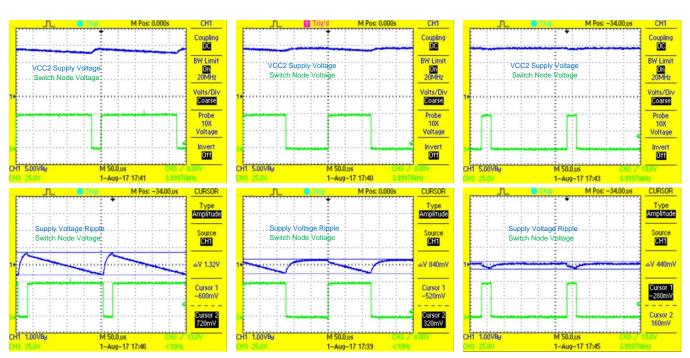

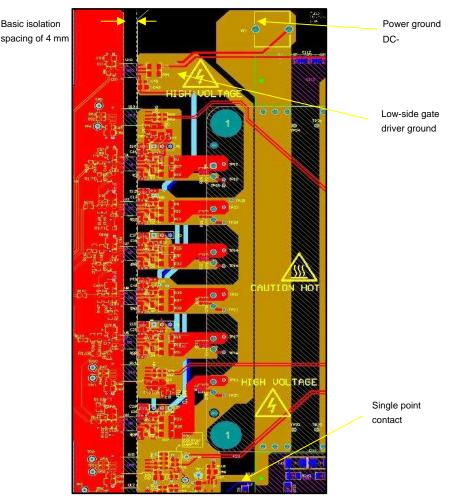

## 3.2.3.7 Interlocking Functioning

This experiment is done by applying a negative deadband (setting both high-side and low-side PWM signals high for a certain time) at the inputs of the gate drivers. Figure 32 shows that because of interlocking, the negative dead time at the input is converted into positive dead band at the output of the gate driver. Thus, this protection feature avoids the possibility of shoot-through.

Figure 32. Interlocking Feature of Design

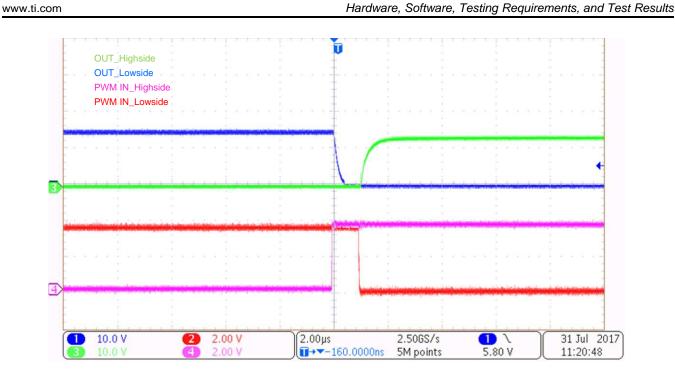

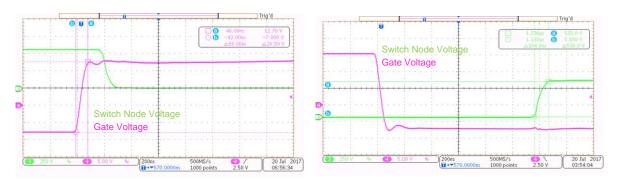

## 3.2.3.8 Thermal Image

Texas

**STRUMENTS**

The thermal image of the board is taken by applying the DC bus voltage of 565 V for a time period of 30 minutes. The switching frequency is kept at 16 kHz. For safety purposes, the board to be tested is kept in a glass chamber and the thermal camera is focused from outside the chamber as shown in Figure 33. For more accurate parameters, see the UCC53x0 datasheet (SLLSER8).

Figure 33. Image of Board Inside High-Voltage Safety Box

Copyright © 2017, Texas Instruments Incorporated

Hardware, Software, Testing Requirements, and Test Results

www.ti.com

Figure 34 shows the thermal image of the boards UCC5350MCD respectively and the corresponding minimum, maximum, and average temperatures. The ambient temperature while making these measurements is 25°C.

Figure 34. Thermal Image of Board With Gate Driver UCC5350MCD

## 3.2.4 Test Results for UCC5390ECD

## 3.2.4.1 UVLO Protection

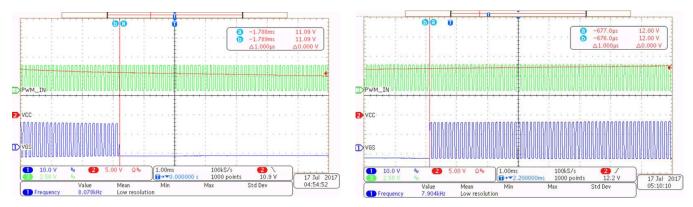

The UCC5390ECD has an external pin for UVLO measurement, which is referenced to ground rather than VEE2. As shown in Figure 35, IGBT is turned off if the secondary side supply voltage of the UCC5390ECD, VCC2, drops below 11.09 V irrespective of IN+, IN– until VCC2 goes above 12 V.

Figure 35. UVLO Protection Feature of UCC5390ECD Gate Driver

## 3.2.4.2 Power Consumption by Gate Drivers

In this experiment, the UCC5390ECD is used to drive the IGBT module, 6MI180VB-120-50. The static power loss,  $P_{GDQ}$  includes quiescent power loss on the driver as well as driver self-power consumption when operating with a certain switching frequency. The power supplied by the gate driver can be calculated by measuring the average current consumed by it as shown in Equation 10.  $P_{GDQ} = VCC1 \times ICC1 + VCC2 \times ICC2 \approx VCC2 \times ICC2$  (10)

Table 9 shows the power supplied to the gate driver at 8- and 16-kHz switching frequencies:

| FREQ<br>SWITCHING | SUPPLY CURRENT (ICC2) | SUPPLY<br>VOLTAGE<br>(VCC2) | POWER SUPPLIED, P <sub>GDQ</sub><br>(3 DRIVERS) | POWER SUPPLIED, P <sub>GDQ</sub><br>(PER GATE DRIVER) |

|-------------------|-----------------------|-----------------------------|-------------------------------------------------|-------------------------------------------------------|

| 8 kHz             | 0.075 A               | 24 V                        | 1.8 W                                           | 0.6 W                                                 |

| 16 kHz            | 0.127 A               | 24 V                        | 3.048 W                                         | 1.016 W                                               |

## Table 9. Power Supplied to Bottom Gate Drivers

The power lost to drive the gate of the IGBT, that is the switching operation loss, can be calculated as follows:

$P_{GSW} = Qg \times Vg \times f_{SW}$

(11)

To compare the switching operation loss with the quiescent power loss,  $P_{GSW}$  is calculated for two different frequencies- (8 kHz and 16 kHz) and is summarized in Table 10:

## Table 10. Power Lost to Gate During Switching

| FREQ SWITCHING (f <sub>sw</sub> ) | Q_g     | V_g  | P <sub>GSW</sub> |

|-----------------------------------|---------|------|------------------|

| 8 kHz                             | 2000 nC | 24 V | 0.348 W          |

| 16 kHz                            | 2000 nc | 24 V | 0.768 W          |

## 3.2.4.3 Propagation Delay

Figure 36 shows the propagation delays measured for the three low-side gate drivers at rising and falling edges for the UCC5390ECD.Table 11 lists the propagation delays of the bottom gate drivers.

## Table 11. Propagation Delay of Bottom Three Gate Drivers (UCC5390ECD)

| PARAMETER              | U2    | U4    | U6     |

|------------------------|-------|-------|--------|

| Rising edge (turnon)   | 80 ns | 80 ns | 100 ns |

| Falling edge (turnoff) | 72 ns | 90 ns | 80 ns  |

#### Hardware, Software, Testing Requirements, and Test Results

www.ti.com

Also note that the maximum skew between the propagation delay is 20 ns.

Figure 36. Propagation Delay of Bottom Gate Drivers (UCC5350ECD)

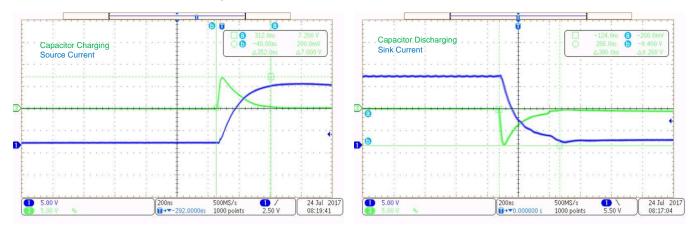

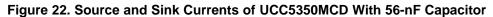

## 3.2.4.4 Source-Sink Currents

As in Section 3.2.3.3, the IGBT module is replaced with an external capacitor of 56 nF and source and sink currents are measured. The value of external gate resistor used for making these measurements is 0.75  $\Omega$ . Figure 37 shows the sourcing and sinking capability of gate drivers when the external capacitor is used.

Source Current =

$$\frac{\text{Voltage drop across external resistor during IGBT turnon}}{\text{Value of external resistor}} = \frac{10.9 \text{ V}}{0.75 \Omega} = 14.53 \text{ A}$$

(12)

Sink Current =  $\frac{\text{Voltage drop across external resistor during IGBT turnoff}}{\text{Value of external resistor}} = \frac{10.6 \text{ V}}{0.75 \Omega} = 14.13 \text{ A}$  (13)

30

## 3.2.4.5 Turnon and Turnoff Times of IGBT

Table 12 shows the theoretical values of turnon and turnoff times.

## Table 12. Theoretical Values of Turnon and Turnoff Times at 565-V Bus Voltage

| PARAMETER                   | UCC5350ECD (250 V) | UCC5350ECD (565 V) |

|-----------------------------|--------------------|--------------------|

| R_external                  | 0 Ω                | 0 Ω                |

| R_internal_igbt             | 3.8 Ω              | 3.8 Ω              |

| R_on_driver                 | 0.714 Ω            | 0.714 Ω            |

| R_off_driver                | 0.13 Ω             | 0.13 Ω             |

| IGBT module used            | 6MI180VB-120-50    | 6MI180VB-120-50    |

| CISS of IGBT                | 29 nF              | 29 nF              |

| CRSS of IGBT                | 0.8 nF             | 0.8 nF             |

| Supply voltage, VCC2        | 15V/-8V            | 15 V/–8 V          |

| Turnon current (Ig1+Ig2_on) | 4.18 A             | 4.18 A             |

| Turnoff current (Ig2_off)   | 3.51 A             | 3.51 A             |

| Turnon time (t1+t2_on)      | 95 ns              | 95 ns              |

| Turnoff time (t2_off)       | 50.8 ns            | 128 ns             |

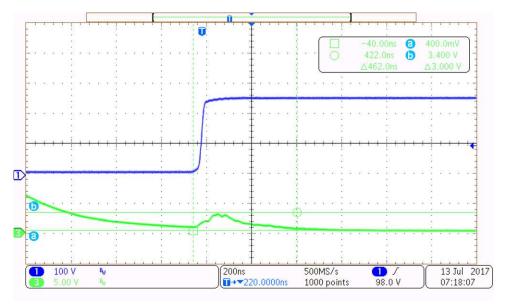

Figure 38 and Figure 39 shows the experimental values of the corresponding calculated results for the UCC5350MCD. The experiment is carried out for two different sets of DC Bus voltages: 250 V and 565 V.

Figure 38. Turnon and Turnoff Times of IGBT at 250-V Bus Voltage Using IGBT 6MI180VB-120-50 With UCC5390ECD

Figure 39. Turnon and Turnoff Times of IGBT at 565-V Bus Voltage Using IGBT 6MI180VB-120-50 With UCC5390ECD

Table 13 summarizes the experimental results as follows:

| PARAMETER              | UCC5390ECD (250 V) | UCC5390ECD (565 V) |

|------------------------|--------------------|--------------------|

| IGBT used              | 6MI180VB-120-50    | 6MI180VB-120-50    |

| Turnon time (t1+t2_on) | 88 ns              | 88 ns              |

| Turnoff time (t2_off)  | 64 ns              | 104 ns             |

| Table 13. Experimental Values of | Turnon and Turnoff | Times of IGBTs |

|----------------------------------|--------------------|----------------|

|----------------------------------|--------------------|----------------|

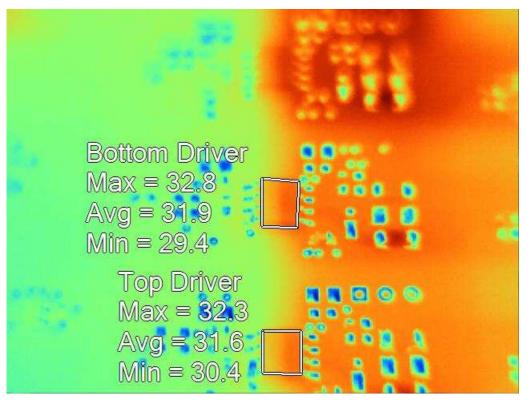

## 3.2.4.6 Thermal Image of Board

Figure 40 shows the thermal image of the boards, UCC5390ECD, and the corresponding minimum, maximum, and average temperatures. The ambient temperature while making these measurements is 25°C.

Figure 40. Thermal Image of Board With Gate Driver UCC5390ECD

## 4 Design Files

## 4.1 Schematics

To download the schematics, see the design files at TIDA-01420 .

## 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01420.

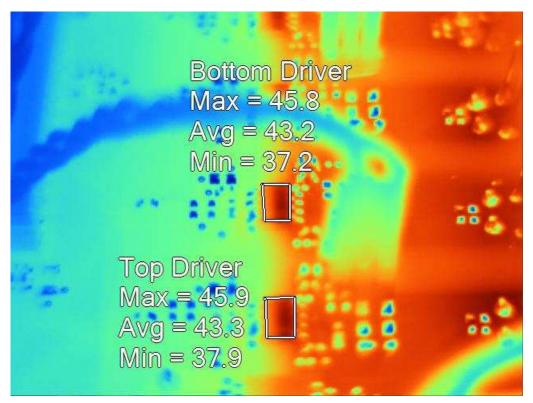

## 4.3 PCB Layout Recommendations

Figure 41 shows the isolation barrier and ground split. The hot-side (high-voltage power side) and the cold-side (low-voltage controller side) copper tracks are separated from each other by a basic isolation barrier. The narrow body package of the gate driver is placed across the isolation barrier. A copper-to-copper creepage spacing of 4 mm is maintained between the hot and cold sides. The low-side gate driver grounds and DC bus negative are common. To avoid noise due to switching currents in the DC bus negative from interfering with the gate driver operation, a split is done in the ground plane and they are connected together at a single point as shown in Figure 41.

Figure 41. Basic Isolation Barrier and Ground Split Layout

#### Design Files

www.ti.com

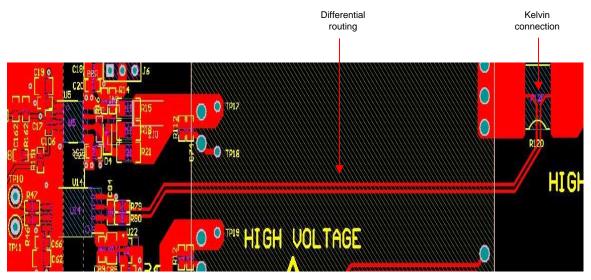

The shunt resistance of 4 m $\Omega$  is in the same range as that of the stray parasitic trace resistances. For accurate shunt-based current sensing, it is important to sense the exact voltage across the shunt resistor only and avoid measuring the drop across the trace and contact parasitic resistance. This is done by implementing a Kelvin connection as shown inFigure 42. Differential routing is done from the shunt resistor to the  $\Delta\Sigma$  modulator. Any noise is common to both the traces and gets cancelled off in the differential input stage of the modulator.

Figure 42. Shunt Resistor Connection to  $\Delta\Sigma$  Modulator Layout

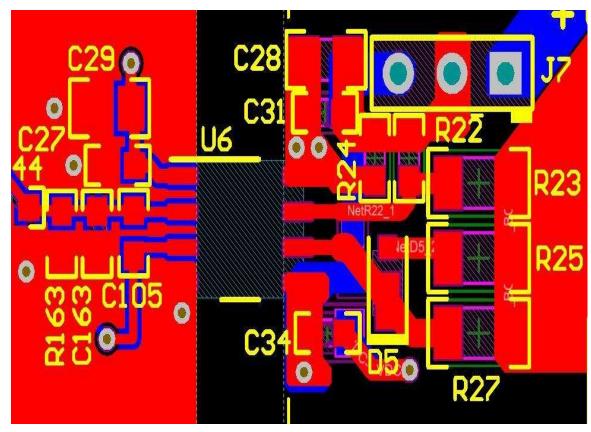

As shown in Figure 43, the primary- and secondary-side noise-decoupling capacitors must be connected close to the device between the VCC1 and GND1 pins and between the VCC2 and VEE2 pins to bypass noise and to support high peak currents when turning on the IGBT. It is essential to limit the high peak currents that charge and discharge the IGBT gates to a minimal physical area. This limitation decreases the loop inductance and minimizes noise on the gate terminals of the IGBTs. The gate driver must be placed as close as possible to the IGBTs. To ensure isolation performance between the primary and secondary side, avoid placing any PCB traces or copper below the driver device.

Figure 43. Low-Side Gate Driver Layout

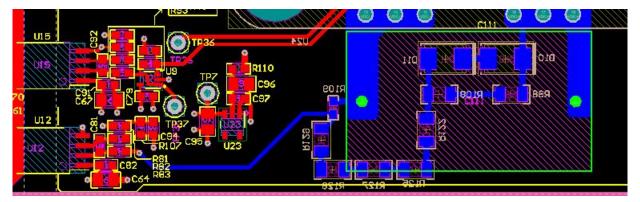

Figure 44 shows the DC bus voltage sense circuit. The high-impedance resistor divider network is connected across the pins of the high-voltage DC-link film capacitor C111. The attenuated voltage is sensed by  $\Delta\Sigma$  modulator U12. It is important to sense the voltage across the film capacitor for low-noise measurement.

Figure 44. Connection of DC Bus Voltage Sensing

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01420.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01420.

35

Design Files

## 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01420.

## 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01420.

## 5 Related Documentation

- 1. Texas Instruments, *Reinforced Isolated Phase Current Sense Reference Design With Small Delta-Sigma Modulators*, TIDA-00914 Design Guide (TIDUD07)

- 2. Texas Instruments, *Isolated Current Shunt and Voltage Measurement Kit*, TIDA-00171 Design Guide (TIDU499)

- 3. Texas Instruments, *Isolated Current Shunt and Voltage Measurement for Motor Drives Using AM437x*, TIDA-00209 Design Guide (TIDU755)

- 4. Texas Instruments, Sensorless Field Oriented Control of 3-Phase Permanent Magnet Synchronous Motors Using TMS320F2833x, Application Report (SPRABQ4)

- 5. Texas Instruments, *Wide-Input Isolated IGBT Gate-Drive Fly-Buck™ Power Supply for Three-Phase Inverters*, TIDA-00199 Design Guide (TIDU670)

- 6. Texas Instruments, *Reference Design for Reinforced Isolation Three-Phase Inverter With Current, Voltage, and Temp Protection,* TIDA-00366 Design Guide (TIDUBX1)

## 5.1 Trademarks

Delfino is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

## 6 Terminology

- **IGBT** Insulated gate bipolar transistor

- **VFD** Variable frequency drive

- PWM— Pulse width modulation

- UVLO— Undervoltage lockout

- **DNP** Do not populate

## 7 About the Authors

**AISHWARYA BHATNAGAR** is a systems engineer at Texas Instruments, where she is responsible for developing reference design solutions for the Motor Drive segment within Industrial Systems. Aishwarya earned her bachelor of technology in electronics and communication engineering from MNNIT, Allahabad.

**MARTIN STAEBLER** is a system architect in the Industrial Systems-Motor Drive team at Texas Instruments, responsible for specifying reference designs for industrial drives.

## 7.1 Recognition

The authors would like to recognize the excellent contributions from **PAWAN NAYAK** and **NELSON ALEXANDER** during the design, test, and documentation phases of the TIDA-01420 reference design.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated