# TI Designs: TIDA-01610 Automotive Tracking Power Supply Reference Design for **Audio Amplifiers**

# **TEXAS INSTRUMENTS**

#### Description

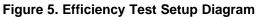

This reference design implements a 10-A, two-phase boost converter with an adjustable output voltage that can be dynamically set for voltages from 16-V to 40-V DC. The output voltage range allows tracking an audio signal when provided by either a PWM signal or a voltage.

#### Resources

TIDA-01610 LM25122-Q1

5

**Design Folder** Product Folder

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

• 10-A Continuous Output

PWM or DC Control of Output Voltage

Output Voltage Range: 16 V to 40 V

Input Voltage Range: 9 V to 16 V

Allows Adjustment of Audio Amplifier Power Supply to Match Signal Conditions

#### Applications

Features

•

•

Automotive External Amplifier

Copyright © 2018, Texas Instruments Incorporated

2

#### 1 System Description

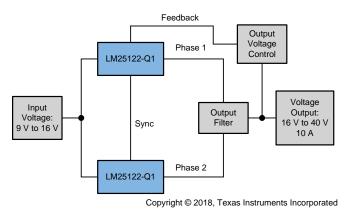

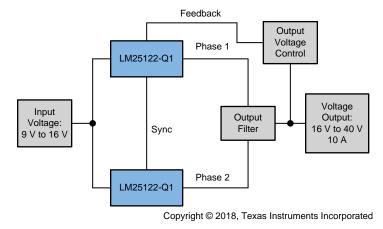

This reference design is a dual-phase boost using the LM25112-Q1 boost controller for automotive audio applications. This design can operate from 9 V to 16 V. The design has an adjustable output of 16 V to 40 V and is capable of sourcing a 10-A continuous current, suitable for powering a power audio amplifier. The LM25112-Q1 boost controller has a bypass function. When  $V_{IN}$  is equal to or greater than the set output voltage, the device will bypass  $V_{IN}$  using the high-side sync FET. Output adjustment is achieved by applying a 3.3-V PWM signal to the adjustment input. Adjusting the duty cycle of the PWM signal from 10% to 90% adjusts the output from 40 V to 16 V, respectively.

This design is also capable of tracking a sine wave up to 500 Hz without distortion and achieves a delay time of less than 300 µs between sine wave and the output voltage. The switching frequency is set to 150 kHz and a four-layer PCB is used. When used with an audio processor system capable of supplying the PWM signal, the reference design can be used to track an audio signal, adjusting the output voltage based on the audio signal conditions. An audio amplifier powered by this circuit can provide high-power output when the boost output voltage is set high. A lower power supply voltage is used when less volume is required, allowing the audio amplifier to dissipate less heat than it would if the boost supply was left set to the maximum voltage.

#### 1.1 Key System Specifications

| PARAMETER                | SPECIFICATIONS                             |

|--------------------------|--------------------------------------------|

| Input voltage            | 9-V to 16-V DC                             |

| Output voltage           | 16-V to 40-V DC                            |

| Output current           | 10 A                                       |

| Tracking input voltage   | 0 V min, 3.3 V max                         |

|                          | 0.33 V to 3 V to meet output voltage range |

| Tracking input frequency | 500 Hz, max                                |

| Tracking PWM frequency   | 100 kHz, minimum                           |

#### **Table 1. Key System Specifications**

### 2 System Overview

### 2.1 Block Diagram

System Overview

Figure 1. TIDA-01610 Block Diagram

#### 2.2 Highlighted Products

#### 2.2.1 LM25122-Q1 Wide-Input Synchronous Boost Controller With Multiple Phase Capability

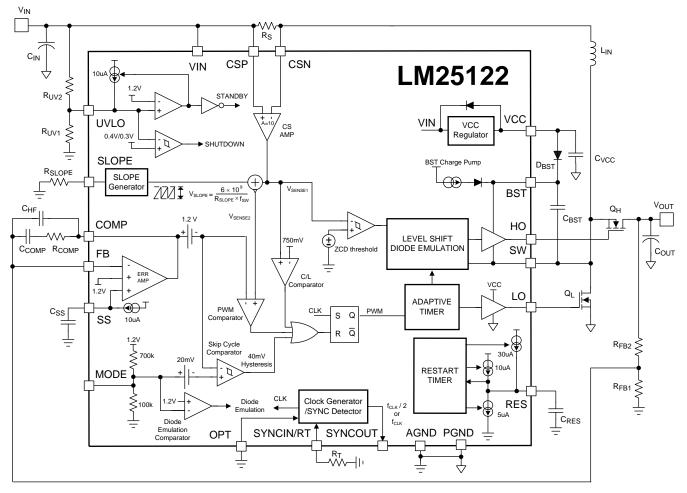

The LM25122 is a multiphase capable synchronous boost controller intended for high-efficiency synchronous boost regulator applications. The control method is based upon peak current mode control.

Current mode control provides inherent line feedforward, cycle-by-cycle current limiting and ease of loop compensation.

The switching frequency is programmable up to 600 kHz. Higher efficiency is achieved by two robust Nchannel MOSFET gate drivers with adaptive dead-time control. A user-selectable diode emulation mode also enables discontinuous mode operation for improved efficiency at light load conditions.

An internal charge pump allows 100% duty cycle for high-side synchronous switch (bypass operation). A 180° phase shifted clock output enables easy multiphase interleaved configuration. Additional features include thermal shutdown, frequency synchronization, hiccup mode current limit and adjustable line undervoltage lockout.

Copyright © 2016, Texas Instruments Incorporated

Figure 2. LM25122-Q1 Block Diagram

System Overview

# 2.3 System Design Theory

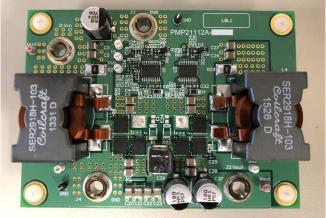

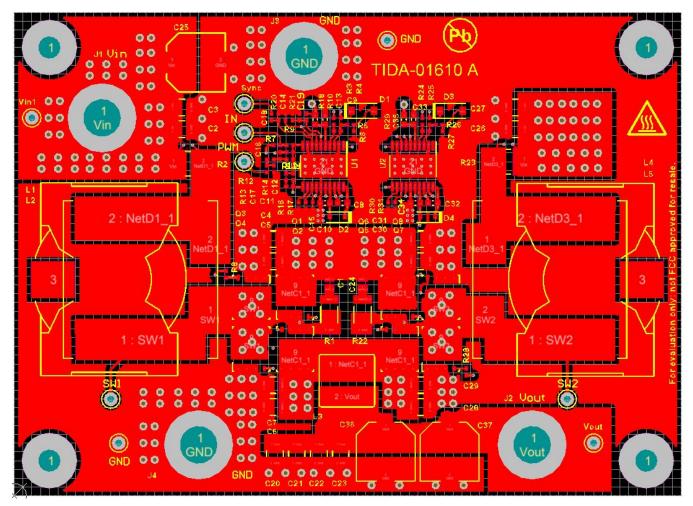

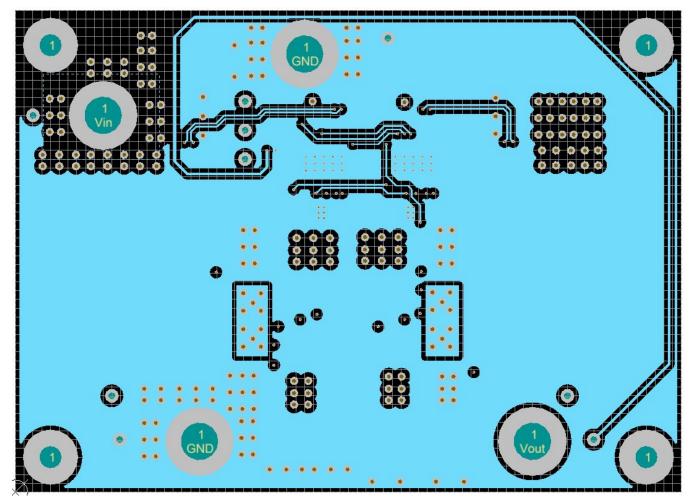

Figure 3. PCB Top View

#### System Overview

www.ti.com

#### 2.3.1 Boost Design

Copyright © 2017, Texas Instruments Incorporated

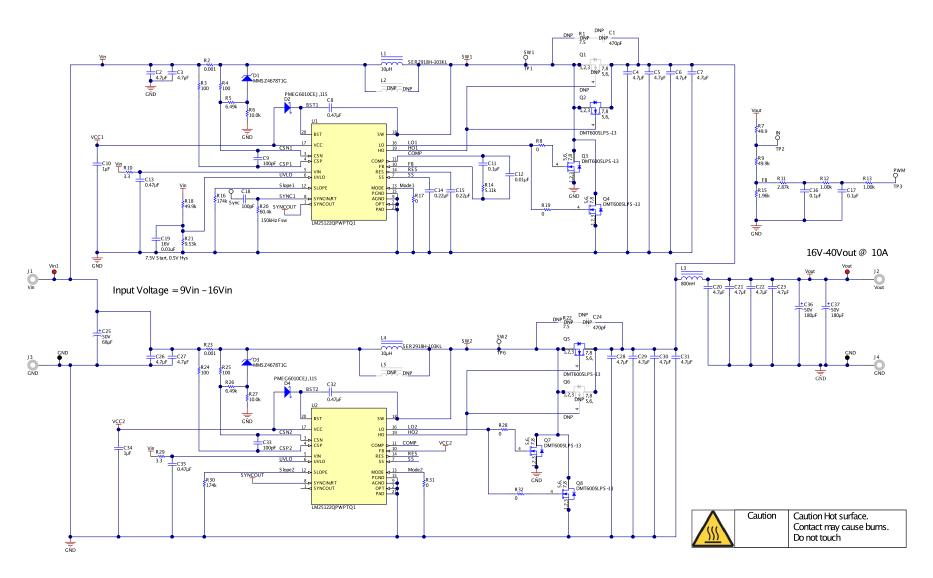

#### Figure 4. TIDA-01610 Schematic

To ensure a continuous 10-A delivery to the load, a two-phase boost topology is used for this reference design. A two-phase implementation allows reduction in the size of filter capacitors and inductors while simultaneously lowering power dissipation in the main boost switch transistor. The filter inductor can shrink because the average current is divided between two inductors. The LM25122-Q1 is ideal for this design because it provides SYNCOUT and SYNC in pins for use in creating multi-phase designs. In the reference design, U1 provides the master timing to U2. The feedback pin on U2 is tied to U2's VCC input to set the device for slave operation. Other than the interconnection for synchronization, the circuits around U1 and U2 are identical. The undervoltage lockout (UVLO) and compensation network are shared by the two boost circuits.

Each phase is designed as a 5-A output boost. The designer must make trade-offs because the voltage can be set anywhere in the range of 16 V to 40 V. The same constraints apply to both phases.

The switching frequency is set for 150 kHz by R20. The frequency setting and load requirements determine the necessary filter component values for inductance and total capacitance. 150 kHz is chosen to ensure minimum switching losses and heat dissipation. The value of inductors L1 and L4 is 10  $\mu$ H. The peak inductor current is almost 26 A, so the inductor must have a high current rating. Large inductor ripple current results in large core loss in the inductor. The selected inductance provides a 20% to 30% inductor ripple current ratio to the average inductor current across entire input and output operating voltages with a 10-A load current. The selected SER2918H-103 is suitable for high-power applications like this design. The SER2918H-103 has DCR to reduce DC loss. Its core design reduces core loss.

Ceramic capacitors are chosen for the input and output filters closest to U1. C25, C2, C3, C26, and C27 are the input capacitors. The input capacitors in a boost topology see continuous current. Therefore, the input capacitor's RMS current is low. The worst case RMS current in the input capacitors is 2.6 A, so a single electrolytic capacitor with moderate ESR in addition to four ceramic capacitors ensures proper RMS current split as well as damping some amount of wiring inductance from the supply. C25 is shared by both boost phases.

The output capacitors in a boost topology see discontinuous, pulsating current. The worst case RMS current in the output capacitor is 20 A. One job of the output capacitors is to maintain the output voltage in a load transient event. A second stage filter is added to attenuate the RMS current going into the large value electrolytic capacitors at the final output. This filter is necessary because the DC voltage of a ceramic capacitor must be derated and because the boost topology has a slow loop response due to the presence of a right-half-plane zero in the boost transfer function. In this reference design, C4 through C7 are the first stage output capacitors in the U1 phase, and C28 through C31 are the output capacitors for the second phase. These are all 4.7- $\mu$ F, 80-V capacitors. The high voltage rating ensures the total capacitance value does not drop significantly when the output is set to 40 V. The second low-pass filter consists of L3, C20 through C23, C36, and C37.

The switch and synchronous rectifier transistors chosen are automotive rated and have low  $R_{DS(on)}$ . Due to the high peak current, two transistors are paralleled to reduce heat dissipation in the switch transistors. The synchronous rectifier does not dissipate as much power, so only one transistor is needed; however, this reference design provides enough space for two.

The output voltage can track a 500-Hz sine wave signal with little distortion. Consequently, the LM25122-Q1 has to charge and discharge the output capacitors from 16 V to 40 V then back to 16 V at a rate of 500 Hz. During the discharging event, the synchronous FET is discharging current from the output and returning the current back to the input, which creates a negative voltage across the current sense amplifier. The differential current sense amplifier on the LM25122-Q1 does not support negative current sense. Therefore, a level shift circuit must be implemented to bias the no-load current sense value to the middle of the dynamic range. The bias circuit consists of D1, R5, and R6 in phase 1 and D3, R26, and R27 in phase 2. This implementation allows the amplifier to transition between the current limit threshold and zero, which ensures regulation during a tracking event. Due to the level shift implementation, a  $1-m\Omega$ current sense resistor is used to ensure full load delivery of the charging current during the tracking event.

The operation mode is set for diode emulation mode by tying U1, pin 13 to ground through R17. In FPWM mode, with a pre-biased output at no load, a large reverse current upon start-up is potentially destructive. Selecting diode emulation mode prevents potential large reverse currents. The offset provided to the current sense amplifier forces continuous conduction mode during all conditions of operation, even with the mode pin set to diode emulation mode.

8

www.ti.com

UVLO is set so the regulator starts operating when the input voltage is above 7.5 V. The input voltage is filtered by R10 and C13. R10 provides U1's  $V_{IN}$  connection with some isolation from the switching transients on  $V_{IN}$ .

#### 2.3.2 Tracking Control

The tracking control circuit is part of the output voltage feedback network for the power supply. The tracking control point is TP3, which is also labeled PWM on the schematic. Resistors R7, R9, and R15 form the normal part of the output voltage feedback network. Resistors R11, R12, and R13 along with capacitors C16 and C17 form an input filter for the PWM signal. R13, C17, R12, and C16 form a low-pass filter that filters a PWM signal. The PWM signal need not be PWM. This signal can also be a sine wave of 500 Hz or less, or a DC voltage can be applied to control the boost output voltage.

The boost regulator drives the output voltage to maintain 1.2 V at the feedback pin on U1. Changing the voltage at TP3 can therefore control the output voltage.  $V_{OUT}$  is inversely proportional to the voltage at TP3. The PWM input design works with a 3.3-V PWM output from a microprocessor. The resistor values of the PWM input network are chosen so the boost regulator provides a 40-V output when a 3.3-V PWM signal with a 10% duty cycle is present. If the PWM signal has a 90% duty cycle, the boost output is 16 V.

The PWM signal must be at least 100 kHz. Otherwise, the filter network cannot filter the noise from the PWM signal well and the noise will appear in the output of the boost converter. If the values of C16 and C17 are increased, more filtering would be provided to the control signal. However, it would take longer for the boost output voltage to respond to changes in the control signal, which lowers the frequency that the power supply output responds to. In an actual system, the control signal varies based on the level, or volume, setting of an audio signal.

# 3 Hardware Setup, Testing Requirements, and Test Results

### 3.1 Hardware Setup

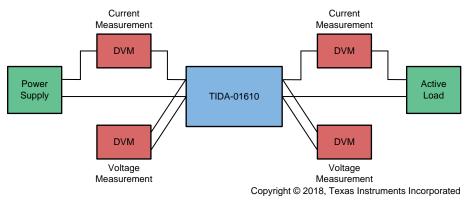

In addition to the setup defined in Figure 5, three 6.8-mF, 65-V rated electrolytic capacitors are used to damp the wiring inductance of the input supply for all test data taken on this design guide.

# 3.2 Testing and Results

#### 3.2.1 Test Setup

Figure 5 shows the setup for the efficiency test.

# 3.2.2 Test Results

#### 3.2.2.1 Efficiency

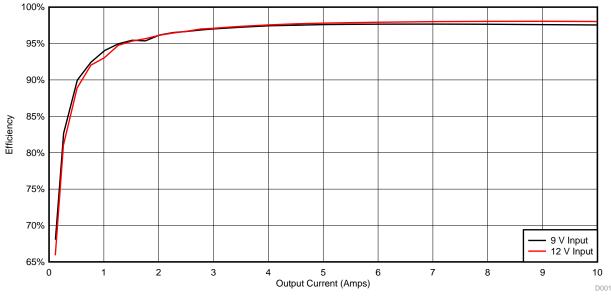

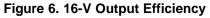

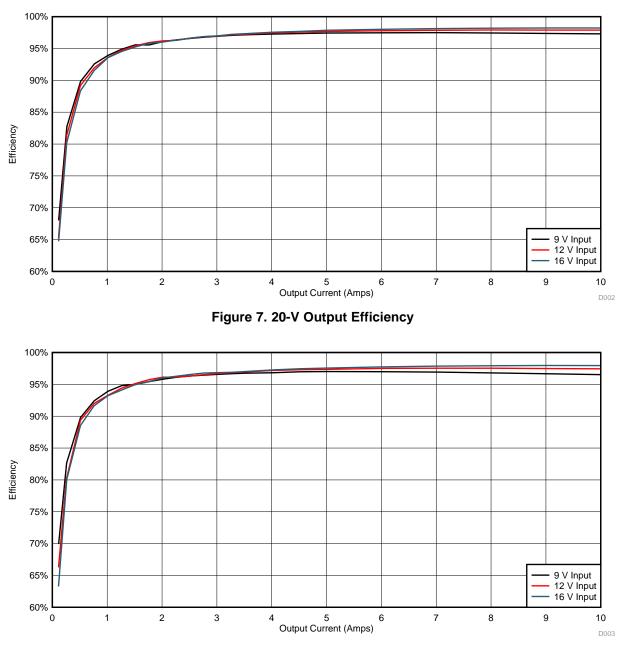

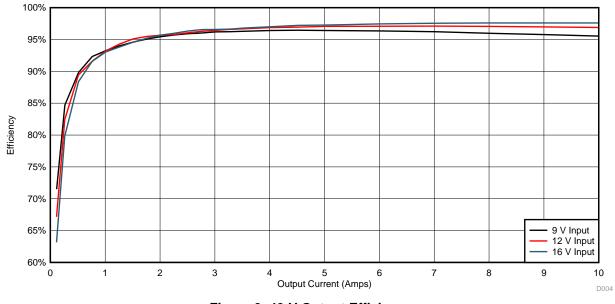

The power output efficiency is plotted in Figure 6, Figure 7, Figure 8, and Figure 9. In all cases, the efficiency is above 90% for loads above 0.5 A and above 95% for loads above 2 A.

Figure 8. 30-V Output Efficiency

Figure 9. 40-V Output Efficiency

### 3.2.2.2 Switching Waveforms and Output Ripple

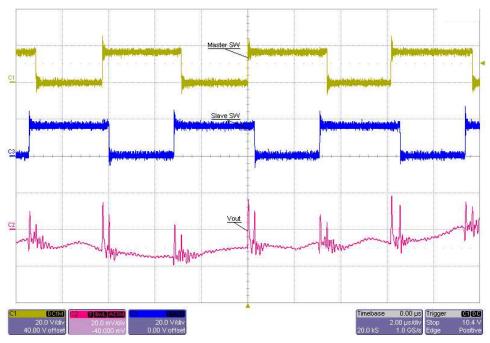

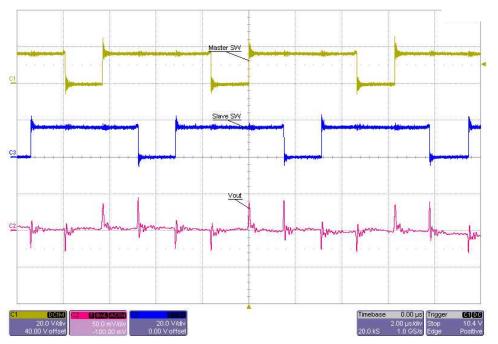

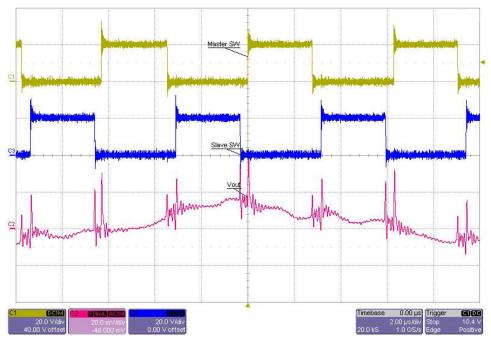

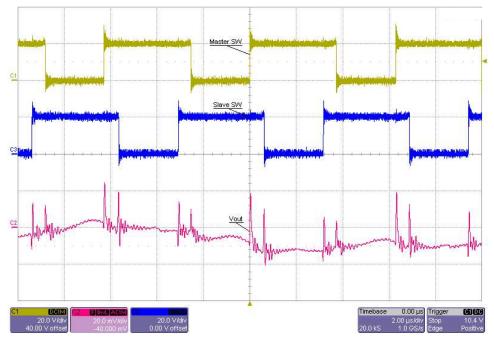

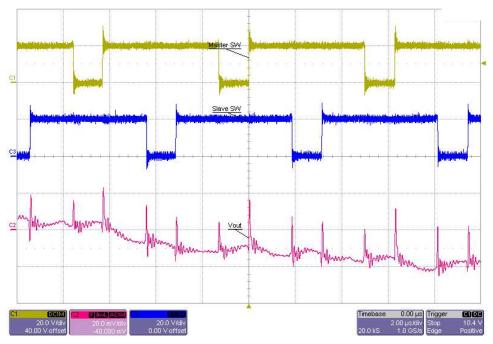

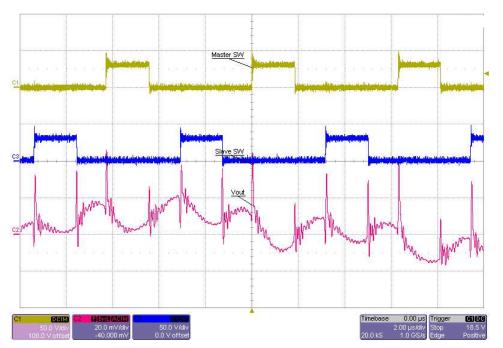

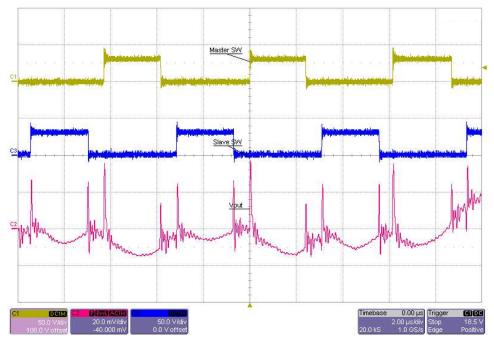

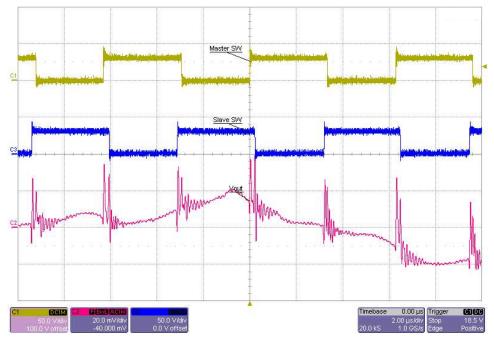

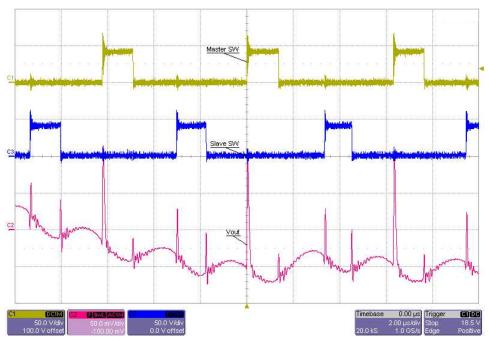

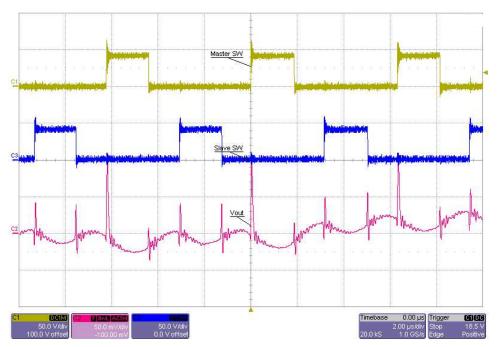

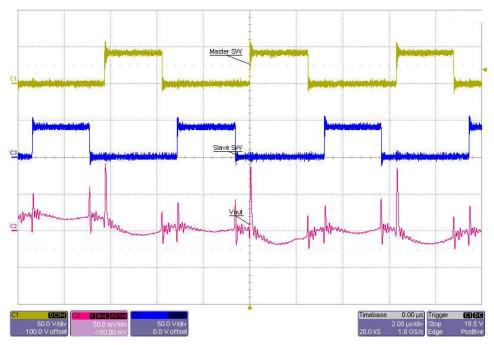

The switching waveforms and output ripple are measured with oscilloscope probes connected to TP1 (SW1), TP2 (SW2), and the  $V_{OUT}$  test points shown in Figure 4. In the oscilloscope traces in Figure 10, the yellow trace is the switch node for the master LM25122-Q1, the blue trace is the slave switch node, and the pink trace is the output ripple and noise. The worst cast output ripple is about 180 mVp-p with a 9-V input and a 40-V output, as shown in Figure 18.

Figure 10. 9-V Input, 16-V Output, Full Load

Figure 11. 12-V Input, 16-V Output, Full Load

Figure 12. 9-V Input, 20-V Output, Full Load

Figure 13. 12-V Input, 20-V Output, Full Load

Figure 14. 16-V Input, 20-V Output, Full Load

Figure 15. 9-V Input, 30-V Output, Full Load

Figure 16. 12-V Input, 30-V Output, Full Load

Figure 17. 16-V Input, 30-V Output, Full Load

Figure 18. 9-V Input, 40-V Output, Full Load

Figure 19. 12-V Input, 40-V Output, Full Load

Figure 20. 16-V Input, 40-V Output, Full Load

Hardware Setup, Testing Requirements, and Test Results

#### www.ti.com

#### 3.2.2.3 Start-Up Transient

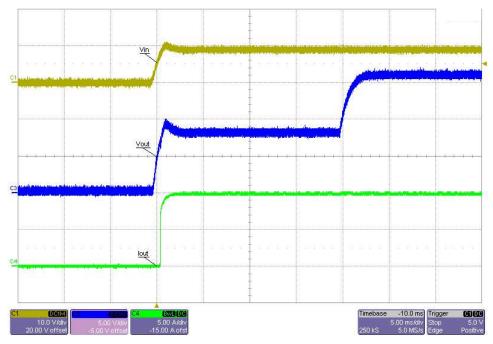

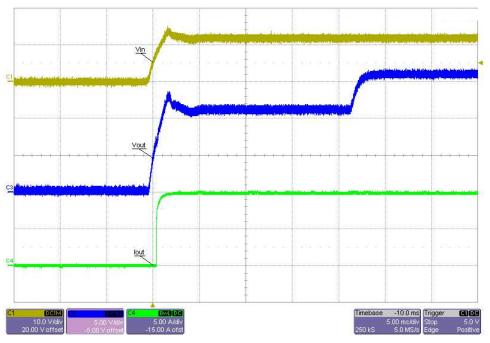

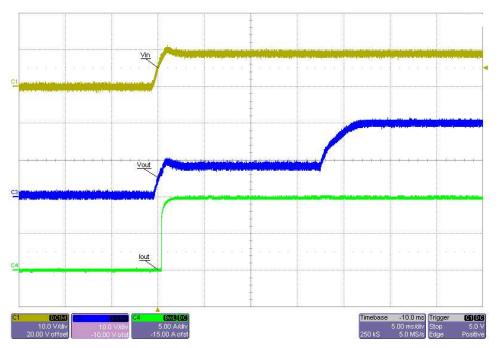

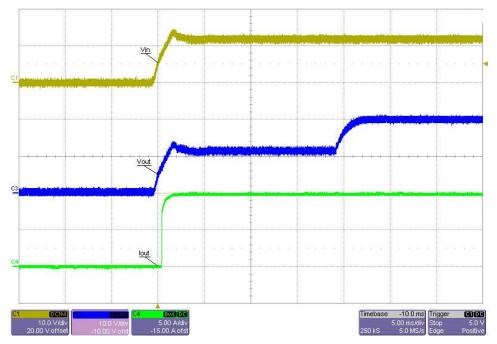

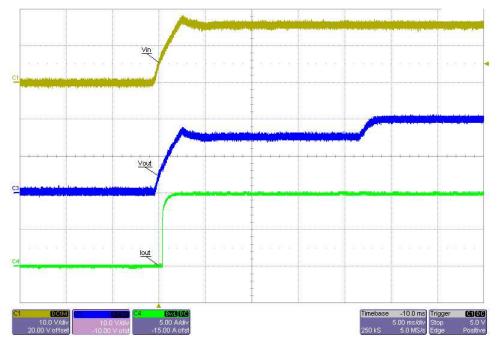

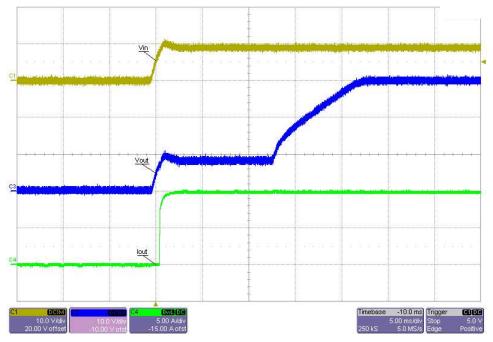

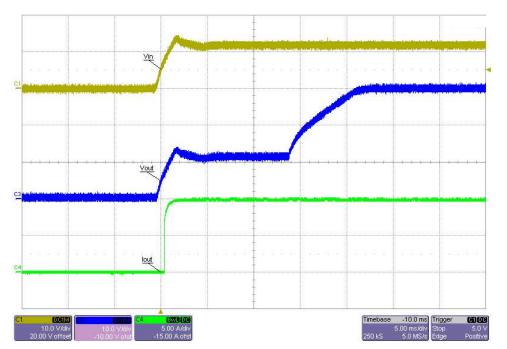

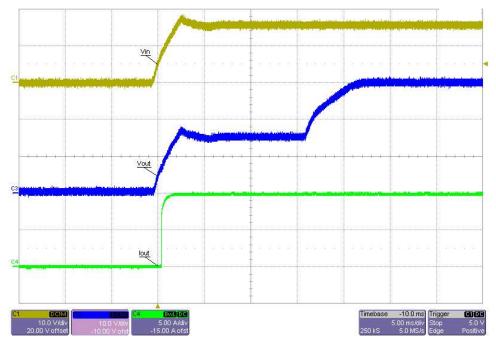

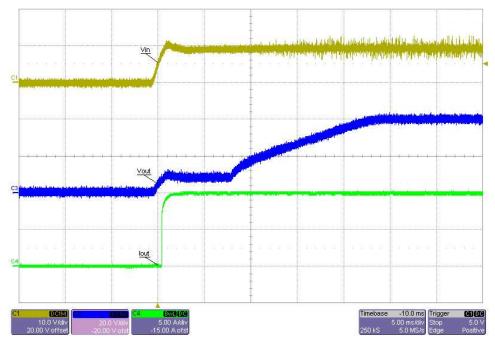

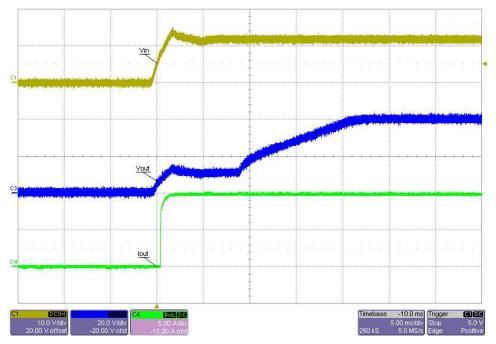

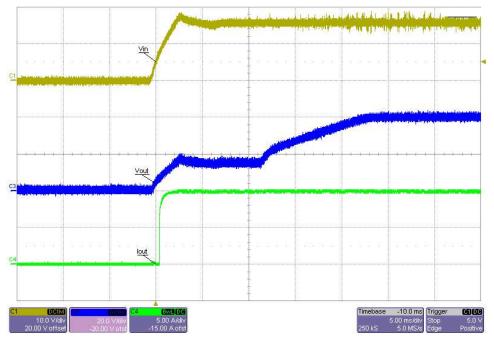

The start-up transient behavior is measured with oscilloscope probes connected to the input and output voltages and an inductive current probe to measure the output current to the load. In the oscilloscope traces in this section, the yellow trace is the input voltage, the blue trace is the output voltage, and the green trace is the output current. At start-up, the output reaches 40 V in about 22 ms for input voltages of 12 V and 16 V and 23 ms for an input voltage of 9 V.

Figure 21. 9-V Input, 16-V Output, 10-A Load Start-up

Figure 22. 12-V Input, 16-V Output, 10-A Load Start-up

Figure 23. 9-V Input, 20-V Output, 10-A Load Start-up

Figure 24. 12-V Input, 20-V Output, 10-A Load Start-up

Figure 25. 16-V Input, 20-V Output, 10-A Load Start-up

Figure 26. 9-V Input, 30-V Output, 10-A Load Start-up

Figure 27. 12-V Input, 30-V Output, 10-A Load Start-up

Figure 28. 16-V Input, 30-V Output, 10-A Load Start-up

Figure 29. 9-V Input, 40-V Output, 10-A Load Start-up

Figure 30. 12-V Input, 40-V Output, 10-A Load Start-up

Figure 31. 16-V Input, 40-V Output, 10-A Load Start-up

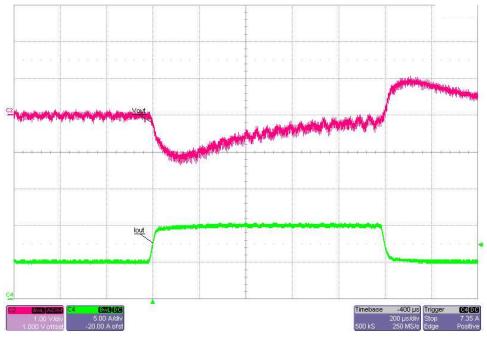

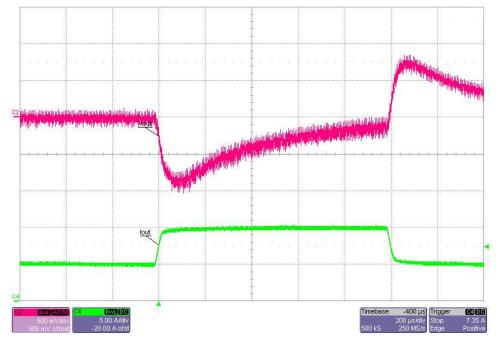

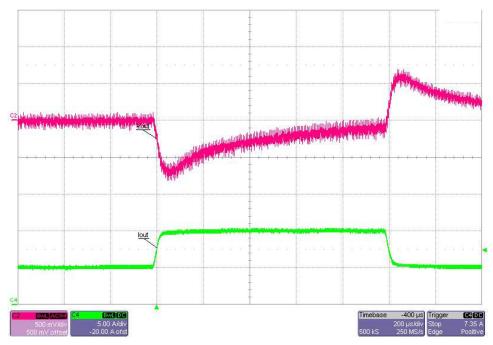

#### 3.2.2.4 Transient Response

The load step transient response is measured with an oscilloscope probe on the output voltage and an inductive current probe measuring the output current. In the following plots, the pink trace is the output voltage and the green trace is the output current. The load step response is measured with a load step of 5 A to 10 A with input voltages of 9 V, 12 V, and 16 V. Output voltage is set for 40 V because this is the worst case condition. The worst case droop and overshoot occurs when the input voltage is 49 V, as shown in Figure 32. The maximum voltage droop is 1.4 V, and the maximum overshoot is 1.2 V.

Figure 32. 9-V Input, 40-V Output, 5-A to 10-A Load Transient

Figure 33. 12-V Input, 40-V Output, 5-A to 10-A Load Transient

Figure 34. 16-V Input, 40-V Output, 5-A to 10-A Load Transient

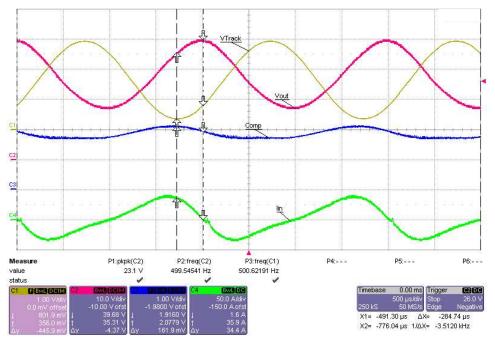

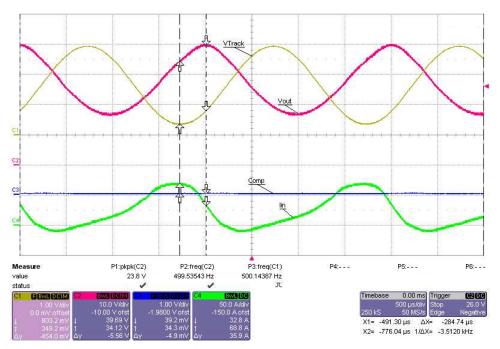

#### 3.2.2.5 Envelope Tracking

Figure 35 shows the response of the output voltage to a 500-Hz tracking signal. The tracking signal varies from 0.3 V to 3 V. In the following plots, the yellow trace is the tracking signal, the pink track is the output voltage, the blue trace measures the compensation voltage, and the green trace measures the input current. The input voltage is 12 V in both cases. Note that the output voltage is delayed by 285 µs from the tracking voltage.

Figure 35. Tracking Response, 12-V Input, No Load, 500-Hz Tracking Signal

Figure 36. Tracking Response, 12-V Input, 10-A Load, 500-Hz Tracking Signal

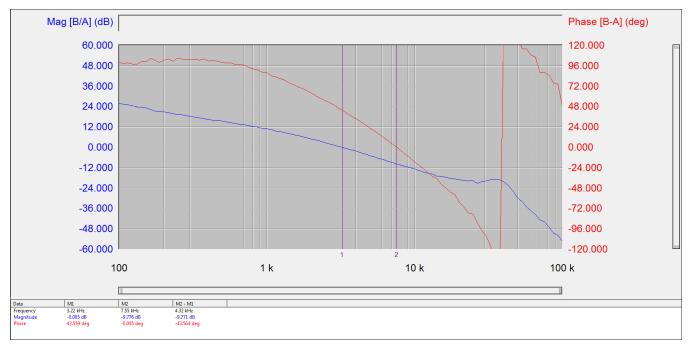

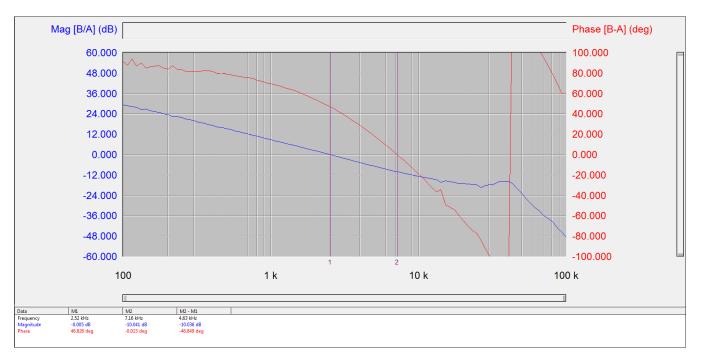

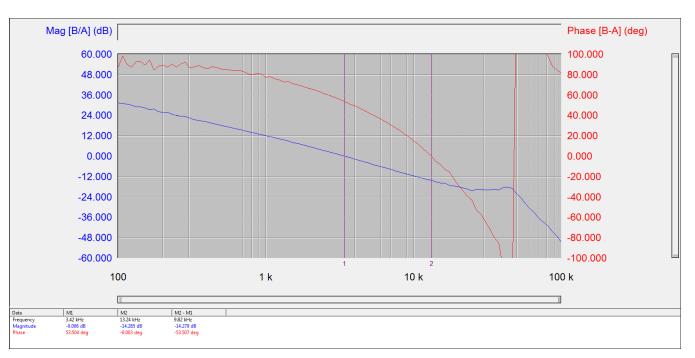

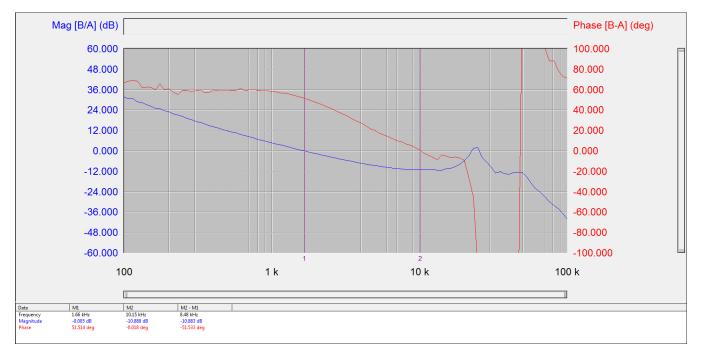

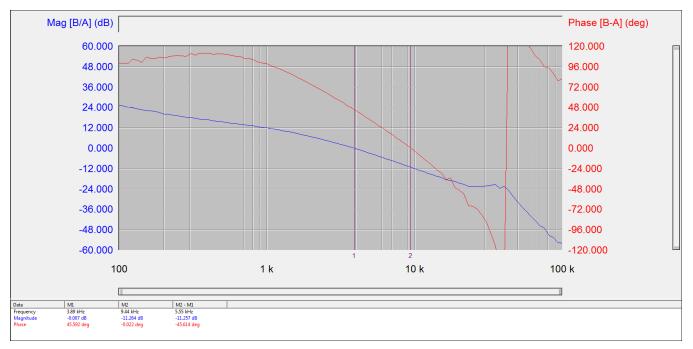

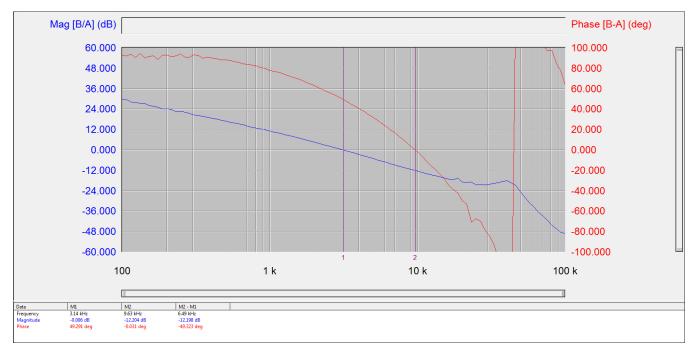

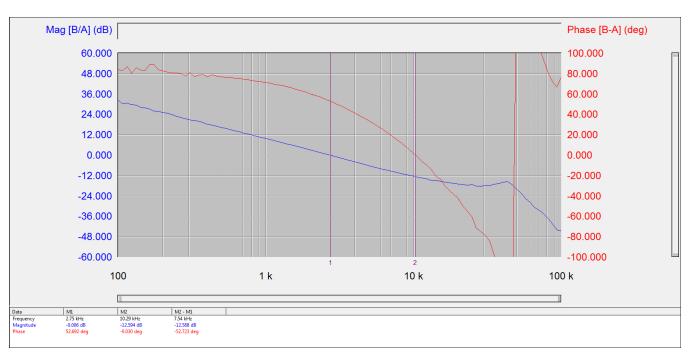

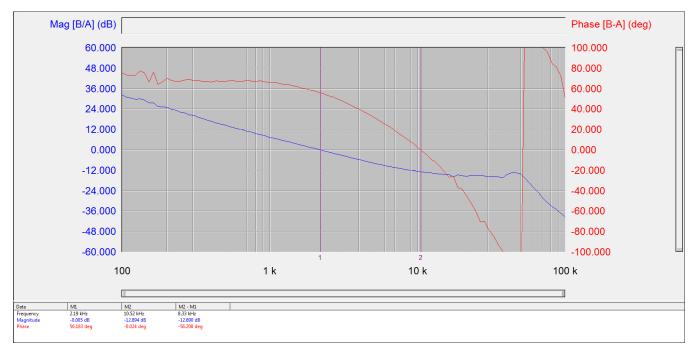

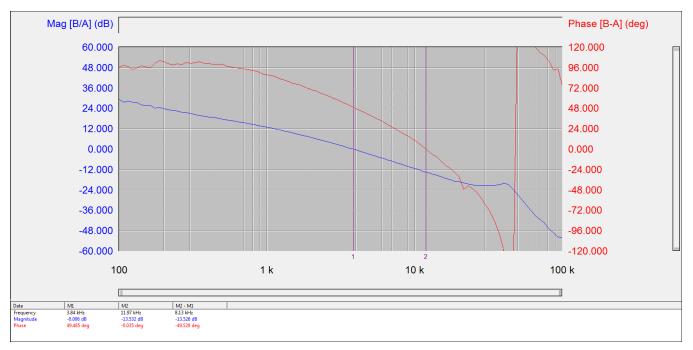

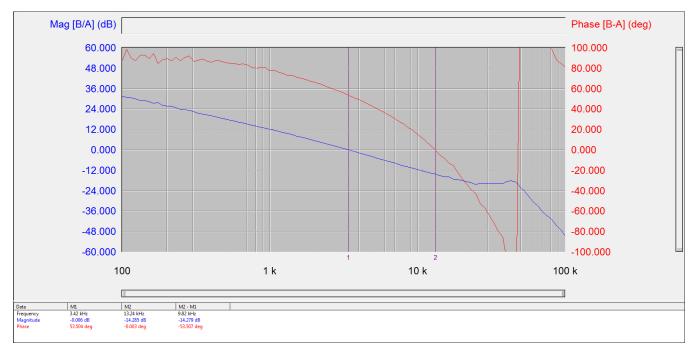

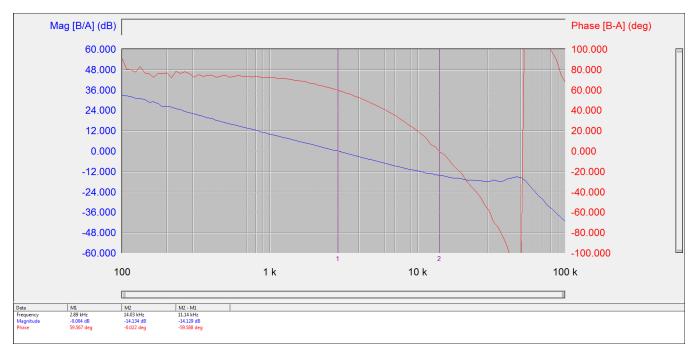

#### 3.2.2.6 Frequency Response

This section shows the gain and phase margin for a 10-A output with the input voltage set to 9 V, 12 V, or 16 V and the output voltage set to 16 V, 24 V, 30 V, or 40 V.

Figure 37. 9-V Input, 16-V Output, 10-A load: 43.56-Degree Phase Margin, -9.78-dB Gain Margin

Figure 38. 9-V Input, 24-V Output, 10-A Load: 46.83-Degree Phase Margin, -10.04-dB Gain Margin

Figure 39. 9-V Input, 30-V Output, 10-A Load: 48.94-Degree Phase Margin, -10.36-dB Gain Margin

Figure 40. 9-V Input, 40-V Output, 10-A Load: 51.51-Degree Phase Margin, -10.89-dB Gain Margin

Figure 41. 12-V Input, 16-V Output, 10-A load: 45.6-Degree Phase Margin, -11.26-dB Gain Margin

Figure 42. 12-V Input, 24-V Output, 10-A Load: 49.29-Degree Phase Margin, -12.204-dB Gain Margin

Hardware Setup, Testing Requirements, and Test Results

Figure 43. 12-V Input, 30-V Output, 10-A Load: 52.69-Degree Phase Margin, -12.59-dB Gain Margin

Figure 44. 12-V Input, 40-V Output, 10-A Load: 56.18-Degree Phase Margin, -12.89-dB Gain Margin

Figure 45. 16-V Input, 24-V Output, 10-A Load: 49.49-Degree Phase Margin, -13.53-dB Gain Margin

Figure 46. 16-V Input, 30-V Output, 10-A Load: 53.51-Degree Phase Margin, -14.29-dB Gain Margin

Hardware Setup, Testing Requirements, and Test Results

Figure 47. 16-V Input, 40-V Output, 10-A Load: 59.57-Degree Phase Margin, -14.13-dB Gain Margin

#### 4 **Design Files**

#### **Schematics** 4.1

To download the schematics, see the design files at TIDA-01610.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01610.

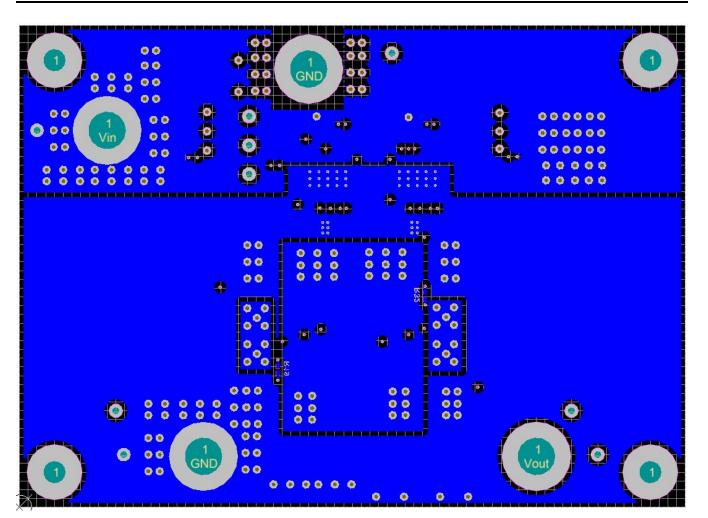

#### 4.3 PCB Layout Recommendations

The PCB is a four-layer board with routing on all four layers. All components are placed on the top layer. The input caps, current sense resistors R2 and R23, inductors L1 and L2, the synchronous rectifier transistors, and the output capacitors are placed so that the copper traces are as short as possible and the current loop from the input capacitor ground to the output capacitor ground is short. Multiple large vias are used to ensure low impedance where high current nets change layers on the PCB. The switch transistors also form a short path from the input inductor to ground between the input and output capacitors. Because the LM25122-Q1 boost controllers are not in the high current path, they are placed away from the main current loop. All high current paths have large copper areas to minimize impedance. V<sub>OUT</sub> is connected to the output filter on this layer.

#### Figure 48. PCB Top Layer

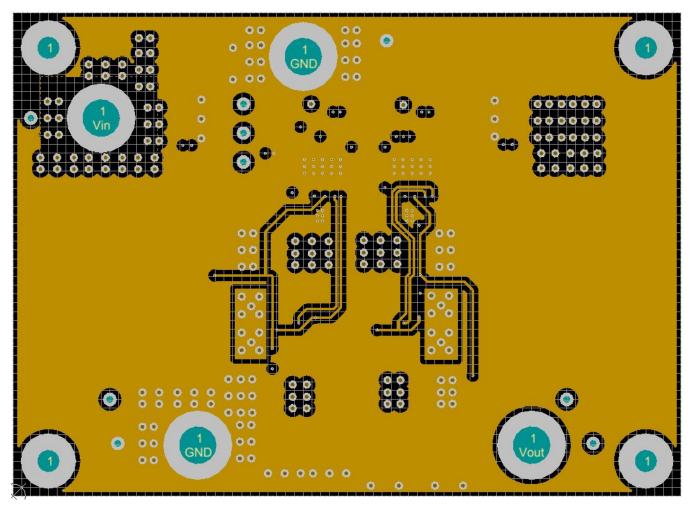

Figure 49. PCB Layer 2

On layer 2, HO1 is routed next to the part of SW1 that connects from U1 to Q1 and Q2, and HO2 and SW2 are routed in a similar manner from U2 to Q5 and Q6. LO1 and LO 2 are also routed on this layer. The large copper pour on this layer is ground.

Figure 50. PCB Layer 3

PCB layer 3 contains the signals shared by U1 and U2. The pairs of nets toward the top are the Kelvin connections from current sense resistors R2 and R23. One connection in each pair is connected to  $V_{IN}$ . The vias for these connections fall inside of a  $V_{IN}$  plane that is on the bottom layer. Because of this, cutouts are placed around the four vias so that they do not connect to the plane. If they did, the current measurement would not be accurate due to the voltage not being sensed right at the resistors. Most of layer 3 is ground. The bottom has a plane for  $V_{IN}$ , a plane for net C1-1 (which is the connection point of the two output phases), and a ground plane.

Figure 51. PCB Bottom Layer

# 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01610.

# 4.4 Altium Project Files

To download the Altium project files, see the design files at TIDA-01610.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01610.

# 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01610.

### 5 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 6 About the Authors

**MARK KNAPP** is a systems architect at Texas Instruments Incorporated who specializes in automotive premium audio systems and instrument clusters. He also has an extensive background in video camera systems and infrared imaging systems for military, automotive, and industrial applications. Mark earned his BSEE at the University of Michigan-Dearborn and his MSEE at the University of Texas at Dallas.

**XINYU DAI** has a system application role at Texas Instruments Incorporated and specializes in designing various power supply topologies for industrial, consumer, and automotive applications. His background includes kilowatt multi-phase designs, compact designs for personal electronics, and EMI optimized designs for automotive applications. Xinyu earned his BSEE at the Georgia Institute of Technology with high honor.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated