# TI Designs: TIDA-01634 Multi-MHz GaN Power Stage Reference Design for High-Speed DC/DC Converters

# TEXAS INSTRUMENTS

### Description

This reference design implements a multi-MHz power stage design based on the LMG1210 half-bridge GaN driver and GaN power HEMTs. With highly efficient switches and flexible dead-time adjustment, this design can significantly improve power density while achieving good efficiency as well as wide control bandwidth. This power stage design can be widely applied to many space-constrained and fast response required applications such as 5G telecom power, servers, and industrial power supplies.

# Features

- Compact GaN-Based Power Stage Design With Switching up to 50 MHz

- Independent PWM Inputs for High Side and Low Side, or Single PWM Input With Adjustable Dead Time

- Minimum Pulse Width of 3 ns

- High Slew Rate Immunity of 300 V/ns

- Driver UVLO and Overtemperature Protection

#### Resources

TIDA-01634 LMG1210 Design Folder Product Folder

ASK Our E2E<sup>™</sup> Experts

### Applications

- High-Speed, Synchronous Buck Converters

- Envelope Tracking

- Class D Audio Amplifiers

- Server and Network Power Supplies

- Industrial Power Supplies

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

#### 1 System Description

Switching-mode power supply designers are always pursing higher power density, which requires higher frequency and efficiency. Compared to silicon FETs, gallium nitride (GaN) and high electron mobility transistors (HEMTs) exhibit a lower figure of merit, smaller gate charge, faster switching, and no reverse recovery loss.

This reference design uses GaN power HEMTs and the LMG1210 GaN half-bridge driver to realize a multi-MHz power stage with high efficiency. The half-bridge driver allows a single PWM input with configurable dead time or two independent inputs for high-side and low-side gate drive. Dead-time adjustment can be realized with two resistors for low-to-high and high-to-low transition settings from 0 ns to 20 ns. In addition, the bootstrap switching action also prevents overvoltage of high-side gate due to large third quadrant voltage drop of GaN HEMTs.

This power stage can realize 3 ns of minimum on-time and up to a 50-MHz operation frequency. This design can stand a slew rate of 300 V/ns of common mode transient and provides driver UVLO and overtemperature protection.

This design can be applied to many space-constrained and fast response required applications such as 5G telecom power, 48-to-POL server power, and industrial power supplies.

#### 1.1 Key System Specifications

| PARAMETER                        | TEST CONDITIONS | MIN | ТҮР  | MAX | UNITS |  |

|----------------------------------|-----------------|-----|------|-----|-------|--|

| INPUT AND OUTPUT CHARACTERISTICS |                 |     |      |     |       |  |

| Input and output voltage         |                 | 0   |      | 60  | V     |  |

| Input and output current         |                 | 0   | 4    | 5   | А     |  |

| Bias voltage                     |                 | 6   | 7    | 18  | V     |  |

| Maximum bias current             |                 | 100 |      |     | mA    |  |

| SYSTEM CHARACTERIS               | TICS            |     |      |     |       |  |

| Switching frequency              |                 | 0.1 | 1    | 50  | MHz   |  |

| Slew rate                        |                 |     | 70   |     | V/ns  |  |

| Full load efficiency             |                 | 96  | 96.5 | 97  | %     |  |

#### **Table 1. Key System Specifications**

<sup>(1)</sup> With 200 LFPM of airflow on the board to ensure good thermal stability. No additional heat sink used.

### 2 System Overview

#### 2.1 Block Diagram

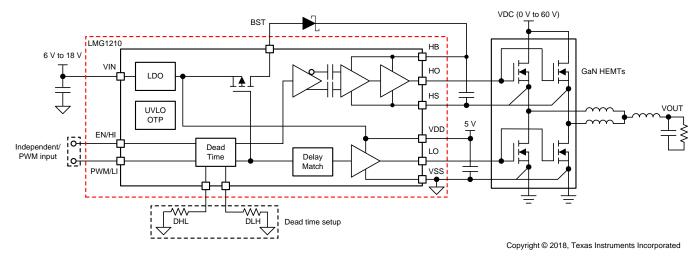

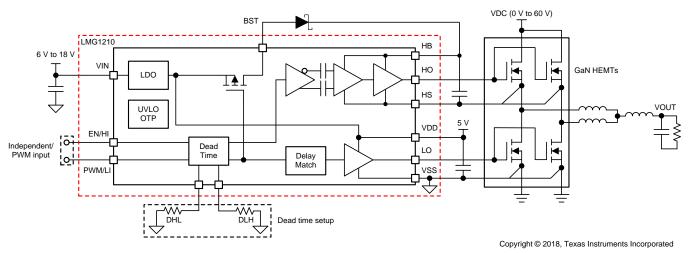

Figure 1 shows the block diagram of this design. One half-bridge driver LMG1210 with an external boot strap diode drives two paralleled half bridges. Four 65-V rated GaN FETs are used as switching devices.

Figure 1. TIDA-01634 Block Diagram

#### 2.2 Design Considerations

#### 2.2.1 FET Selection

Switching related losses increase linearly with frequency and can become dominate at multi-MHz operation. Based on the targeted switching frequency and power level, switching devices should be carefully selected to realize a balance between  $R_{DS(on)}$  and switching related loss.

In this application, GaN HEMT is chosen due to its significant advantages in switching. Typical Si MOSFETs exhibit high switching loss, including I/V overlap,  $C_{OSS}$  loss, and reverse recovery loss. With no reverse recovery, small C <sub>OSS</sub>, and fast switching speed, GaN FETS are ideally suited for high-frequency applications. The switching related characteristics are listed as the table below to compare GaN and Si.

Furthermore, it is critical to choose the appropriate GaN HEMT for the specific switching frequency and load current. With similar figure of merit, smaller C<sub>OSS</sub> is preferred for high-frequency switching as switching loss can be dominating under multi-MHz switching. For example, in Table 2, the two GaN FETs have a similar figure of merit but one of them (EPC2039) has a larger C<sub>OSS</sub> loss. In this design, two FETs with small C<sub>OSS</sub> are paralleled to achieve both small C<sub>OSS</sub> loss and conduction loss for the targeted load current.

| PARAMETER                                          | EPC8009 (GaN) | EPC2039 (GaN) | BSP320S (Si) |

|----------------------------------------------------|---------------|---------------|--------------|

| Max V <sub>DS</sub> (V)                            | 65            | 80            | 60           |

| R <sub>DS(on)</sub> (mΩ)                           | 130           | 25            | 120          |

| Q <sub>g</sub> (nC)                                | 0.37          | 1.91          | 12           |

| Q <sub>gs</sub> (nC)                               | 0.12          | 0.76          | 1            |

| Q <sub>gd</sub> (nC)                               | 0.055         | 0.42          | 4.7          |

| Q <sub>oss</sub> (nC)                              | 0.94          | 7.64          | 2.25         |

| Q <sub>rr</sub> (nC)                               | 0             | 0             | 80           |

| FOM ( $Q_g \times R_{DS(on)}$ ) (nC × m $\Omega$ ) | 48.1          | 47.75         | 1440         |

| Table 2. Ke | v Parameter                           | Comparison o | f Switching FETs                       |

|-------------|---------------------------------------|--------------|----------------------------------------|

|             | · · · · · · · · · · · · · · · · · · · |              | · • ······ ··························· |

#### 2.2.2 Capacitor Selection

#### 2.2.2.1 Gate Loop Capacitor

The bypass capacitor for the LMG120 must be located on the top layer with ground return on the layer immediately adjacent with a recommended minimal spacing of 5 mils. Also, the placement must be as close as possible to the IC and connected to both VDD and GND using large power planes. This bypass capacitor has to be at least a 0.1 µF (up to 1 µF) with a temperature coefficient of X7R or better. For this particular application, it is highly recommended to use low-inductance body types such as LICC, IDC, feed-though, and LGA. Add another 1-µF to 10-µF bulk VDD decoupling capacitor as well.

In addition, place the V<sub>IN</sub> decoupling capacitor as close to the device as possible, but this is a lower priority than the VDD decoupling capacitor.

#### 2.2.2.2 **Power Loop Capacitor**

The selection of the high-frequency capacitors for the power loop is critical to help minimize the loop stray inductance. The capacitors have to be selected to allow for the maximum bus voltage and to provide both enough charge to sustain the current and to provide a minimal inductive path. X7R or better material is needed to provide stability and low ESR. A mix of 0603 and 0805 is used, where the 0603 capacitors are in the closest proximity to the power loop and the 0805 capacitors are adjacent to those first capacitors. Low-inductance, wide-body packages are preferred.

The layout of this section is critical and will be discussed later in this document.

#### 2.2.3 FETs Paralleling

When FETs with smaller C<sub>oss</sub> and switching loss are selected, switching related loss can be minimized to allow a high operation frequency of the DC/DC converter. At the same time, conduction loss also needs to be considered with respect to load condition. When load current is high, two half-bridges can be paralleled together to increase the current capability of the power stage.

Due to the fast switching of GaN FETs, small parasitic inductance needs to be achieved even when paralleling the FETs. In this case, a "pseudo-parallel" structure is preferred, which means two half-bridges are designed with shared gate drive with minimal parasitics. A small inductor is recommended between the two switching nodes. If no inductor is between the two nodes, small part-to-part variations in the threshold voltage of the GaN can cause one FET to turn on earlier and absorb a disproportionate share of the switching losses, thus causing a thermal imbalance.

In addition, it is critical to keep identical layout loops between the two legs to achieve similar delay and gate voltage profile in the switching transient.

#### 2.2.4 **Layout Considerations**

The layout of the GaN-based power stage requires specific attention to the loop inductance for both the power loop and gate drive loop. If two half-bridges are paralleled, it is also highly suggested to make the layout symmetric to achieve a similar performance and parasitics for the two loops.

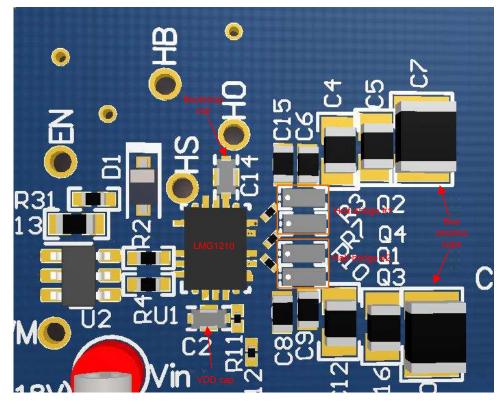

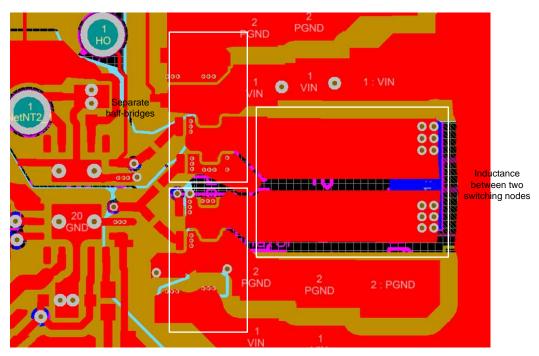

Figure 2 shows a general view of the layout.

Figure 2. Layout General View

#### 2.2.4.1 Gate Drive Loop Layout

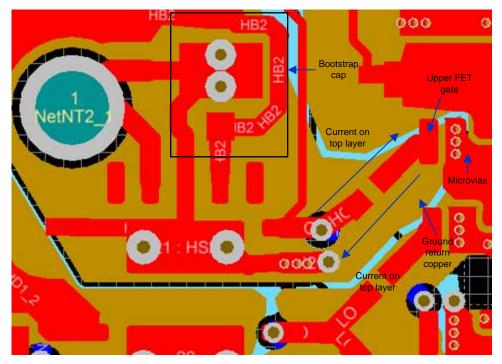

The following figures show the layout of the gate loop of the upper and lower FETs. To achieve the minimum loop inductance, the layout of gate loop must follow these rules:

- Have the VDD capacitor or bootstrap capacitor as close as possible to the gate driver because these traces will be part of the gate loop.

- Use a dedicated Kelvin source or minimum sharing of source trace between the gate loop and main power loop to achieve the minimum common source inductance. The high di/dt on the main loop can be easily be coupled to the gate loop to cause decreased switching speed and other negative effects.

- To minimize the gate loop inductance, the ground return path has to be on the adjacent layer with minimum inter-layer dielectric thickness, and have as much overlap as possible to the driver output. In this case, the current flow on the input of FET gate is the opposite of the ground current return, which offsets the magnetic field and reduces PCB stray inductance.

- To keep the return loops as short as possible, micro-vias in pads are used extensively in this design to further reduce the parasitic inductances and improve the vertical current extraction from components.

Figure 3. Gate Drive Loop Layout for High-Side FET

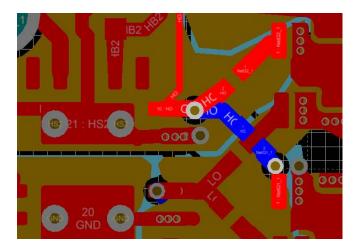

In certain circumstances that require paralleled FETs, the following rules help achieve better symmetry and at the same time minimize the gate loop inductance.

- Place the paralleled FETs with similar distance to the output of the driver. Have the FET gate loop traces laid out on different layers to keep the traces with identical length to the FETs.

- Keep the identical return paths on different layers, and make sure that for each FET, the return ground layer is on the adjacent layer of its dedicated gate path to minimize the stray inductance.

Figure 4 and Figure 5 show the gate loop layout of this reference design with two FETs paralleling.

Figure 4. Gate Drive Path for Paralleled FETs

Figure 5. Return Path of Paralleled FETs Gate Drive

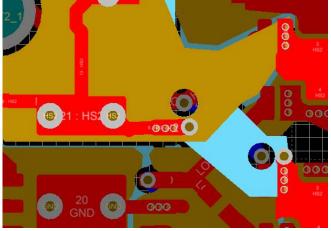

#### 2.2.4.2 Power Loop Layout

The layout of power loop is also aimed at minimizing stray inductance. To realize a small power loop:

- Place ceramic capacitors with a small package as close to the devices as possible. These capacitors

are usually better in frequency response and have a high bandwidth to absorb high-frequency noise

generated during switching.

- A very compact component placement is needed. Place the upper and lower FETs side by side, and use the layer immediately beneath for the return path. Use micro-vias (filled) in the pads to help keep the loop short.

- Have the return pass overlapped with the topside current path to create an opposite magnetic field. This field helps cancel the magnetic field in the loop and reduce the inductance.

- Minimize the overlap between switching node and ground/Vin copper. This overlap avoids the extra

parasitic capacitance, which adds to C<sub>OSS</sub> of FETs. If not designed well, the parasitic capacitors can

generate significant loss at high switching frequency.

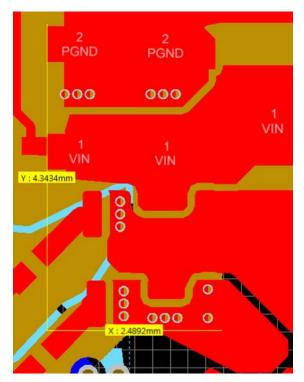

Figure 6 shows the size of the power loop is 2.5 mm  $\times$  4.3 mm. The 6800-pF capacitors are placed closest to the FETs, while other larger capacitors are placed further in a line. The return path is placed right underneath the top layer trace through micro-vias, spaced by the inter-layer dielectric thickness.

Figure 6. Power Loop Layout For a Half-Bridge

When paralleled FETs are used, they are laid out in a "pseudo-parallel" structure to have a minimized loop. This structure means two legs are laid out separately but share the same gate driver. The power loops of both half-bridges are laid out in a very symmetric pattern. The component placement and copper shapes are all symmetric. This structure helps achieve very similar loop characteristics in switching and conduction.

The switching nodes are connected with some PCB trace as small inductors in between (for more information, see Section 2.2.4.1). Depending on the selected FETs and operation voltage, the needed inductance between the two nodes can be varied. In this case, PCB trace inductors are used. In a practical design, these inductors can be replaced by external wires to obtain more flexibility on inductance values.

7

System Overview

Figure 7. Symmetric Power Loop Layout for Paralleled Half-Bridges

#### 2.2.5 Dead Time Optimization

8

There are two modes of inputs to enable the HS and LS outputs of the driver LMG1210: PWM mode and independent mode.

For PWM mode, two separate resistors set up the high-to-low and low-to-high transition dead times from 0 ns to 20 ns. With one input, two output signals can be generated. For independent mode, two independent signals are used to control the HS and LS switches.

An appropriate dead time is critical in a multi-MHz power stage design. GaN HEMTs are majority carrier devices, which lack the typical body diode present in MOSFETs. The conduction in the third quadrant is still possible through internal gate biasing, which causes a higher voltage drop in the channel due to the activation voltage and the channel resistance (while in linear mode). This drop is what is experienced during dead time. The voltage drop produces a loss, which is directly proportional to frequency, current, and time spent in the dead time. This loss can significantly degrade efficiency, especially in converters operating at high frequency and low input or output voltages. For example, in a 12-V to 1.8-V buck converter operating at 5 MHz and 10-A output, going from a dead time of 1 ns to 10 ns can degrade efficiency by 8.5%.

To minimize the dead time and its associated loss, the low-side and high-side propagation delay mismatch of the driver must be predictable and unaffected by part-to-part variation, temperature, bootstrap voltage, HS pin voltage, or HS slew rate. Table 3 summarizes the mismatch variations of the LMG1210 for these parameters. With the minimum variation of delay time in different effects with the LMG1210, the smallest dead time can be achieved, which results in much improved efficiency in the multi-MHz power stage.

In most converters, one edge is soft-switched. To avoid hard switching and maintain a small effective dead time on this soft-switched edge, the dead time must be varied depending on load current. For the other hard-switched edge, it is optimal to pursue the fixed minimum dead time when considering these variations.

| Table 3. Variation of Dead Time by Different Factors for LMG1210 |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

|                              | EDGE                                        |                           |                                             |                           |  |

|------------------------------|---------------------------------------------|---------------------------|---------------------------------------------|---------------------------|--|

| EFFECT                       | HIGH-OFF TO LOW-ON (HARD-SWITCHING<br>EDGE) |                           | LOW-OFF TO HIGH-ON (SOFT-SWITCHING<br>EDGE) |                           |  |

|                              | PARAMETER<br>VARIATION                      | LMG1210 VARIATION<br>(ns) | PARAMETER<br>VARIATION                      | LMG1210 VARIATION<br>(ns) |  |

| Variation of HS              | None (V <sub>IN</sub> )                     | 0                         | Minimal                                     | 0                         |  |

| Variation of Vbst            | 4 V to 4.5 V                                | 0.3                       | 4 V to 4.5 V                                | 0.3                       |  |

| Variation of CMTI            | None                                        | 0                         | 10 V/ns to 100 V/ns                         | 0.2                       |  |

| Intrinsic driver variation   |                                             | 0.7                       |                                             | 0.7                       |  |

| Total variation in dead time |                                             | 1                         |                                             | 1.2                       |  |

#### 2.2.6 Inductor Selection

The EVM comes equipped with a 1- $\mu$ H, 9-A inductor. If a different operating point in frequency, voltage, or current ripple is desired, it is likely that a new value of inductor will be more suited.

When selecting the new inductor, the value of the inductor must respect the value found from Equation 1: lind  $\geq$  V B U S min (IL\_sat, IF E T\_D C max)  $\cdot$  to n (1)

where:

- V<sub>BUS</sub> is the bus voltage across the power stage

- ton is the on-time of the upper FET (active FET)

- I<sub>L sat</sub> is the inductor saturation current

- I<sub>FET DCmax</sub> is the allowed maximum DC current of switching FETs

#### 2.3 Highlighted Products

#### 2.3.1 LMG1210

The LMG1210 is a 200-V, half-bridge, high-performance GaN FET driver designed for applications that require high switching speed, low dead time, and high efficiency. The drive voltage is precisely controlled by an internal linear regulator to 5 V when higher auxiliary voltages are used.

The LMG1210 is optimized to operate at very high frequencies. The extremely small mismatch and propagation delay of this device allows reduced dead time requirements. Additional parasitic capacitance across the GaN FET is minimized to less than 1 pF to reduce additional switching losses. An external bootstrap diode is used to charge the high-side driver to allow optimal selection for the circuit operating conditions. An internal switch turns off the bootstrap diode when the low side is not on, effectively preventing the high-side bootstrap from overcharging and minimizing the reverse recovery charge when a silicon diode is used as the bootstrap diode.

The driver can operate either with dual inputs with independent control of each driver or can be operated with a single PWM input with an independently adjustable dead time from 0 ns to 20 ns for each edge. The LMG1210 operates over a wide temperature range from -40°C to +125°C and is offered in a low-inductance QFN package.

#### 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware

- DC voltage source: Capable of supplying the input of the board up to 60 V as desired; capable of supplying 10 A and supports current limiting

- DC bias source: Capable of 6-V to 18-V output at up to 0.3 A

- Oscilloscope: Capable of at least a 200-MHz operation, using oscilloscope probes with a "pigtail" spring ground clip instead of the standard alligator clip

- DC multimeters: Capable of 100-V measurement, suitable for determining operation and efficiency (if desired)

- DC load: Capable of 100-V operation at up to 10 A in constant current-mode operation

- Function generator: Single output for PWM mode, dual synchronous output for independent mode; capable of at least 0-V to 3-V signal (operating maximum digital input is 5 V)

- Fan: 200LFM minimum airflow is recommended to cool the PCB when operating above a 10-A output current

- (Optional) Power meter: Capable of 100-V operation at up to 10 A

### 3.2 Testing and Results

#### 3.2.1 Test Setup

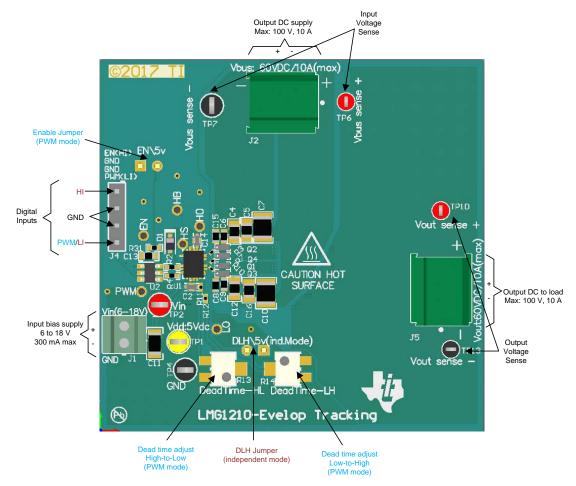

Connect the input and bias supplies and DC electronic load as shown in Figure 8.

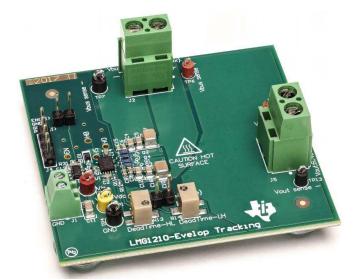

#### Figure 8. Top View of TIDA-01634 Hardware

#### Hardware, Software, Testing Requirements, and Test Results

To get rid of the high-frequency noise induced by the probe parasitics, use the small pigtails without the probe clips. This minimizes measurement error and produces a cleaner signal with the fast switching GaN devices used on this reference design. The data shown in this design guide is obtained using this method.

Figure 9. Low Parasitic Measurement Setup

To obtain the best performance of this board:

- Thermal: The parts used on this board are extremely small. If the dissipation exceeds 2 W, actively cool the board (as it has no heat-sink) using a fan or a similar device.

- Voltage spikes: As the test is running, whenever increasing the voltage and the current, it is important to monitor the voltage on the switched node to ensure the peak voltage does not exceed the 65-V rating of the EPC8009 FETs as those could damage the components.

- Additional capacitance on switched nodes: Typically, the method to observe the voltage at the highside gate and the switched node is using a voltage probe. These probes come with several tens of pF of capacitance, which given the frequency can negatively impact efficiency. For precise efficiency measurements, remove all probes connected to switching nodes.

#### 3.2.2 Test Results

#### 3.2.2.1 Efficiency

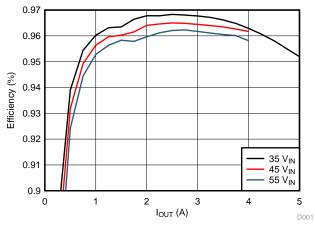

Figure 10 shows the efficiency results in this section, which exclude driver losses. The power stage is running at 10 MHz with a 85% duty cycle with respect to different output current.

Figure 10. Power Stage Efficiency With EPC8009 1-µH Inductor, Running at 10 MHz 85% Duty Cycle vs Output Current

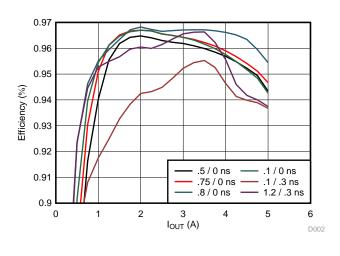

#### 3.2.2.2 Dead-Time Tuning

Tuning the dead time correctly for high-speed application can greatly improve performance. Pay attention when tuning the dead time of the two FETs before applying the input voltage.

Figure 11 shows the effect of changing the dead time on a sub-optimal design. The values refer to the transitions high-to-low first (first number) and low-to-high (second number).

It is possible to see a direct impact of any dead time on the low side turning on (as this contributes to third-quadrant conduction losses). For the high-side turnon dead time, there is an optimal value (that is dependent on components variation across boards), which is typically between 0 ns and 2 ns.

Figure 11. Effect of Dead-Time Tuning on Efficiency

Figure 12. Dead Time Measurement Done at  $V_{IN} = 0$ Showing High-to-Low Transition Dead Time of 640 ps

Hardware, Software, Testing Requirements, and Test Results

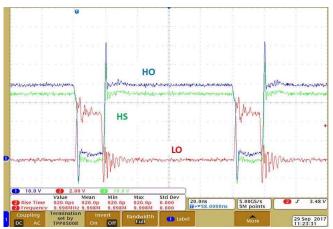

#### 3.2.2.3 Switching Waveforms

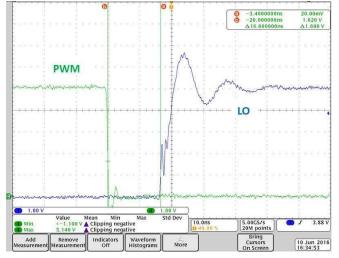

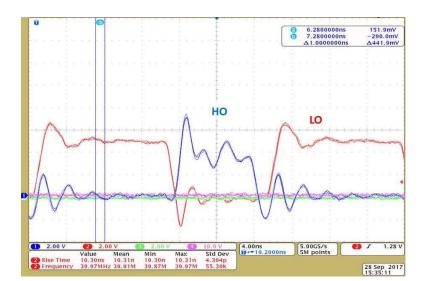

Figure 13. PWM High-to-Low Delay Time

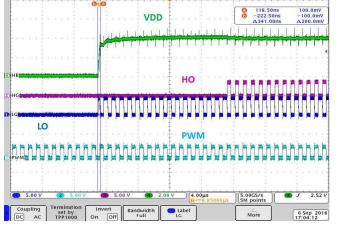

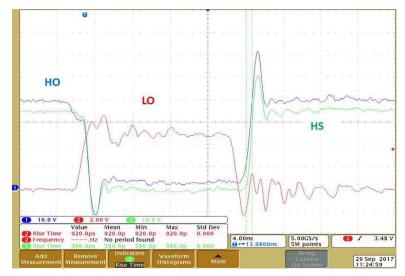

Figure 15. HO and LO Outputs of LMG1210 During Startup

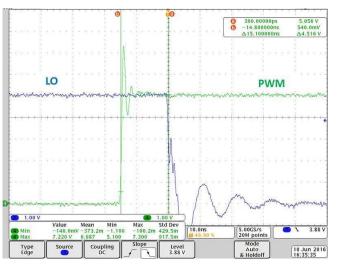

Figure 14. PWM Low-to-High Delay Time

Figure 16. Power Stage Switching at 10 MHz, 35 V

Figure 17. HO and LO Signals When Switching at 40 MHz With No DC Bus Voltage

Figure 18. Switching Transient With 70 V/ns on Switching Node

### 4 Design Files

### 4.1 Schematics

To download the schematics, see the design files at TIDA-01634.

### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01634.

### 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01634.

#### 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01634.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01634.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01634.

### 5 Related Documentation

- 1. Texas Instruments, Using the LMG1210EVM-012 300 V Half-Bridge Driver for GaN User's Guide

- 2. Texas Instruments, LMG1210 200-V, 1.5-A, 3-A Half-Bridge GaN Driver With Adjustable Dead Time Data Sheet

- 3. Texas Instruments, Optimizing Efficiency Through Dead Time Control With the LMG1210 GaN Driver Application Report

### 5.1 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners. Design Files

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated