# Design Guide: TIDA-010010 Industrial Gigabit Ethernet PHY Reference Design

# Texas Instruments

# Description

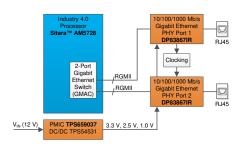

PLC applications require high speed gigabit Ethernet interface. This can be realized using our reference design which implements the DP83867IR industrial gigabit Ethernet physical layer transceiver to the gigabit Ethernet MAC peripheral block inside the Sitara<sup>™</sup> AM5728 processor.

This TI design shows how to interface the DP83867IR industrial gigabit Ethernet Physical Layer Transceiver (PHY) to the gigabit Ethernet MAC (GMAC) peripheral block inside the Sitara<sup>™</sup> AM5728 high-performance application processor. The hardware design is based on the AM5728 evaluation module (EVM) schematics and layout, but replaces the two KSZ9031 Ethernet PHY with TI's DP83867IR gigabit Ethernet PHY. The DP83867IR solution provides many advantages versus the former solution, including smaller board space area, reduced bill of material (BOM), lower power consumption, and overall lower production cost. The TI design addresses the design challenges like voltage supply generation, Ethernet PHY clocking, and RGMII- and MDI-interfaces. It provides a reference implementation for the DP83867IR PHY on power-on-reset generation, bootstrapping, and register configuration.

# Resources

| TIDA-010010 | Design Folder  |

|-------------|----------------|

| DP83867IR   | Product Folder |

| AM5728      | Product Folder |

| TPS659037   | Product Folder |

| TPS54531    | Product Folder |

|             |                |

# **Design Images**

Ask our TI E2E<sup>™</sup> support experts

# Features

- Integration of DP83867IR industrial gigabit Ethernet PHY for harsh industrial environments with Sitara<sup>™</sup> AM5728 high-performance application processor

- Simplifying the gigabit Ethernet device integration bill-of-material (BOM) by reducing the cost for power supply, integrating RGMII termination resistors and PHY clocking tree

- DP83867IR industrial Ethernet PHY with lowpower consumption 457 mW under full operating power

- Integrated MDI termination resistors reducing BOM, and board space, and simplifying layout

- Programmable MII, GMII, RGMI termination impedance inside the DP83867IR PHY

- DP83867IR PHY register configuration examples

with bootstrap and MDIO software

- RGMII and MDIO signal integrity considerations for power-on-reset and PHY bootstrap

# Applications

- Factory Automation and Control

- Industrial Drives

- Grid Infrastructure

- Building Automation

# **1** System Description

This TI design interfaces the DP83867IR gigabit Ethernet PHY to the Sitara AM5728 high performance application processor from Texas Instruments (TI). The hardware schematics are based on the AM5728 evaluation module (EVM) and replaces the KSZ9031 Ethernet PHY with DP83867IR Ethernet PHY. System designers can leverage from the benefits of using DP83867IR for reduces board space and BOM, reduced PHY power consumption. The TI design is a hardware reference implementation and reference register configuration for the DP83867IR with AM5728.

The TI design addresses system designer challenges like RGMII and MDI signal integrity, DP83867IR bootstrap configuration, register configuration over MDIO, DP83867IR clocking tree and DP83867IR voltage supply generation.

# **1.1 Key System Specifications**

| FUNCTION                                  | SPECIFICATION                                                                       | COMMENT                                                                                                     |

|-------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Number of Ethernet ports                  | 2 Ports                                                                             | 2 × DP83867IR                                                                                               |

| MDI                                       | 1000BASE-T (copper), 100BASE-TX, 10BASE-<br>Te                                      | -                                                                                                           |

| MAC interface                             | RGMII                                                                               | -                                                                                                           |

| EMAC and switch                           | 2-Port gigabit Ethernet (GMAC)                                                      | GMAC integrated inside Sitara<br>AM5728                                                                     |

| Status LEDs                               | 2 per single Ethernet Port                                                          | Integrated into RJ45 jack                                                                                   |

| IEEE 1588v2                               | Y                                                                                   | Hardware enabled, not tested                                                                                |

| RJ45 jack with integrated transformer     | Y                                                                                   | -                                                                                                           |

| Serial Management Interface (SMI)         | Y                                                                                   | -                                                                                                           |

| Low power                                 | 457 mW in 1000Base-T (copper) mode                                                  | -                                                                                                           |

| Integrated termination resistors          | Y                                                                                   | Integrated into DP83867IR                                                                                   |

| RGMII delay mode on RX and TX             | Programmable delay                                                                  | Integrated into DP83867IR                                                                                   |

| Clock                                     | 25 MHz (<50 ppm)                                                                    | -                                                                                                           |

| Shared clocking tree                      | Y                                                                                   | PHY 1 generated clock for PHY<br>2                                                                          |

| Ethernet PHY power supply                 | Onboard power management integrated circuit (PMIC) generates 3.3 V, 2.5 V and 1.0 V | No additional DC/DC or LDO needed                                                                           |

| Reference register configuration software | Y                                                                                   | Based on TI real-time operating<br>system (RTOS) with source<br>code portable to other operating<br>systems |

Table 1-1. Key System Specifications

# 2 System Overview

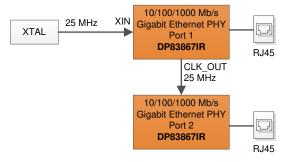

# 2.1 Block Diagram

Figure 2-1. TIDA-010010 Block Diagram

#### 2.2 Design Considerations

This TI design interfaces the DP83867IR gigabit Ethernet PHY to the Sitara AM5728 high-performance application processor. The AM5728 EVM (TMDSEVM572X) uses the KSZ9031 Ethernet PHY which has several disadvantages when compared to the DP83867IR gigabit Ethernet PHY solution. This TI design shows engineers on how to migrate to the DP83867IR gigabit Ethernet PHY solution on the area of RGMII interface signal integrity, PHY bootstrap configurations, PHY register configuration over MDIO, PHY clocking, PHY power supply. It also lists alternative power supply and clocking options.

# 2.3 Highlighted Products

#### 2.3.1 DP83867IR 10/100/1000-Mbps Gigabit Ethernet PHY

- Fully compatible to IEEE 802.3 10BASE-Te, 100BASE-TX, and 1000BASE-T specification

- Industrial operating temperature range –40°C to 85°C

- · Clock output to clock additional PHYs using one crystal (or clock) source

- 8-kV IEC 61000-4-2 ESD protection (direct contact)

- RGMII interface with support for programmable clock skew

- · RGMII Integrated termination resistors

- Low power: 457 mW

- Low deterministic TX and RX latency

For the full feature description, see the *DP83867IR Robust, Low Power 10/100/1000 Ethernet Physical Layer Transceiver* data sheet.

#### 2.3.2 AM5728 Sitara Processor: Dual ARM® Cortex®-A15 and Dual DSP

- ARM dual Cortex-A15 microprocessor subsystem

- Up to 2 C66x<sup>™</sup> floating-point VLIW DSP

- 2-Port Gigabit Ethernet (GMAC)

- 2 × dual-core *Programmable Real-Time Unit and Industrial Communication Subsystem* (PRU-ICSS) for industrial Ethernet

- Up to 2.5MB of on-chip L3 RAM

- Two DDR3, DDR3L Memory Interface (EMIF) Modules

- Quad SPI (QSPI)

- PCI-Express<sup>®</sup> 2.0 Subsystems with two 5-Gbps lanes

- Dual Controller Area Network (DCAN) modules

For the full feature description, see the AM572x Sitara™ Processors Silicon Revision 2.0 data sheet.

#### 2.3.3 TPS659037 Power Management Unit (PMU) for Processors

- · Seven step-down Switched-Mode Power Supply (SMPS) regulators

- Seven general-purpose Low Dropout Regulators (LDOs) with 50-mV steps

- Short-circuit protection

- Powergood indication (voltage and overcurrent indication)

- Clock management 16-MHz crystal oscillator and 32-kHz RC oscillator

- Real-Time Clock (RTC) with alarm wake-up mechanism

- 12-bit Sigma-Delta General-Purpose Analog-to-Digital Converter (ADC) with three external input channels and six internal channels for self monitoring

- Thermal Monitoring: High temperature warning and thermal shutdown

- Undervoltage Lockout

For the full feature description, see the *TPS65903x-Q1 Automotive Power Management Unit (PMU)* for *Processor* data sheet.

#### 2.3.4 TPS54531 570-kHz Step-Down Converter

- 3.5 to 28 V input voltage range

- Adjustable output voltage down to 0.8 V

- High efficiency at light loads with a pulse skipping Eco-mode

- 570-kHz switching frequency

- Overvoltage transient protection

- · Cycle-by-cycle current-limit, frequency fold back and thermal shutdown protection

- · Available in easy-to-use thermally enhanced 8-pin SO PowerPAD package

For the full feature description, see the *TPS54531 5-A, 28-V Input, Step-Down SWIFT™ DC-DC Converter With Eco-mode*<sup>™</sup> data sheet.

#### 2.4 System Design Theory

#### 2.4.1 DP83867IR Gigabit Ethernet PHY and AM5728 EVM Introduction

The AM5728 EVM is a high-performance application processor evaluation and development platform with dual ARM Cortex A-15 and two C66x DSP. TI offers processor software development kits (Processor SDK) for TI RTOS (real-time operating system), Linux (high level operating system, HLOS) and Linux RT (real-time Linux). Engineers can reuse the existing hardware and software infrastructure when interfacing the DP83867IR gigabit Ethernet PHY with the AM5728 EVM.

Using the DP83867IR in designs has several advantages over the KSZ9031:

- DP83867IR supports harsh industrial environments

- Industrial temperature range from –40°C to +85°C

- Small form factor in QFN(48) package

- Reduced system power consumption

- Simplifying BOM by removing large size FETs for PHY power generation

- Using existing PMIC to generate DP83867IR voltage supply

- First PHY generates clock for second PHY

- Integrated termination resistors in RGMII and MDI interface, no need to add external resistors

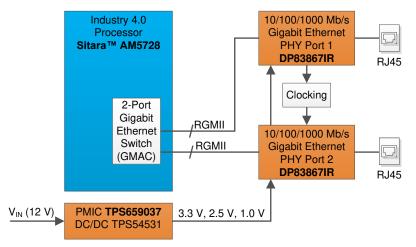

Figure 2-2 shows the board.

Figure 2-2. DP83867IR Gigabit Ethernet PHY on AM5728 EVM

The next sections explain the integration of the DP83867IR onto the AM5728 EVM.

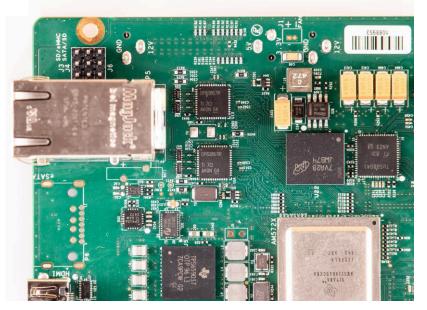

#### 2.4.2 DP83867IR Power Supply Generation

The DP83867IR device support either a 2-supply or a 3-supply configuration. The difference between these two configurations is an additional 1.8-V supply in the 3-supply configuration, leads to archive additional power savings. The 1.8-V supply is removed in the 2-supply configuration. This TI design uses the 2-supply configuration. More information on power supply is found in the *DP83867IR Robust, Low Power 10/100/1000 Ethernet Physical Layer Transceiver* data sheet.

The DP83867IR Ethernet PHY requires the following voltage supplies for the 2-supply configuration: 3.3 V, 2.5 V and 1.0 V for the QFN48 package.

The current (typical values) for each voltage rail are:

- 3.3 V: 14 mA

- 2.5 V: 137 mA

- 1.0 V (QFN48 package): 108 mA

Figure 2-3. DP83867IR Power Supply Generation

The 3.3-V voltage for the DP83867IR is generated by the TPS54531 step-down converter which generates the 3.3-V supply for the complete board. The 2.5 V and 1.0 V are generated by two SMPT rails within the TPS6590378, which were unused in the TMDSEVM572X EVM design. The two SMPT rails are configured and enabled by the application software because they are not present after PMIC power up. Note that using the AM5728 internal boot ROM does not enable those voltages hence prevent using the internal boot ROM to boot

from Ethernet option. However, any external bootloader (for example, MLO, u-boot, and so forth) can enable the SMPT supply rails of the PMIC to enable boot over Ethernet by the secondary bootloader.

#### Note

In case the system design does not allow using two SMPT rails of the PMIC, use the following alternative options to generate 2.5-V and 1.0-V voltage supply.

- 1. WCSP package option with 0.35-mm pitch enables smaller PCB board space area

- From 5-V or 3.3-V source voltage to 2.5-V supply voltage: TPS62802 this is a 5.7 mm<sup>2</sup> total solution size when using 0603 inductor and 0402 capacitors.

- From 5-V or 3.3-V or 2.5-V source voltage to 1.0-V supply voltage: TPS62801 this is 5.7 mm<sup>2</sup> total solution size when using 0603 inductor and 0402 capacitors

- 2. QFN package option

- From 5-V or 3.3-V voltage to 2.5-V supply voltage: TPS62230

- 5-V or 3.3-V or 2.5-V voltage to 1.0 V: TPS62239

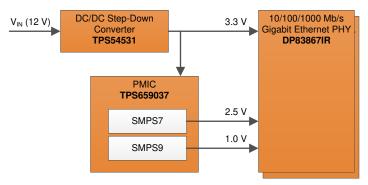

#### 2.4.3 DP83867IR Clock Generation

The TMDS5728EVM uses a two crystal clock solution approach, that is, one crystal generating 25-MHz clock for each PHY. This TI design leverages the CLK\_OUT signal available from the DP83867IR, which is a 25-MHz clock signal generated by the PHY form the XIN signal. Use the CLK\_OUT signal from the first PHY to provide the 25-MHz clock to a second PHY. Therefore the second crystal is not required and can be removed from the BOM.

The 25-MHz crystal is connected to the XIN/XOUT of the first PHY. After power up the first PHY outputs the 25 MHz at the CLK\_OUT pad, which is feed into the XIN of the second PHY. Note that a dedicated reset sequence is required for this daisy chaining of clocks, which is controlled by the application processor using GPIOs.

Figure 2-4. DP83867IR Clock Generation

#### 2.4.4 DP83867 Reset Generation

The use of the daisy chained clock approach requires a specific PHY reset sequence after power up. The reason for the reset sequence is that a valid clock signal needs to be present at the PHY before the RESET signal is released. Once power is applied to the first PHY the crystal starts to generate the 25-MHz clock at the XIN pad. After 25 MHz are present at the first PHY the RESET signal of the first PHY is released. It takes then some specific time inside the first PHY before the CLK\_OUT signal puts out 25-MHz clock. This TI design uses the worst case delay time of 201 ms. After 201 ms the second PHY will have 25 MHz at the XIN pad and the RESET signal of the second PHY can be released.

| PHY Port 1 |  |

|------------|--|

| VDD        |  |

| XI Clock   |  |

| RESET_N    |  |

| CLK_OUT    |  |

| PHY Port 2 |  |

| VDD        |  |

| XI Clock   |  |

| RESET N    |  |

Figure 2-5. DP83867 Reset Generation

The reset generation of the PHY cannot be controlled by the a single GPIO from the application processor because of the reset sequence. Hence this TI design used two dedicated GPIO port from the application processor to control the RESET signal of the two PHYs. Each GPIO is combined with a SN74LVC1G08 AND gate of the PORZ signal from the PMIC to enable a common system reset. In case only a single GPIO signals is available from the processor, then the designer can choose to use the PORZ signal for the first PHY only and only reset the second PHY with a combination of GPIO and PORZ signal.

When selecting another GPIO for controlling the RESET signal, please choose them with low after the processor power on reset to keep the PHYs in reset state until the power supply has been enabled.

#### 2.4.5 DP83867 and AM5728 Bootstrap Consideration for Mid-Voltage Levels

The DP83867IR is configured through bootstrap mode during power-on-reset. At power-on-reset the DP83867IR latches a user defined voltage level at a set of dedicated bootstrap input pins. The DP83867IR supports 4 voltage levels for bootstrap configuration. With each of the voltage level a dedicated configuration mode is set, for example, full-duplex or half-duplex operation mode, configuration of the MDIO address and others. The voltage levels detected by the DP83867IR are 0 V (Mode 1), 1.4 V (Mode 2), 2.4 V (Mode 3) and 3.3 V (Mode 4). Especially 1.4 V (Mode 2) and 2.4 V (Mode 3) are referred as mid-voltage level in the following description.

The AM5728 processor has a constrain with exposed to mid-voltage levels, which has an effect o the power-onhour (POH) lifetime. The AM5728 exposure to mid-voltage levels time should be avoided and the voltage level have to be kept either above Vhmin or below Vlmax as specified in the AM572x Sitara<sup>TM</sup> Processors Silicon Revision 2.0 data sheet.

Typically the mid-voltage levels are present in the system during power up of the devices. Because the AM5728 has configured many of its pads as input after system reset, the AM5728 is exposed to the mid-voltage levels before the bootloader and application reconfigure those pins in the correct operation mode.

This TI design uses only Mode 1 or Mode 4 as bootstrap configuration modes for the DP83867IR PHY to avoid mid-voltage levels. One of the bootstrap configurations is configure individual MDIO addresses for each PHY. All remaining PHY configuration is performed over MDIO access once the PHY is released out of reset. Using this approach eliminates the need for additional buffers to isolate the AM5728 pads from the DP83867 pads to avoid mid-voltage levels.

In case the system design requires mid-voltage level, the use of buffers is required which isolates the midvoltage level for the DP83867IR bootstrapping to be seen AM5728 pad. Please refer to TIDA-00299 on how the buffers can be added to the system design.

The DP83867IR PHY register configuration over MDIO interface is part of this TI Design.

#### 2.4.6 Reduced Gigabit Media Independent Interface (RGMII)

The DP83867IR has integrated termination resistors in the RXD data lines, which are RX\_D0, RX\_D1, RX\_D2, RX\_D3, RX\_CLK and RX\_CTRL. Therefore there are no external line driver resistors needed to be added on the PCB between the DP83867IR and the AM5728. The DP83867IR has control registers to adjust the drive strength of the RXD data lines to control the voltage slope for voltage under- and overshoot.

The TXD data lines, which are TX\_D0, TX\_D1, TX\_D2, TX\_D3, TX\_CLK and TX\_CTRL have line driver resistors of 22  $\Omega$  added between the DP83867IR and the AM5728.

During the trace length have of the RXD as well as the TXD have to be matched. For more details, see the *DP83867IR Robust, Low Power 10/100/1000 Ethernet Physical Layer Transceiver* data sheet and TI Design TIDA-00204.

The line driver resistors in the TXD path have to get placed as close as possible to the AM5728 pins to be effective.

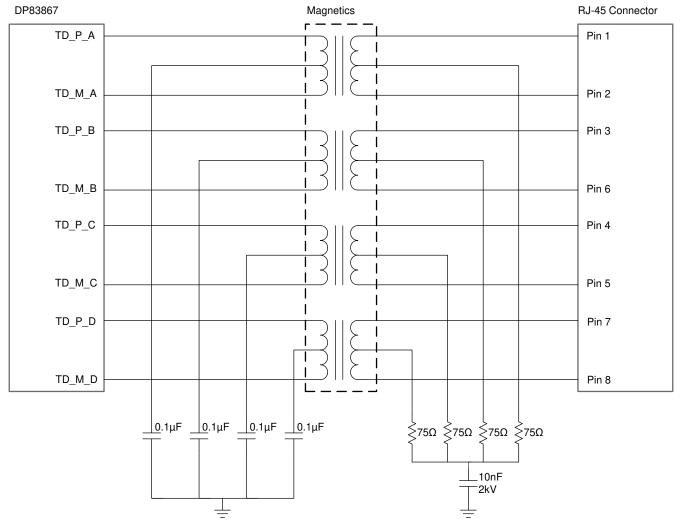

#### 2.4.7 Media Dependent Interface (MDI)

The MDI interface is connects the DP83867IR to the transformer and the RJ45 connector. There is no need to place external termination resistors for the MDI interface as the he MDI interface of the DP83867IR has integrated termination resistors. The magnetic can be placed separately or they can be integrated into the RJ45 connector.

There are a variety of RJ45 connector with integrated magnetic. Typically the integrated magnetic can have a variety of configurations of resistor and capacitor connects. It is important to select the magnetic according , hence make sure to select a magnetic that follows the DP83867IR data sheet recommendations.

Figure 2-6. Magnetics Connections

There are solutions with the transformer integrated into the RJ45 connector as well as separate transformer and RJ45 connectors. This TI design uses an integrated transformer into the RJ45 connector. The TIDA-00204 shows an example of separate transformers. Use a length matching of each MDI pair as well as to the pairs itself.

Specific care has to be taken when routing the traces of the MDI lines and signal pairs. They PCB traces must be length matched.

Texas

www.ti.com

Lastly, ESD protection devices TPD1E05U06 are added between the DP83867IR and transformer to prevent ESD strikes to reach the DP83867IR device.

#### 2.4.8 RJ45 Port With Integrated Magnetic and Status LEDs

The magnetic on the MDI interface between the DP83867IR and the RJ45 port can either be external (they need to be placed on the PCB between the DP83867IR and the RJ45 connector) or they can be integrated into the RJ45 connector. Similar options are available for the status LEDs, and it is up to the system requirements to choose the appropriate solution. The benefits of external magnetic and status LEDs are a higher immunity against EMI.

This TI design used integrated magnetic and status LEDs. For a TI design reference with external magnetic please refer to TIDA-00204.

#### 2.5 Gigabit Ethernet Solution Comparison

This section compares the TI DP83867IR solution against the KSZ9031 solution.

| FUNCTION                       | DP83867IR                      | KSZ9031                           | COMMENT                                                |  |  |  |  |  |  |  |  |  |

|--------------------------------|--------------------------------|-----------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Voltages                       | 3.3 V, 2.5 V, 1.0 V            | 3.3 V, 1.2 V                      | 2 × DP83867IR                                          |  |  |  |  |  |  |  |  |  |

| Voltage generation             | PMIC, DC/DC                    | DC/DC, LDO<br>(FDT434P), inductor | LDO is not power efficient and uses bigger board space |  |  |  |  |  |  |  |  |  |

| RGMII TX termination resistors | Integrated                     | External termination resistors    | External resistors require more board space            |  |  |  |  |  |  |  |  |  |

| Power consumption              | 467 mW                         | 621 mW                            | LDO losses of KSZ9031 are not part of the calculation  |  |  |  |  |  |  |  |  |  |

| Clock generation               | Single XTAL                    | Two 25-MHz crystals               | Two crystals require more board space                  |  |  |  |  |  |  |  |  |  |

| MDI Interface                  | Integrated ESD protection      | NA                                | -                                                      |  |  |  |  |  |  |  |  |  |

| PHY boot strapping             | Minimum bootstrapping required | Y                                 | -                                                      |  |  |  |  |  |  |  |  |  |

#### Table 2-1. Comparison of the DP83867IR and KSZ9031 Solutions

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

## 3.1.1 Hardware

The following hardware components are required to validate the Ethernet functionality

- TIDA-010010 AM5728 EVM with two DP83867IR Ethernet PHYs

- Multi-meter

- Oscilloscope

- Windows PC with two Gbit Ethernet ports

- Ethernet cables CAT5e or better quality to support 1000 Mbps Ethernet

#### 3.1.2 Software

The following software components are required to validate the Ethernet functionality

- Code Composer Studio 7.4 or higher

- Processor SDK RTOS for AM572x

- Ethernet packet sniffer (for example, Wireshark)

- Ethernet packet generator (for example, Colasoft Packet Builder 2.0)

- Test application project *EMAC\_DP83867\_evmAM572x*

#### 3.1.2.1 Power Supply for DP83867IR

The DP83867IR requires 3 voltages: 3.3 V, 2.5 V and 1.0 V. The 3.3-V voltage is generated by the DC/DC converter TPS54531D after board power is enabled by TPS6590378 PMIC. The 2.5 V and 1.0 V voltages are generated by the TPS6590378 PMIC through the integrated DC/DC converters SMPS7 (2.5 V) and SMPS9 (1.0 V). The SMPS7 and SMPS9 rails need to get configured and enabled by the application software.

The TPS6590378 PMIC is programmed over the I2C interface. The Processor SDK RTOS provides a chip support library (CSL) to read and write from the PMIC device over the I2C interface.

The function *dp83867\_pmic\_init()* in file phy\_init.c configure and enable the 2.5-V and 1.0-V voltages output in the PMIC.

```

void dp83867 pmic init(void)

{

const pmhalPmicOperations t *pmicOps;

uint32 t

retVal;

/* Register the I2C functions with the PMIC Communication to ensure the

PMIC can be communicated with I2C driver

PMHALI2CCommRegister(&gPmicI2cfunc);

pmicOps = PMHALTps659037GetPMICOps();

retVal = PMHALPmicRegister(pmicOps);

if(retVal != 0)

return;

/* enable the PHY voltage supplies */

PMHALPmicSetRegulatorVoltage(PMHAL PRCM PMIC REGULATOR EPHY2V5,2500, PM TIMEOUT INFINITE, FALSE);

PMHALPmicSetRegulatorVoltage(PMHAL_PRCM_PMIC_REGULATOR_EPHY1V0,1000,PM_TIMEOUT_INFINITE,FALSE);

PMHALPmicEnableRegulator(PMHAL_PRCM_PMIC_REGULATOR_EPHY2V5);

PMHALPmicEnableRegulator(PMHAL_PRCM_PMIC_REGULATOR_EPHY1V0);

}

```

#### 3.1.2.2 DP83867IR Reset Sequence

The two DP83867IR requires a reset sequence as described here

The application software controls the signals GPIO5\_17 and GPIO3\_29 to perform the RESET sequence for the two DP83867IR. The application software first sets both GPIOs to '0' to set both DP83867IR into RESET state. After 1 $\mu$ s the application software releases the RESET for the first DP83867IR. It takes approximately 200 ms (worst case) for the first PHY to output the 25-MHz clock on its CLK\_OUT pin. After this wait time the application software releases the RESET for DP83867IR.

The function *dp83867\_reset\_sequence()* in file phy\_init.c performs the reset sequence as previously described.

```

void dp83867 reset sequence(void)

{

uint32 t regVal = 0;

/* configure GPIOs as outputs*/

/* pinmux */

/* AM572x EVM GPIO5 17 RESET PHY1 */

CSL FINS(regVal, CONTROL CORE PAD IO PAD RMII MHZ 50 CLK RMII MHZ 50 CLK MUXMODE, 0xEU);

((CSL_padRegsOvly) CSL_MPU_CORE_PAD_IO_REGISTERS_REGS)->PAD_RMII MHZ 50 CLK = regVal;

/* AM572x EVM GPIO3 29 RESET PHY2 */

CSL FINS(regVal, CONTROL CORE PAD IO PAD VIN2A DEO VIN2A DEO MUXMODE, 0×EU);

((CSL_padRegsOvly) CSL_MFU_CORE_PAD_TO_REGISTERS_REGS)->PAD_VIN2A_DE0 = regVal;

/* configure GPIO */

GPIO init();

/* Reset sequence: lus reset asserted; then first PHY needs to wait for 201 ms before second

PHY comes out of reset */

GPIO_write(0, 0); /* set GPIO5_17 to low */

/* set GPIO3_29 to low */

GPIO_write(1, 0);

/* wait 8 us*/

delay(1);

GPIO_write(0, 1); /* set GPIO5_17 to high */

/* wait 201 ms */

delay(201*125);

GPIO write(1, 1); /* set GPIO3 29 to high */

}

```

#### 3.1.2.3 DP83867IR Configuration Over MDIO

The TI design applies only a minimum bootstrap resistors to configure the DP83867IR. All additional register configuration is performed over the MDIO interface by the application software.

The initial DP83867IR register configuration is performed by function ENETPHY\_Init() in file enet\_phy.c.

```

int32_t ENETPHY_Init(ENETPHY_Handle hPhyDev, uint32_t miibase, uint32_t inst, uint32_t PhyMask,

uint32 t MLinkMask, uint32 t MdixMask, uint32 t PhyAddr, uint32 t ResetBit, uint32 t MdioBusFreq,

uint32 t MdioClockFreq,int32_t verbose)

{

uint32 t *PhyState = &((ENETPHY DEVICE *) hPhyDev)->PhyState;

int32 t ret =0 ;

uint32_t phy;

((ENETPHY_DEVICE *) hPhyDev)->miibase

= miibase;

((ENETPHY_DEVICE *) hPhyDev)->inst

((ENETPHY_DEVICE *) hPhyDev)->PhyMask

= inst;

= PhyMask;

((ENETPHY_DEVICE *) hPhyDev)->MLinkMask = MLinkMask;

((ENETPHY_DEVICE *) hPhyDev)->MdixMask = MdixMask;

*PhyState &= ~ENETPHY MDIX MASK; /* Set initial State to MDI */

CSL MDIO setClkDivVal((CSL mdioHandle) ((ENETPHY DEVICE *) hPhyDev)->miibase, (MdioBusFreq/

MdioClockFreq - 1));

CSL MDIO enableFaultDetect((CSL mdioHandle) ((ENETPHY DEVICE *) hPhyDev)->miibase);

CSL_MDIO_disablePreamble((CSL_mdioHandle) ((ENETPHY_DEVICE *) hPhyDev)->miibase);

CSL_MDIO_enableStateMachine((CSL_mdioHandle) ((ENETPHY_DEVICE *) hPhyDev)->miibase);

ENETPHY UserAccessRead(hPhyDev, ENETPHY BMCR, PhyAddr, &phy);

phy |= DP AUTO NEGOTIATION ENABLE | DP DUPLEX MODE;

ENETPHY UserAccessWrite(hPhyDev, ENETPHY_BMCR,PhyAddr,phy);

ENETPHY_UserAccessRead(hPhyDev, ENETPHY_ANAR, PhyAddr, &phy);

phy |= DP_TX_FD | DP_TX | DP_10_FD | DP_10BASETE_EN;

ENETPHY_USerAccessWrite(hPhyDev, ENETPHY_ANAR, PhyAddr, phy);

ENETPHY_UserAccessRead(hPhyDev, ENETPHY_CFG1, PhyAddr, &phy);

phy |= DP 1000BASE T FULL DUPLEX | DP 1000BASE T HALF DUPLEX;

ENETPHY UserAccessWrite(hPhyDev, ENETPHY CFG1, PhyAddr, phy);

/* disable clock out of second PHY */

if(PhyAddr != 0)

{

ENETPHY UserAccessRead(hPhyDev, ENETPHY IO MUX CFG, PhyAddr, &phy);

phy \&= \overline{~}(DP CLK O DISABLE);

ENETPHY UserAccessWrite (hPhyDev, ENETPHY IO MUX CFG, PhyAddr, phy);

}

```

```

/* set RGMII Delay Control Register TX Delay) */

ENETPHY_UserAccessRead(hPhyDev, ENETPHY_RGMIIDCTL, PhyAddr, &phy);

phy &= ~(0xF<<4);

phy |= 0x3<<4; /* set RGMII_TX_DELAY_CTRL to 1.00 ns */

ENETPHY_UserAccessWrite(hPhyDev, ENETPHY_RGMIIDCTL, PhyAddr, phy);

(void)ResetBit; /* suppress warning */

*PhyState=INIT;</pre>

```

```

return ret;

}/* end of function ENETPHY_Init*/

```

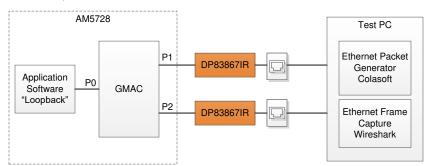

# 3.1.3 2 Gigabit Ethernet (GMAC) Peripheral

The GMAC is a peripheral inside the AM5728 application processor. It is a 2-port switch with two physical ports connector to the two DP83867IR Ethernet PHYs and one internal host port. The host port is named P0 and the two physical ports are named P1 and P2. When the application software sends a broadcast Ethernet frame into the GMAC via port P0, the GMAC will send out this broadcast Ethernet frame both ports, P1 and P2. Similar to when a broadcast frame is either received from port P1 or P2, the GMAC will send it out on P0 and P2 or P1. Please refer to the AM5728 technical reference manual (TRM) for additional information about the GMAC peripheral.

The application software configures the GMAC through the CSL library. The GMAC example with DP83867OIR is based on the example project *EMAC\_BasicExample\_evmAM572x\_armBiosExampleProject* from the Processor SDK RTOS. The example demonstrates how to receive and transmit Ethernet frames without any TCP/IP stack and is best suited for DP83867IR and AM5728 solution validation.

# 3.2 Testing and Results

The testing of this design focuses on receiving and transmitting of Ethernet frames. The test PC transmits broadcast Ethernet frame to Ethernet Port P1 (or P2). Each broadcast frame is transmitted by the GMAC to P0 and P2 (or P1). The application software send any received Ethernet frame back to P0 (Ethernet application loopback). Each frame transmitted from the test PC is received twice on both Ethernet Ports P1 and P2 and once at the host port P0. For validation the test PC sends out a known number of broadcast frames. The reception is confirmed by the Ethernet Tools Wireshark on the PC and with the RX/TX statistics in the GMAC peripheral.

#### 3.2.1 Test Setup

Figure 3-1 shows the test setup.

Figure 3-1. Test Setup

#### 3.2.2 Test Results

#### 3.2.2.1 Ethernet Frame Generation

The Ethernet frame generator on the test PC 1 generates 10,000 Ethernet frames (size 1500 bytes). Figure 3-2 shows the configuration.

| File Edit Send Help                                       |                          |                                                                                                                 |         |                              |                              |                        |           | and the second se |

|-----------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|---------|------------------------------|------------------------------|------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           |                          | - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 - 1990 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Import Export - Add Insert Copy Paste Delete Mov          |                          | Send Send All.                                                                                                  | Adapter | Ø<br>About                   |                              |                        | 2         | Colasoft <sup>®</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 🞯 Decode Editor                                           |                          | Packet No. 2                                                                                                    | Pack    | et List                      |                              |                        | Packets 2 | Selected 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Packet Info:                                              |                          | *                                                                                                               | No.     | Delta Time                   | Source                       | Destination            | Protocol  | Size Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - Packet Number:                                          | 000002                   |                                                                                                                 | 1       | 0.100000                     | 01:02:03:03:02:01            | FF:FF:FF:FF:FF:FF      | ARP Reg.  | . 64 Who                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - Packet Length:                                          | 1,500                    |                                                                                                                 | -       | A CONTRACTOR OF A CONTRACTOR | 192.168.0.1:0                | 192.168.0.255:0        | UDP       | 1.500 Src=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| - @ Captured Length:                                      | 1,496                    |                                                                                                                 | 2       | 0.100000                     | 192.168.0.1:0                | 192.166.0.25510        | UDP       | 1,500   Src=                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Delta Time                                                | 0.100000 Second          |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ethernet Type II                                          | [0/14]                   |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Destination Address:                                      | FF:FF:FF:FF:FF:F         | F [0/6]                                                                                                         | San     | d Selected Pac               | kots                         |                        | X         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - By Source Address:                                      | 01:02:03:02:01:0         | 1 [6/6]                                                                                                         | Sen     | u selecteu raci              | Kets                         |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Protocol:                                                 | 0x0800                   | (Interne                                                                                                        |         | Options                      |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| E IP - Internet Protocol                                  | [14/20]                  |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - Version:                                                | 4 [14/1] 0xF0            |                                                                                                                 |         | Adapter: USB3                | 3.0 to Gigabit Ethernet Adap | ot 🔛                   | Select    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - Header Length:                                          | 5 (20 Bytes) [           | 14/1] 0x0F                                                                                                      |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 😑 🐵 Differentiated Services Field:                        | 0000 0000 [15/1          | ] OxFF                                                                                                          |         | Burst Mode (r                | no delay between packets)    |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - Differentiated Services Codepoint:                      | 0000 00 [15/1            | ] OxFC                                                                                                          |         |                              | 10000 🌩 loo                  |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -• Transport Protocol will ignore the C                   | E (Igno                  | re) [15/1]                                                                                                      |         | Loop Sending                 | 10000 1000                   | ops (zero for infinite |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -Q Congestion:                                            | (No C                    | Congestion)                                                                                                     |         | Dolay Robyon                 | en Loops: 0 🎒 mill           | transmanda.            |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -P Total Length:                                          | 1000                     | (1000 Bytes)                                                                                                    |         | Deidy betwee                 | min coops.                   | iseconus               |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - PIdentification:                                        | 0x0000                   | (0) [18/2]                                                                                                      |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B @ Fragment Flags:                                       | 010 (Don'                | t Fragment)                                                                                                     |         | Sending Informat             | ion                          |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -0 Reserved:                                              | 0 [20/1                  | ] 0x80                                                                                                          |         | rending informat             | 1011                         |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - Fragment:                                               | .1                       | (Don't Fragm                                                                                                    |         | Total Packets:               | 1 * 10000 = 10000            |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -O More Fragment:                                         | 0 (Last                  | Fragment)                                                                                                       |         | i otar i otarotori           | 1 10000 10000                |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pragment Offset:                                          | 0 [20/2] 0x1FE           | 'F                                                                                                              |         | Packets Sent:                | 10000                        |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| @ Time To Live:                                           | 64                       | [22/1] +                                                                                                        |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| * III                                                     |                          | •                                                                                                               |         | Progress:                    | <b>3</b> -                   |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Hex Editor                                                | Total 1.496 bytes S      | election 2 bytes                                                                                                | r   -   |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                           | 00 00 40 1E              |                                                                                                                 | 4       |                              | Start                        | Stop Close             | Help      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0015 00 40 11 B4 B4 C0 A8 00 01 C0 A8 00 FF 00 00 00 00 0 | 00 1A 79 AF .0           | y.                                                                                                              |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 002A 00 00 00 00 00 00 00 00 00 00 00 00 00               |                          |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                           |                          |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0069 00 00 00 00 00 00 00 00 00 00 00 00 00               | 00 00 00 00              |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                           |                          |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0093 00 00 00 00 00 00 00 00 00 00 00 00 00               |                          | *****                                                                                                           |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 00BD 00 00 00 00 00 00 00 00 00 00 00 00 00               |                          |                                                                                                                 |         |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 00D2 00 00 00 00 00 00 00 00 00 00 00 00 00               | 00 00 00 00 <sup> </sup> | *                                                                                                               | -       |                              |                              |                        |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                                                         |                          | P                                                                                                               | *       |                              |                              | III                    | 17        | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 3-2. Colasoft® Packet Builder GUI - Configuration

#### 3.2.2.1.1 GMAC Statistics Registers

Figure 3-3 shows the RX statistics. The GMAC statistics shows that it received 10,000 (0x2710 hex) good frames.

| Disassem bly    |                            |   |

|-----------------|----------------------------|---|

|                 | 🤹 🕶 🕶 🗢 🖓 🚱 📑 🖻            | 1 |

| 0x48484900      | 122                        |   |

| x48484900 < M   | emory Rendering 2> 🔀       |   |

| 32-Bit Hex - TI | Style 🗸 🗑                  |   |

| 0x48484900      | STATS GOOD RX FRAMES       | ~ |

| 0x48484900      |                            |   |

| 0x48484904      | STATS_BROADCAST_RX_FRAMES  |   |

| 0x48484904      | 00002710                   |   |

| 0x48484908      | STATS MULTICAST RX FRAMES  |   |

| 0x48484908      | 0000000                    |   |

| 0x4848490C      | STATS_PAUSE_RX_FRAMES      |   |

| 0x4848490C      | 0000000                    |   |

| 0x48484910      | STATS_RX_CRC_ERRORS        |   |

| 0x48484910      | 0000000                    |   |

| 0x48484914      | STATS_RX_ALIGN_CODE_ERRORS |   |

| 0x48484914      | 0000000                    | 1 |

| 0x48484918      | STATS_OVERSIZE_RX_FRAMES   |   |

| 0x48484918      | 0000000                    |   |

| 0x4848491C      | STATS_RX_JABBERS           |   |

| 0x4848491C      | 0000000                    |   |

| 0x48484920      | STATS_UNDERSIZE_RX_FRAMES  |   |

| 0x48484920      | 0000000                    |   |

| 0x48484924      | STATS_RX_FRAGMENTS         | v |

Figure 3-3. GMAC RX Statistics

Figure 3-4 shows the TX statistics. The GMAC statistics shows that it transmitted 30,000 (0x7530 hex) good frames. This amount splits up in port P2 transmitting the frames received from the test PC at port P1, and port P1 and P2 transmitting the loopback frames from the application software on P0.

| 0x48484900      | 50                                      |      |

|-----------------|-----------------------------------------|------|

| x48484934 - 0x  | 48484900(+0x34) < Memory Rendering 2> 🔀 |      |

| 32-Bit Hex - TI | Style 🗸 📾                               |      |

| 0x48484934      | STATS_GOOD_TX_FRAMES                    | ^    |

| 0x48484934      | 00007530                                |      |

| 0x48484938      | STATS_BROADCAST_TX_FRAMES               |      |

| 0x48484938      | 00007530                                |      |

| 0x4848493C      | STATS MULTICAST TX FRAMES               |      |

| 0x4848493C      | 0000000                                 |      |

| 0x48484940      | STATS PAUSE TX FRAMES                   |      |

| 0x48484940      | 0000000                                 |      |

| 0x48484944      | STATS_DEFERRED_TX_FRAMES                |      |

| 0x48484944      | 0000000                                 |      |

| 0x48484948      | STATS COLLISIONS                        |      |

| 0x48484948      | 0000000                                 |      |

| 0x4848494C      | STATS_SINGLE_COLLISION_TX_FRAMES        |      |

| 0x4848494C      | 0000000                                 |      |

| 0x48484950      | STATS_MULTIPLE_COLLISION_TX_FRAMES      |      |

| 0x48484950      | 0000000                                 |      |

| 0x48484954      | STATS_EXCESSIVE_COLLISIONS              |      |

| 0x48484954      | 0000000                                 |      |

| 0x48484958      | STATS_LATE_COLLISIONS                   | 1.20 |

Figure 3-4. GMAC RX Statistics

#### 3.2.2.2 Test PC Received Frames

Figure 3-5 shows the Ethernet frame captured on one Ethernet port of a total of 20,000 Ethernet frames.

| e <u>E</u> c | dit <u>V</u> iew   | Go                 | Cap          | ture  | Ar      | nalyz | e <u>S</u> | tati      | tics | Te       | leph   | ony   | N      | ireles | ss <u>T</u> o | ools <u>H</u> | elp  |        |        |     |            |       |    |      |              |         |    |

|--------------|--------------------|--------------------|--------------|-------|---------|-------|------------|-----------|------|----------|--------|-------|--------|--------|---------------|---------------|------|--------|--------|-----|------------|-------|----|------|--------------|---------|----|

|              | 2                  | 1. 1               | X            | 3     | ٩       | ٠     | ٠          |           | •    | ۲        |        |       | 0      | 0      | Q             | 11            |      |        |        |     |            |       |    |      |              |         |    |

| Apply        | a display filt     | :er <              | Ctrl-/       | >     |         |       |            |           |      |          |        |       |        |        |               |               |      |        |        |     |            |       |    | E    | <b>) •</b> E | xpressi | on |

|              |                    | Time               |              |       | Sou     | rce   |            |           |      |          |        | Desti | inatio | on     |               |               | Pro  | otocol | Length | Inf | 0          |       |    |      |              |         |    |