# Design Guide: TIDA-01027 Low-noise power-supply reference design maximizing performance in 12.8-GSPS data acquisition systems

# Texas Instruments

# Description

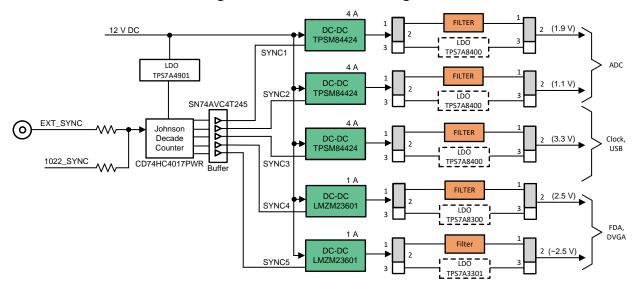

Applications requiring high-speed, multi-GSPS data acquisition (DAQ) must include an efficient, low noise point-of-load (PoL) power supply design that is capable of preserving the native analog front end (AFE) signal chain performance. The AFE power supply will often include multiple supply rails powered from a main bus. Since multiple free-running DC/DC converters can generate frequency components causing both conductive and radiated noise, potentially affecting signal chain performance, it is paramount that the power supply design minimize any signal chain impact. The reference design demonstrates an efficient, low noise 5-rail power-supply design for very high-speed DAQ systems capable of > 12.8 GSPS. The power supply DC/DC converters are frequency synchronized and phase-shifted in order to minimize input current ripple and control frequency content. Furthermore, any potential radiated electromagnetic interference (EMI) is minimized by using TI's high performance *HotRod*<sup>™</sup> packaging technology.

#### Resources

TIDA-01027, TIDA-01022 TPSM84424, LMZM23601 CD74HC4017 TPS7A84, TPS7A8300, TPS7A33, TPS7A49 TSW14J57EVM, TSW14J56EVM Design Folder Product Folder Product Folder Product Folder Tool Folder

ASK Our E2E<sup>™</sup> Experts

FILTER 12 V DC (1.9 V) - 100 -TPS7A8400 SYNC LDO TPS7A4901 2 (1.1 V) SYNC ī po SN74AVC4T245 TPS7A8400 FILTER 2 (3.3 V) ₿ Counte - 100 1022\_SYNC TPS7A8400 (2.5 V) DC I MZN SYNC LDO TPS7A8300 Filter (-2.5 V) MZM236 LDO TPS7A3301

#### Features

- Efficient, low-noise, point-of-load DAQ power supply for very high-speed AFE

- Phase-shifted DC/DC converter clocks to reduce inrush current and power-supply noise

- External frequency sync to manage DC/DC converters spurs

- Configure output with ability to bypass each LDO and use just the DC/DC converter and filter

- Used with TIDA-01022 and TIDA-01028 to show the impact on a 12.8 GSPS AFE with 9 GHz of analog BW

#### Applications

- High-Speed DAQ (DAQ)

- High-Performance Oscilloscope (DSO)

- Wireless Communication Test Equipment (WCTE)

- RADAR, Non-Military Land Mobile Radio

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

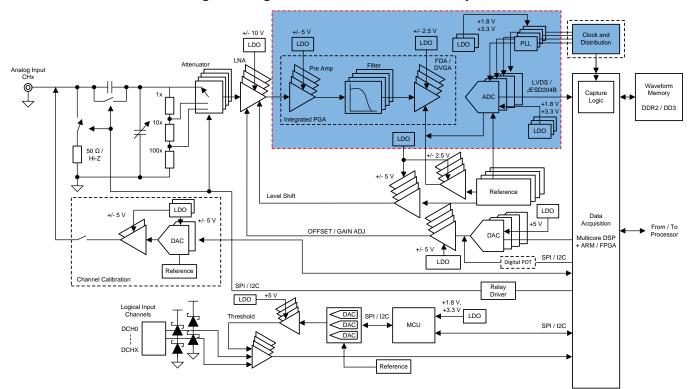

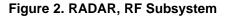

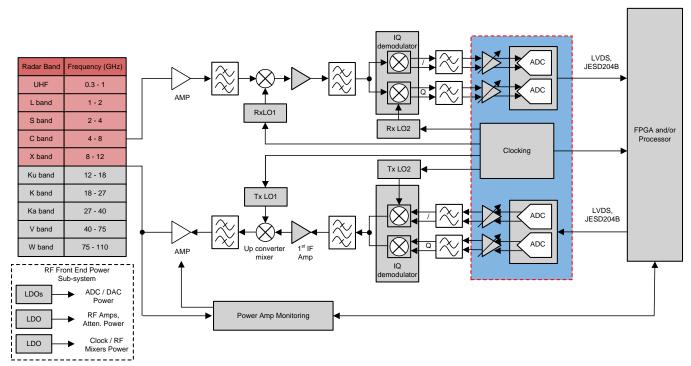

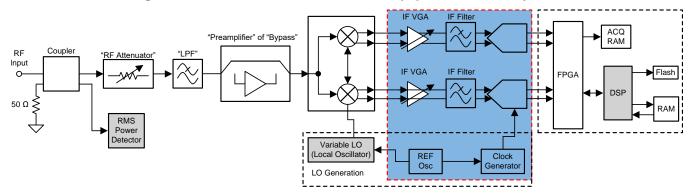

Multichannel, high-speed, GSPS data acquisition (DAQ) applications such as a digital storage oscilloscope (DSO), phased-array radio detection and ranging (RADAR), multiple-input multiple-output (MIMO) wireless communication, and wireless communication tester equipment (WCTE) all require accurate phase-coherency between channels to effectively direct multi-antenna systems and for accurate data reconstruction. These complex, high-tech systems, illustrated in Figure 1, Figure 2, and Figure 3, consist of high-speed AFE, clocking, point-of-load (PoL) power, and calibration subsystems. This reference design focuses on the PoL power design of the AFE, highlighted in blue, and how to maximize efficiency and minimize any impact on the raw signal chain performance.

#### Figure 1. High-Performance DSO AFE Subsystem

#### Figure 3. Wireless Communication Test Equipment AFE Subsystem

System Description

www.ti.com

# 1.1 Key System Specifications

| PARAMETER                                | SPECIFICATIONS                                                                            | DETAILS         |

|------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|

| Input voltage range                      | 5 V to 17 V                                                                               | Section 2.2.3.1 |

| Total number of outputs                  | 5                                                                                         | Section 2.1     |

| Output voltage, maximum output current   | +1.9 V - 4 A, +1.1 - 4 A, +3.3 V - 4 A, +2.5 V - 1000 mA, -2.5 V - 800 mA (at 12-V input) | Section 2.2.3.1 |

| Efficiency                               | > 85% (DC/DC + Filter at 12-V input)                                                      | Section 3.2.2.3 |

| External frequency synchronization DC/DC | 750 kHz at 12-V input, 700 kHz to 1300 kHz at 5-V input                                   |                 |

| Connectors                               | 2.54-mm header and compatible with TIDA-01022 hardware                                    | Section 3.1.1   |

| Form factor                              | 107 mm × 25 mm (only DC/DC converters), 117.5 mm × 51 mm (PCB form factor)                | Section 3.1.1   |

# Table 1. Key System Specifications<sup>(1)</sup>

<sup>(1)</sup> See *Testing and Results* (Section 3.2) for more details.

#### 2 System Design Overview

By their very nature, these multichannel, high-precision applications require multiple (2 to > 1000) signal chains which demand both power and PCB-efficient design. The power demands and increased board density add the additional design challenge that the power supply components can interfere directly by either conductive or radiated energy, degrading the system's total effective number of bits (ENOB). Therefore, it is important the PoL power supply design be optimized for efficiency and noise. In this reference design we first consider power tree optimization for both supply and PCB efficiency. Next, we closely choose the DC/DC converters that will optimize efficiency for the given load, in this example, the TIDA-01022, TIDA-01028, 1–4 channel, 12 bit up to 12.8 GSPS AFE. As part of our converter selection, products that are known to limit EMI radiation are used. Finally, we consider the LDO efficiency and what impact, if any, it will have on the system ENOB if removed.

#### 2.1 Block Diagram

Figure 4 shows the simplified block diagram of this design. A 12-V input supply is bucked down to supply 5 separate AFE supplies using TI's efficient DC/DC converter modules. These supplies are used to power the FDA, DVGA, ADC, and clock, USB components of the AFE. Each converter output can be buffered by a low-noise LDO to help filter any supply ripple and noise within the bandwidth of the LDO. The LDO can be bypassed to measure the signal chain impact and efficiency improvement. To reduce inrush current, a Johnson counter is used to generate multi-phase, frequency synced clocks for the DC/DC converters. This not only reduces the amplitude, but also increases the effective beat frequency by the number of phases generated by the counter.

#### Figure 4. TIDA-01027 Block Diagram

#### 2.2 Design Considerations

This section describes different design challenges and their impact on the system performance. Noisereduction methods and their implementation is also discussed in this section.

#### 2.2.1 Design Challenges

**Efficiency and Thermal Performance**: A low-dropout regulator (LDO) between the switching regulator and the ADC is used to clean up the output noise and the switching-frequency spurs. However, this clean power-supply design comes at the expense of additional power consumption because the LDO requires headroom for the dropout voltage in order to function properly. Therefore, eliminating the low-noise LDO from this chain can bring significant power savings and also reduce the board space, heat, and cost of the design.

#### Power Supply Noise Sources:

- 1. Switching Noise: DC/DCs are the source for this noise

- Electromagnetic Interference(EMI): EMI is mainly categorized into two types, Conducted EMI and Radiated EMI.

- a. Conducted EMI: Common impedance coupling and parasitic are major contributing sources

- b. Radiated EMI: The main source is external high-frequency signals, but the effect of dl/dt and ringing nodes of the power supply may be significant

- 3. Thermal, Flicker Noise: DC/DC and LDO are source of this noise

#### Impact of Noise:

6

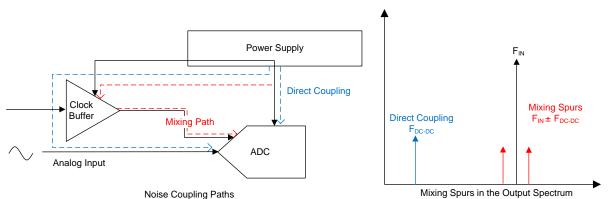

Impact noise in high-speed ADCs: Noise at the output power supply degrades performance of ADC (NSD, ENOB, and SFDR), as it directly couples to the ADC input path or to the clock path that generates spurs near to the input signal frequency. Figure 5 shows coupling paths of switching noise and its effect on the ADC output spectrum. For more information, see the *Designing a modern power supply for RF sampling converters analog application journal*.

#### Figure 5. Power Supply Noise Coupling Paths and its Effect on the ADC Output Spectrum

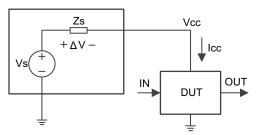

- 2. Impact of noise in clock generators: Noise floor and phase noise at the output of the clock generator is mainly affected due to two reasons:

- a. The change in the current demand of the clock generators: Figure 6 shows a simple setup with a clock generator and supply. As I<sub>CC</sub> changes, and the drop across Z<sub>s</sub> changes (that is,  $\Delta V$ ) this translates to changes in the supply V<sub>CC</sub> and is added as noise to the clock generator.

#### Figure 6. Simple Setup With Clock Generator and Supply

b. LDO output noise: The LDO output is regulated with respect to the LDO band gap reference. Any noise on the band gap is translated at the LDO output that contributes to phase noise and increases noise floor of the system.

For more information, see the Supply noise effect on oscillator phase noise application report.

- 3. Impact of noise in high-speed systems:

- Digitizers, high-speed DAQ, oscilloscopes: ENOB is used to evaluate the performance of digitizers. It summarizes noise and frequency response of a system. As it decreases, it makes timing measurement less accurate and decreases measurement precision.

- b. RADAR, SDR: Instead of the traditional ADC specifications(SNR, SFDR and ENOB), intermodulation distortion (IMD) and noise floor are used to evaluate the performance of RADARs. Noise increases intermodulation distortion and noise floor of the system that reduces maximum range and receiver sensitivity.

# 2.2.2 How to Mitigate Noise in High-Speed Systems

| NOISE REDUCTION OPTIONS                        | REDUCES<br>SWITCHING<br>NOISE | REDUCES<br>EMI | DEVICE<br>FEATURE | DESIGN<br>OPTION | IMPLEMENTED<br>ON THIS DESIGN | DESIGN THEORY     |

|------------------------------------------------|-------------------------------|----------------|-------------------|------------------|-------------------------------|-------------------|

| Spread Spectrum frequency modulation (SSFM)    |                               | 1              | 1                 |                  | x                             |                   |

| Clock synchronization pin                      | 1                             |                | 1                 |                  | 1                             | Section 2.2.3.4   |

| TI HotRod <sup>™</sup> or (FCOL QFN)           |                               | $\checkmark$   | 1                 |                  | 1                             |                   |

| Integrated inductor power module               |                               | $\checkmark$   | 1                 |                  | 1                             |                   |

| Slew rate control                              |                               | $\checkmark$   | 1                 |                  | x                             |                   |

| Pin optimization: Symmetric (butterfly) pinout |                               | $\checkmark$   | 1                 |                  | 1                             |                   |

| Slew rate control (RC snubber)                 |                               | $\checkmark$   |                   | х                | x                             |                   |

| Phase control                                  | 1                             | $\checkmark$   |                   | 1                | 1                             | Section 2.2.3.4   |

| Filtering: Discrete filter                     | √                             |                |                   | 1                | 1                             | Section 2.2.3.3.1 |

| Filtering: LDO                                 | 1                             |                |                   | 1                | 1                             | Section 2.2.3.3.2 |

#### **Table 2. Noise-Mitigating Options**

See Section 3.2.2.1 for the results after implementation of previously listed noise-reduction methods.

Table 2 shows different device and system noise mitigation options. The following explains mitigation options mentioned in the table and how they are implemented.

- 1. Device features:

- a. Frequency and Phase control

- i. Spread Spectrum frequency modulation (SSFM): This method varies switching frequency of converters, typically ±10%. The improvement in EMI is achieved by not allowing radiated energy to stay in the interested bandwidth for a significant length of time. To implement SSFM, the device should have the capability to track frequency change with regard to time. SSFM may improve EMI, but it is not a substitute for standard layout, filter, and shielding practices. For more information, see the *EE Times* article: *Frequency spreading provides switching-supply EMI insurance*.

- ii. Multiple Phase synchronization: This method applies to systems using two or more converters

and is achieved by externally supplying phase-shifted synchronized clocks to converters. The result is less noise, as the converters are running at different time intervals in a switching cycle. It also reduces the beating effect of converters, inrush current, and input-output capacitors size. The device should have an external synchronization feature to implement this method. For more information, see the *EE Times* article: *Synchronizing Makes for Well-Behaved Power Supplies*.

- b. Package

- i. Flip-chip on lead (FCOL QFN) or TI HotRod<sup>™</sup>: This package reduces switch-node ringing (one of the contributors to EMI). In this type of package, there are no wires to connect the IC to the lead frame. Solder bumps are placed on the IC die; the die is then flipped and attached to the lead frame. This helps to reduce parasitic capacitance and inductance. For more information, see the *TI* E2E<sup>TM</sup> article: Effects of IC package on EMI performance.

- ii. Integrated power modules: Integrated power modules include MOSFET and an inductor in a shielded package that helps to eliminate an EM coupling inductor from external sources. It simplifies the layout helping to reduce unwanted parasitic and current path compared to converter controllers. See the *Simplify low EMI design with power modules application report white paper* for more details.

To find the appropriate buck converter or to boost the power for your design, see to the following links: Buck Modules Integrated Inductor Boost Modules Integrated Inductor

Buck Boost Inverting Modules Integrated Inductor

- c. Slew rate: Slew rate control devices have independent control on the turn-on and the turn-off time of the high- and low-side MOSFET of the converter. This allows better control on the rise and fall time of the switching node, helping to reduce the ringing. For more information, see the *TI E*2*E*<sup>TM</sup> article: *How to use slew rate for EMI control*.

- d. Pin Optimization: The butterfly package of device helps designers reduce EMI using PCB layout. H-field due to high current paths can be cancelled, resulting in lower effective inductance and lower EMI. For more information, see the *TI E2E<sup>™</sup>* article: *How a DC/DC converter package and pinout design can enhance automotive EMI performance*.

- 2. System Design:

- a. Phase control: In this method, DC/DCs are operated with phase-shifted frequency synchronized clocks, to bring down EMI, switching noise, and di/dt. It is achieved by using an oscillator with programmable phase and frequencies.

- b. Slew rate control (as in RC snubber): Ringing at the DC/DC output can be reduced by using an RC snubber at the switching node of the DC/DC converter. However, it increases losses and reduces efficiency.

- c. Filtering: Noise due to power supply at the ADC input should be at least less than one-third of ADC noise floor. This is to ensure ADC performance is not limited by power supply. This is achieved with:

- i. Discrete Filter: For more information, see Section 2.2.3.3.1 of this design guide.

- ii. Linear Regulation: LDO is used to get the required power supply rejection ratio (PSRR) at ADC power supply to reduce switching noise of the DC/DC converters. To understand LDO PSRR in more detail, see the *Understanding power supply ripple rejection in linear regulators technical brief*.

# 2.2.3 Circuit Design

In this section, power supply design for high-speed ADC is described. Initially we start with DC/DC converter selection, and optimize power tree. This process is repeated for different DC/DC converters until it meets the efficiency and size requirements. Next, we select LDO or Filter to reject DC/DC output ripple and reduce power supply noise. In addition to this, multiphase frequency synchronization implementation is also discussed in this section. Finally, WEBENCH® Power Designer instructions are included.

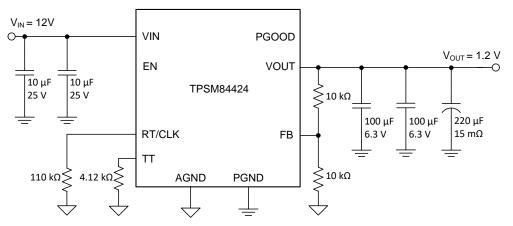

#### 2.2.3.1 DC/DC Converter Selection

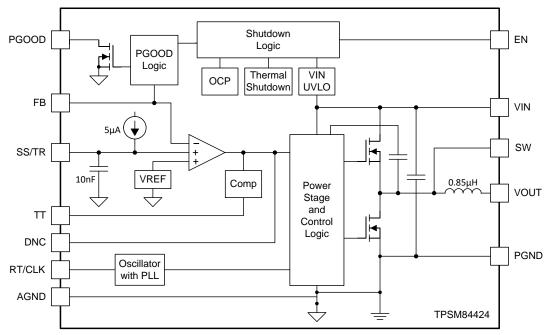

The WEBENCH® Power Designer is used to select DC/DC converters for this design. Section 2.2.3.5 has the steps for using this tool. The TPSM84424 device is selected for this design to generate +1.9 V, +1.1 V, and +3.3 V, as it has both small form factor and high efficiency(> 87% at 1.9-V, 2-A output for 12-V input). This device output voltage ripple is less than 10 mV with a 12-V input and 1.9-V, 2-A output load. It has an enable pin, Power Good output, and *External Sync* option, that fulfill the design requirements. Furthermore, it supplies up to 4 A and is part of the TPSM84x24 family that can provide 6 A and 8 A in the same package size and support output voltages from 0.6 V to 10 V.

Figure 7 shows the circuit diagram to generate +1.2-V power rail using the TSPM84424 device. The output voltage of the TPSM84424 device is externally adjustable using a two-resistor divider (RFBT and RFBB). An external sync signal is provided to the RT/CLK pin of the converter to set the switching frequency, that enables the management of potentially degrading power-supply-generated spurs. The +3.3-V, +1.9-V, and +1.1-V rails use the same device in similar circuit configurations. See the *TPSM84424* 4.5-V to 17-V input, 0.6-V to 10-V output, 4-A power module data sheet or use WEBENCH to select the values of components.

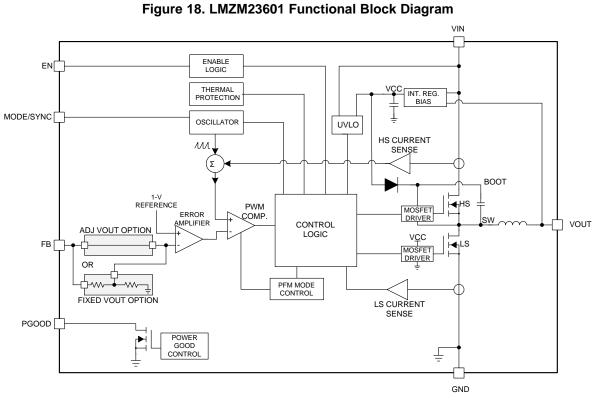

Figure 7. TPSM84424 Circuit Diagram

The LMZM23601 DC/DC converter is used to generate  $\pm 2.5$ -V rails that are required for the input amplifiers of the AFE. It can deliver up to 1000 mA and is used in inverting buck-boost topology to generate a -2.5-V rail. The maximum output current of the -2.5-V rail is less than lout<sub>max</sub>  $\times (1 - D)$  (where D is duty cycle of the converter). The output voltage of the LMZM23601 device is externally adjustable using a two-resistor divider (RFBT and RFBB). In this design, the amplifier inputs were bypassed and the signal was directly input to the ADC with the balun. As a result, the sync pin was not utilized. See the *LMZM23601 36-V, 1-A step-down DC/DC power module in 3.8-mm × 3-mm package data sheet* and *Inverting application for the LMZM23601 and LMZM23600 application report* for more details.

# 2.2.3.2 Power Tree Selection

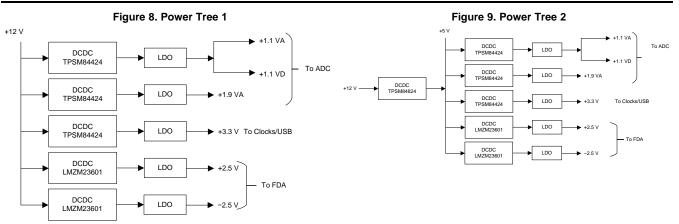

A DAQ system requires multiple rails to power the analog, digital, and mixed-signal circuits. The total system power requirement increases with the number-of-channels requirement. Therefore, select the power tree for high efficiency and small form factor. Figure 8 and Figure 9 show two different multi-channel power supply trees. To improve system efficiency, the input DC rail is down-converted using the DC/DC buck switching regulator and then regulated using a low-drop linear regulator as both Figure 8 and Figure 9 show.

#### System Design Overview

#### Table 3. Efficiency of Converters at Different Output Voltages

| CONVERTERS | I/P VOLTAGE | O/P VOLTAGE | LOAD  | SWITCHING FREQUENCY | EFFICIENCY |

|------------|-------------|-------------|-------|---------------------|------------|

| TPSM84424  | 5V          | 1.1 V       | 2.5 A | 400 kHz             | 92%        |

|            | 5V          | 1.9 V       | 2.0 A | 450 kHz             | 94%        |

|            | 5V          | 3.3 V       | 2.0 A | 1000 kHz            | 97%        |

|            | 12 V        | 1.1 V       | 2.5 A | 400 kHz             | 85%        |

|            | 12 V        | 1.9 V       | 2.0 A | 450 kHz             | 87%        |

|            | 12 V        | 3.3 V       | 2.0 A | 1000 kHz            | 92%        |

| LMZM23601  | 5 V         | 2.5 V       | 0.5 A | 1000 kHz            | 84%        |

|            | 5 V         | –2.5 V      | 0.5 A | 1000 kHz            | 84%        |

|            | 12 V        | 2.5 V       | 0.5 A | 1000 kHz            | 76%        |

|            | 12 V        | –2.5 V      | 0.5 A | 1000 kHz            | 76%        |

| TPSM84824  | 12 V        | 5 V         | 4 A   | 1200 kHz            | 94%        |

Using data from Table 3, the final efficiency of DC/DCs is calculated using Equation 1.

Efficiency(n) =  $\frac{\sum_{i=1}^{k}}{\sum_{i=1}^{k}}$

where

10

- k is the number of output rails

- P<sub>i</sub> is the output power of each rail

- n<sub>i</sub> is the efficiency of each output rail

(1)

The net efficiency of converters using the power-supply tree shown in Figure 8 = 86.6 %.

The net efficiency of converters using the power-supply tree shown in Figure 9 = 87.5 %.

**NOTE:** For calculation, the efficiency of the –2.5-V rail is assumed to be the same as the +2.5-V rail and the –2.5-V rail is generated using the LMZM23601 device in inverting buck-boost configuration.

The power-supply scheme in Figure 9 shows only 1% better efficiency than the power supply shown in Figure 8, but it uses an additional converter. Therefore, in this design the power-supply tree in Figure 8 is used.

# 2.2.3.3 DC/DC Ripple Rejection Using Filter or LDO

DC/DC converter selection is discussed in Section 2.2.3.1. However, AFE needs a low-noise power supply for good performance. Therefore we use LDO, Filter, or its combination after DC/DC converters. This section describes filter design and LDO selection for high-speed GSPS ADC. They are designed for rejection such that power supply spurs are less than the next spur in the given bandwidth. In the next paragraph, rejection calculation is explained.

The TPSM84424 device has an output voltage ripple less 12 mV at the 12-V input and 1.1-V, 2.5-A output load. For a -100 dBFS spur target and 800-mV full scale of ADC, the required voltage ripple and PSRR is calculated using Equation 2 and Equation 3. The required PSRR equals to 63 dB, for previously listed data. In general, a high-speed ADC does not have good PSRR. With sufficient decoupling capacitors, more than 20-dB PSRR is achieved. Therefore, to meet the design target, more than 40-dB PSRR is required. It can be achieved using LDO, or a filter, or an LDO + filter combination. The following subsections detail the filter and LDO circuit design to achieve PSRR > 40 dB. If the required rejection is not met by LDO or Filter, then its combination is used.

$V_{PPxdBFS} = V_{PP0dBFS} \times 10^{\text{Design Spur target(dBFS)/20}}$ (2) Required PSRR =  $20\log(\frac{V_{PP_source}}{V_{PPxdBFS}})$  (3)

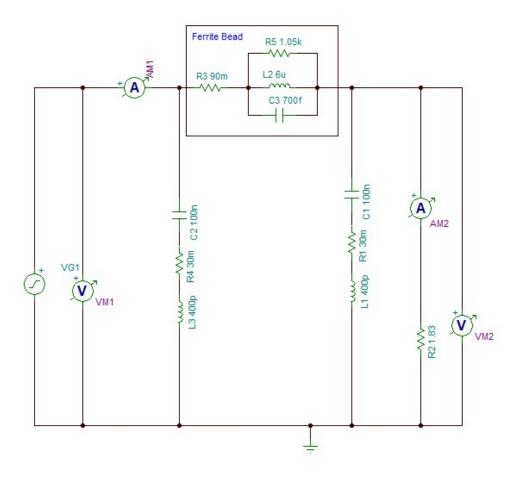

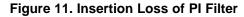

#### 2.2.3.3.1 Filter Design

A PI filter is used to filter DC/DC noise. The filter consists of a Ferrite bead (1000  $\Omega$  at 100 MHz, BLM41PG102SN1L) and two capacitors of 0.1  $\mu$ F. A filter is placed near the ADC, for each of its power rails. Figure 10 shows a ferrite bead equivalent circuit. It is modeled as R || L || C. The R, L, and C parameters are found from the impedance plot of the ferrite bead. Figure 11 shows the insertion loss plot of the filter at a 1.1-V, 600-mA load from simulation. It provides rejection of 50 dB at 750 kHz which meets the design requirement. A feedthrough capacitor (such as the NFM31PC276B0J3) is also considered in this design, which works best as an electromagnetic interference (EMI) filter. ESR and ESL reduces for this type of geometry, compared to an equivalent, similar-sized MLCCs. Hence, it provides 10-dB to 15-dB rejection even at high frequency around 100 MHz. The feedthrough capacitor is placed near the DC/DC converter.

Figure 10. PI Filter Simulation Circuit

# 2.2.3.3.2 LDO Circuit

increase it.

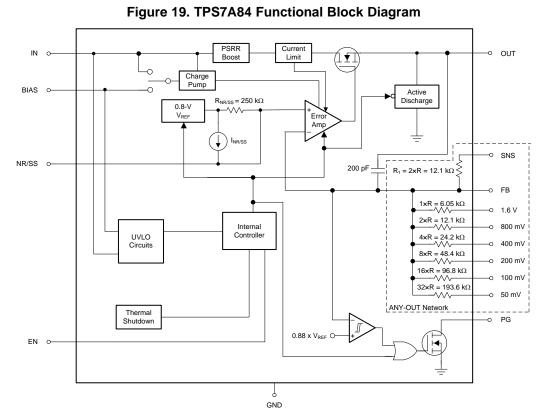

The TPS7A84 LDO is used in this design. This is a high PSRR, low-noise LDO, and has Power Good and enable pins. This device is provided for +3.3-V, +1.9-V, and +1.1-V power rails. It provides high PSRR up to 40 dB at 750 kHz, that meets the design requirement. If PSRR required is more, use a post PI filter to

This device has ANY-OUT<sup>™</sup> programmable pins to program the desired output voltage. The sum of the internal reference voltage (VREF = 0.8 V) plus the accumulated sum of the respective voltage is assigned to each active pin. The ANY-OUT pins (pin 10, pin 7, and pin 6) are programmed to active low to achieve 1.9 V at output. Figure 12 shows the LDO circuit.

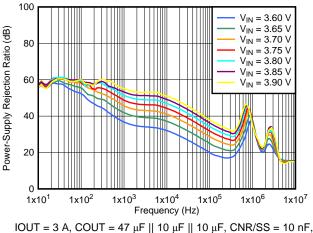

Figure 13 shows PSRR vs frequency of this LDO for different input voltages. For  $V_{IN} = 3.8$  V, LDO has PSRR of 40 dB at 500 kHz for 500-mV dropout voltage. And so we have set 500-mV LDO dropout for +3.3-V, +1.9-V, and +1.1-V power rails.

The TPS7A8300 and TPS7A33 devices are provided for  $\pm 2.5$ -V power rails. They both are ultra-low noise LDO capable of sourcing a maximum load of 1 A. The  $\pm 2.5$ -V rails are generated with output feedback resistors.

**NOTE:** The TPS7A84 device requires a bias voltage  $\ge 3.0$  V to operate if  $1.1 \text{ V} \le V_{IN} < 1.4$  V. This reference design does not have an option to supply the required bias voltage. Either the V<sub>IN</sub> must be greater than 1.4 V, or bias voltage must be applied externally.

#### Figure 12. TPS7A84 LDO Circuit to Generate +3.3 V

Figure 13. PSRR vs Frequency and  $V_{IN}$  for  $V_{OUT}$  = 3.3 V

System Design Overview

$1001 = 3 \text{ A}, \text{ COUT} = 47 \ \mu\text{F} \parallel 10 \ \mu\text{F} \parallel 10 \ \mu\text{F}, \text{ CNR/SS} = 10 \ \text{nF}, \text{CFF} = 10 \ \text{nF}$

#### System Design Overview

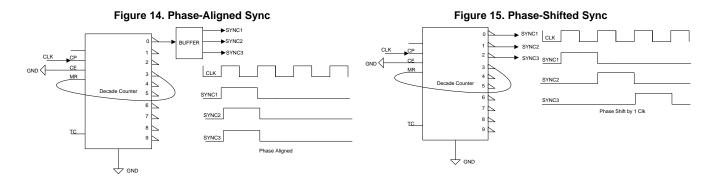

#### 2.2.3.4 Multi-Phase Sync Generation

As discussed in Section 2.2.2, phase control helps to bring down EMI, switching noise, and di/dt. The basic idea is to operate DC/DC converters at different time intervals in a switching cycle, that reduces di/dt, and results in reduction in EMI. Furthermore, frequency sync is used to manage DC/DC-generated spurs in the ADC output spectrum. Consequently, a digital filter can be implemented to remove these known spurs. Frequency sync also helps in eliminating noise due to beating effect of DC/DC converters. In this design, all DC/DCs are selected such that they support external frequency synchronization. The Sync signal is provided to a high-speed ring counter with decoded outputs. This generates phase-shifted and phase-aligned clock signals that are fed to the converters.

Figure 14 and Figure 15 show circuit diagrams to generate phase-aligned and phase-shifted sync pulses SYNC1, SYNC2, and SYNC3, respectively, for +1.9-V, +1.1-V and +3.3-V rails. In a phase-shifted sync scheme, sync signals are 120° phase apart. This reference design implements phase shifting of +1.9-V, +1.1-V, and +3.3-V rails, because  $\pm 2.5$ -V rails are powered down and the amplifier inputs were bypassed with the balun. Phase shifting also helps reduce input ripple current and input capacitance for DC/DC converters.

#### 2.2.3.5 WEBENCH® Power Designer Steps

In this design, the WEBENCH® Power Designer is used to design power rail circuits. The WEBENCH® environment gives us end-to-end power supply design capabilities that save time during all phases of the design process. The following steps are used to design a 1.9-V power rail circuit:

- 1. Go to WEBENCH® Power Designer

- 2. Select DC/DC Power Designs and Click on Start Design

- 3. Provide *Input Voltage Range, Output Voltage*, and *Max Output Current*. Using the *Advanced Options*, set the *Max Vout Ripple* and Nominal lout current parameters. Select one of the design considerations from *Balanced, Low cost, High Efficiency* and *Small Footprint*. In this design, the input voltage for DC/DC converters is 12 V, as most of the applications such as high-speed DAQ, oscilloscope, and so forth, use 12-V power rail to generate ADC power rails.

- 4. Agree to the Terms and Conditions of Use and Select View Designs

- 5. Apply filters to reduce the total number of designs. Figure 16 shows a list of power supply designs for a 1.9-V rail in WEBENCH, after the following filters are applied.

- a. Regulator type In this design, Module(Integrated Inductor) is selected

- b. Select IC features: This design requires converters to have Enable, Power Good, and SYNC pins.

- c. Select Design Attributes like efficiency, BOM Cost, Switching frequency, and so forth, if you have specific requirements.

| Select a Design                                                   | tput: 1.9 V at 2 A | Temp    | o: 30 °C C | hange           |                    |                  |                   | SELECT               |                          | CUS          | STOMIZE SIMULATE                                                                                             | EXPOR     |

|-------------------------------------------------------------------|--------------------|---------|------------|-----------------|--------------------|------------------|-------------------|----------------------|--------------------------|--------------|--------------------------------------------------------------------------------------------------------------|-----------|

|                                                                   |                    |         | 11 matchin | g designs out o | f 351 total de:    | signs            |                   |                      |                          |              | Select Additional Columns 🔻                                                                                  | CARD VIEW |

| Filters                                                           | CLEAR FILTER       | rs<br>^ | Compare    | Part Number     | Schematic<br>Image | lout(Max)<br>(A) | Efficiency<br>(%) | BOM<br>Area<br>(mm²) | BOM<br>Cost(\$<br>  1ku) | BOM<br>Count | Description                                                                                                  | Customize |

| IC Features                                                       | ^                  |         | ~          | TPSM84424       | 6F. 🖣 30           | 4                | 86.63             | 156                  | 5.5                      | 10           | 4.5V to 17V Input, 0.6V-10V<br>Output, 4A Power Module in<br>Compact 7.5x7.5mm Footprint                     | CUSTOMIZE |

| Power Good                                                        |                    |         |            | TPSM84624       | 0.000              | 6                | 86.63             | 156                  | 6.5                      | 10           | 4.5V to 17V Input, 0.6V-10V<br>Output, 6A Power Module in<br>Compact 7.5x7.5mm Footprint                     | CUSTOMIZE |

| Adjustable Soft Star                                              |                    | ł       |            | TPSM84824       | 0.030              | 8                | 86.63             | 156                  | 7.5                      | 10           | 4.5V to 17V Input, 0.6V-10V<br>Output, 8A Power Module in<br>Compact 7.5x7.5mm Footprint                     | CUSTOMIZE |

| Light Load Efficiency  Synchronous Rectifie  Adjustable Current L | cation             | 1       |            | TPSM84A22       | -16                | 10               | 85.02             | 194                  | 7.51                     | 2            | 8V to 14V Input, 1.2V to 2.05V<br>Output, 10A Power Module with<br>Integrated Input and Output<br>Capacitors | CUSTOMIZE |

| Adjustable Frequence                                              |                    | ~       |            | LMZM33606       |                    | 6                | 83.8              | 299                  | 10.41                    | 9            | 3.5V to 36V Input, 1V to 20V<br>Output, 6A Power Module in<br>10x16x4mm QFN Package with                     | CUSTOMIZE |

#### Figure 16. Power Design Using WEBENCH®

- Now, select a design from the available list and click *Customize*. In this design, the TPSM84424 device is used for +3.3-V, +1.9-V, and +1.1-V rails and the LMZM23601 device is used for ±2.5-V rail generation.

- 7. Simulate to verify the design. Select the simulation type from *Startup*, *Load Transient*, *Input Transient* and *Steady State*.

- **NOTE:** WEBENCH provides options to export schematic, PCB Layout and BOM for Altium Designer, Cadence OrCAD, CadSoft Eagle, Mentor Graphics and P-CAD Software.

WEBENCH Power Designer has much more capability than what is mentioned in this section. Refer to WEBENCH for more information or see the short training video WEBENCH Power Designer: Step by Step, to get started.

#### 2.3 Highlighted Products

The devices used and the reasons for selecting them are explained in this section.

#### 2.3.1 TPSM84424, TPSM84624, and TPSM84824

| TPSM84424 4.5-V to 17-V input, 0.6-V to 10-V output, 4-A power module data sheet | TPSM84424 samples and availability |

|----------------------------------------------------------------------------------|------------------------------------|

| Evaluation Modules:                                                              | TPSM84424 EVM                      |

#### Figure 17. TPSM84424 Functional Block Diagram

The TPSM84424 power module is an easy-to-use integrated power supply that combines a 4-A DC/DC converter with power MOSFETs, a shielded inductor and passives into a small form factor, QFM package. It is used in this design to bring down the 12-V input voltage to 1.9 V, 1.1 V and 3.3 V. This power solution allows as few as six external components while maintaining the ability to adjust key parameters to meet specific design requirements. It has the TurboTrans<sup>™</sup> feature that allows the transient response to be optimized for reduced output voltage deviation with less required output capacitance.

#### Why choose this device? Key features:

- High efficiency, > 87% at 1.9-V, 2-A output for 12-V input

- HotRod package to reduce EMI

- Allows synchronization to an external clock

- 7.5-mm × 7.5-mm × 5.3-mm QFM package

- This device meets EN55011 Class B radiated EMI limits

#### Alternatives:

| DEVICE    | I <sub>OUT</sub> (MAX) (A) | V <sub>IN</sub> (MAX) (V) | V <sub>IN</sub> (MIN) (V) | V <sub>OUT</sub> (MAX) (V) | V <sub>OUT</sub> (MIN) (V) | EMI TESTED, ENABLE, FREQUENCY<br>SYNCHRONIZATION, POWER GOOD |

|-----------|----------------------------|---------------------------|---------------------------|----------------------------|----------------------------|--------------------------------------------------------------|

| TPSM84624 | 6                          | 17                        | 4.5                       | 10                         | 0.6                        | $\checkmark$                                                 |

| TPSM84824 | 8                          | 17                        | 4.5                       | 10                         | 0.6                        | ✓                                                            |

| LMZM33606 | 6                          | 36                        | 3.5                       | 20                         | 1                          | $\checkmark$                                                 |

Use the WEBENCH® Power Designer to create a custom design with the TPSM84424 device.

#### 2.3.2 LMZM23601

| LMZM23601 36-V, 1-A step-down DC/DC power module in 3.8-mm × 3-<br>mm package data sheet | LMZM23601 Samples and Availability                      |

|------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                                                                                          | LMZM23601 3.3-V Output EVM,<br>LMZM23601 5-V Output EVM |

The LMZM23601 device is an integrated-inductor power module, that is specifically designed for spaceconstrained industrial applications. It is used in this design to bring down the 12-V input voltage to  $\pm 2.5$  V. It is available in two fixed output voltage options of 5-V and 3.3-V, and an adjustable (ADJ) output voltage option supporting a 2.5-V to 15-V range. The LMZM23601 has an input voltage range of 4-V to 36-V and can deliver up to 1000-mA of output current.

An inverting buck configuration is implemented using the LMZM23601 device for generation of a –2.5-V power rail. See the *LMZM23601 36-V*, *1-A step-down DC/DC power module in 3.8-mm × 3-mm package data sheet* for more details.

#### Why choose this device? Key features:

- EMI tested

- Allows synchronization to an external clock

- Miniature 3.8-mm × 3-mm × 1.6-mm package Alternatives:

| DEVICE    | I <sub>оυт</sub> (МАХ)<br>(А) | V <sub>IN</sub> (MAX)(V) | V <sub>IN</sub> (MIN) (V) | V <sub>оит</sub><br>(МАХ)(V) | V <sub>out</sub> (MIN)<br>(V) | EMI TESTED, ENABLE, FREQUENCY<br>SYNCHRONIZATION, POWER GOOD |

|-----------|-------------------------------|--------------------------|---------------------------|------------------------------|-------------------------------|--------------------------------------------------------------|

| LMZM23600 | 0.5                           | 36                       | 4                         | 2.5                          | 15                            | $\checkmark$                                                 |

| LMZM33602 | 2                             | 36                       | 4                         | 1                            | 18                            | ✓                                                            |

Use the WEBENCH® Power Designer to create a custom design with the LMZM23601 device.

#### System Design Overview

#### 2.3.3 TPS7A84

| TPS7A84 high-current (3 A), high-accuracy (1%), low-noise (4.4 $\mu$ V <sub>RMS</sub> ), LDO voltage regulator data sheet | TPS7A84 samples and availability |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Evaluation Modules                                                                                                        | TPS7A84 EVM                      |

The TPS7A84 is a low-noise (4.4  $\mu$ V<sub>RMS</sub>), low-dropout linear regulator (LDO) capable of sourcing 3 A with only 180 mV of maximum dropout. The device output voltage is pin-programmable from 0.8 V to 3.95 V and adjustable from 0.8 V to 5.0 V using an external resistor divider.

#### Why choose this device? Key features:

- Good power-supply ripple rejection ratio: 40 dB at 500 kHz

- Low output voltage noise: 4.4 μV<sub>RMS</sub> at 0.8-V output

- 1% (max) accuracy over line, load, and temperature

- Enable and Power Good pins to implement power sequencing Alternatives

| Device    | I <sub>оυт</sub> (МАХ)<br>(А) | V <sub>IN</sub> (MAX)<br>(V) | V <sub>IN</sub> (MIN)<br>(V) | V <sub>OUT</sub> (MIN)<br>(V) | V <sub>оит</sub> (МАХ)<br>(V) | PSRR at 500<br>kHz (dB) | FEATURES                                         |

|-----------|-------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|-------------------------|--------------------------------------------------|

| TPS7A8300 | 2                             | 6.5                          | 1.1                          | 0.8                           | 5                             | 30                      | Enable, output discharge, power good, soft start |

| TPS7A85   | 4                             | 6.5                          | 1.1                          | 0.8                           | 5                             | 40                      | Enable, output discharge, power good, soft start |

# 2.3.4 CD74HC4017

The CD74HC4017 device is a decade counter with decode outputs. It is used in this design to generate multi-phase synchronized clocks of switching regulators. It can take a maximum of 30-MHz clock input at VCC = 4.5 V and  $25^{\circ}C$ .

# 3 Hardware, Software, Testing Requirements, and Test Results

# 3.1 Required Hardware and Software

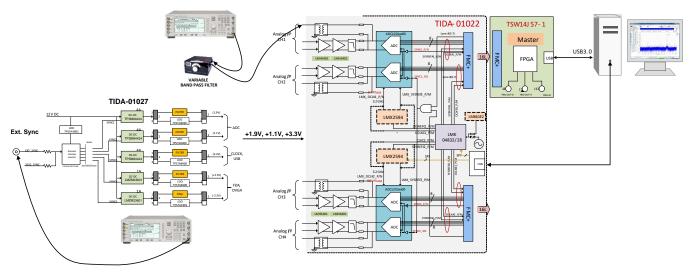

This design uses the following hardware and software to measure the impact of the power supply on DAQ performance.

- TIDA-01027 power supply board

- High-speed DAQ, (TIDA-01022 board is used)

- TSW14J57 capture card (FPGA)

- HSDC TID GUI (Used to program TIDA-01022 board)

- High-speed data converter pro software (Used to capture data from FPGA)

# 3.1.1 Hardware Description

Texas

www.ti.com

**STRUMENTS**

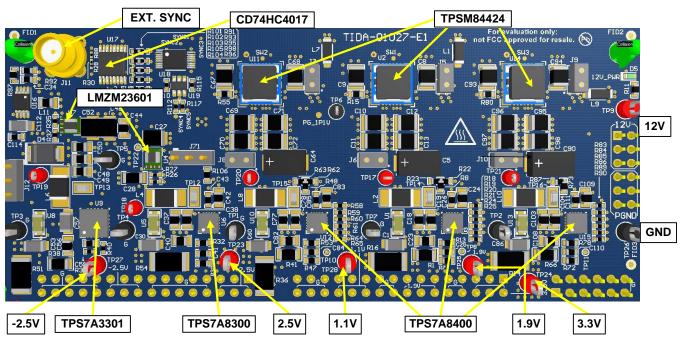

Figure 20 shows the TIDA-01027 reference design hardware. The printed circuit board (PCB) has a 117.5mm × 51-mm rectangular form factor. This board is compatible with the TIDA-01022 (high-speed DAQ) and can be plugged to the last for quick evaluation. The input voltage of the board ranges from 5 V to 17 V. The integrated circuits (TPSM84824, LMZM23601, CD74HC4017, TPS7A8400, TPS7A8300, and TPS7A3301), several test points, and jumpers are located on the top side of the PCB. SMA Connector J11 provides external synchronization of DC/DC converters. D5 LED ON state indicates the input voltage available. The default configuration is DC/DC + Filter, where LDOs are bypassed by the filters.

# Figure 20. TIDA-01027 Hardware Image

# 3.1.2 Test Point Description

Table 4 lists the test points and their functions.

| Table 4 | . Test | Point | Descri | ption |

|---------|--------|-------|--------|-------|

|         |        |       |        |       |

| TEST POINT                         | FUNCTION      |

|------------------------------------|---------------|

| TP9                                | 12-V DC Input |

| TP1, TP2, TP3, TP4, TP5, TP7, TP26 | Ground        |

| TP23                               | +2.5 V        |

| TP27                               | -2.5 V        |

Low-noise power-supply reference design maximizing performance in 12.8-GSPS data acquisition systems

Copyright © 2019, Texas Instruments Incorporated

|               | • • •                                                     |

|---------------|-----------------------------------------------------------|

| TEST POINT    | FUNCTION                                                  |

| TP24          | +3.3 V                                                    |

| TP25          | +1.9 V                                                    |

| TP28          | +1.1 V                                                    |

| SW1, SW2, SW3 | Duty cycle of DC/DC 1.9 V, 1.1 V, and 3.3 V, respectively |

Table 4. Test Point Description (continued)

# 3.2 Testing and Results

#### 3.2.1 Test Setup

The TIDA-01022 board is used to measure the power supply impact on the AFE performance. This is a high-speed, multi-channel data capture board, capable of capturing data at a maximum of 12.8 GSPS. This board uses two 12-bit, 6.4 GSPS ADCs. See the TIDA-01022 and TIDA-01028 reference designs for more information. For all test results, the sampling frequency of the TIDA-1022 board is set to 3.2 GSPS. An input signal of frequency  $F_{IN} = 800$  MHz and amplitude  $A_{IN} = -1$  dBFS is used, and is synchronized to the ADC clock. This is done to avoid spectral leakage. The ±2.5-V power rail is powered down in the TIDA-01027 board, and an input signal is provided to the TIDA-01022 Channel 1 with balun. Figure 21 shows the test setup to capture the ADC output spectrum.

Figure 21. Test Setup to Capture ADC Output Spectrum

#### 3.2.2 Test Results

In the following subsections, the ADC output spectrum is compared between the power supply that uses Filter and LDO, and their impact on the ADC is observed. Furthermore, phase shifting is compared with phase aligned for input ripple current to show reduction in EMI due to phase shift. Finally, power-supply efficiency data is included for both DC/DC and DC/DC+LDO.

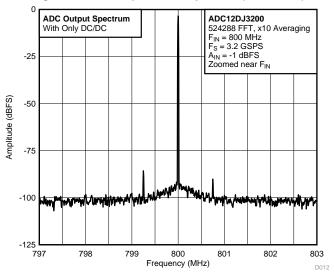

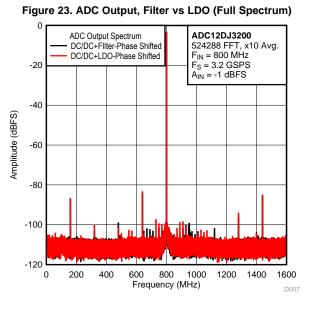

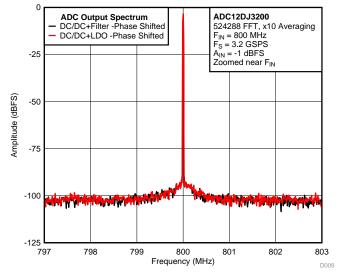

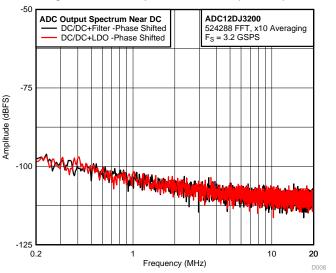

# 3.2.2.1 ADC Output Spectrum, Comparison Between LDO and Filter

In this test case, an input signal of 800-MHz frequency and an external low-noise 3.2-GHz clock are used. In the power-supply board, TIDA-01027, only three rails +1.9 V, +1.1 V, and +3.3 V are powered on. They are set at 750-kHz switching frequency and are 120° phase-shifted. Other rails  $\pm 2.5$  V are powered down, because amplifiers are bypassed and input to ADC is provided with balun. The output spectrum of 12-bit ADC, **ADC12DJ3200**, is captured and compared for LDO and filter output options of the power supply. FFT uses 524288 samples and is averaged by 10 for this measurement.

20 Low-noise power-supply reference design maximizing performance in 12.8-GSPS data acquisition systems

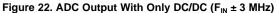

When the Filter is removed, direct DC/DC output is provided to the ADC power-supply pins,  $F_{DC/DC}$  and  $F_{in}\pm F_{DC/DC}$  spurs appear in the spectrum, as Figure 22 shows.In this case, spurs appear at 799.25 MHz and 800.75 MHz. Filter and LDO are used to reduce these spurs. Figure 23, Figure 24 and Figure 25 show the output spectrum of the ADC with power supply that uses LDO and Filter. The output spectrum is compared between them. It is observed that there are not any  $F_{DC/DC}$  and  $F_{in}\pm F_{DC/DC}$  spurs in the spectrum either using LDO or Filter. The same noise floor is achieved by replacing LDO with Filter. Thus, Filter replaces LDO in this design.

Figure 24. ADC Output, Filter vs LDO (F<sub>IN</sub> ± 3 MHz)

Figure 25. ADC Output, Filter vs LDO (Near DC)

#### 3.2.2.2 Input Ripple Current

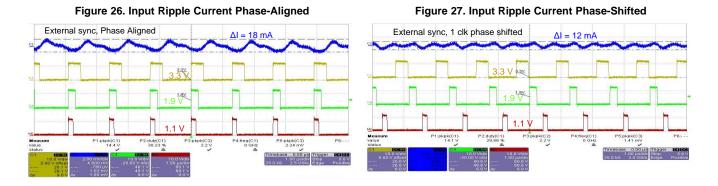

Input ripple is measured to compare between phase-shifted and phase-aligned frequency synchronization schemes. A current probe is used at the power supply input for this measurement. DC/DC converters are set to 750-kHz frequency with output loads of 2.5 A, 2.0 A, and 2.0 A for 1.1-V, 1.9-V, and 3.3-V rails, respectively. Figure 26 and Figure 27 show input ripple current measurement with a total  $20 \ \mu$ F input capacitor. It is observed that phase shifting reduces input ripple current, that results in EMI reduction due to di/dt. Phase-shifting also reduces inrush current and total input capacitor.

#### 3.2.2.3 Power-Supply Efficiency

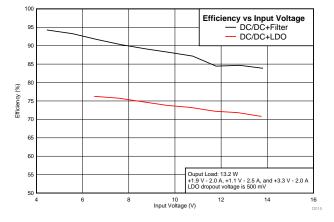

Figure 28 shows the power-supply efficiency comparison between DC/DC+Filter and DC/DC+LDO configurations. It is observed that removing LDO improves total efficiency by more than 13%, and maximum efficiency of 85% is achieved at the 12-V input.

To calculate the efficiency of the power supply, the input voltage is measured at the input of the converter. Output voltage is measured at Filter and LDO outputs, respectively, in the DC/DC+Filter and DC/DC+LDO case, and the output current is measured using 10-m resistors. In the TIDA-01027 board, only three rails +1.9 V, +1.1 V, and +3.3 V are powered. All converters are operating at 750 kHz. The LDO dropout voltage is set to 500 mV. The load current of converters are 2.5 A, 2.0 A, and 2.0 A for 1.1-V, 1.9-V, and 3.3-V power rails, respectively.

#### Figure 28. Efficiency vs Input Voltage Curve

#### 3.2.3 Summary

The analog front end (AFE) performance remains unaffected after LDO is replaced with Filter for 12-bit high-speed GSPS systems. This improves power-supply efficiency, reduces power consumption and PCB size, and enhances thermal performance. TI HotRod<sup>™</sup> package technology reduces DC/DC EMI. Phase-shifting reduces power-supply noise, inrush current, input ripple current, and input capacitance.

#### 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01027.

# 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01027.

# 4.3 PCB Layout Recommendations

#### 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01027.

# 4.4 Altium Project

To download the Altium Designer® project files, see the design files at TIDA-01027.

#### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01027.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01027.

# 5 Related Documentation

- 1. Texas Instruments, Power-supply design for high-speed ADCs application report

- 2. Texas Instruments, Designing a modern power supply for RF sampling converters analog application journal

- 3. Texas Instruments, Using a buck converter in an inverting buck-boost topology

- 4. Texas Instruments, Inverting application for the LMZM23601 and LMZM23600 application report

- 5. Texas Instruments, Supply noise effect on oscillator phase noise application report

- 6. Texas Instruments, Low noise power solution reference design for clock generators design guide

- 7. Texas Instruments, Simplify low EMI design with power modules white paper

#### 5.1 Trademarks

E2E, HotRod, ANY-OUT, TurboTrans are trademarks of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. Altium Designer is a registered trademark of Altium LLC or its affiliated companies. All other trademarks are the property of their respective owners.

# 5.2 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# 6 About the Author

**SHAURY ANAND** is a systems engineer at Texas Instruments India, where he is responsible for developing reference design solutions for the industrial segment

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated