# Design Guide: TIDA-010239 AC Level 2 Charger Platform Reference Design

# Description

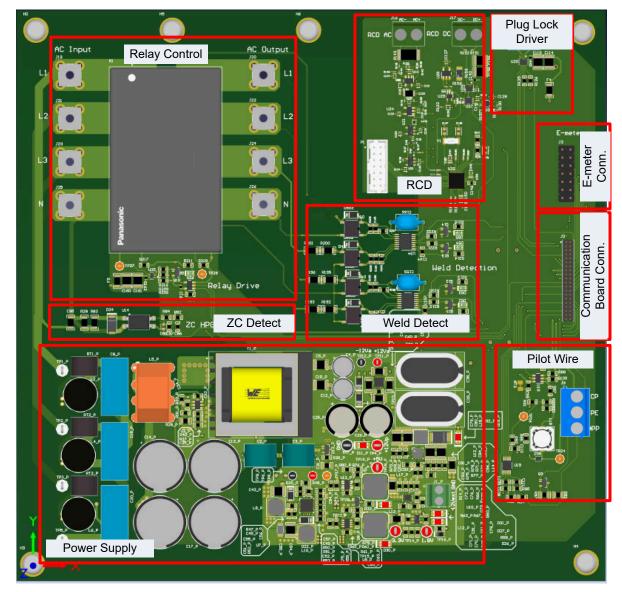

Electric vehicle service equipment (EVSE) facilitates power delivery to electric vehicles safely from the grid. An EVSE control system consists of an auxiliary power stage, an off-board AC/DC high-power stage (only in DC charging stations), energy metering unit, AC and DC residual current detector, an isolation monitor unit, relays and contactors with drive, twoway communication over single wire, and service and user interfaces. This reference design highlights an ultra-low standby isolated AC/DC auxiliary power stage followed by converters and linear regulators, a comparator-based control pilot interface to meet the IEC61851 standard, an efficient relay and contactor drive, plug lock motor driver, flux gate circuit to detect AC and DC currents for RCD applications, and isolated line voltage sensing across the relay and contactor.

#### Resources

| TIDA-010239                     | Design Folder |

|---------------------------------|---------------|

| UCC28742, TLV1805               | Product Folde |

| ISO1212, DRV8220                | Product Folde |

| ADC122S051                      | Product Folde |

| TPS7A39, TPS7A20, ATL431, TL431 | Product Folde |

| TPS563210A, TPS55330            | Product Folde |

| TPS259470, TL7705A              | Product Folde |

|                                 |               |

Ask our TI E2E<sup>™</sup> support experts

# Features

- Ultra-low standby UCC28742-based isolated 29-W AC/DC stage to improve energy efficiency

- Supercapacitor backup supplying up to 7.5 W for 3 seconds during energy storage release (AC mains failing)

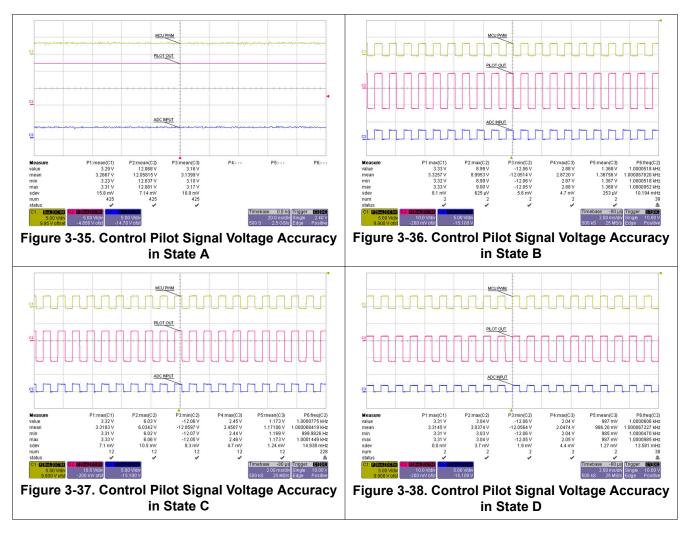

- Tight output voltage regulation (< ±5%) of low dropouts (LDO) and the high slew rate of the TLV1805 device for control pilot interface

- Ultra-low standby as well as cost-optimized converters and linear regulators to power up points-of-load

- DRV8220 current controller to drive high-current relays and contactors for thermal protection, RCD AC and DC detection, and plug lock control

- Isolated line voltage sensing using the ISO1212 digital-input receiver for welded relay and contactor detection

# Applications

• AC charging (pile) station

1

# **1 System Description**

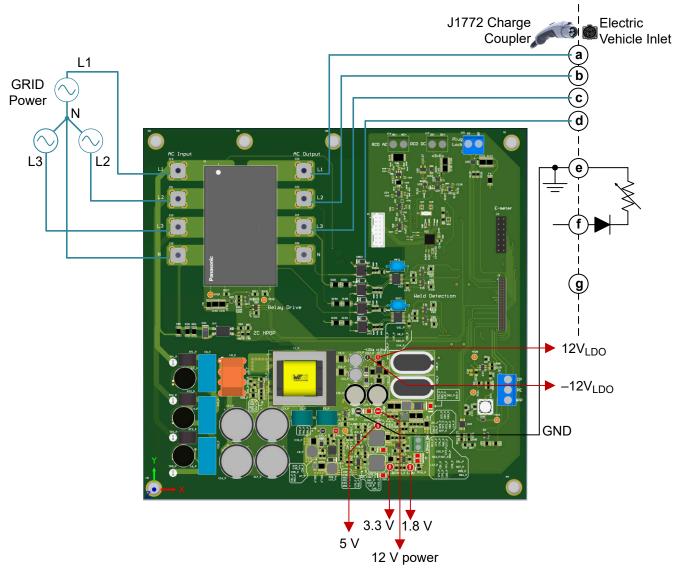

Electric vehicles (EVs), including plug-in hybrid electric vehicles (PHEVs), receive energy from the electrical grid through electric vehicle supply equipment (EVSE), more commonly known as EV chargers. To facilitate the power delivery to the vehicle, the EVSE sits between a stable grid connection and the vehicle as shown in Figure 1-1.

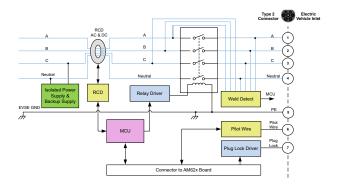

Figure 1-1. AC Level 2 Charger High-Level Block Diagram

The primary EVSE functionality includes:

- Regulated electrical current makes sure that the best possible current is provided and falls within the maximum current the EV can handle.

- AC/DC residual current detection (RCD)

- Relay and contactor drive and latched contact detection

- Energy metering

- Automatic disconnect when a hardware fault is detected, the power is shut off, to avoid risks like battery damage, an electrical short, or a fire.

- Safety lock-out feature prevents current from flowing when the charger is not connected to an EV.

An EVSE control system mainly consists of auxiliary power stage, off-board AC/DC high power stage (only in DC charging stations), energy metering, AC and DC residual current detection, isolation monitor unit, relays and contactors with drive, two-way communication, and service and user interfaces.

# **1.1 EV Charging Station Challenges**

The EVSE design for EV charging stations presents several challenges including those presented in the following sections.

#### 1.1.1 SAE J1772 or Equivalent Standard Compliant EV Charging Stations

Many electric vehicle manufacturers have adopted the SAE J1772 standard for electrical connections to an EV. The same specifications also translate into international localizations, with differing form factors. The control pilot is the primary control conductor and is connected to the equipment ground through control circuitry on the vehicle and performs the following functions:

- Verifies that the vehicle is present and connected

- · Permits energization and de-energization of the supply

- Transmits supply equipment current rating to the vehicle

- Monitors the presence of the equipment ground

- Establishes vehicle ventilation requirements

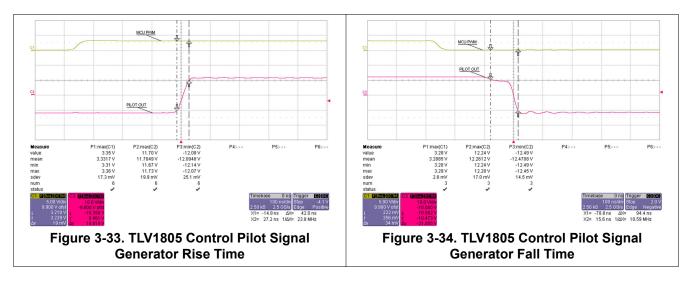

Table 1-1 shows the SAE J1772 standard mandates control pilot circuit generator parameters.

| Table 1-1. Control Fliot Signal Generator Farameters per SAE 31/72 |        |        |        |       |  |

|--------------------------------------------------------------------|--------|--------|--------|-------|--|

| PARAMETER <sup>(1)</sup>                                           | MIN    | NOM    | MAX    | UNITS |  |

| Voltage high, open circuit                                         | 11.40  | 12.00  | 12.60  | V     |  |

| Voltage low, open circuit                                          | -11.40 | -12.00 | -12.60 | V     |  |

| Frequency                                                          |        | 1000   |        | Hz    |  |

| Pulse width <sup>(2)</sup>                                         |        | 5      |        | μs    |  |

| Rise time <sup>(3)</sup>                                           |        | 2      |        | μs    |  |

| Fall time <sup>(3)</sup>                                           |        | 2      |        | μs    |  |

| Settling time <sup>(4)</sup>                                       |        | 3      |        | μs    |  |

#### Table 1-1. Control Pilot Signal Generator Parameters per SAE J1772

(1) Tolerances to be maintained over the environmental conditions and useful life as specified by the manufacturer

(2) Measured at 50% points of complete negative-to-positive or positive-to-negative transitions

(3) 10% to 90% of complete negative-to-positive transition or 90% to 10% of complete positive-to-negative transition measured between the pulse generator output and R1. Note that the term *generator* refers to the EVSE circuitry prior to and driving the 1-k $\Omega$  source resistor with a ±12-V square wave. This circuitry must have rise and fall times faster than 2 µs. Rise and fall times slower than 2 µs begin to add noticeably to the output rise and fall times dictated by the 1-k $\Omega$  resistor and all the capacitance on the pilot line.

(4) To 95% of steady-state value, measured from the start of transition

# 1.1.2 AC and DC Leakage, Residual Current Detection (RCD)

The primary requirement in providing protection during EV charging is the ability to detect AC and DC residual currents and thereby mitigate the risk of electric shock or fire.

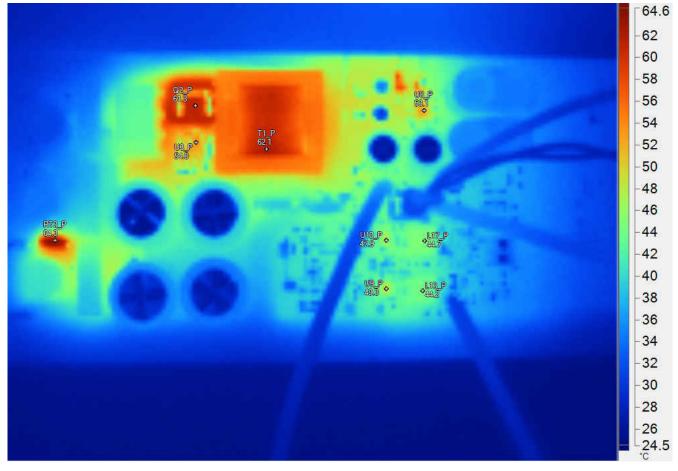

#### 1.1.3 Efficient Relay and Contactor Drive

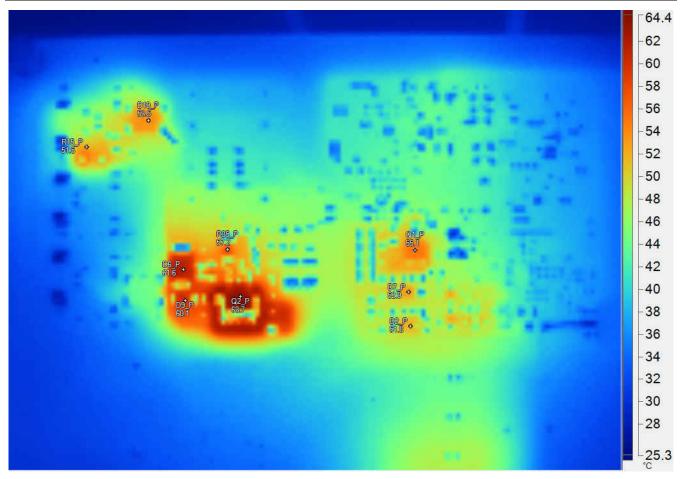

In normal use cases, high-current relays or contactors can typically draw 10s to 100s of milliamps as an inductive load, requiring specific drive architectures. Because of the amount of time that a relay or contactor requires to remain powered, an efficient drive solution is preferred to avoid thermal problems.

3

### 1.1.4 Contact Weld Detection

For safety reasons, detecting the output voltage of the relay and contactor is critical. The contacts can experience arcing and become fused together, providing power to the plug even when not powered by the system. Checking that the operation completed correctly is important and is to be done every time the relay is opened.

This reference design showcases ultra-low standby isolated AC/DC auxiliary power stage followed by ultra-low  $I_Q$  as well as cost-optimized converters and linear regulators, comparator-based control pilot interface to meet SAE J1772 standard, efficient relay and contactor driver design, and digital isolator based line voltage sensing to detect fusing of relay and contactor contacts due to arcing.

# **1.2 Key System Specifications**

| Table 1-2. Key System Specifications |                                                                                                                                                                                                                          |        |          |      |                  |                                                                        |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|------|------------------|------------------------------------------------------------------------|--|--|

| PARAMETER                            | NOTES AND CONDITIONS                                                                                                                                                                                                     | MIN    | NOM      | MAX  | UNIT             | DETAILS                                                                |  |  |

| INPUT CHARACTERISTI                  | cs                                                                                                                                                                                                                       |        |          |      |                  |                                                                        |  |  |

| Input voltage,V <sub>IN</sub>        |                                                                                                                                                                                                                          | 85     | 120, 230 | 460  | V <sub>RMS</sub> | Line voltage                                                           |  |  |

| Line frequency, f <sub>LINE</sub>    |                                                                                                                                                                                                                          | 47     | 60, 50   | 63   | Hz               |                                                                        |  |  |

| OUTPUT CHARACTERIS                   | TICS                                                                                                                                                                                                                     |        |          |      |                  |                                                                        |  |  |

| Output voltage, V <sub>OUT1</sub>    | Flyback output 1                                                                                                                                                                                                         |        | 12       |      | V                | UCC28742-based AC/DC flyback                                           |  |  |

| Output current, I <sub>OUT1</sub>    |                                                                                                                                                                                                                          |        | 2.2      |      | A                | power stage with 3 outputs                                             |  |  |

| Output voltage, V <sub>OUT2</sub>    | Flyback output 2                                                                                                                                                                                                         |        | 14       |      | V                |                                                                        |  |  |

| Output current, I <sub>OUT2</sub>    |                                                                                                                                                                                                                          |        | 0.1      |      | A                |                                                                        |  |  |

| Output voltage, V <sub>OUT3</sub>    | Flyback output 3                                                                                                                                                                                                         |        | -14      |      | V                |                                                                        |  |  |

| Output current, I <sub>OUT3</sub>    |                                                                                                                                                                                                                          |        | 0.1      |      | A                |                                                                        |  |  |

| Total output power, P <sub>OUT</sub> | Output power of flyback power stage                                                                                                                                                                                      |        |          | 28.8 | w                | -                                                                      |  |  |

| POINT OF LOAD AND AU                 | JXILIARY SECTION CHARACTER                                                                                                                                                                                               | ISTICS | 1 1      |      | 1                |                                                                        |  |  |

| TPS7A3901                            | Dual LDO                                                                                                                                                                                                                 |        | +12      |      | V                | Nominal current = 100 mA                                               |  |  |

| TPS7A3901                            |                                                                                                                                                                                                                          |        | -12      |      | V                | Nominal current = 100 mA                                               |  |  |

| TPS76318                             | LDO                                                                                                                                                                                                                      |        | +1.8     |      | V                | Nominal current = 30 mA                                                |  |  |

| TPS259470                            | eFuse                                                                                                                                                                                                                    |        | +5       |      | V                | Overcurrent protection = 4.5 A                                         |  |  |

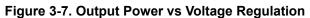

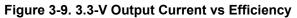

| TPS563210A                           | Sync-Buck                                                                                                                                                                                                                |        | +5       |      | V                | Nominal current = 1.2 A, 1.3 A max                                     |  |  |

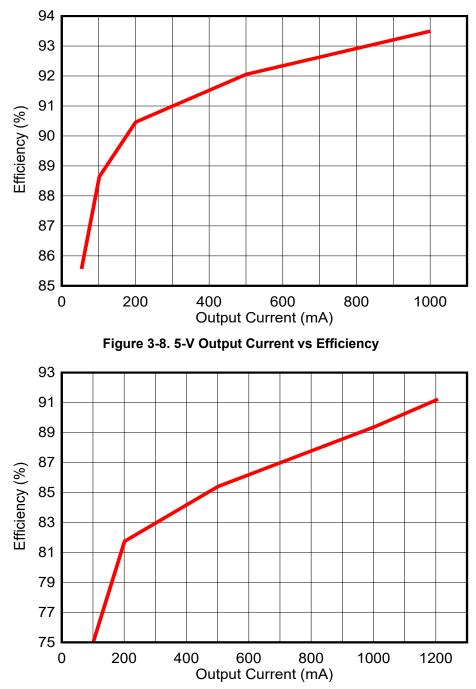

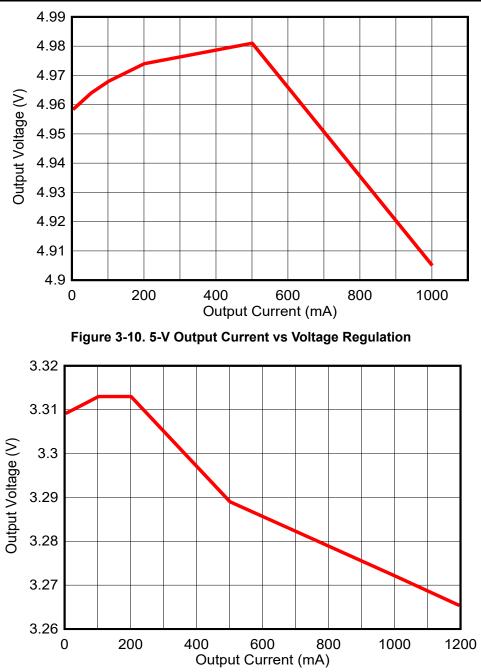

| TPS563210A                           | Sync-Buck                                                                                                                                                                                                                |        | +3.3     |      | V                | Nominal current = 0.8 A, 1.5 A max                                     |  |  |

| TPS65130                             | Dual converter (Boost +<br>inverting-Buck/Boost)" active<br>during energy storage release                                                                                                                                |        | ± 14     |      | v                | Nominal current = 0.1 A                                                |  |  |

| TPS55330                             | Non-sync Boost: active during<br>energy storage release                                                                                                                                                                  |        | +11.5    |      | V                | Nominal current = 1.8 A                                                |  |  |

| SUPERCAPACITOR BAC                   | KUP CHARACTERISTICS                                                                                                                                                                                                      |        |          |      | 1                |                                                                        |  |  |

| Supercap normal<br>operating voltage | 2 × 2.5-μF supercapacitors<br>in series. Charger charges to<br>7.8 V. Boost UVLO sets min<br>operating voltage to 4.3 V.<br>Supplying 7.5 W for 3 s (after<br>boost) during energy storage<br>release (AC mains failing) | +4.3   | +7.8     |      | v                | Peak current = 4.06 A, for 1 s from full rate voltage to half voltage. |  |  |

| TL7705A                              | Voltage supervisor for EoC of 2 × 2.5-µF supercapacitors in series                                                                                                                                                       |        | +7.49    |      | v                | Threshold for End of Charge                                            |  |  |

| Linear charger                       | Charges supercapacitors from 0<br>V to 7.8 V in 81 s and from 4.3 V<br>to 7.8 V in 36 s                                                                                                                                  |        | +120     |      | mA               |                                                                        |  |  |

#### Table 1-2. Key System Specifications

# 2 System Overview

2.1 Block Diagram

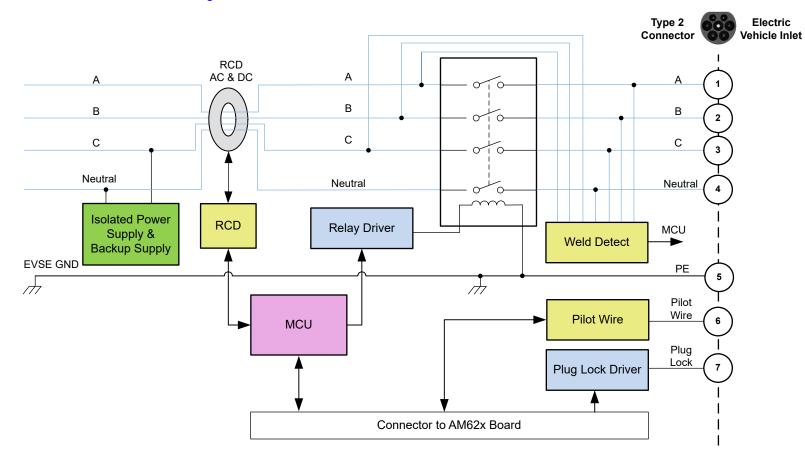

Figure 2-1. TIDA-010239 Block Diagram

5

# 2.2 Design Considerations

# 2.2.1 Isolated AC/DC Power Supply Design

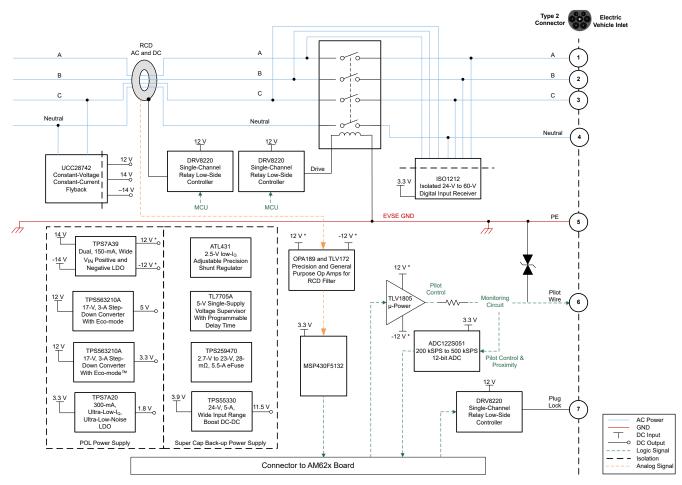

The isolated AC/DC power stage is multiple outputs winding flyback stage based on the UCC28742 device. The UCC28742 controller provides constant-voltage (CV) using an optical coupler to improve transient response to large-load steps. Constant-current (CC) regulation is accomplished through primary-side regulation (PSR) techniques. This device processes information from the optocoupled feedback and an auxiliary flyback winding for precise high-performance control of the output voltage and current. Figure 2-2 shows the system block diagram for the power supply design and the design parameters are shown in Table 2-1.

These are the main components of the power supply:

- A three-phase input flyback with synchronous rectification supplies three voltages: 12 V (power) and ± 14 V (low power)

- Two buck converters (based on TPS563210), one dual-LDO (TPS7A3901) and a second LDO (TPS7A2018) take the power from the flyback and supply further 5 V, 3.3 V, 1.8 V, and ± 12 V

- Two supercapacitors, 2.5 μF each are connected in series and are charged by means of a 120-mA constant current linear regulator, setting the charging voltage to 7.8 V

- A boost converter with TPS55330 supplies all voltages as soon as mains power is missing

- A further 12-V input port, protected against overcurrent and reverse polarity, is managed by the eFuse TPS259470, useful during debug. This way the whole system can be supplied without the need of single or three-phase high-voltage input

- An inverting buck-boost generates ±14 V for the dual-LDO during energy storage discharge, taking power from the regulated 5-V rail

Figure 2-2. Isolated AC/DC Power Supply Block Diagram

| PARAMETER                                                     | NOTES AND CONDITIONS                                                                        | MIN   | NOM      | MAX   | UNIT             |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------|----------|-------|------------------|

| INPUT CHARACTERISTICS                                         | 1                                                                                           |       | 1        |       |                  |

| Input voltage,V <sub>IN</sub>                                 |                                                                                             | 85    | 115, 230 | 460   | V <sub>RMS</sub> |

| Maximum input current                                         | $V_{IN} = V_{IN(min)}, I_{OUT} = I_{OUT(max)}$                                              |       | 0.8      |       | A <sub>RMS</sub> |

| Line frequency                                                |                                                                                             | 47    | 60, 50   | 63    | Hz               |

| Desired capacitor bulk voltage,<br>V <sub>BULK(desired)</sub> |                                                                                             | 85    |          |       | V                |

| No load input power<br>consumption                            | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$ , $I_{OUT} = 0$ A                                  |       |          | 500   | mW               |

| OUTPUT CHARACTERISTICS                                        |                                                                                             |       |          |       |                  |

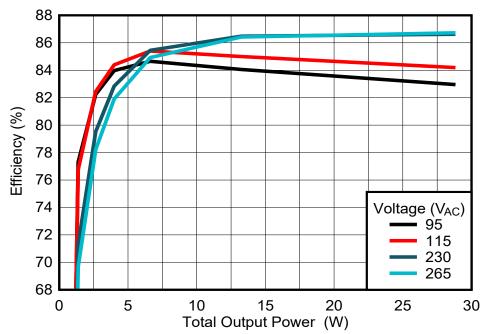

| Output voltage, V <sub>OUT1</sub>                             | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$                                                    | 11.4  | 12       | 12.6  | V                |

| Output current, I <sub>OUT1</sub>                             |                                                                                             |       |          | 2.2   | A                |

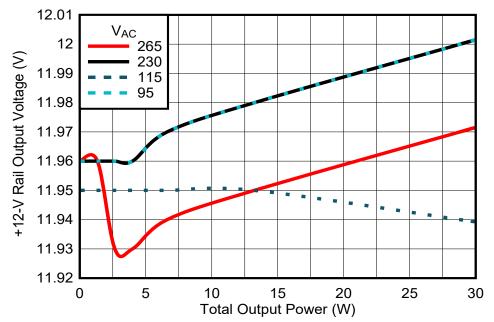

| Output voltage, V <sub>OUT2</sub>                             | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$                                                    | 10.5  | 12       | 12.1  | V                |

| Output current, I <sub>OUT2</sub>                             |                                                                                             |       |          | 0.1   | A                |

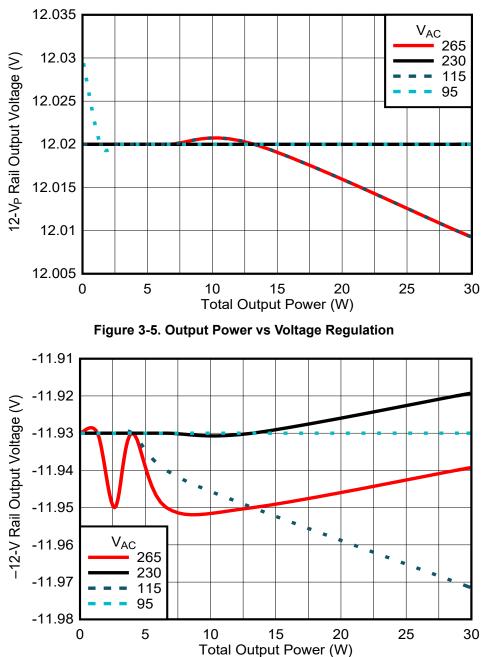

| Output voltage, V <sub>OUT3</sub>                             | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$                                                    | -10.5 | -12      | -12.1 | V                |

| Output current, I <sub>OUT3</sub>                             |                                                                                             |       |          | 0.1   | A                |

| Total output power, P <sub>OUT</sub>                          |                                                                                             |       |          | 28.8  | W                |

| Output voltage regulation                                     | Line regulation: $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$ ,<br>$I_{OUT1} \le I_{OUT1(max)}$ |       | 0.1%     |       |                  |

|                                                               | Load regulation: $0 \text{ A} \leq I_{OUT1} \leq I_{OUT1(max)}$                             |       | 0.2%     |       |                  |

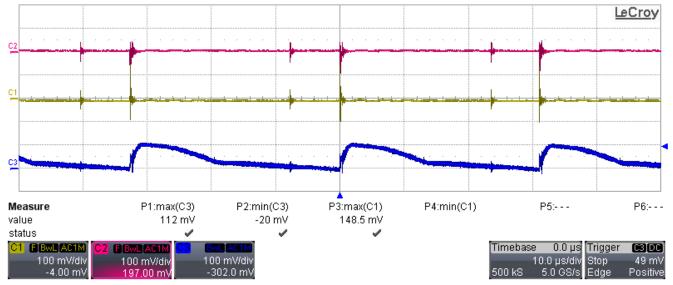

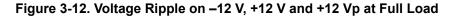

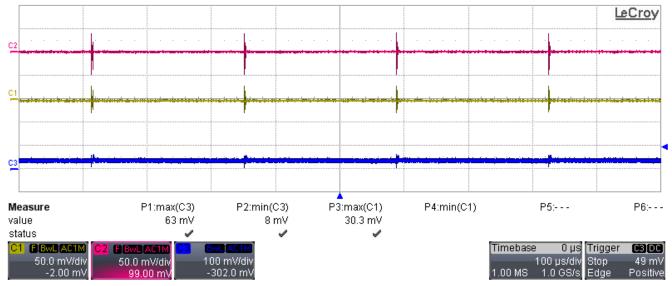

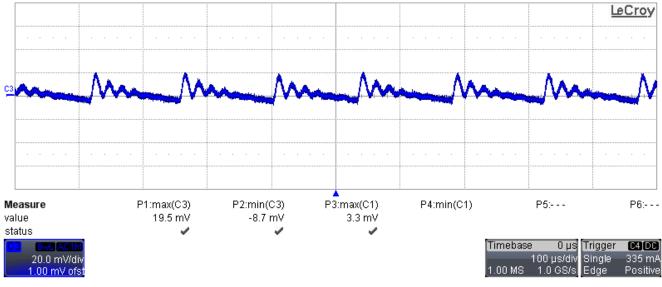

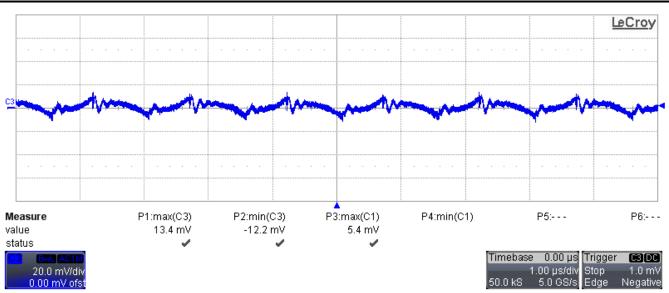

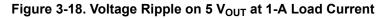

| Output voltage ripple                                         | $V_{IN(min)} \le V_{IN} \le V_{IN(max)},$<br>0 A \le I_{OUT1} \le I_{OUT1(max)}             |       |          | 100   | mVpp             |

| Total output overcurrent, I <sub>OCC</sub>                    | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}$                                                    |       |          | 2.4   | A                |

| Minimum output voltage, CC<br>mode                            | $V_{IN(min)} \le V_{IN} \le V_{IN(max)}, I_{OUT} = I_{OCC}$                                 |       | 5        |       | V                |

| Brown-out protection                                          | I <sub>OUT</sub> = I <sub>OUT(max)</sub>                                                    | 49.9  | 55.9     | 61.8  | V <sub>RMS</sub> |

| Transient response overshoot                                  | $I_{OUT} = I_{OUT(max)}$ to 0-A load transient                                              |       |          | 0.2   | V                |

| Transient response time                                       | $I_{OUT} = I_{OUT(max)}$ to 0-A load transient                                              |       |          | 5     | ms               |

| SYSTEMS CHARACTERISTICS                                       | 3                                                                                           |       |          |       |                  |

| Switching frequency, f <sub>SW</sub>                          |                                                                                             | 1.2   |          | 40    | kHz              |

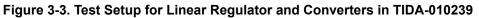

| Average efficiency                                            | 25%, 50%, 75%, 100% load average at nominal input voltages                                  | 84.8  | 85.5     | 86.2  | %                |

| Operating temperature                                         |                                                                                             |       | 25       |       | °C               |

|                                                               | ·                                                                                           |       | 1        |       |                  |

7

### 2.2.1.1 Input Bulk Capacitance and Minimum Bulk Voltage

The minimum voltage on the input bulk capacitance is needed to determine the maximum primary-to-secondary turns-ratio of the transformer. The input power of the converter based on target full-load efficiency, the minimum input RMS voltage, and the minimum AC input frequency determine the input capacitance requirement. Maximum input power is determined based on Equation 1:

$$P_{IN} = \frac{V_{OCV} \times I_{OCC}}{n} = \frac{12 V \times 2.2 A + |-14 V| \times 0.1 A + |+14 V| \times 0.1 A}{0.8} \approx 36.5 W$$

#### where

- V<sub>OCV</sub> is the regulated output voltage of the converter

- I<sub>OCC</sub> is the converter total output CC target

- η is the converter overall efficiency at full-power output

Equation 2 provides an accurate solution for the total input capacitance based on a target minimum bulk capacitor voltage. Alternatively, to target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance value.

$$C_{BULK} = \frac{2P_{IN} \times \left\{ 0.25 + \frac{1}{2\pi} \times \arcsin\left(\frac{V_{BULK}(\text{desired})}{\sqrt{2} \times V_{IN}(\text{min})}\right) \right\}}{\left(2V_{IN}(\text{min})^2 - V_{BULK}(\text{desired})^2\right) \times f_{LINE}(\text{min})} \approx 58.9 \,\mu F \tag{2}$$

$C_{BULK(selected)} = 68 \,\mu F$

Four 68- $\mu$ F electrolytic capacitors were used at the input to create an equivalent 68- $\mu$ F bulk capacitor to support a maximum input voltage of 460 V<sub>RMS</sub>. This selection changes the minimum V<sub>BULK</sub> voltage to 90.7 V (also called V<sub>BULK</sub> VALLEY) per the UCC28742 design calculator.

#### 2.2.1.2 Transformer Turns-Ratio, Primary Inductance, and Primary Peak Current

The target maximum switching frequency at full load, the minimum input-capacitor bulk voltage, and the estimated DCM resonant time determine the maximum primary-to-secondary turns-ratio of the transformer. Initially, determine the maximum-available total duty-cycle of the on-time and secondary conduction time based on the target switching frequency ( $f_{MAX}$ ) and DCM resonant time ( $t_R$ ).

At the transition-mode operation limit of DCM, the interval required from the end of the secondary current conduction to the first valley of the V<sub>DS</sub> voltage is  $\frac{1}{2}$  of the DCM resonant period (t<sub>R</sub>), or 1 µs assuming 500-kHz DCM resonant frequency. The maximum allowable MOSFET on-time D<sub>MAX</sub> is determined using Equation 4:

$$D_{MAX} = 1 - D_{MAGCC} - \left(\frac{t_R}{2} \times f_{MAX}\right) = 1 - 0.475 - 38 \, kHz \times \frac{2\,\mu s}{2} = 0.485 \tag{4}$$

where

- t<sub>R</sub> is the estimated period of the LC resonant frequency at the switch node

- D<sub>MAGCC</sub> is defined as the duty cycle of the secondary-diode conduction during CC operation and is fixed internally by the UCC28742 device at 0.475

When  $D_{MAX}$  is known, the maximum primary-to-secondary turns ratio is determined with Equation 5. The total voltage on the secondary winding must be determined, which is the sum of  $V_{OCV}$  and  $V_{F}$ .

$$N_{PS(max)} = \frac{D_{MAX} \times V_{BULK} \text{_VALLEY}}{D_{MAGCC} \times (V_{OCV} + V_F)}$$

(5)

Assuming V<sub>F</sub> = 0.8 V:

$$N_{PS(max)} = \frac{0.485 \times 90.7 V}{0.475 \times (12 V + 0.8 V)} = 7.24$$

(6)

$$N_{PS(selected)} = 7$$

(7)

8 AC Level 2 Charger Platform Reference Design

(3)

(1)

(9)

A higher turns-ratio generally improves efficiency, but can limit operation at a low input voltage. Transformer design iterations are generally necessary to evaluate system-level performance trade-offs.

The primary transformer inductance is calculated using the standard energy storage equation for flyback transformers. The primary current, maximum switching frequency, output voltage and current targets, and transformer power losses are included in Equation 8:

$$L_P = \frac{2 \times (V_{OCV} + V_F) \times I_{OCC}}{\eta_{XFMR} \times I^2 _{PP(max)} \times f_{MAX}} = 627.7 \,\mu H$$

(8)

$$L_{P(selected)} = 700 \,\mu H$$

The UCC28742 CC regulation is achieved by maintaining  $D_{MAGCC}$  at the maximum primary peak current setting. The product of  $D_{MAGCC}$  and  $V_{CST(max)}$  defines a CC-regulating voltage factor  $V_{CCR}$  which is used with  $N_{PS}$  to determine the current-sense resistor value necessary to achieve the regulated CC target,  $I_{OCC}$  (see Equation 10).

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2 \times I_{OCC}} \times \sqrt{g_{XFMR}}$$

(10)

$$R_{CS} = \frac{0.363 \, V \times 7}{2 \times 2.2 \, A} \times \sqrt{0.9} = 0.547 \, \Omega \tag{11}$$

$$R_{CS(selected)} = 0.5 \,\Omega \tag{12}$$

#### where

- V<sub>CCR</sub> is the CC regulation factor (from the UCC28742 High-Efficiency Flyback Controller with Optocoupler Feedback data sheet)

- V<sub>CST</sub> is the CS-pin current-sense threshold (from the *data sheet*)

$$I_{PP(max)} = \frac{V_{CST(max)}}{R_{CS}} = \frac{0.83 V}{0.5 \Omega} = 1.66 A$$

(13)

$$I_{PP(nom)} = \frac{V_{CST(nom)}}{R_{CS}} = \frac{0.77 \, V}{0.5 \, \Omega} = 1.54A \tag{14}$$

$N_{AS}$  is determined by the lowest target operating output voltage while in CC regulation and by the  $V_{DD}$  UVLO turnoff threshold of the UCC28742 device. Additional energy is supplied to  $V_{DD}$  from the transformer leakage-inductance which allows a lower turns ratio to be used in many designs.

$$N_{AS} = \frac{V_{DD}(off) + V_{FA}}{V_{OCC} + V_F} = \frac{8.15 \ V + 0.8 \ V}{5 \ V + 0.8 \ V} = 1.54$$

(15)

where

- V<sub>DD(off)</sub> is UCC28742 turnoff threshold (from the *data sheet*)

- V<sub>OCC</sub> is the lowest output voltage target of the converter while in constant-current regulation

- V<sub>FA</sub> is voltage drop across rectifier diode on auxiliary side of flyback stage

$N_{AS(selected)} = 1.455 \tag{16}$

This implies:

$$N_{PA(selected)} = 4.81$$

(17)

(19)

Since the ±14-V rails are unregulated, the turn ratio determines their output voltage:

$$N_{PT} = \frac{N_{PS}}{(V_{OV14} + V_F)/(V_{OCV} + V_F)} = \frac{7}{(14 V + 0.8 V)/(12 V + 0.8 V)} = 6.05$$

(18)

$N_{PT(selected)} = 5.92$

#### 2.2.1.3 Transformer Parameter Calculations: Primary and Secondary RMS Currents

With the primary inductance of 700 µH, the absolute maximum switching frequency is calculated from:

$$f_{MAX} = \frac{2 \times (12 V + 0.8 V) \times 2.2 A}{0.9 \times (1.54 A)^2 \times 700 \ \mu H} = 37.7 \ kHz \tag{20}$$

The maximum switching period is:

$$t_{SW} = \frac{1}{f_{MAX}} = \frac{1}{37.7 \ kHz} = 26.5 \ \mu s \tag{21}$$

The actual maximum on-time is given by:

$$t_{ON(\max)} = \frac{I_{PP(nom)} \times L_P}{V_{BULK_VALLEY}} = \frac{1.54 \, A \times 700 \, \mu H}{90.7 \, V} = 11.88 \, \mu s$$

(22)

The maximum duty cycle of operation (D<sub>MAX</sub>) is:

$$D_{MAX} = \frac{t_{ON}(max)}{t_{SW}} = \frac{11.88 \ \mu s}{26.5 \ \mu s} = 0.448 \tag{23}$$

The transformer primary RMS current (IPRMS) is:

$$I_{PRMS} = I_{PP(max)} \sqrt{\frac{D_{MAX}}{3}} = 1.66 \ A \times \sqrt{\frac{0.448}{3}} = 0.641 \ A \tag{24}$$

The transformer secondary peak current RMS current (I<sub>SEC(max)</sub>) is:

$$I_{SEC(max)} = I_{PP(max)} \times N_{PS} = 1.66 A \times 7 = 11.62 A$$

(25)

The transformer secondary RMS current (I<sub>SEC RMS</sub>) is:

$$I_{SEC\_RMS} = I_{SEC(max)} \sqrt{\frac{D_{MAX}}{3}} = 11.62 \ A \times \sqrt{\frac{0.448}{3}} = 4.49 \ A \tag{26}$$

Based on these calculations, a Würth Elektronik<sup>™</sup> transformer was designed for this application (part number 750320029), which has the following specifications:

- N<sub>PS</sub> = 7 ±2% (primary to secondary turns-ratio)

- N<sub>PT</sub> = 5.92 ±2% (primary to tertiary turns-ratio)

- N<sub>PA</sub> = 4.81 ±2% (primary to auxiliary turns-ratio)

- $L_P = 700 \pm 10\% \mu H$  (primary inductance)

- L<sub>LK</sub> = 10 μH (primary leakage inductance)

#### 2.2.1.4 Main Switching Power MOSFET Selection

The drain-to-source RMS current, I<sub>DS RMS</sub>, through switching FET is calculated using:

$I_{DS\_RMS} = I_{PRMS} = 0.641 A$

Select a MOSFET with five times the  $I_{DS_{RMS}}$  calculated. The maximum voltage across the FET can be estimated using:

(27)

$$V_{DSPK} = \left(V_{IN(max)} \times \sqrt{2}\right) + \left(V_{OCV} + V_F\right) \times N_{PS} + V_{LK} = \left(460 \ V \times \sqrt{2}\right) + \left(12 \ V + 0.8 \ V\right) \times 7 + 63 \ V = 803.1 \ V \tag{28}$$

Considering a de-rating of 15% and leakage spike of around 150 V, the voltage rating of the MOSFET must be around 925-V DC. A 950-V MOSFET is selected.

#### 2.2.1.5 Rectifying Diode Selection

Calculate the secondary output diode or synchronous rectifier FET reverse voltage or blocking voltage needed (V<sub>DIODE BLOCKING</sub>):

$$V_{DIODE\_BLOCKING} = \frac{V_{IN\_DC(max)}}{N_{PS}} + V_{OCV} = \frac{460 \ V \times \sqrt{2}}{7} + 12 \ V = 104.9 \ V$$

(29)

For this reference design, a 200-V, 24-A rated synchronous rectifier FET is selected for the +12-Vp rail to reduce losses. For the ±14 rails, Schottky diodes with 200-V voltage and 1-A forward current ratings are selected.

$$V_{DIODE\_BLOCKING\_AUX} = \frac{V_{IN\_DC(max)}}{N_{PA}} + (V_{OCV} + V_F) \times N_{AS} - V_{FA} = \frac{460 \ V \times \sqrt{2}}{4.81} + (12 \ V + 0.8 \ V) \times 1.455 - 0.6 \ V = 153 \ V(30)$$

For the auxiliary rail, a Schottky diode with 400-V voltage and 1-A forward current ratings is selected. Here normally a 200-V diode is sufficient, but spikes over 153 V must be considered. If a 300-V diode, is selected, the diode does not bring any advantage because 300-V and 400-V small diodes have no difference in terms of reverse recovery time, nor  $V_F$ .

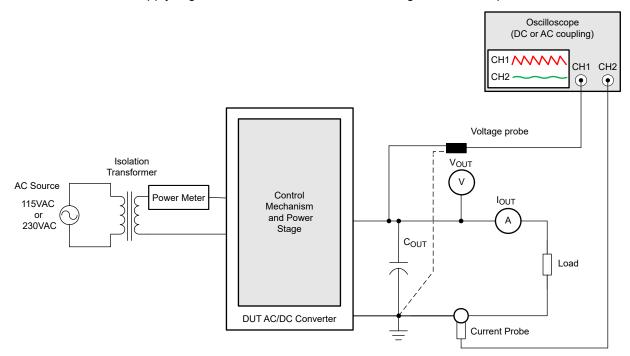

#### 2.2.1.6 Output Capacitor Selection

For this reference design, the output capacitor ( $C_{OUT}$ ) for output is selected to prevent  $V_{OUT}$  (12 V) from dropping below the minimum output voltage ( $V_{OTRM}$ ) during transients up to 0.1 V and ripple voltage less than 100 mV.

$$C_{OUT} \ge \frac{\frac{I_{OCC}}{2} \times \left(t\right)}{V_{OCV} - V_{OTRM}}$$

(31)

Assuming  $V_{OTRM}$  = 11.9 V,

$$C_{OUT} \ge \frac{\frac{2.2 A}{2} \times (50 \ \mu s)}{12 \ V - 11.9 \ V} \ge 550 \ \mu F$$

(32)

$C_{OUT(selected)} = 2 \times 680 \,\mu F \tag{33}$

Considering the allowable output ripple voltage of 100 mV (5%), the ESR and RMS current of the capacitor must be:

$$ESR = \frac{V_{OUT\_RIPPLE}}{I_{SEC(max)}} = \frac{200 \ mV}{11.62 \ A} = 17.2 \ m\Omega$$

(34)

$$I_{COUT\_RMS} = \sqrt{\left(I_{SEC\_RMS}\right)^2 - \left(I_{OCC}\right)^2} = \sqrt{\left(4.49 \ A\right)^2 - \left(2.2 \ A\right)^2} = 5.0 \ A \tag{35}$$

#### 2.2.1.7 Capacitance on VDD Pin

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage in CC regulation. The capacitance on VDD must supply the primary-side operating current used during start-up and between low-frequency switching pulses. The largest result of two independent calculations denoted in Equation 36 determines the value of  $C_{VDD}$ .

At start-up, when  $V_{VDD(on)}$  is reached,  $C_{VDD}$  alone supplies the device operating current and MOSFET gate current until the output of the converter reaches the target minimum operating voltage in CC regulation,  $V_{OCC}$ . Now the auxiliary winding sustains VDD for the UCC28742 device above UVLO. The total output current available to the load and to charge the output capacitors is the CC-regulation target,  $I_{OCC}$ . Equation 36 assumes that all of the output current of the converter is available to charge the output capacitance until  $V_{OCC}$  is achieved.

(37)

(40)

(43)

For typical applications, Equation 37 includes an estimated q<sub>G</sub> × f<sub>SW(max)</sub> of average gate drive current and a 1-V margin added to V<sub>VDD</sub>.

$$C_{VDD} \ge \frac{\left(I_{RUN} + q_G f_{SW}(max)\right) \times \frac{C_{OUT} \times V_{OCC}}{I_{OCC}}}{V_{DD}(on) - \left(V_{DD}(off) + 1 V\right)}$$

(36)

$$C_{VDD} \ge \frac{\left(2 \ mA + 10 \ nC \times 37.7 \ kHz\right) \times \frac{1360 \ \mu F \times 12 \ V}{2.2 \ V}}{21 \ V - (8.5 \ V + 1 \ V)} \ge 0.128 \ \mu F$$

(37)

The current design uses 10-µF and 0.1-µF capacitors.

#### 2.2.1.8 Open-loop Voltage Regulation Versus Pin Resistor Divider, Line Compensation Resistor

The resistor divider at the VS pin determines the output voltage regulation point of the flyback converter. Also, the high-side divider resistor (R<sub>S1</sub>) determines the line voltage at which the controller enables continuous DRV operation. R<sub>S1</sub> is initially determined based on transformer auxiliary-to-primary turns ratio and desired input voltage operating threshold.

$$R_{S1} = \frac{V_{IN}(run) \times \sqrt{2}}{N_{PA} \times I_{VSL}(min)}$$

(38)

where

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio

- $V_{IN(run)}$  is the AC<sub>RMS</sub> voltage to enable turn-on of the controller (run); in case of DC input, leave out the  $\sqrt{2}$ term in the equation

- V<sub>SL(run)</sub> is the run threshold for the current pulled out of the VS pin during the switch on-time (see the Electrical Characteristics section of the UCC28742 data sheet)

$$R_{S1} = \frac{80 \, V \times \sqrt{2}}{4.81 \times 210 \, \mu A} = 112 \, k\Omega \tag{39}$$

$R_{S1(selected)} = 121 \ k\Omega$

The low-side VS pin resistor is selected based on the desired V<sub>OUT</sub> regulation voltage in open-loop conditions and sets the maximum allowable voltage during open-loop conditions.

$$R_{S2} = \frac{R_{S1} \times V_{OVPTH}}{N_{AS} \times (V_{OV} + V_F) - V_{OVPTH}}$$

(41)

where

- V<sub>OV</sub> is the maximum allowable peak voltage at the converter output

- V<sub>F</sub> is the output-rectifier forward drop at near-zero current

- N<sub>AS</sub> is the transformer auxiliary-to-secondary turns ratio

- V<sub>OVPTH</sub> is the overvoltage detection threshold at the VS input (see the Electrical Characteristics section of the UCC28742 data sheet)

$$R_{S2} = \frac{121 \ k\Omega \times 4.65 \ V}{1.455 \times (15 \ V + 0.8 \ V) - 4.65 \ V} = 30.7 \ k\Omega \tag{42}$$

$$R_{S2(selected)} = 33.2 \ k\Omega$$

The UCC28742 device maintains tight CC regulation over varying input lines by using the line-compensation feature. The line-compensation resistor ( $R_{IC}$ ) value is determined by the current flowing in  $R_{S1}$  and the total internal gate drive and external MOSFET turn-off delay. Assuming an internal delay of 50 ns in the UCC28742 device:

TEXAS INSTRUMENTS www.ti.com

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times t_D \times N_{PA}}{L_P}$$

System Overview

(44)

(46)

- t<sub>D</sub> is the current-sense delay including MOSFET turn-off delay

- K<sub>LC</sub> is a current-scaling constant (see the Electrical Characteristics section of the UCC28742 data sheet)

$$R_{LC} = \frac{25 \times 121 \ k\Omega \times 0.5 \ \Omega \times (46 \ ns + 50 \ ns) \times 4.81}{700 \ \mu H} = 998 \ \Omega \tag{45}$$

$$R_{LC(selected)} = 1 k\Omega$$

#### 2.2.1.9 Feedback Elements

The output voltage is set through the sense network resistors  $R_{FB1}$  and  $R_{FB2}$ . Select the value of the feedback resistor based on the desired output voltage with:

$$V_{th} = \frac{V_{OCV} \times R_{FB2}}{R_{FB1} + R_{FB2}} \tag{47}$$

where

The op amp compensation network,  $Z_{FB}$ , is determined using well-established design techniques for control-loop stability. Typically, a type-II compensation network is used. See the *UCC28742 data sheet* and the design calculator for details.

#### 2.2.1.10 Backup Power Supply

There are three possible power scenarios:

1. Single or three-phase power available:

- a. The converter supplies all voltages and charges the supercapacitors in a variable time between 1 minute and 21 seconds as first charge, and 36 seconds as successive recharges.

- b. The switching waveform present on the secondary side winding is peak-rectified and is used to disable the inverting buck-boost.

- c. At the same time, as the voltage on the supercapacitors is in the range 4.3 V–7.8 V, the boost converter is active and delivers 11.5 V. This voltage level, slightly lower than 12 V, is on purpose to avoid delivering current when mains is present. Keeping the boost converter active eliminates the delay due to the device soft start.

- d. When the supercapacitors are charged, a voltage supervisor TL7705A is enabling the flag "EOC" (end of charge, useful for a digital output to uC) and turning an LED on.

- 2. Power unavailable:

- a. Since the boost converter with TPS55330 is always active, the 12-Vp bus droops from 12 V to 11.5 V, keeping all rails alive.

- b. At the same time, both ± 14-V outputs from the flyback converter go to zero and the peak rectified voltage used for the signal *Disable* goes to zero.

- c. Then the inverting buck-boost starts and supplies  $\pm 14$  V, which are connected by ORing diodes to the input of the dual LDO, supplying  $\pm 12$  V.

- d. The power is delivered until the supercapacitors are discharged below boost UVLO (4.3 V). At this point all rails are off.

- 3. 12-V bench supply on:

- a. Here the supercapacitors are not recharged because there is no voltage on auxiliary winding of the flyback.

- b. The 12 V from bench power is supplying all the rails normally. The inverting buck-boost is also supplying ±14 V for dual LDO.

#### 2.2.1.11 Supercapacitor Selection

The supercapacitors supplies the 12-V and the 5-V rails (AM62 SOM) in case of unexpected AC input shut down to turn off the main relay and unlock the plug. Assume 1 s duration time as the initial specification.

- 12-V rail: Peak current 1.8 A for 200 ms (unlock plug and relay off)

- 12-V rail: Average current 1.8 A × 0.2 s + 0.1 A × 0.8 s = 0.44 A

- 5-V rail: Average current 0.275 A for 1 s

The total peak power required from supercap, PPK SC:

$$P_{PK\_SC} = (V_{12Vp} \times I_{PK\_1} + V_{5V} \times I_{PK\_2} / \eta_{BUCK}) / \eta_{BOOST}$$

$$\tag{48}$$

Total 27.2 W peak for 200 ms or a peak current of approximately 3.5 A (that is, 27.2 W / 7.8 V). Total average power required from supercapacitor, PAVE SC:

$$\mathsf{P}_{\mathsf{AVE}\_\mathsf{SC}} = (\mathsf{V}_{12\mathsf{V}\mathsf{p}} \times \mathsf{I}_{\mathsf{A}\mathsf{VE}\_1} + \mathsf{V}_{\mathsf{5V}} \times \mathsf{I}_{\mathsf{A}\mathsf{VE}\_2} / \eta_{\mathsf{BUCK}}) / \eta_{\mathsf{BOOST}}$$

(50)

$$P_{AVE\_SC} = (12 V \times 0.44 A + 5 V \times 0.275 A / 0.9) / 0.85 = 8 W \text{ (that is, 8 J in 1 s)}$$

(51)

Consider that the supercapacitor is charged up to 7.8 V and then discharged down to 4.3 V (that is, UVLO of the TPS55330 boost converter):

$$C_{\text{MIN}\_\text{SERIES}} = 2 \times (E) / ((V_2)^2 - (V_1)^2) = 2 \times (8 \text{ J}) / ((7.8 \text{ V})^2 - (4.3 \text{ V})^2) = 0.3778 \text{ F.}$$

(52)

$$C_{MIN} = 2 \times C_{MIN\_SERIES} = 0.76 \text{ F (for 1 s)}$$

(53)

where

- C<sub>MIN SERIES</sub> is the minimum equivalent series capacitor

- C<sub>MIN</sub> is the minimum individual capacitance

Now, for 3 s we need  $C_{MIN} = 3 \times 0.76 = 2.28$  F.

For this design, two 2.5-F in series that support up to 47.5 W and 4 A peak are selected.

Note that the TL7705 voltage supervisor monitors for charge completion at an slightly lower voltage of 7.49 V. The supercapacitor energy available from 7.49 V to 4.3 V, E<sub>SC 7p5</sub>:

$$E_{SC_{7p5}} = 0.5 \times C \times (V_1^2 - V_2^2) = 0.5 \times 1.25 F \times (7.49^2 - 4.3^2) = 23.5 J$$

(54)

The energy available after accounting for boost efficiency, E<sub>SC 7p5 BOOST</sub>:

$$E_{SC 7p5 BOOST} = E_{SC 7p5} \times \eta_{BOOST} = 23.5 J \times 0.85 = 20 J$$

(55)

The power available during 3 s, P<sub>SC 7p5</sub>:

$$P_{SC_{7p5}} = E_{SC_{7p5}BOOST} / time = 20 J / 3 s = 6.65 W$$

(56)

The supercapacitor energy available from 7.8 V to 4.3 V, E<sub>SC 7p8</sub>:

$$E_{SC, 7n8} = 0.5 \times C \times (V_1^2 - V_2^2) = 0.5 \times 1.25 F \times (7.8^2 - 4.3^2) = 26.5 J$$

(57)

The energy available after accounting for boost efficiency, E<sub>SC 7p8 BOOST</sub>:

The power available during 3 s, P<sub>SC\_7p8</sub>:

P<sub>SC 7p8</sub> = E<sub>SC 7p8 BOOST</sub> / time = 22.5 J / 3 s = 7.5 W

(59)

### 2.2.1.12 Supercapacitor Charger Design

The shunt voltage reference (U6\_P) sets the final charge voltage to 7.8 V. The NPN transistor (Q4\_P) and  $4.99-\Omega$  resistor (R38\_P) limit the charge current to approximately 120 mA (0.6 V / 4.99  $\Omega$ ). The NMOS FET (Q3\_P) operates in saturation region to maintain the required charge voltage drop. U6\_P pulls down the gate of Q3\_P as soon as Vbackup (as shown in the schematic) reaches 7.8 V. This way, Vbackup stays constant at the nominal 7.8 V. There are two charging scenarios:

- Charging time as first power supply turn-on: here Vbackup is zero. The ΔV that must be covered is from zero to 7.8 V; therefore, the charging time is ΔT = C × ΔV / I = 1.25 F × 7.8 V / 120 mA = 81.25 seconds (1 minute and 21 seconds).

- 2. Charging time after energy storage release: here Vbackup is the UVLO of the boost converter (4.3 V). The  $\Delta V$  that must be covered is from 4.3 V to 7.8 V; the charging time is  $\Delta T = C \times \Delta V / I = 1.25 F \times (7.8 V 4.3 V) / 120 mA = 36.46$  seconds.

In summary, the worst-case charging time is 1 minute and 21 seconds, while recharging between energy storage releases is 36.46 seconds.

### 2.2.2 Control Pilot Signal Interface

The control pilot circuit is the primary control means to make sure of proper operation when connecting an EV or PHEV to the EVSE. The pilot signal is the key method through which a J1772-compliant EVSE communicates with a vehicle. The pilot signal is based on a 1-kHz,  $\pm$ 12-V PWM signal that is transmitted to a vehicle over the charging chord. The vehicle can then respond by placing various loads on the line, affecting the voltage, which the EVSE measures.

#### 2.2.2.1 J1772 Duty Cycle

The duty cycle of the pilot signals communicate the limit of current the EVSE is capable of supplying to the vehicle; the vehicle can then use up to that amount of current for the charging circuitry. This current rating is primarily determined by the electromechanical components in the EVSE, such as conductors, relays, contactors, and the service connection.

The relationship between duty cycle and current is defined by two different equations depending on the current range specified; for a 6- to 51-A service, is:

$$\mathsf{Duty cycle} = \frac{\mathsf{Amps}}{0.6} \tag{60}$$

For a higher service in the 51- to 80-A range, is:

Duty cycle =

$$\frac{\text{Amps}}{2.5} + 64$$

(61)

To demonstrate this relationship further, Table 2-2 shows some of the common service ratings.

| Table 2-2. Thot Signal Example Duty Cycle |            |  |  |  |

|-------------------------------------------|------------|--|--|--|

| AMPS                                      | DUTY CYCLE |  |  |  |

| 5                                         | 8.3%       |  |  |  |

| 15                                        | 25%        |  |  |  |

| 30                                        | 50%        |  |  |  |

| 40                                        | 66.6%      |  |  |  |

| 65                                        | 90%        |  |  |  |

| 80                                        | 96%        |  |  |  |

|                                           |            |  |  |  |

Table 2-2. Pilot Signal Example Duty Cycle

In this design, the PWM is generated by a timer module on the MSP430<sup>™</sup> MCU. The current rating can typically be set as a permanent value in the firmware because the current rating is so tightly coupled to the external hardware.

Advanced EVSEs with a human machine interface (HMI) can enable the current to be derated if the service line is unable to provide enough current with a stable voltage. A significant voltage drop as a result of wire loss is possible in these high-current applications.

#### 2.2.2.1.1 Control Pilot Signal States

The EVSE connection and negotiation occurs through various states of the PWM signal and load resistances of the vehicle. Table 2-3 highlights these states.

| STATE   | PILOT HIGH VOLTAGE | PILOT LOW VOLTAGE | FREQUENCY | RESISTANCE | DESCRIPTION                       |  |

|---------|--------------------|-------------------|-----------|------------|-----------------------------------|--|

| State A | 12 V               | N/A               | DC        | N/A        | Not connected                     |  |

| State B | 9 V                | –12 V             | 1 kHz     | 2.74 kΩ    | EV connected, ready to charge     |  |

| State C | 6 V                | –12 V             | 1 kHz     | 882 Ω      | EV charging                       |  |

| State D | 3 V                | –12 V             | 1 kHz     | 246 Ω      | EV charging, ventilation required |  |

| State E | 0 V                | 0 V               | N/A       |            | Error                             |  |

| State F | N/A                | –12 V             | N/A       | _          | Unknown error                     |  |

Table 2-3. Pilot Signal State Parameters

States A, B, and C are the core functionality and define the normal operation. An EVSE typically performs several self-tests upon initially powering on and then enters State A. When ready, the normal connection process follows several steps:

- 1. The EVSE puts 12 V on the pilot wire. This transmission signals the vehicle when the plug is connected.

- 2. When the plug is connected, the vehicle places a 2.74-k $\Omega$  load on the pilot line, which drops the voltage to 9 V.

- 3. The EVSE moves to State B, where the EVSE enables the PWM, which signals the vehicle how much current the vehicle can draw. The EVSE also closes the relays, providing power to the vehicle.

- 4. The vehicle starts to draw power and switches to the  $822-\Omega$  load, which drops the voltage to 6 V, signaling the EVSE that charging has started.

- 5. Most vehicles continue to pull low amounts of power in state C, even when fully charged, so the charging process is ended by unplugging the cable, which returns the voltage to 12 V. The EVSE measures this process and closes the relays and returns to State A.

Additional error handling such as missing diodes in the vehicle or an improper connection can be detected and handled by the EVSE by cutting the power, as well.

#### 2.2.2.1.2 Control Pilot Signal Circuit

The pilot signal is required to travel down several meters of cable and through a load resistance. The pilot signal is also a bipolar  $\pm 12$ -V signal, which requires special consideration. To accommodate these parameters, an amplifier with a wide input range and reasonable power output is selected. The TLV1805 device has a voltage rating of  $\pm 18$  V and a current rating of 475 mA, making the device a good match for the application. In addition, while most EVSEs do not require an automotive qualification, a Q1-rated variant of the TLV1805-Q1 device exists, if this feature is desired.

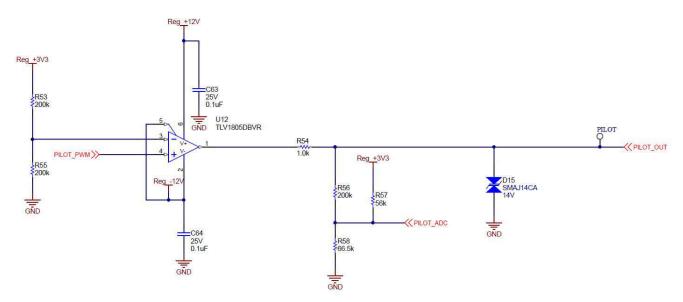

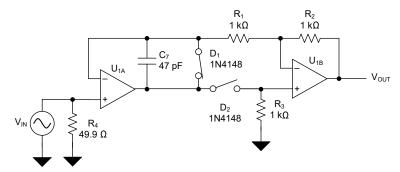

The amplification circuit is a simple rail-to-rail output configuration of the TLV1805 device, with the MCU I/O driving the positive input. The output of the pilot amplifier is also fed into a simple voltage divider so that the MCU can measure the voltage during operation and detect the load resistance of the vehicle. Figure 2-3 shows the full schematic of this subsystem.

Figure 2-3. Control Pilot Signal Generator Circuit

To validate the architecture, the design was tested in the TINA-TI<sup>™</sup> software from TI, which is a spice-based simulation tool.

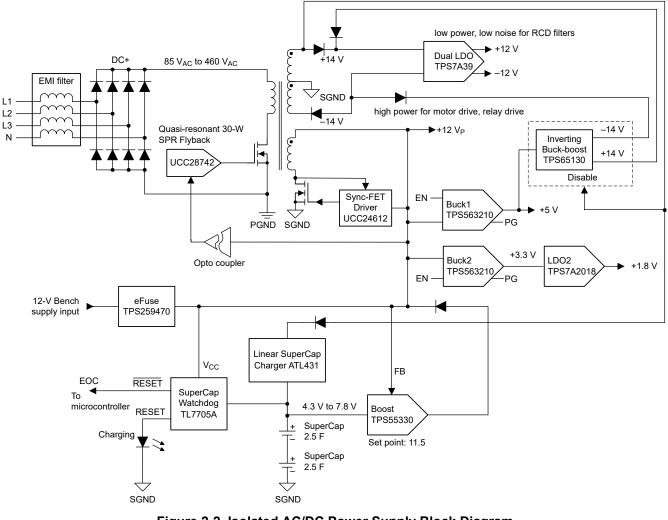

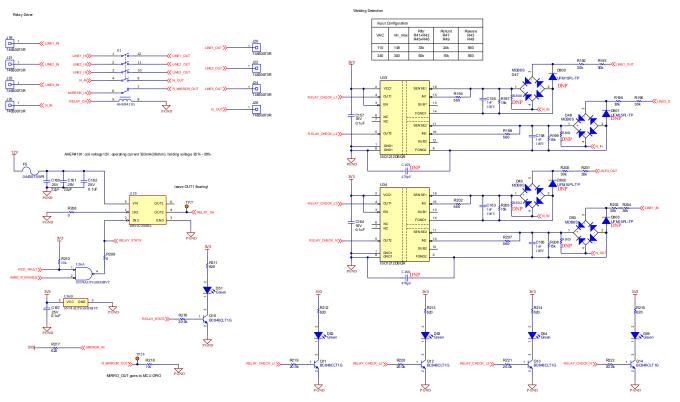

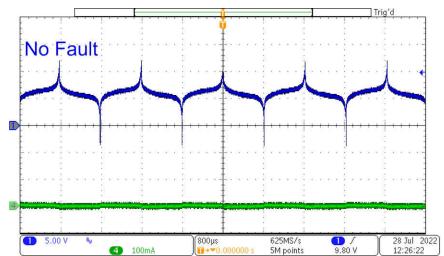

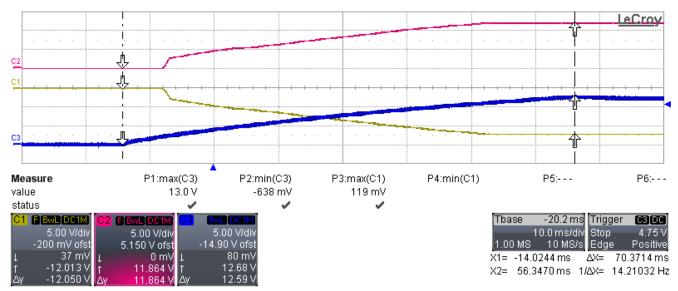

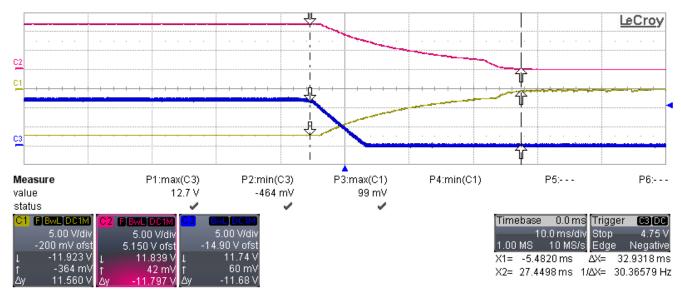

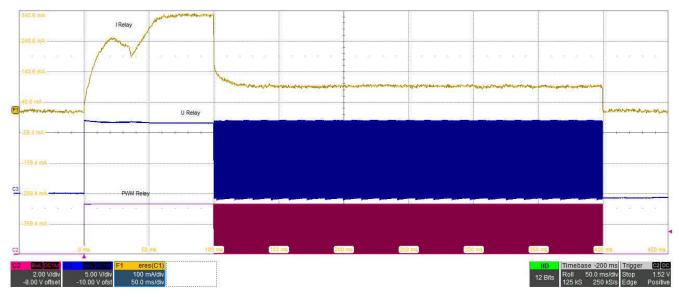

## 2.2.3 Relay Drive and Weld Detect

The primary functionality of the EVSE is the reliable control of large currents directed toward an electric vehicle at the mains voltage. In a normal use case, the relay or contactor must be held closed for several hours to fully charge a vehicle; however, the relays cannot be welded because of safety concerns. If something fails in the control system, the relays must fail open. These high current relays or contactors can typically draw tens to hundreds of milliamps as an inductive load, requiring specific drive architectures.

Because of the amount of time that a relay or contactor requires to remain powered, an efficient drive device is preferred to the typical Darlington array, or even discrete transistor configuration. For this reason, the DRV8220 current controller is selected to drive the relays or contactors in the design. The DRV8220 device is designed to regulate the current with a well-controlled waveform to reduce power dissipation.

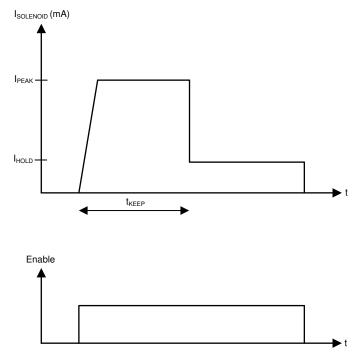

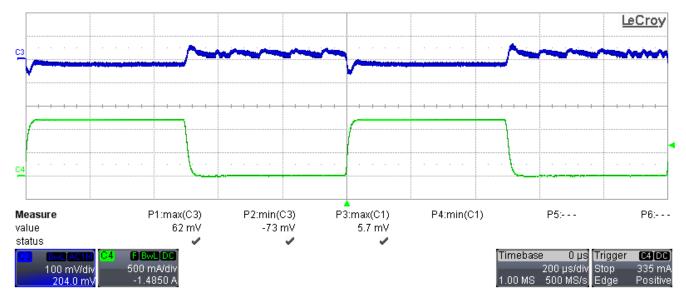

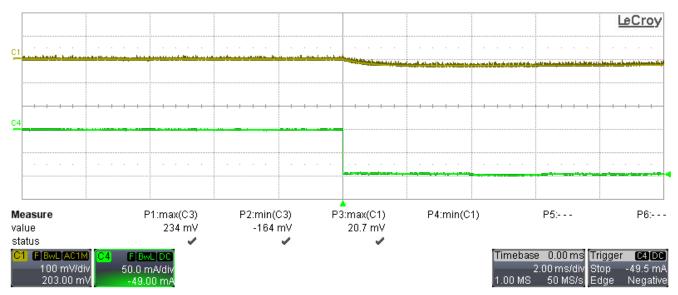

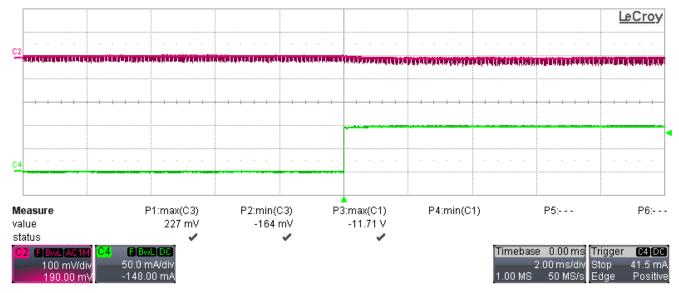

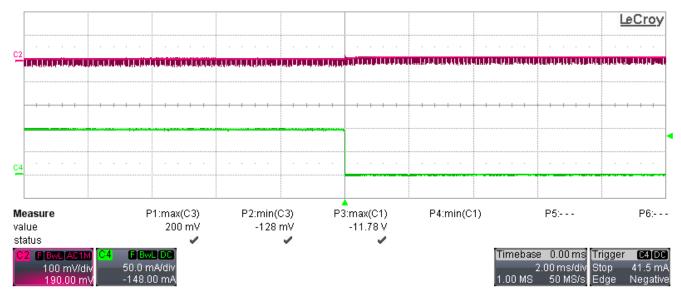

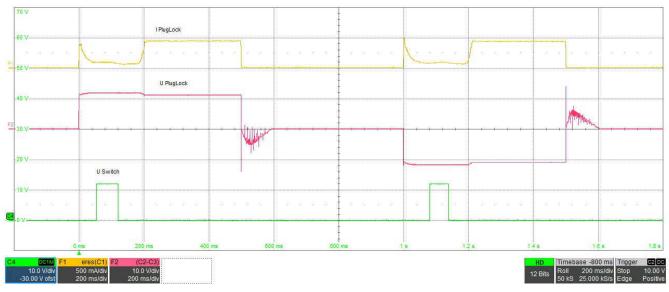

Relays and contactors use electromechanical solenoids for their operation. Activation starts when EN pin voltage is pulled high either by an external driver or internal pullup. Once the EN pin is driven to GND, the DRV8220 device allows the solenoid current to decay to zero. The solenoid current is ramped up fast to enable opening of the relay or contactor. After initial ramping, the solenoid current is kept at a peak value to maintain correct operation, after which the current is reduced to a lower hold level to avoid thermal problems and reduce power dissipation.

Figure 2-4. Typical Current Waveform Through the Solenoid

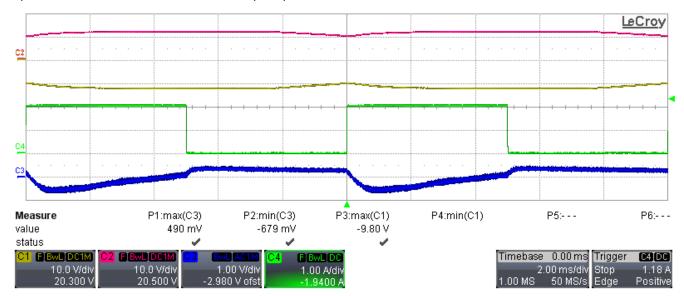

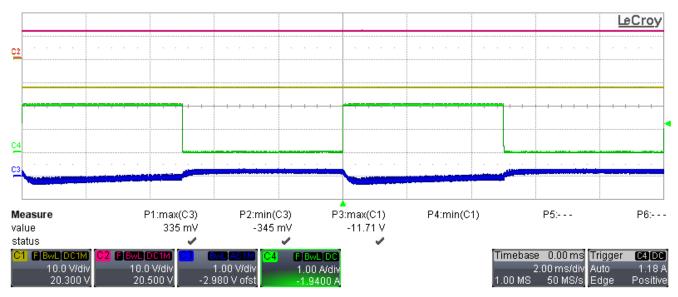

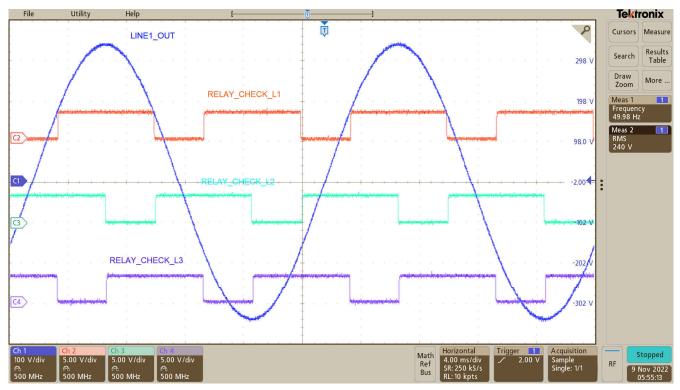

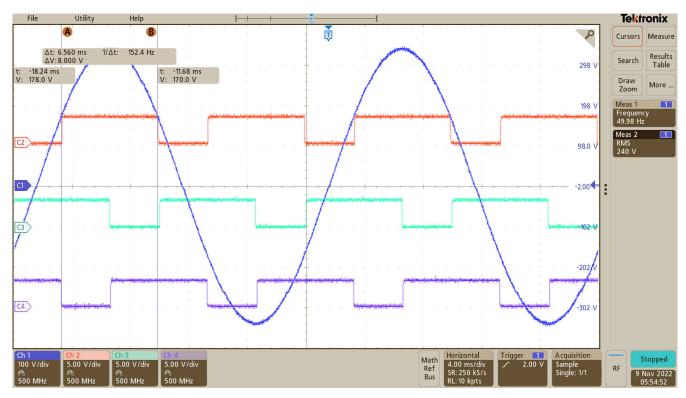

For safety reasons, detecting the output voltage of the primary relay is critical. The contacts can experience arcing and become fused together, providing power to the plug even when the contacts are not enabled. Checking that the operation completed correctly is important and must be done every time the relay is opened. To implement this check, the ISO1212 fully-integrated, isolated digital-input receiver is used to sense line voltage.

The outputs (OUT1 and OUT2) from the ISO1212 device are GPIO-level DC signals that are high when voltage is present and are fed directly into the MCU for fault detection. For this reference design, the high and low thresholds are set to 125  $V_{RMS}$  and 121  $V_{RMS}$ , respectively. The full circuit is shown in Figure 2-5. To learn more about AC and DC detection with ISO1212, see *ISO121x Threshold Calculator for 9V to 300V DC and AC Voltage Detection*.

Figure 2-5. AC Weld Detect Circuit

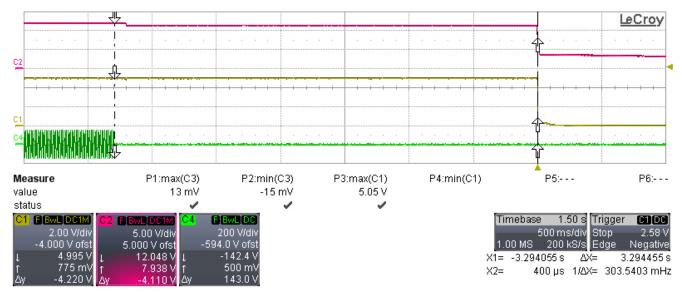

### 2.2.4 Residual Current Detection

This reference design implements a discrete version of residual current detection (RCD) capable of detecting two types of ground faults, AC current of 30 mA<sub>RMS</sub> and DC current of 6 mA. This detection is enabled utilizing an auto-oscillation circuit along with a receiver filter circuit. For the auto-oscillation circuit, the DRV8220 H-bridge is used to drive the magnetic core in and out of saturation. In addition, a feedback circuit is used to determine when the core reaches saturation and switches the drive coil current in the opposite direction. This enables the design to detect small amounts of DC current with a single toroidal magnetic core. The receive filter stage is used to filter the auto-oscillation driving frequency and signal condition the fault current signal. This filtered signal is captured by the internal ADC of the MSP430 with a sampling rate of 25,000 samples per second. The signal highest and lowest values are stored over 10 ms to determine if the fault type is AC or DC. The AC and DC trip thresholds can be adjusted via software to support different regional specifications. If the stored values are above trip thresholds, the MCU outputs a GPIO high, which is intended to interface with a relay driver to trip the relay. The GPIO returns low when the fault current lowers below an adjustable hysteresis. A summary of the sub-circuits follows for the AC and DC leakage current detection circuit.

#### Note

The following RCD description references component designators from the TIDA-010237 schematic. For a more detailed RCD description see the TIDA-010237 user's guide.

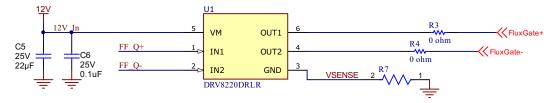

#### 2.2.4.1 Auto-Oscillation Circuit

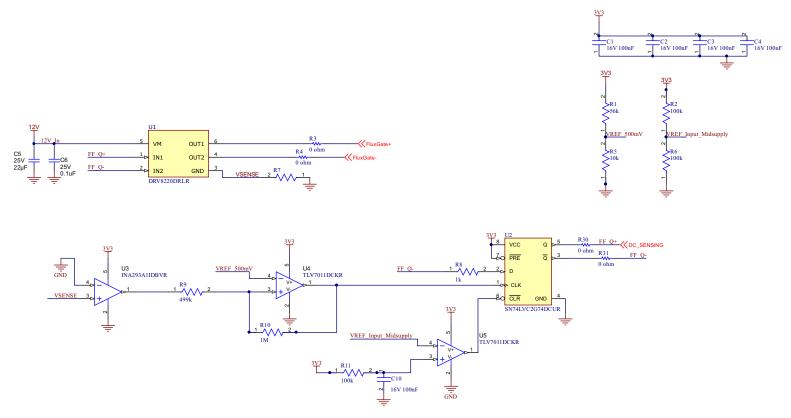

The auto-oscillation sub-circuit detects when the fluxgate sensor reaches saturation, then reverses the current direction. When saturation is reached, current sense voltage exceeds the comparator threshold, which causes the DFF to flip control signals to the DRV8220 H-bridge. This drives the fluxgate sensor core to saturation in the opposite direction.

Figure 2-6. Auto-Oscillation Circuit Schematic

This circuit monitors the current flowing through the fluxgate and reverses drive current direction once saturation is reached. The auto-oscillation circuit is needed to detect DC faults.

The phase lines and neutral wires go through a fluxgate sensor. During normal operation without a fault condition, the sum of currents equals zero.

During a ground fault condition, the sum of currents is not equal to zero. During a DC fault, there is an imbalance of current flowing through the line and current returning through the neutral wire. The fluxgate does not detect steady DC current. An oscillating drive current is pushed through the fluxgate sensor coil. This DC fault current produces a magnetic field which opposes fluxgate drive in one direction, and assists fluxgate drive in the opposite direction; resulting in a duty cycle shift. Under normal conditions, the duty cycle of the switching is 50%. During a DC fault, the duty cycle shifts.

The oscillation frequency depends on the signal chain between R7 to pin 1 of the DFF. Match the current sense amplifier gain and  $V_{REF}$  voltage to make sure the core is driven to saturation. Driving the core deeper into saturation reduces noise, removing the need for degaussing. When the core is fully saturated, all material within the core is magnetically aligned. When all material is aligned, there are no stray fields within the material to contribute noise.

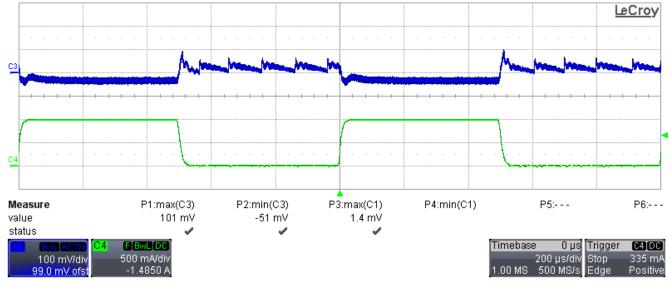

### 2.2.4.2 DRV8220 H-Bridge

The DRV8220 is an integrated motor driver with four N-channel power FETs, charge pump regulator, and protection circuitry. The device can supply up to 1.76 A of output current, operating on a supply voltage from 4.5 V to 18 V. The driver offers robust internal protection including undervoltage lockout, output overcurrent, and device overtemperature. The DRV8220 drives current through the magnetic core to saturate the core. This device is the smallest, most cost-effective device capable of driving enough current. The output of the DRV8220 is controlled by pins 1 and 2. The state of these pins determines which direction current flows through the magnetic coil. When the saturation detection circuit threshold is passed, the control signals to pins 1 and 2 flip, which flips the DRV8220 output. The low-side current sense resistor (R7) detects current through the DRV8220. The current spikes when the core reaches saturation, which is read by the saturation detection circuit.

Figure 2-7. DRV8220 Schematic

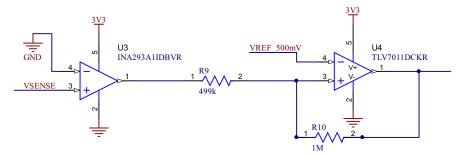

### 2.2.4.3 Saturation Detection Circuit

The saturation detection circuit is made of the low-side current sense resistor (R7), current sense amplifier INA293, and comparator TLV7011. The comparator outputs high when the fluxgate sensor coil saturation is reached. The circuit shown in Figure 2-8 is used to determine when the fluxgate sensor has reached saturation.

Figure 2-8. Saturation Detection Schematic

$V_{SENSE}$  is read from the low-side shunt resistor of the DRV8220.  $V_{SENSE}$  gives the current through the fluxgate sensor coil. This signal is gained up by current sense amplifier INA293, with a fixed gain of 20 V/V. The gained signal is compared to a reference voltage  $V_{REF}$  of 500 mV, which is sourced from a resistor divider. When the current sense signal passes the  $V_{REF}$  voltage, the core has saturated and the DRV8220 must switch the output directions. The output of comparator TLV7011 feeds into a DFF which is explained more in the H-Bridge Controlled by DFF section.

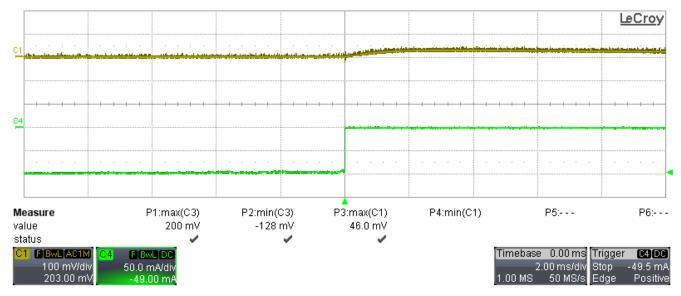

Figure 2-9. Burden Resistor Going Into Saturation

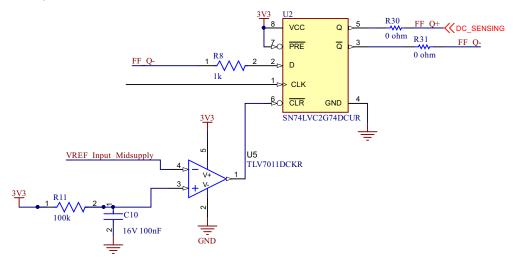

#### 2.2.4.4 H-Bridge Controlled by DFF

The output logic to control DRV8220 reverses output Q with each positive CLK edge. The DFF circuit reverses output Q with each positive CLK edge. Inverted output  $\overline{Q}$  is connected to input data D, so each positive clock edge inverts the outputs.

Figure 2-10. DFF SN74LVC2G74 Circuit

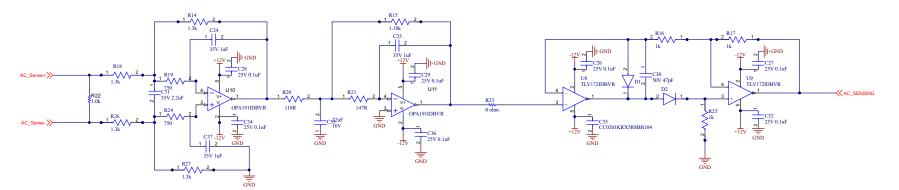

# 2.2.4.5 Filter Stage

The three goals of filter stage are to gain the ground fault detection signal, filter the noise created by the auto-oscillation circuit, and correct a DC bias inherent to the fluxgate core. The filter filters noise in the signal path from the burden resistor to the ADC. Too much noise can trigger false trips. The major source of noise is switching noise caused by the auto-oscillation circuit generating switching of the DRV8220. The auto-oscillation switching frequency changes with fluxgate sensor permeability, burden resistance, or adjusting the saturation detection circuit. The Hitachi nanocrystalline cores used for testing ranged from 600 Hz to 800 Hz with a  $1-k\Omega$  burden resistor.

During a fault, the filter stage outputs a detectable signal read by the ADC. A fault trip occurs when the filter stage output signal passes a threshold and the MCU determines the fault type, as AC and DC faults have separate trip thresholds adjustable within software. In this design with a gain of 20 dB, a DC fault of 6-mA outputs a 200-mV offset. An AC fault of 30-mA<sub>RMS</sub> outputs a peak of 600 mV. The gain can be increased, make sure the trip threshold is below the rail of op amps. The filter stage is designed to gain the fault signal by 20 dB and attenuate frequencies above 70 Hz. The filter stage consists of four subsections: differential to single end, low-pass filter, full-wave rectifier, and a DC offset circuit in place of R23.

The filter topology used is the Multiple FeedBack (MFB) topology and is often preferred due to low sensitivity to component variations. The MFB topology creates an inverting second-order stage. This inversion can be a concern in the filter application. The MFB filter circuit can be configured as a low-pass filter, high-pass filter, or band-pass filter based on the component selection. For this application, a fourth-order low-pass filter with a Butterworth response was used.

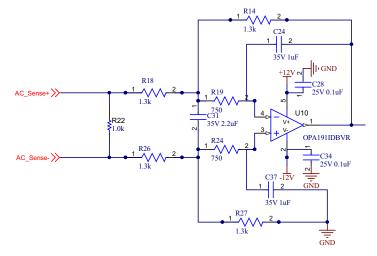

### 2.2.4.6 Differential to Single-Ended Converter

The differential to single-end conversion is performed by the first part of the signal chain. The first op amp converts the differential signal across the fluxgate burden resistor to a single-ended signal. This simplifies later signal conditioning and allows the ADC to read a ground referenced signal. R22 is the burden resistor across the coils of the fluxgate sensor.

Impedance matching to op amp inputs is important to minimize error. Mismatched impedance adds error to the fault detection signal. Trace from R22 to U10 can be similar to reduce error. To increase the ground fault signal, replace R18 and R26 with buffer op amps or resistors an order of magnitude larger. A higher impedance relative to the burden resistor (R22) gives a higher ground fault signal due to the resistor divider effect.

Figure 2-12. Differential to Single-Ended Schematic

#### 2.2.4.7 Low-Pass Filter

The low-pass filter is optimized to attenuate auto-oscillation frequencies. The goal is to reduce noise to prevent false trips. This design has a gain of 20 dB at 0 Hz and a cutoff frequency of 70 Hz. The auto-oscillation frequency depends on many variables: magnetic core material, burden resistance, and the auto-oscillation signal chain. This design with a nanocrystalline core material results an oscillation around 800 Hz. The low-pass filter is optimized to attenuate noise created by the auto-oscillation circuit.

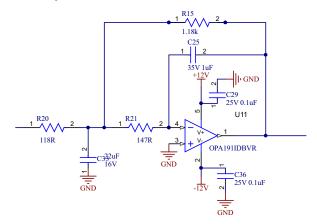

Figure 2-13. Low-Pass Filter Schematic

#### 2.2.4.8 Full-Wave Rectifier

The full-wave rectifier only flips negative voltage to positive. The full-wave rectifier allows the same trip threshold for negative and positive fault current. The other reason for using the full-wave rectifier is to convert the negative polarity of the signal to positive voltage within the input range of the ADC of the MCU and prevent Electrical Overstress (EOS).

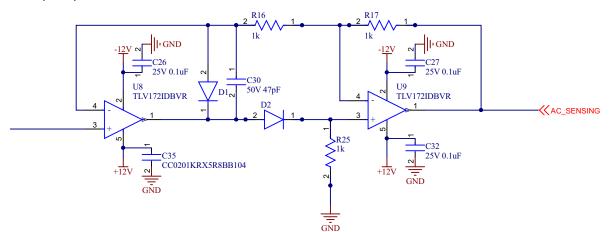

Figure 2-14. Full-Wave Rectifier Schematic

This precision full-wave rectifier can turn alternating current (AC) signals to single polarity signals. The op amps, U8 and U9, buffer the input signal and compensate for the voltage drops across D1 and D2 allowing for small signal inputs. The circuit is used in this application to quantify the absolute value of input signals which have both positive and negative polarities.

This topology was chosen over other full-wave rectifier topologies for the simplicity while achieving the desired performance. U1A and U1B control the biasing of D1 and D2 to change the signal path based on the polarity of the input signal achieving the full-wave rectification. The input impedance of the circuit is set by the termination resistor R4 and can be set to match the source impedance or as high as the input impedance of the U1A amplifier.

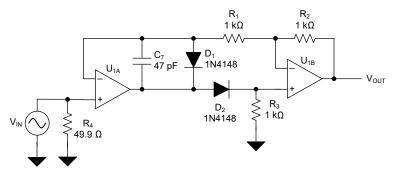

Figure 2-15. Circuit Schematic

Figure 2-16 and Equation 62 show the circuit schematic and transfer function for positive input signals. Positive input signals reverse-bias D1 and forward-bias D2 making the components act like an open circuit and short circuit, respectively. In this configuration, the U1A amplifier drives the non-inverting input of U1B such that the voltage at the inverting input of U1A is equal to  $V_{IN}$ . Because current does not flow into the high-impedance inverting input of U1A, there is no current through R1 or R2 and U1B acts as a buffer. U1A must therefore also act as a buffer and  $V_{OUT}$  is simply equal to  $V_{IN}$ .

Figure 2-16. Simplified Circuit for Positive Input Signals

$V_{OUT} = V_{IN}$

(62)

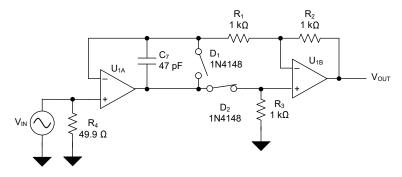

Figure 2-17 and Equation 63 show the circuit and transfer function for negative inputs. Negative input signals forward bias D1 and reverse bias D2. Therefore, U1A drives U1B like a standard inverting amplifier while R3 biases the non-inverting node of U1B to GND. In this configuration, the output is now positive for negative input signals achieving the full-wave rectification.

Figure 2-17. Simplified Circuit for Negative Input Signals

#### 2.2.4.9 MCU Selection

For this design, the MSP430F5131 MCU is chosen for the high clock speed required for timer capture DC fault detection. The timer capture method directly measured duty cycle changes by triggering a timer on each duty cycle edge, so a high clock speed was required. This timer capture method is used in many existing RCD modules. Alternatively, a lower BOM cost is possible by reading DC fault with an ADC instead of using the timer capture method.

The most important specification of MCU selection is the integrated ADC. The ADC must have an effective resolution small enough to consistently differentiate between a fault. This design sees a 200-mV filter output during a 6-mA DC fault, and 600-mV maximum filter output during an 30-mA<sub>RMS</sub> AC fault<sup>1</sup>. This design uses a 10-bit ADC with a full scale range of 1.5 V integrated in the MSP430F5131 MCU.

The ADC needs a sample speed faster than 2000 samples per second. The software stores the low value read by the ADC and uses the low value to determine if an AC or DC fault occurred. The ADC must sample quickly enough to consistently detect a low value during an AC waveform to differentiate AC versus DC fault.

The largest source of noise is the ADC reference voltage error. This design has a total reference voltage error of 1.5%. The fault detection signal needs to be amplified as much as possible to make this error less significant.

<sup>&</sup>lt;sup>1</sup> These fault threshold values can be increased by increasing the gain of the filter stage.

# 2.3 Highlighted Products

# 2.3.1 UCC28742

The UCC28742 is a flyback power-supply controller which provides high-performance voltage regulation using an optically coupled feedback signal from a secondary-side voltage regulator. The device provides accurate constant-current regulation using primary-side feedback. The controller operates in discontinuous-conduction mode (DCM) with valley-switching to minimize switching losses and allow for the use of low cost output rectifiers. The control law scheme combines frequency with primary peak-current amplitude modulation to provide high conversion efficiency across the load range. The control law provides a wide dynamic operating range of output power which allows the power-supply designer to achieve low standby power dissipation. During low-power operating conditions, the power-management features of the controller reduce the device operating current at switching frequencies below 25 kHz. At and above this frequency, the UCC28742 includes features in the modulator to reduce the EMI peak energy of the fundamental switching frequency and harmonics. A complete low-cost and low component-count system is realized using a straight-forward design process.

### 2.3.2 TLV1805

The TLV1805 comparator features rail-to-rail inputs with a push-pull output stage that operates at supply voltages as high as 40 V or  $\pm$ 20 V. The rail-to-rail input stage enables detection of signals close to the supply and ground while the push-pull output stage creates fast transition edges to either supply rail. A low supply current of 135 µA per channel with small, space-saving packages, makes these comparators versatile for use in a wide range of applications, from portable to industrial.

#### 2.3.3 DRV8220

DRV8220 is an integrated H-bridge driver with multiple control interface options: PWM (IN1, IN2) interface (DRL and DSG packages), PH/EN (DSG only), or half-bridge interface (DSG only). To reduce area and external components on a printed circuit board, the device integrates a charge pump regulator and its capacitors. Both DSG and DRL packages support a timed auto-sleep mode which reduces microcontroller GPIO connections by eliminating a disable/sleep pin and automatically putting the device into a low-power sleep mode when the inputs remain inactive for 1-2 ms. When using autosleep for PWM or PH/EN mode, the nSLEEP pin can be tied high. The nSLEEP pin allows the device to be put to sleep in half-bridge mode where autosleep is not available.

#### 2.3.4 ISO1212

The ISO1211 and ISO1212 devices are fully-integrated, isolated digital-input receivers with IEC 61131-2 Type 1, 2, and 3 characteristics. The devices receive 24-V to 60-V digital-input signals and provide isolated digital outputs. No field-side power supply is required. An external resistor, R<sub>SENSE</sub>, on the input-signal path precisely sets the limit for the current drawn from the field input based on an internal feedback loop. The voltage transition thresholds are compliant with Type 1, 2, and 3 and can be increased further using an external resistor, R<sub>THR</sub>.

The ISO121x devices use an ON-OFF keying (OOK) modulation scheme to transmit the digital data across a silicon-dioxide based isolation barrier. The transmitter sends a high frequency carrier across the barrier to represent one digital state and sends no signal to represent the other digital state. The receiver demodulates the signal after advanced signal conditioning and produces the output through a buffer stage.

#### 2.3.5 ADC122S051

The ADC122S051 and ADC122S051Q devices are low-power, two-channel CMOS 12-bit analog-to-digital converters with high-speed serial interface. Unlike the conventional practice of specifying performance at a single sample rate only, the ADC122S051 and ADC122S051Q is fully specified over a sample rate range of 200 ksps to 500 ksps. The converter is based on a successive-approximation register architecture with an internal track-and-hold circuit. It can be configured to accept one or two input at inputs IN1 and IN2.

#### 2.3.6 TPS7A39

The TPS7A39 device is a dual, monolithic, high PSRR, positive and negative low-dropout (LDO) voltage regulator capable of sourcing (and sinking) up to 150 mA of current. The regulated outputs can be independently and externally adjusted to symmetrical or asymmetrical voltages, making this device an ideal dual, bipolar power supply for signal conditioning. Both positive and negative outputs of the TPS7A39 ratiometrically track each other during start-up to mitigate floating conditions and other power-supply sequencing issues common in dual-rail systems. The negative output can regulate up to 0 V, extending the common-mode range for single-supply

amplifiers. The TPS7A39 also features high PSRR to eliminate power-supply noise, such as switching noise, that can compromise signal integrity.

#### 2.3.7 TPS7A20

The TPS7A20 is an ultra-small, low-dropout (LDO) linear regulator that can source 300 mA of output current. The TPS7A20 is designed to provide low noise, high PSRR, and excellent load and line transient performance that can meet the requirements of RF and other sensitive analog circuits. Using remarkable design techniques, the TPS7A20 offers an ultra-low noise performance without the addition of a noise bypass capacitor. The TPS7A20 also provides the advantage of low quiescent current, which can be good for battery-powered applications. With an input voltage range of 1.6 V to 6.0 V and an output range of 0.8 V to 5.5 V, the TPS7A20 can be used for a wide variety of applications. The device uses a precision reference circuit to provide a maximum accuracy of 1.5% over load, line, and temperature variations.

### 2.3.8 ATL431

The ATL431 and ATL432 are three-terminal adjustable shunt regulators, with specified thermal stability over applicable automotive, commercial, and industrial temperature ranges. The output voltage can be set to any value between Vref (approximately 2.5 V) and 36 V, with two external resistors. These devices have a typical output impedance of 0.05  $\Omega$ . Active output circuitry provides a very sharp turn-on characteristic, making these devices excellent replacements for Zener diodes in many applications, such as onboard regulation, adjustable power supplies, and switching power supplies.

#### 2.3.9 TL431

The TL431 and TL432 devices are three-terminal adjustable shunt regulators, with specified thermal stability over applicable automotive, commercial, and military temperature ranges. The output voltage can be set to any value between Vref (approximately 2.5 V) and 36 V, with two external resistors. These devices have a typical output impedance of 0.2  $\Omega$ . Active output circuitry provides a very sharp turn-on characteristic, making these devices excellent replacements for Zener diodes in many applications, such as onboard regulation, adjustable power supplies, and switching power supplies. The TL432 device has exactly the same functionality and electrical specifications as the TL431 device, but has different pinouts for the DBV, DBZ, and PK packages.

#### 2.3.10 TPS563210A

The TPS562210A and TPS563210A are simple, easy-to-use, 2-A, 3-A synchronous step-down converters in 8 pin SOT-23 package. The devices are optimized to operate with minimum external component counts and optimized to achieve low standby current. These switch mode power supply (SMPS) devices employ D-CAP2<sup>™</sup> control mode providing a fast transient response and supporting both low equivalent series resistance (ESR) output capacitors such as specialty polymer and ultra-low ESR ceramic capacitors with no external compensation components.

#### 2.3.11 TPS55330