## Application Brief Space-Grade, 30-krad, High-Side Current Sensing Comparator Circuit

# TEXAS INSTRUMENTS

#### **Design Goals**

| Load Current (IL)                  |                                        | System Supply | Comparator Output Status |                                           | Radiation                    |                     |

|------------------------------------|----------------------------------------|---------------|--------------------------|-------------------------------------------|------------------------------|---------------------|

| Over Current<br>(I <sub>OC</sub> ) | Recovery Current<br>(I <sub>RC</sub> ) | Typical       | Over Current             | Normal Operation                          | Total Ionizing<br>Dose (TID) | SEL Immunity to LET |

| 1 A                                | 0.5 A                                  | 10 V          | V <sub>OL</sub> < 0.4 V  | V <sub>OH</sub> = V <sub>PU</sub> = 3.3 V | 30 krad(Si)                  | 43 MeV·cm²/mg       |

## **Design Description**

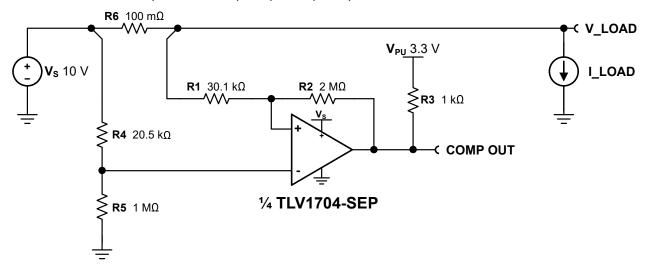

This application brief shows how to implement a simple rad-tolerant circuit that detects an over-current event caused by a single-event latch-up (SEL), in systems where not all other components SEL immune up to the target LET. This solution uses one comparator with a rail-to-rail input common mode range to create an over-current alert (OC-Alert) signal at the comparator output (COMP OUT) if the load current rises above 1A. The OC-Alert signal in this implementation is active low. So when the 1A threshold is exceeded, the comparator output goes low. Hysteresis is implemented such that OC-Alert will return to a logic high state when the load current reduces to 0.5A (a 50% reduction). This circuit uses an open-collector output comparator in order to level shift the output high logic level for controlling a digital logic input pin. For applications needing to drive the gate of a MOSFET switch, a comparator with a push-pull output is preferred.

1

#### **Design Notes**

- 1. Select a comparator with rail-to-rail input common mode range to enable high-side current sensing.

- 2. Select a comparator with an open-collector output stage for level-shifting.

- 3. Select a comparator with low input offset voltage to optimize accuracy.

- 4. Calculate the value for the shunt resistor (R<sub>6</sub>) so the shunt voltage (V<sub>SHUNT</sub>) is at least ten times larger than the comparator offset voltage (V<sub>IO</sub>).

### **Design Steps**

Select value of R<sub>6</sub> so V<sub>SHUNT</sub> is at least 10x greater than the comparator input offset voltage (V<sub>IO</sub>). Note that making R<sub>6</sub> very large will improve OC detection accuracy but will reduce supply headroom.

$V_{SHUNT}$  = (  $I_{OC} R_6$  ) ≥ 10  $V_{IO}$  = 55 mV

set  $R_6$  = 100 m $\Omega$  for  $I_{OC}$  = 1 A &  $V_{IO}$  = 5.5 mV

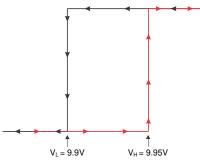

2. Determine the desired switching thresholds for when the comparator output will transition from high-to-low  $(V_L)$  and low-to-high  $(V_H)$ .  $V_L$  represents the threshold when the load current crosses the OC level, while  $V_H$  represents the threshold when the load current recovers to a normal operating level.

$V_{H} = V_{S} - (I_{RC} R_{6}) = 10 - (0.5 \times 0.1) = 9.95 V$

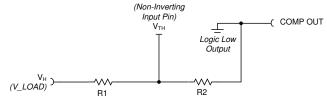

3. With the non-inverting input pin of the comparator labeled as V<sub>TH</sub> and the comparator output in a logic low state (ground), derive an equation for V<sub>TH</sub> where V<sub>H</sub> represents the load voltage (V<sub>LOAD</sub>) when the comparator output transitions from low to high. Note that the simplified diagram for deriving the equation shows the comparator output as ground (logic low).

$$V_{TH} = V_H \left(\frac{R_2}{R_1 + R_2}\right)$$

2

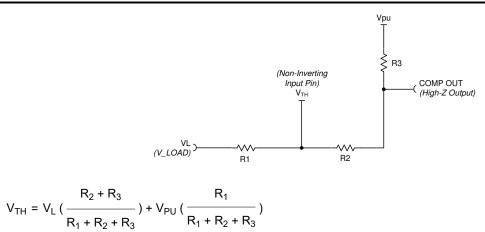

4. With the non-inverting input pin of the comparator labeled as V<sub>TH</sub> and the comparator output in a high-impedance state, derive an equation for V<sub>TH</sub> where V<sub>L</sub> represents the load voltage (V<sub>LOAD</sub>) when the comparator output transitions from high to low. Applying "superposition" theory to solve for V<sub>TH</sub> is recommended.

$R_1 + R_2 + R_3$   $R_1 + R_2 + R_3$ 5. Eliminate variable V<sub>TH</sub> by setting the two equations equal to each other and

Eliminate variable V<sub>TH</sub> by setting the two equations equal to each other and solve for R<sub>1</sub>. The result is the following quadratic equation. Solving for R<sub>2</sub> is less desirable since there are more standard values for small resistor values than the larger ones.

$$0 = V_{PU} R_1^2 + [V_{PU} R_2 + V_L (R_3 + R_2) - V_H R_2] R_1 + (V_L - V_H) [R_2^2 + (R_2 R_3)]$$

6. Select values for R3 and R2. Please note that  $R_3$  is significantly smaller than  $R_2$  ( $R_3 << R_2$ ). Increasing  $R_3$  will cause the comparator logic high output level to increase beyond  $V_{PU}$  and should be avoided. For example, increasing  $R_3$  to a value of 100k can cause the logic high output to be 3.6 V. In this case, we can select  $R_2 = 2M$  and  $R_3 = 1k$ .

$R_2 = 2 M\Omega$

$R_3 = 1 k\Omega$

7. Calculate R<sub>1</sub> after substituting in numeric values for V<sub>PU</sub>, R<sub>2</sub>, V<sub>L</sub>, V<sub>H</sub>, and R<sub>3</sub>. For this design, set V<sub>PU</sub> = 3.3, R<sub>2</sub> = 2M, V<sub>L</sub> = 9.9, V<sub>H</sub> = 9.95, and R<sub>3</sub> = 1k.

$0 = 3.3 R_1^2 + (6.591 M) R_1 - (200.1 G)$

the positive root for  $R_1 = 29.9 \text{ k}\Omega$

using standard 1 % resistor values ,  $R_1 = 30.1 \text{ k}\Omega$

8. Calculate V<sub>TH</sub> using the equation derived in Design Step 3; use the calculated value for R<sub>1</sub>. Note that V<sub>TH</sub> is less than V<sub>L</sub> since V<sub>PU</sub> is less that V<sub>L</sub>.

$$V_{TH} = V_{H} \left( \frac{R_{2}}{R_{1} + R_{2}} \right) = 9.802 V$$

9. With the inverting terminal labeled as  $V_{TH}$ , derive an equation for  $V_{TH}$  in terms of  $R_4$ ,  $R_5$ , and  $V_S$ .

$$V_{TH} = V_{S} \left( \frac{R_{5}}{R_{4} + R_{5}} \right)$$

10. Calculate R<sub>4</sub> after substituting in numeric values R<sub>5</sub>=1M, V<sub>S</sub>=10, and the calculated value for V<sub>TH</sub>.

$$R_4$$

= (  $\frac{R_5 (V_S - V_{TH})}{V_{TH}}$  ) = 20 . 15 kΩ

using standard 1 % resistor values ,  $R_4$  = 20 . 5  $k\Omega$

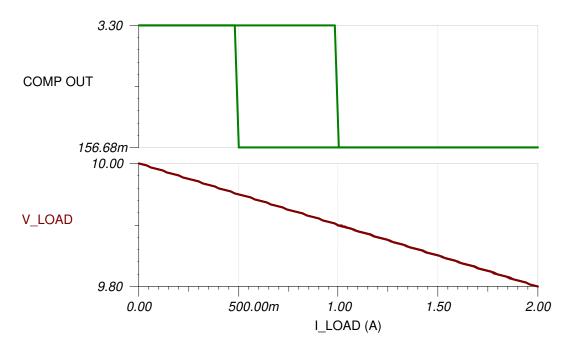

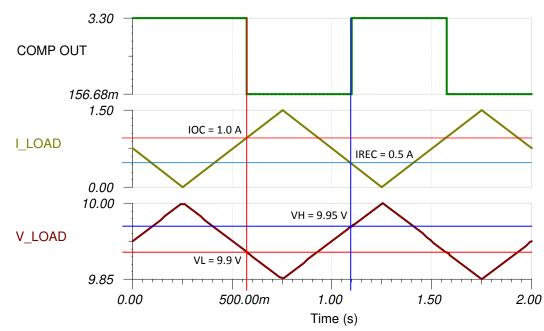

#### **Design Simulations**

#### **Transient Simulation Results**

#### **Design References**

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See Circuit SPICE Simulation File SBOMBL5, http://www.ti.com/lit/zip/sbombl5.

#### **Design Featured Comparator**

| TLV1704-SEP                                    |                              |  |  |  |

|------------------------------------------------|------------------------------|--|--|--|

| Vs                                             | 2.2 V to 36 V                |  |  |  |

| V <sub>inCM</sub>                              | Rail-to-rail                 |  |  |  |

| V <sub>OUT</sub>                               | Open-Collector, Rail-to-rail |  |  |  |

| V <sub>os</sub>                                | 500 µV                       |  |  |  |

| Ι <sub>Q</sub>                                 | 55 μA/channel                |  |  |  |

| t <sub>PD(HL)</sub>                            | 460 ns                       |  |  |  |

| #Channels                                      | 4                            |  |  |  |

| TID Characterization (ELDRS-Free)              | 30 krad(Si)                  |  |  |  |

| TID Radiation Lot Acceptance Test (RLAT) / RHA | 20 krad(Si)                  |  |  |  |

| SEL Immune to LET                              | 43 MeV⋅cm²/mg                |  |  |  |

| https://www.ti.com/product/TLV1704-SEP         |                              |  |  |  |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated