## TI TECH DAYS

# How to trouble shoot Op Amp PCB layout issues with real world examples

**Tim Claycomb**

**General Purpose Amplifiers**

## **Summary**

- 1) General op amp PCB layout recommendations

- 2) What to look for during PCB layout with examples

- 3) Conclusion

## **General PCB Layout Recommendations**

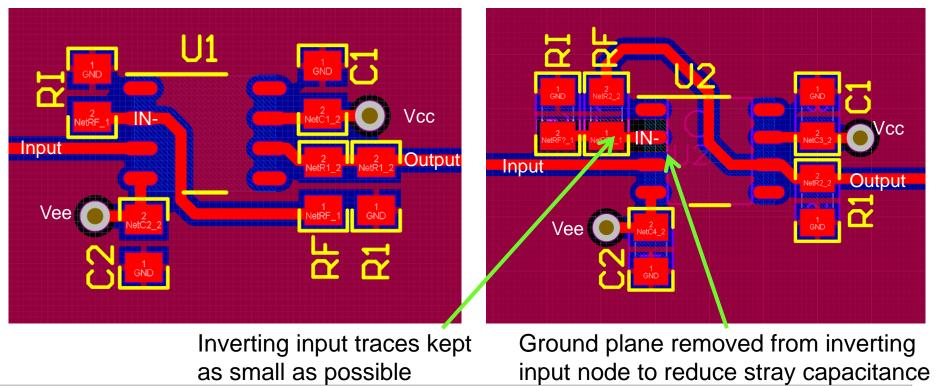

- 1) Minimize trace length on the inverting input pin

- 2) Place decoupling capacitors as close to the supply pin as possible

- 3) Do not place vias between decoupling capacitor and supply pin

- 4) Pour at least one solid ground plane

- 5) Make traces as wide as possible

- 6) Consider using a current limiting series resistor between inputs and low impedance connection (GND)

- 7) Place GND vias next to GND connections of components

## What to look for during PCB layout

4

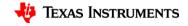

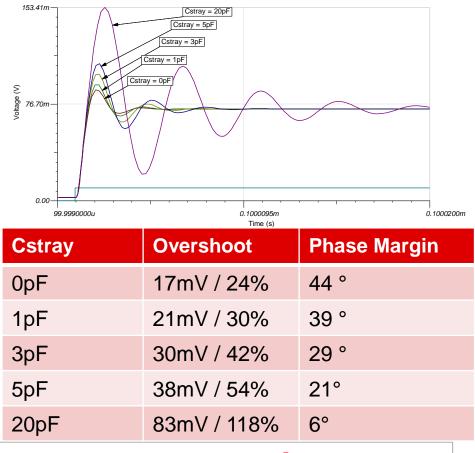

Description of Issue: Excessive overshoot and ringing on output of amplifier

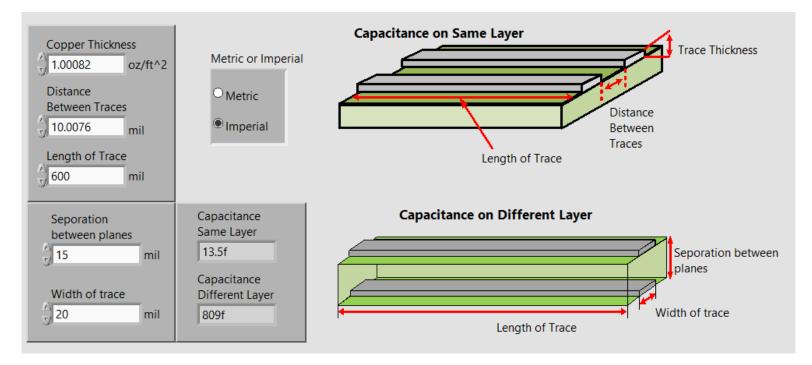

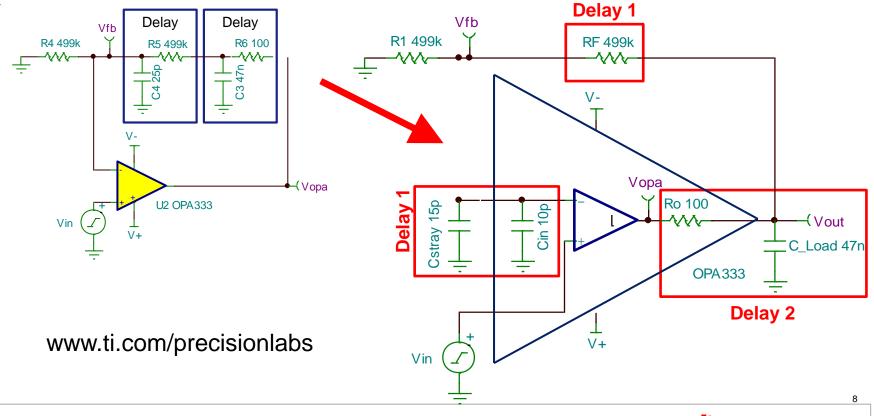

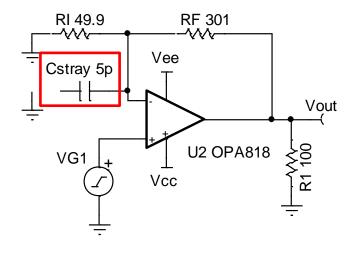

**Possible layout issue**: Capacitance on inverting input pin of amplifier in high speed circuits and high value feedback resistors.

~50% Overshoot = 25 degrees of Phase Margin

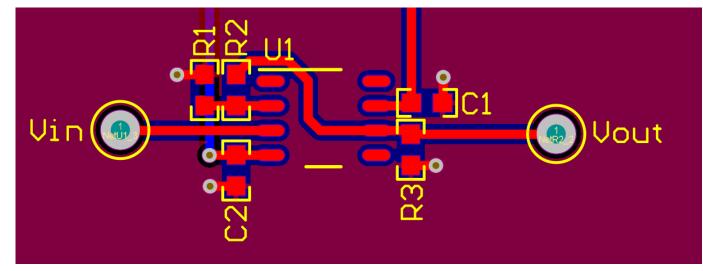

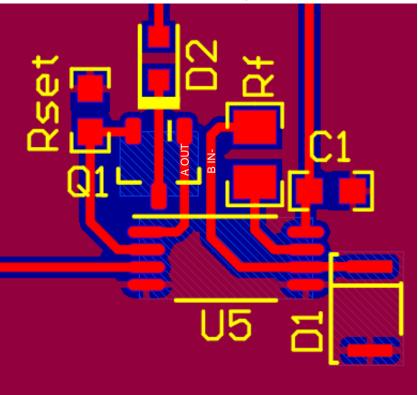

**Current Layout**

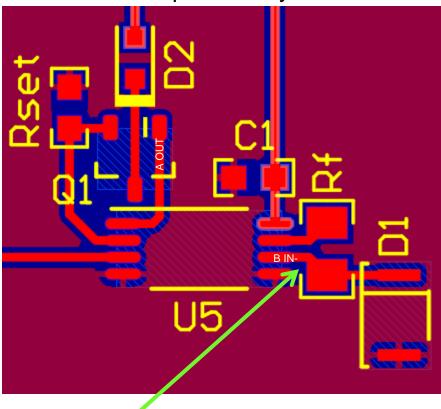

#### Improved Layout

Capacitor is two parallel plates

#### http://www.ti.com/tool/ANALOG-ENGINEER-CALC

~1pF from trace

Stability Issues occur because of too much delay in the feedback

Large overshoot? Think Stability

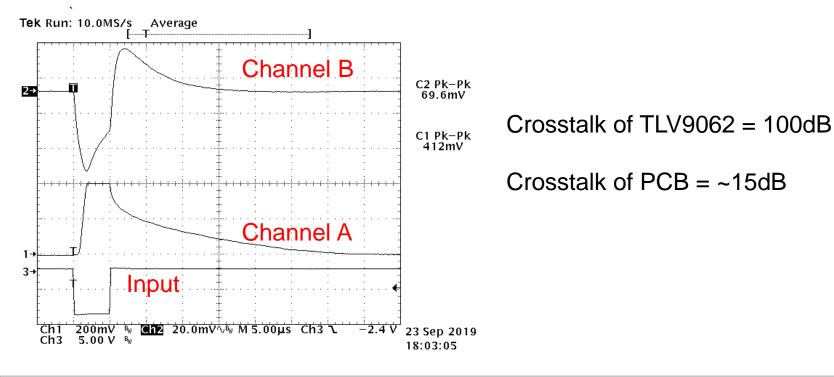

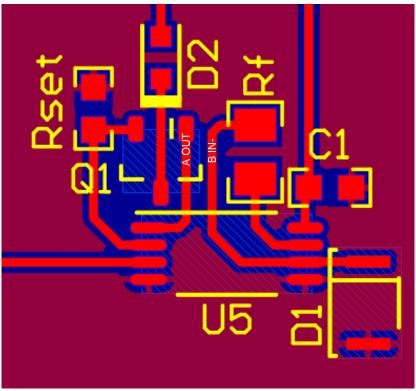

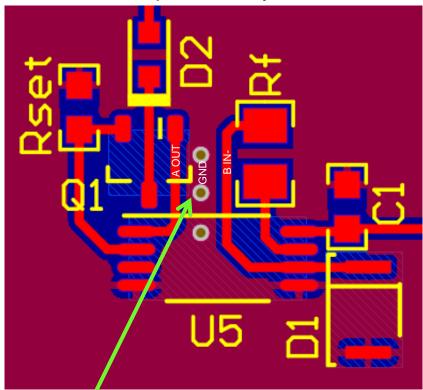

**Description of Issue**: Channel A (high output current) output is influencing CH B (TIA) – crosstalk? **Possible layout issue**: Coupling due to PCB traces routed parallel and close together

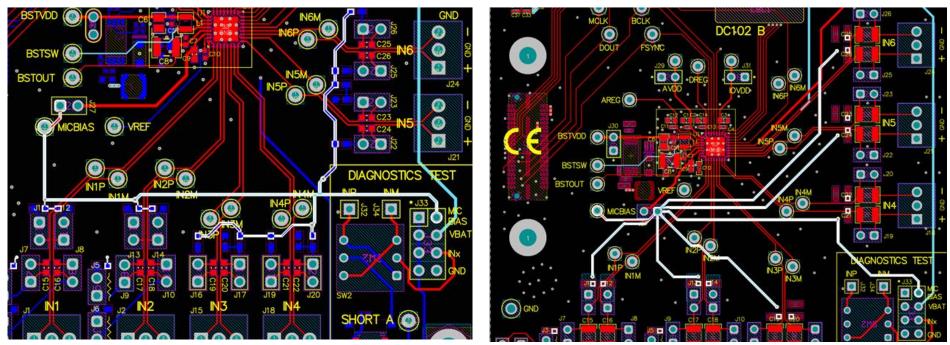

#### Current Layout

Improved Layout

Move Rf away from CH A Output

#### Current Layout

#### Improved Layout

Add GND pour with vias between CH A Output and CH B IN-

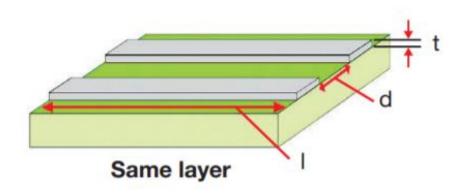

• The closer two traces are to each other the more capacitance there is between them.

$$C = \frac{k \times t \times l}{d}$$

#### Analog Engineer's Pocket Reference http://www.ti.com/lit/slyw038

C decreases as distance increases

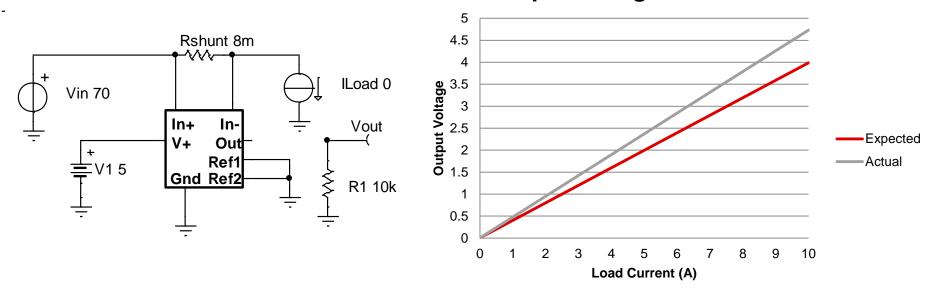

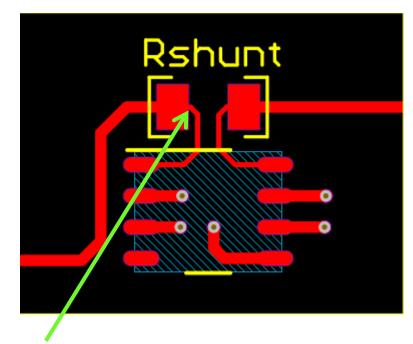

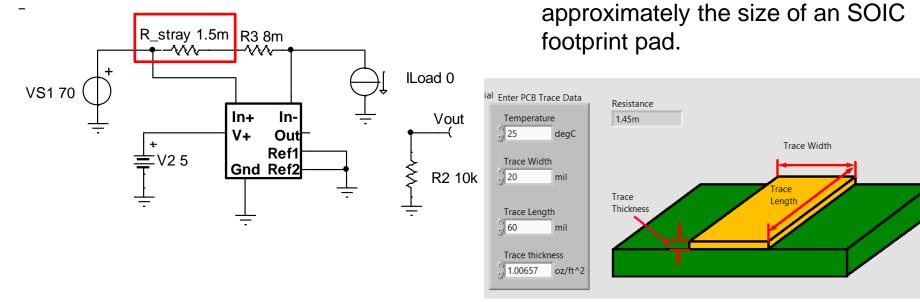

## **Look for Kelvin Connection on Rshunt**

**Description of Issue**: Seeing high gain error in current sensing application **Possible layout issue**: Not using a Kelvin connection

#### **Output Voltage vs. Load Current**

## **Look for Kelvin Connection on Rshunt**

# Rshunt 11111

Current Layout

Improved Layout

Kelvin connection to Rshunt

#### $8m\Omega$ shunt

## **Look for Kelvin Connection on Rshunt**

A 20mil wide 60mil long trace is

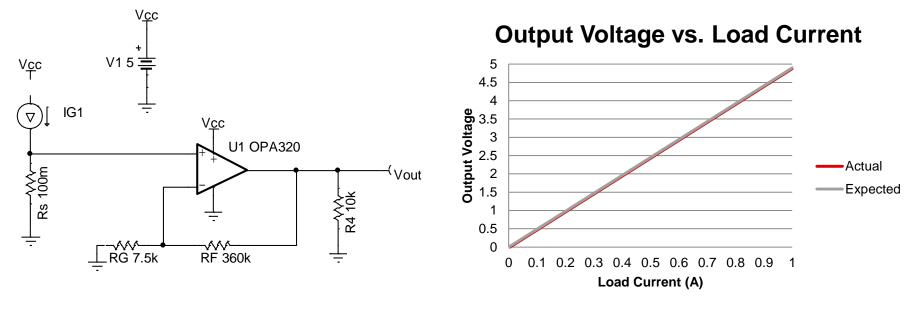

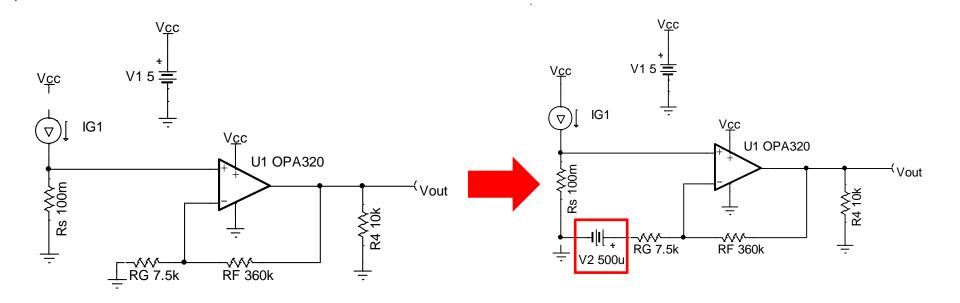

## **Look for RG Placement**

**Description of Issue**: Seeing high offset error in low-side current sensing application **Possible layout issue**: Gain setting resistor not placed close to shunt

~25mV of offset on output

Vos Max =  $150\mu$ V

17

## **Look for RG Placement**

### **Look for RG Placement**

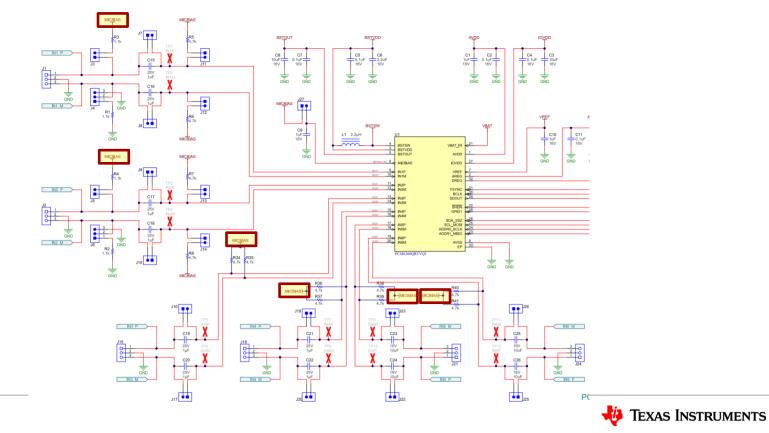

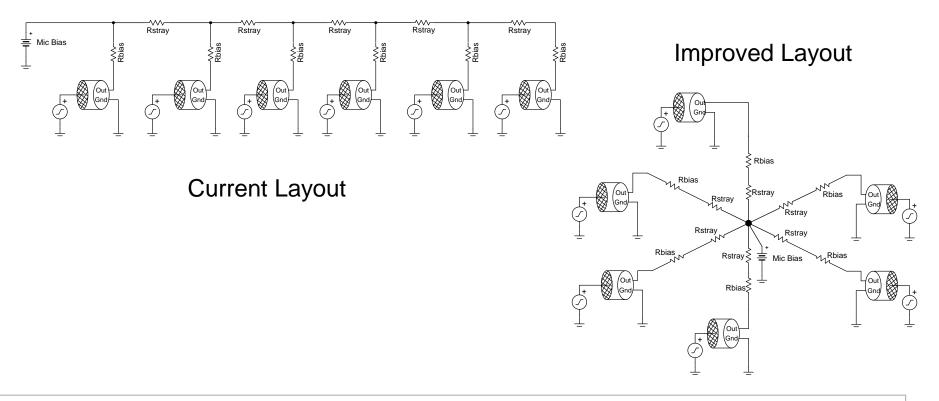

## **Look for Star Connection**

<u>Description of Issue</u>: Crosstalk in multi-channel microphone circuit <u>Possible layout issue</u>: Microphone bias voltage is not star connected

## **Look for Star Connection**

#### **Current Layout**

Improved Layout

## **Look for Star Connection**

#### ©2020 Texas Instruments Incorporated. All rights reserved.

The material is provided strictly "as-is" for informational purposes only and without any warranty. Use of this material is subject to TI's **Terms of Use**, viewable at TI.com

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated