The ADS58J64EVM device is an evaluation board used to evaluate the ADS58J64 Integrated Receiver from TI. This User's Guide is intended to guide users through setting up and evaluating the ADC for the best performance.

|       |        | Contents                                        |    |

|-------|--------|-------------------------------------------------|----|

| 1     | Overv  | iew                                             | 3  |

|       | 1.1    | Required Hardware                               | 3  |

|       | 1.2    | Required Software                               | 3  |

|       | 1.3    | Evaluation Board Feature Identification Summary | 4  |

|       | 1.4    | References                                      | 4  |

| 2     | Quick  | Start Guide                                     | 4  |

|       | 2.1    | Software Installation                           | 4  |

|       | 2.2    | Hardware Setup Procedure                        |    |

|       | 2.3    | Software Setup Procedure                        | 6  |

|       | 2.4    | Quick Start Troubleshooting                     |    |

| 3     | Optim  | izing Evaluation Results                        | 10 |

|       | 3.1    | ADS58J64 Operating Mode                         | 10 |

|       | 3.2    | LMK04828 Clocking Configuration                 | 11 |

|       | 3.3    | Using an External Clock                         | 11 |

|       | 3.4    | Using a Coherent Input Source Frequency         | 12 |

|       | 3.5    | HSDC Pro Settings.                              | 12 |

| 4     | Softw  | are Description                                 |    |

|       | 4.1    | ADS58J64 GUI                                    | 13 |

|       | 4.2    | Low Level View                                  | 14 |

| 5     | EVM    | Hardware Modifications from Default             | 15 |

| Apper | ndix A |                                                 | 16 |

### List of Figures

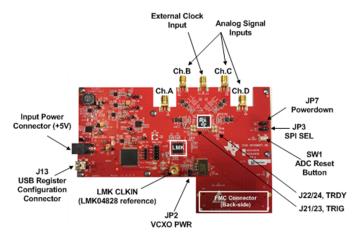

| 1 | EVM Feature Locations                                   | 4  |

|---|---------------------------------------------------------|----|

| 2 | Quick Start Test Setup                                  | 5  |

| 3 | HSDC Pro GUI Main Panel                                 | 7  |

| 4 | HSDC Pro Sampling Rate and Additional Device Parameters | 7  |

| 5 | Data Capture Results from Quick Start Procedure         | 8  |

| 6 | Test Setup Using an External Device Clock Source        | 12 |

| 7 | ADS58J64 GUI                                            | 13 |

| 8 | Low Level View Tab                                      | 14 |

### List of Tables

| 1 | Quick Start Performance Measurements               | 8  |

|---|----------------------------------------------------|----|

| 2 | Troubleshooting Tips                               | 9  |

| 3 | HSDC Pro ADC Output Data Rate                      | 10 |

| 4 | LK04828 Macro States Provided in Configuration GUI | 11 |

| 5 | HSDC Pro Options for Optimal Analysis Results      | 12 |

| 6 | ADS58J64 GUI Tab Descriptions                      | 13 |

|   |                                                    |    |

| 7  | Low Level View Controls                             | 14 |

|----|-----------------------------------------------------|----|

|    | Jumper and Button Descriptions and Default Settings |    |

|    | Connector Descriptions                              |    |

| 10 | LED Descriptions                                    | 18 |

### 1 Overview

This evaluation board includes the following important features:

- Transformer-coupled signal input network, allows a single-ended signal source to the EVM.

- LMK04828, a system clock generator, generates the FPGA reference clock for the high-speed serial interface.

- Default transformer-coupled clock input network, tests the receiver performance with a very low-noise clock.

- High-speed serial data output over a standard FMC connector.

- Device registers programming through a USB connector and FTDI USB-to-SPI bus translator.

The ADS58J64EVM device is designed to work seamlessly with the TSW14J56EVM device, the JESD204B data-capture card from TI, and the High-Speed Data Converter Pro (HSDCPro) software tool. The ADS58J64EVM device is also compatible with many of the development kits from leading FPGA vendors that contain an FMC connector.

## 1.1 Required Hardware

The EVM evaluation kit includes the following equipment:

- ADS58J64EVM Evaluation Board (EVM)

- Mini-USB cable

The EVM evaluation kit *does not* include the following list of equipment, but these items are required for evaluation of this product, to achieve the best performance.

- 5-V DC power supply

- TSW14J56EVM data capture board, 5-V power supply, and Mini-USB cable

- Computer running Windows® 8, Windows 7, or Windows XP operating system

- Two low-noise signal generators

- Recommendations: RF generator, > 17 dBm, < -40 dBc harmonics, < 500 fs jitter 20 k 20 MHz, and 10 MHz to 2 GHz frequency range

- Examples: TSW2170EVM, HP® HP8644B, and Rohde & Schwarz® SMA100A

- Bandpass filter for analog input (between 50 MHz to 500 MHz).

- Recommendations: bandpass filter, ≥ 60 dB harmonic attenuation, ≤ 5% bandwidth, > 18 dBm power, and < 5 dB insertion loss</li>

- Examples: Trilithic 5VH-series Tunable BPF, K&L BT-series Tunable BPF, TTE KC6, or KC7-series Fixed BPF

- Bandpass filter for clock input (various frequencies)

- Recommendations: bandpass filter, ≥ 60 dB harmonic attenuation, ≤ 5% bandwidth, > 18 dBm power, <5 dB insertion loss</li>

- Examples: Trilithic 5VH-series Tunable BPF, K&L BT-series Tunable BPF, TTE KC6 or KC7-series Fixed BPF

- Signal path cables, SMA or BNC with BNC-to-SMA adapters

- 6 dB 50-Ω attenuator

## 1.2 Required Software

The following software is required and available online.

- To operate the ADS58J64EVM device: ADS58J64EVM\_GUI\_Installer.zip

- To operate the TSW14J56EVM device: High Speed Data Converter Pro software See Section 1.4 for the software links.

HP is a registered trademark of Hewlett Packard. Windows is a registered trademark of Microsoft. Rohde & Schwarz is a registered trademark of Rohde & Schwarz. Overview

# 1.3 Evaluation Board Feature Identification Summary

Figure 1. EVM Feature Locations

## 1.4 References

- ADS58J64EVM GUI software, schematics, layout, BOM

- ADS58J64 Data Sheet

- LMK04828 Data Sheet

- TSW14J56EVM User's Guide

- High-Speed Data Converter Pro User's Guide

## 2 Quick Start Guide

This section guides users through the EVM test procedure for obtaining a valid data capture from the ADS58J64EVM device, using the TSW14J56EVM capture card. This step is the starting point for all evaluations.

## 2.1 Software Installation

The proper software must be installed before beginning the evaluation. See Section 1.2 for a list of the required software. Section 1.4 of this document contains links to the required software on the TI website.

**NOTE:** The software must be installed before connecting the ADS58J64EVM and TSW14J56EVM devices to the computer for the first time.

### 2.1.1 ADS58J64 GUI Installation

The ADS58J64 GUI is used to control the ADS58J64EVM device. The GUI must be used to properly configure the devices on the EVM.

1. Download the GUI from ti.com.

**NOTE:** For pre-released EVMs, obtain the GUI from the local Field Applications contact.

- 2. Extract the files from the zip file.

- 3. Run setup.exe and follow the installation prompts.

## 2.1.2 High-Speed Data Converter Pro GUI Installation

High-Speed Data Converter Pro (HSDC Pro) is used to control the TSW14J56EVM and analyze the captured data. Please see the HSDC Pro user's guide for more information.

- 1. Download HSDC Pro from the TI website. Section 1.2 contains the link to find the software on the TI website.

- 2. Extract the files from the zip file.

- 3. Run setup.exe and follow the installation prompts.

# 2.2 Hardware Setup Procedure

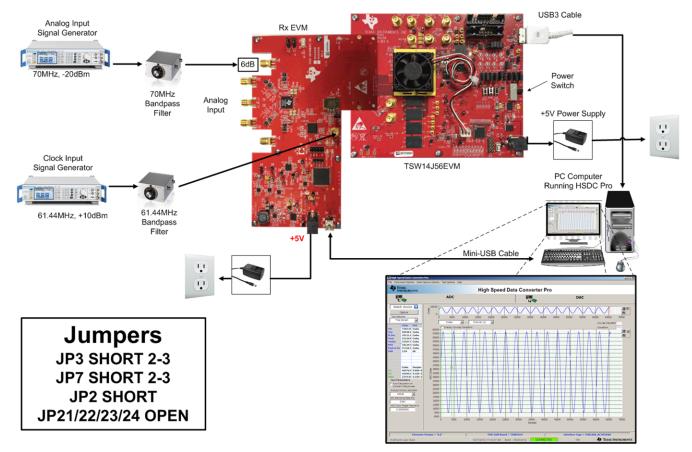

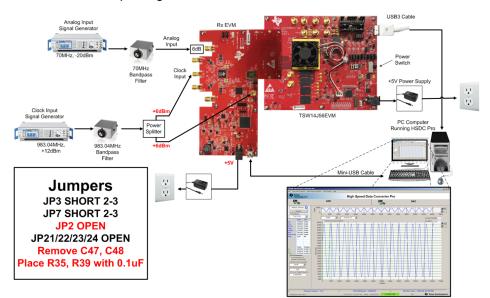

Figure 2 shows a typical test setup using the ADS58J64EVM and TSW14J56EVM REV D devices. This test setup is used for the quick start procedure. The rest of this section describes the hardware setup steps.

Figure 2. Quick Start Test Setup

## 2.2.1 TSW14J56EVM Setup

Set up the TSW14J56EVM device by following these instructions.

- 1. Connect the ADS58J64EVM device to the TSW14J56EVM device using the FMC connectors.

- 2. Connect the included 5-V power supply to connector J11 (5-V IN) of the TSW14J56EVM device.

- 3. Connect the included mini-USB cable to the USB connector (J9) of the TSW14J56EVM device.

- 4. Move the power switch (SW6) of the TSW14J56EVM device to the *on* position.

TEXAS INSTRUMENTS

www.ti.com

Quick Start Guide

### 2.2.2 ADS58J64EVM Setup

Set up the ADS58J64EVM device by following these instructions.

- 1. Connect the included 5-V power supply to the PWR IN (J14) connector.

- 2. Verify that JP7 and JP3 and are shorted at positions 2 3.

- 3. Verify that JP2 is shorted.

- 4. Connect the included mini-USB cable to the USB connector (J13).

- 5. Set the clock input signal generator for 61.44 MHz and 10 dBm.

- 6. Connect the Clock Signal generator to the LMK\_CLK\_IN (J12) connector.

- 7. Place the bandpass filter between the signal generator and the connector, to remove noise from the signal.

- 8. Set the analog input signal generator for 70 MHz and –20 dBm.

- 9. Connect the 6 dB attenuator to the DIN (J5) input.

- 10. Connect the Analog Input Signal generator to the 6 dB attenuator.

- 11. Place the bandpass filter between the analog signal generator and the attenuator input, to remove noise and harmonics from the signal generator.

- 12. Turn on all signal generators.

# 2.3 Software Setup Procedure

The software can be opened and configured once the hardware is properly set up.

# 2.3.1 ADS58J64 GUI Configuration

Set up the ADS58J64EVM GUI by following these instructions.

- 1. Open the ADS58J64EVM GUI from the Start Menu  $\rightarrow$  All Programs  $\rightarrow$  Texas Instruments  $\rightarrow$  ADS58J64 EVM

- 2. After the GUI starts, verify that the green USB Status indicator in the top right corner of the GUI is lit.

- 3. From the INTRO tab, press the Configure LMK04828 button that corresponds to the desired sampling rate. To quickly evaluate device performance and check EVM functionality, the ADS58J64 EVM GUI has two sampling rate options to choose from, 983.04 MHz and 737.28 MHz.

- 4. Press the ADC\_RESET (SW1) button on the ADS58J64EVM device.

- 5. Press the Configure ADS58J64 button that corresponds to the sampling rate selected in step .

- 6. Press the Disable LMK04828 SYSREF to ADC button.

### 2.3.2 HSDC Pro GUI Configuration

Set up the HSDC Pro GUI by following these instructions.

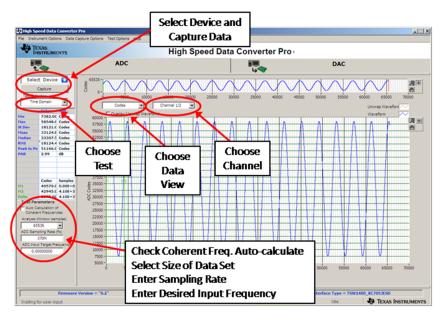

1. Open High Speed Data Converter Pro from the Start Menu → All Programs → Texas Instruments → High Speed Data Converter Pro. Figure 3 shows the GUI main page.

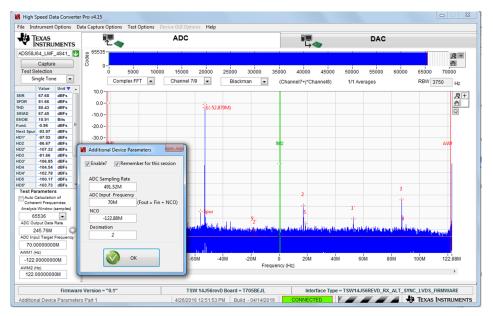

Figure 3. HSDC Pro GUI Main Panel

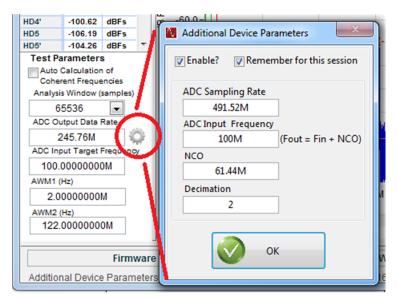

## Figure 4. HSDC Pro Sampling Rate and Additional Device Parameters

- 2. When prompted to select the capture board, select the TSW14J56, whose serial number corresponds to the serial number on the TSW14J56EVM, and click OK.

- 3. Select the ADC tab at the top of the GUI.

- 4. Use the Select ADC drop-down menu in the top-left corner to select ADS58J64\_LMF\_4841\_mode01.

- 5. When prompted to update the firmware for the ADC, click the Yes button, and wait for the firmware to download to the TSW14J56.

Quick Start Guide

www.ti.com

- 6. Press the Additional Device Parameters symbol next to the ADC Output Data Rate (see Figure 4), and enter the following values, then press OK:

- Check the Enable box.

- ADC Sampling Rate = 491.52M

- ADC Input Frequency = 70M

- NCO = -122.88M

- Decimation = 2

- 7. Press the CPU\_RESET button on the TSW14J56EVM device.

- 8. Click the Instrument Options menu at the top of HSDC Pro, and select Reset Board.

- 9. Click Capture in HSDC Pro to capture data from the ADC.

- 10. In HSDCPRO, change the Test Selection to Single Tone.

- 11. Also in HSDCPRO, change the spectrum analysis from Real FFT to Complex FFT.

- 12. From the Test Options file menu, enable the Analysis Window Markers.

- 13. Set the of value of the Analysis Window markers in the lower left corner of the HSDC Pro window:

- AWM1 = -120M

- AWM2 = 120M

- 14. The results from the captured data of Channel 1 should resemble Figure 5, and the performance should be similar to Table 1. If this result was not achieved, then see Section 2.4 of this document.

Figure 5. Data Capture Results from Quick Start Procedure

| Result | Measured Value | Units |

|--------|----------------|-------|

| SNR    | > 67           | dBFS  |

| SFDR   | > 80           | dBFS  |

# 2.4 Quick Start Troubleshooting

Table 2 lists tips which can be used to assist with problems that may have occurred during the quick start procedure.

| Issue                                                             | Troubleshooting Tips                                                                                                                                             |  |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                   | Verify the test setup shown in Figure 2, and repeat the setup procedure as described in this document.                                                           |  |  |

|                                                                   | Check power supplies to the EVM and TSW14J56EVM. Verify that the power switches are in the ON position.                                                          |  |  |

| General problems                                                  | Check signal and clock connections to the EVM.                                                                                                                   |  |  |

|                                                                   | Check that all boards are properly connected together.                                                                                                           |  |  |

|                                                                   | Try pressing the CPU_RESET button on the TSW14J56EVM.                                                                                                            |  |  |

|                                                                   | Try power-cycling the external power supply to the EVM and reprogram the LMK and ADC devices.                                                                    |  |  |

|                                                                   | Verify the settings of the configuration switches on the TSW14J56EVM.                                                                                            |  |  |

| TSW14J56 LEDs are incorrect:<br>D1, D5 – N/A<br>D2, D4 – Flashing | Verify that the EVM configuration GUI is communicating with the USB, and that the configuration procedure was followed.                                          |  |  |

| D3, D6, D7 – OFF                                                  | LEDs not flashing – reprogram the LMK device.                                                                                                                    |  |  |

| D8, D28 – ON                                                      | Try pressing the CPU_RESET button on the TSW14J56EVM.                                                                                                            |  |  |

|                                                                   | Try capturing data in HSDC Pro to force an LED status update.                                                                                                    |  |  |

|                                                                   | Verify that the USB cable is plugged into the EVM and the PC.                                                                                                    |  |  |

|                                                                   | Check the Device Manager of the computer, and verify that a USB Serial Device is recognized when the EVM is connected to the PC.                                 |  |  |

| Device GUI is not working properly.                               | Verify that the green <i>USB Status</i> LED light in the top-right corner of the GUI is lit. If the LED is not lit, press the Reconnect FTDI button.             |  |  |

|                                                                   | Try restarting the configuration GUI.                                                                                                                            |  |  |

|                                                                   | Check default jumper connections as shown in Appendix A.                                                                                                         |  |  |

| HSDC Pro Software is not capturing good data or analysis          | Verify that the TSW14J56EVM is properly connected to the PC with a mini-USB cable, and that the board serial number is properly identified by the HSDP software. |  |  |

| results are incorrect.                                            | Check that the proper ADC device is selected. In default conditions, <i>ADS58J64_LMF_4841_mode01</i> must be selected.                                           |  |  |

|                                                                   | Check that the analysis parameters are properly configured.                                                                                                      |  |  |

|                                                                   | Try to reprogram the LMK device and reset the JESD204 Link.                                                                                                      |  |  |

| HSDP Software gives a time-out error when capturing data.         | Verify that the ADC sampling rate is correct in the HSDC Pro software.                                                                                           |  |  |

|                                                                   | Try pressing the Calibrate ADC button on the INTRO tab, to repeat the configuration GUI procedure for programming the EVM                                        |  |  |

| Sub-optimal measured performance                                  | Check that the spectral analysis parameters are properly configured.                                                                                             |  |  |

|                                                                   | Verify that bandpass filters are used in the clock and input signal paths, and that low-noise signal sources are used.                                           |  |  |

## Table 2. Troubleshooting Tips

# **3 Optimizing Evaluation Results**

This section is meant to assist users in optimizing performance during evaluation of the product.

# 3.1 ADS58J64 Operating Mode

The ADS58J64 device may operate in eight different modes: Mode 0 through Mode 8 (excluding Mode 5). Each mode may require a different device selection in HSDC Pro, device configuration script in the ADS58J64 EVM GUI, and different sampling rate setup in HSDC Pro to operate correctly.

Table 3 shows the HSDC Pro sampling rate setup. The desired mode is selected from the ADS58J64EVM GUI  $\rightarrow$  Mode tab in the configuration GUI.

| ADS58J64 Operating<br>Mode | ADS58J64 Device<br>Clock Frequency | HSDC Pro ADC<br>Sampling Rate | Decimation | NCO                               |  |

|----------------------------|------------------------------------|-------------------------------|------------|-----------------------------------|--|

| Mode 0                     | 983.04 MHz                         | 491.52M                       | 2          | -122.88M                          |  |

|                            | 737.28 MHz                         | 368.64M                       | 2          | -92.16M                           |  |

| Mode 1                     | 983.04 MHz                         | 491.52M                       | 2          | Depends on<br>programmed NCO word |  |

|                            | 737.28 MHz                         | 368.64M                       | 2          | Depends on<br>programmed NCO word |  |

| Mode 2                     | 983.04 MHz                         | 491.52M                       | 2          | 0                                 |  |

|                            | 737.28 MHz                         | 368.64M                       | 2          | 0                                 |  |

| Mode 3                     | 983.04 MHz                         | 491.52M                       | 1          | Depends on<br>programmed NCO word |  |

| Node 5                     | 737.28 MHz                         | 368.64M                       | 1          | Depends on<br>programmed NCO word |  |

| Mode 4                     | 983.04 MHz                         | 491.52M                       | 2          | Depends on<br>programmed NCO word |  |

| Node 4                     | 737.28 MHz                         | 368.64M                       | 2          | Depends on<br>programmed NCO word |  |

| Mode 6                     |                                    | Not yet                       | supported. |                                   |  |

| Mode 7 <sup>(1)</sup>      | 983.04 MHz                         | 491.52M                       | 2          | Depends on<br>programmed NCO word |  |

|                            | 737.28 MHz                         | 368.64M                       | 2          | Depends on<br>programmed NCO word |  |

| Mode 8                     | 983.04 MHz                         | 491.52M                       | 1          | 0                                 |  |

|                            | 737.28 MHz                         | 368.64M                       | 1          | 0                                 |  |

| Table 3.    | <b>HSDC</b> Pro | ADC Output | Data Rate   |

|-------------|-----------------|------------|-------------|

| 1 4 6 1 6 1 |                 |            | - Data Hato |

(1) The ADC Sampling Rate used in HSDC Pro for Mode 7 depends on the .ini file used. The example shown here applies to selecting 'ADS58J64\_LMF\_4421\_mode7' which strips the buffered 0s from the data stream.

For operating in a mode other that Mode 0, follow the default start-up procedure, and then perform the following:

- 1. From the ADS58J64 Mode tab in the configuration GUI, select the desired mode.

- 2. When selecting the device in HSDC Pro (), choose the device and enter the ADC Output Data Rate as reported by the configuration GUI on the ADS58J64 Mode tab.

Based on the sampling rate and mode of operation, adjust *ADC Output Rate Additional Device Parameters* to correctly label the harmonics. An example is shown in Figure 4 for Mode 0.

## 3.2 LMK04828 Clocking Configuration

The sampling clock provided to the ADS58J64 device is generated by the LMK04828 device in the default EVM hardware configuration. Configuration scripts are provided with the Configuration GUI to set up the LMK04828 device in two different states, as shown in Table 4.

The states use the full PLL1 + PLL2 operation and use the onboard VCXO (Y1) for PLL1. If it is required to operate the LMK04828 device in clock distribution mode, the onboard VCXO must be disabled by removing the shorting jumper at JP2.

| Macro State Script        | LMK04828 Mode      | ADS58J64 Device<br>Clock Frequency | Clock Frequency<br>Required at<br>LMK_CLK_IN (J12) | Configuration GUI<br>Shortcut | JP2   |

|---------------------------|--------------------|------------------------------------|----------------------------------------------------|-------------------------------|-------|

| LMK04828_config2_737M.cfg | PLL1 + PLL2        | 737.26 MHz                         | 61.44 MHz                                          | Button on INTRO tab           | Short |

| LMK04828_config2_983M.cfg | PLL1 + PLL2        | 983.04 MHz                         | 61.44 MHz                                          | Button on INTRO tab           | Short |

| LMK04828_config1.cfg      | Clock distribution | Equal to frequency at LMK_CLK_IN   | Flexible                                           | not available                 | Open  |

| Table 4. LK04828 Macro | States | Provided in | Configuration GUI |

|------------------------|--------|-------------|-------------------|

|                        | 0.000  |             |                   |

# 3.3 Using an External Clock

The LMK04828 device provides a very low-noise device clock, but the noise performance may not be as good as a premium bench RF signal generator, so the measured noise performance of the ADS58J64 device can be optimized by using an external signal generator as a clock source.

To provide the ADS58J64 device with an external clock (through EXT\_ADC\_CLK, J6 on the EVM), the following hardware changes must be performed on the EVM:

- Remove C47 and C48

- Place R35 and R39 with 0.1-µF 0402 capacitors.

The external clock is provided to the EVM through the J6 SMA connector at the full device clock rate (983.04 or 737.26 MHz), and amplitude of 6 dBm. This signal path must be filtered to reduce the broadband noise and remove any nonharmonic spurs. Narrow-band filters are recommended to remove as much noise as possible. If a signal generator output is used directly without filtering, significant degradation in SNR results.

A signal with the same frequency must also be provided to the LMK\_CLK\_IN J12 SMA connector with an amplitude of 6 dBm. If these signals are provided from different signal generators, the frequencies of the signals provided to J6 and J12 must be frequency locked together. Alternatively, a power splitter may be used to divide the signal from a single clock generator. When using an external clock, the LMK04828 device must be configured using the *LMK04828\_config1.cfg* macro.

Figure 6 shows the test setup using an external device clock source.

Figure 6. Test Setup Using an External Device Clock Source

# 3.4 Using a Coherent Input Source Frequency

A rectangular window function can be applied to the captured data when the sample rate and the input frequency are set precisely to capture an integer number of cycles of the input frequency (sometimes called coherent frequency). Coherent input and sampling frequencies may yield better SNR results. The clock and analog inputs must be frequency locked (such as through 10-MHz references) to achieve coherency.

# 3.5 HSDC Pro Settings

Table 5 lists the HSDC Pro options which can help improve the performance measurements.

| HSDC Pro Feature                                   | Description                                                                                                                                                                                                                     |  |  |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Analysis window (samples)                          | Selects the number of samples to include in the selected test analysis. Collect more data to improve frequency resolution of FFT analysis.                                                                                      |  |  |

| Data windowing function                            | Select the desired windowing function applied to the data for FFT analysis. Select<br>'Blackman' when sampling a non-coherent input signal or 'Rectangle' when sampling a<br>coherent input signal.                             |  |  |

| Test options $\rightarrow$ notch frequency bins    | Select bins to be removed from the spectrum and back-filled with the average noise level. May also customize which Harmonics/Spurs are considered in SNR and THD calculations and select the method for calculating spur power. |  |  |

| Test options $\rightarrow$ analysis window markers | Enable markers to narrow the Single-Tone FFT test analysis to a specific bandwidth.                                                                                                                                             |  |  |

| Data capture options $\rightarrow$ capture options | Configure the number of contiguous samples per capture (capture depth). May also enable Continuous Capture and FFT Averaging.                                                                                                   |  |  |

Table 5. HSDC Pro Options for Optimal Analysis Results

# 4 Software Description

## 4.1 ADS58J64 GUI

Figure 7 shows the front page of the ADS58J64 GUI as it appears upon opening the GUI.

| ADSS8J64EVM GUI |                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| File Debug      | Settings Help                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                 | ADS58J64EVM Configuration GUI (PG1.0) V.2                                                                                                                                       |  |  |  |  |  |  |  |  |

| INTRO           | ADS58J64 Mode ADS58J64 Other LMK04828 ELOw Level View USB Status (Construct)                                                                                                    |  |  |  |  |  |  |  |  |

|                 |                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                 | EVM Configuration Procedure                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                 | 1) Press one of the 'Configure LMK04828' button to the right to configure the LMK clocking chip on the EVM at the desired sampling rate.                                        |  |  |  |  |  |  |  |  |

|                 | 2) Press the ADC RESET SW1 button on the ADS58J54EVM hardware                                                                                                                   |  |  |  |  |  |  |  |  |

|                 | 3) Press the 'Configure ADS58J64' button to the right to configure the ADS58J64 into Mode 0 and with proper trim. Configure ADS58J64 Configure ADS58J64                         |  |  |  |  |  |  |  |  |

|                 | 4) Press the 'Disable LMK04828 SYSREF' button to turn the SYSREF signal OFF. If desired, the SYSREF can be turned back on on the LMK04828 -> SYNC and SYSREF tab                |  |  |  |  |  |  |  |  |

|                 | 5) Set the desired ADS58J64 DDC mode on the ADS58J64 Mode tab Disable LMK04828                                                                                                  |  |  |  |  |  |  |  |  |

|                 | 6) Open HSDC Pro and follow instructions on ADS58J64 Mode Tab to select the correct device, and enter correct ADC Output Data Rate                                              |  |  |  |  |  |  |  |  |

|                 | The 'Demo One-Push Setup' button executes the following editable configuration files in one step. By default, these execute the procedure above but may be modified as desired. |  |  |  |  |  |  |  |  |

| Write Registe   | er: DIGTOP_ADS58J64.COR 7/5/2016 4:38:44 PM Build: SIMULATION Idle 🐺 TEXAS INSTRUMENTS                                                                                          |  |  |  |  |  |  |  |  |

|                 |                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

## Figure 7. ADS58J64 GUI

Table 6 lists descriptions for each of the tabs of the GUI.

## Table 6. ADS58J64 GUI Tab Descriptions

| Tab                                                                | Description                                                                                                                                                                                              |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRO Quick configuration of the devices on the EVM for evaluation |                                                                                                                                                                                                          |

| ADS58J64 Mode                                                      | Provides DDC Mode control for the ADS58J64                                                                                                                                                               |

| ADS58J64 Other                                                     | Provides additional functionality controls for the ADS58J64                                                                                                                                              |

| LMK04828                                                           | Provides controls for the LMK04828 features that can be used to customize evaluation or set up more advanced clocking schemes.                                                                           |

| Low Level View                                                     | Allows write and read access to all device registers and bits. Also allows loading and saving of configuration files. The device configurations can be saved from this tab for use in the user's system. |

## 4.2 Low Level View

Figure 8 shows the Low Level View tab, which allows users to configure the ADS58J64 ADC at the register bit and field levels.

|                      |                          | 1        | -       |         | 1    |       |              | _          | guration G                  | Re                     | egister Data                 |

|----------------------|--------------------------|----------|---------|---------|------|-------|--------------|------------|-----------------------------|------------------------|------------------------------|

| NTRO                 | ADC16DX370               | LMH65    | 21      | MK0482  | 8 0  | 4X258 | 31           | <u>ا</u> ا | ow Level View               |                        | USB Status Reconnect FTDI ?  |

| Register N           | tap                      |          |         |         |      |       |              |            | Write Data                  | Register Data          | Transfer Read to Write       |

|                      | gister Name              |          | Address | Default | Mode | Size  | Value        |            | 4 129                       |                        |                              |

|                      | C16DX370<br>CONFIG A     |          | 0.00    | 0x3C    | R/W  | 8     | 0.30         | i.         | Write Register              | R W<br>0 2 2 x0012RES1 | 10(1/2)                      |

|                      | DEVICE_CONFIG            |          | 0.02    | 0.00    | R/W  | 8     | 0.00         | -          |                             | 1 0012RES1             |                              |

|                      | CHEP_TYPE                |          | 0x03    | 0x03    | R/W  | 8     | 0.03         |            | Write All                   | 2 SYS_EN[1/            |                              |

|                      | CHIP_ID0<br>CHIP_ID1     |          | 0.04    | 0.02    | R    | 8     | 0.02         |            | Read Data                   | 3 [[] IDLE[1/2]        |                              |

| (                    | CHIP_VERSION             |          | 0.06    | 0.00    | R    | 8     | 0.00         |            | * 81                        | 4 - DLE[2/2]           |                              |

|                      | /ENDOR_ID0<br>/ENDOR_ID1 |          | 0.00    | 0:04    | R    | 8     | 0.04         |            | Read Register               | 5 🖂 🖄 x0012RES6        | 65                           |

|                      | SPLCFG                   |          | 0,00    | 0x01    | R/W  | 8     | 0.01         |            | Read All                    | 6 🔄 🔤 x0012RES6        | Load/save                    |

|                      | DMI                      |          | 0:12    | 0x81    | R/W  | 8     | 0.81         |            | Current Address             | 7 👽 💟 DF[1/1]          |                              |

|                      | OM2<br>MB_ADJ_A          |          |         |         |      | Ϋ́.   | 0x40         |            | × 12                        |                        | config                       |

| 1                    | MB_ADJ_B                 | egis     | ter     | Fie     | ld   |       | 0.00         |            | Note: Load                  |                        |                              |

|                      | SESERVED WVV             | <u> </u> |         |         |      |       | 0xCD<br>0x58 |            | Config will                 |                        |                              |

| F                    | RESERVED0018             | Desc     | rin     | tior    | าร   |       | AB/0         |            | Overwrite all<br>Registers. |                        | Generic                      |

|                      | CDLY_CTRL                |          | 0x1A    | 0.00    | R/W  |       | 0.00         |            |                             |                        | Generic                      |

|                      | RESERVEDOOLB             |          | 0:48    | 0.00    | R/W  | ŝ     | 0.00         |            | Load Config                 | K I                    | Deed/Write                   |

| F                    | RESERVEDO                |          | 0x1C    | 0x48    | R/W  | 8     | 0x48         | ٠          | Save Config                 |                        | Read/Write                   |

|                      | Description              |          |         |         |      |       |              |            |                             |                        |                              |

| DF[7:7]<br>Data Form |                          |          |         |         |      |       |              | -          | Block                       | Address                | Write Data Read Data_Generic |

|                      | 5(1:0)(6:5)              |          |         |         |      |       |              |            | ADC160X370                  | · · 12                 | × 81 × 81                    |

| Reserved             | 43]                      |          |         |         |      |       |              |            |                             |                        | Write Register Read Register |

Figure 8. Low Level View Tab

At any time, the controls described in Table 7 can be used to configure or read from the device.

### Table 7. Low Level View Controls

| Control                             | Description                                                                                                                                                                 |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Register Map                        | Displays the devices on the EVM, registers for those devices, and the states of the registers.                                                                              |  |  |  |

|                                     | Selecting a register field allows bit manipulation in the Register Data section.                                                                                            |  |  |  |

|                                     | • The Value column shows the value of the register at the time the GUI was last updated due to a read or write event.                                                       |  |  |  |

| Write Register button               | Write to the register highlighted in the Register Map with the value in the Write Data field. This button must be clicked after changing bits in the register data section. |  |  |  |

| Write All button                    | Update all registers shown in the Register Map with the values shown in the Register Map summary.                                                                           |  |  |  |

| Read Register button                | Read from the register highlighted in the Register Map and display the results in the Value column.                                                                         |  |  |  |

| Read All button                     | Read from all registers in the Register Map and display current state of hardware.<br>Also updates the controls in the other tabs.                                          |  |  |  |

| Load Config button                  | Load a Configuration File from the disk and write the registers in the file.                                                                                                |  |  |  |

| Save Config button                  | Save a Configuration File to the disk that contains the current register configuration.                                                                                     |  |  |  |

| Register Data Cluster               | Manipulate individual accessible bits of the register highlighted in the Register Map.                                                                                      |  |  |  |

| Generic Read/Write Register buttons | Perform a generic read or write command to the device shown in the <i>Block</i> drop-<br>down box using the Address and Write Data information                              |  |  |  |

# 5 EVM Hardware Modifications from Default

The following hardware changes are required for proper operation of the ADS58J64EVM Rev.A default PCB, built and assembled with PG1.0 ADS58J64 silicon:

- 1. Replace C72/72 with 75  $\Omega$  0402 resistors

- 2. Place R105/106 with 150  $\Omega$  0402 resistors

# A.1 Jumper, Header, and Button Descriptions

Table 8 lists the EVM jumpers and buttons, as well as the default settings for the jumpers. If there are issues, use Table 8 to reset the EVM in the default configuration.

| Jumper | Description                                                      | Default Setting |

|--------|------------------------------------------------------------------|-----------------|

|        | Rx Global Power-Down                                             |                 |

|        | Short 1 – 2: Force as logic HIGH (power down)                    |                 |

| JP7    | Short 2 – 3: Force as logic LOW (normal operation)               |                 |

|        | <b>NOTE:</b> Open is not<br>a valid state<br>for this<br>jumper. | Short 2 – 3     |

|        | SPI Select, CPLD                                                 |                 |

|        | Short 1 – 2: Reserved. Do not use this state.                    |                 |

|        | Short 2 – 3: Default state                                       | -               |

| JP3    | <b>NOTE:</b> Open is not<br>a valid state<br>for this<br>jumper. | Short 2 – 3     |

|        | VCXO Power                                                       |                 |

| JP2    | Short: Supplies 3.3 V to Y1 VCXO                                 | Short           |

|        | Open: Disconnects power from Y1 VCXO                             |                 |

|        | External trigger for Burst Mode, channels A and B                |                 |

| TRIGAB | Pin 1: Trigger signal, 1.8-V logic                               | Open            |

|        | Pin 2: Ground                                                    |                 |

|        | Open: Trigger function not used                                  |                 |

|        | External trigger input for Burst Mode, channels C and D          | Open            |

| TRIGCD | Pin 1: Trigger signal, 1.8-V logic                               |                 |

|        | Pin 2: Ground                                                    |                 |

|        | Open: Trigger function not used                                  |                 |

|        | Trigger Ready output for Burst Mode, channel A and B             | Onen            |

| TRDYAB | Pin 1: Trigger ready signal, 1.8-V logic                         | Open            |

|        | Pin 2: Ground                                                    |                 |

Table 8. Jumper and Button Descriptions and Default Settings

| Jumper | Description                                          | Default Setting |  |

|--------|------------------------------------------------------|-----------------|--|

|        | Trigger Ready output for Burst Mode, channel C and D |                 |  |

| TRDYCD | Pin 1: Trigger ready signal, 1.8-V logic             | Open            |  |

|        | Pin 2: Ground                                        |                 |  |

| SW1    | ADC Reset                                            | - N/A           |  |

| 5001   | Press to reset ADC and its registers.                | - N/A           |  |

|        | ADS58J64 SPI Monitoring Header, ADC<br>SPI           |                 |  |

|        | Pin1: SCK                                            | -<br>· ·        |  |

| J15    | Pin2: SEN                                            | OPEN            |  |

|        | Pin3: SDIO                                           |                 |  |

|        | Pin4: SDO                                            |                 |  |

|        | JTAG Programming Header for CPLD, U3                 |                 |  |

|        | Pin1: TCK                                            |                 |  |

|        | Pin3: TDO                                            | -               |  |

| J14    | Pin4: +1.8 V                                         | OPEN            |  |

|        | Pin5: TMS                                            |                 |  |

|        | Pin9: TDI                                            |                 |  |

|        | Pin2, Pin10: GND                                     |                 |  |

# Table 8. Jumper and Button Descriptions and Default Settings (continued)

# A.2 Connector Descriptions

Table 9 lists the EVM connectors and their function.

## **Table 9. Connector Descriptions**

| Connector        | Description                                  |

|------------------|----------------------------------------------|

| AIN (J1)         | Receiver (ADS58J64) analog input, channel A  |

| BIN (J7)         | Receiver (ADS58J64) analog input, channel B  |

| CIN (J8)         | Receiver (ADS58J64) analog input, channel C  |

| DIN (J5)         | Receiver (ADS58J64) analog input, channel D  |

| EXT_ADC_CLK (J6) | Receiver (ADS58J64) external clock input     |

| LMK_CLK_IN (J12) | LMK04828 reference clock input               |

| J13              | USB3 mini connector for device configuration |

| J14              | 5-V power connector                          |

LED Descriptions

# A.3 LED Descriptions

Table 10 lists the EVM LEDs.

# Table 10. LED Descriptions

| LED              | Description                         |

|------------------|-------------------------------------|

| PWR (D2)         | Indicates status of input power     |

|                  | OFF: Power is not provided at J14   |

|                  | ON: Power <i>is</i> provided at J14 |

| CLKIN0 SEL (D4)  | Not functional                      |

| CLKIN1 SEL (D5)  | Not functional                      |

| PLL1 LOCKED (D6) | LMK04828 lock detect, PLL1          |

|                  | OFF: PLL is not locked              |

|                  | ON: PLL is locked                   |

| PLL2 LOCKED (D3) | LMK04828 Lock Detect, PLL2          |

|                  | OFF: PLL is not locked              |

|                  | ON: PLL is locked                   |

| JESD_SYNC (D7)   | Not functional. Always dimly lit.   |

www.ti.com

### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated