## PGA4311 Evaluation Module

# User's Guide

#### IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of Tl's products or services with <u>statements different from or beyond the parameters</u> stated by Tl for that product or service voids all express and any implied warranties for the associated Tl product or service, is an unfair and deceptive business practice, and Tl is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

#### **EVM IMPORTANT NOTICE**

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation kit being sold by TI is intended for use for **ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY** and is not considered by TI to be fit for commercial use. As such, the goods being provided may not be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety measures typically found in the end product incorporating the goods. As a prototype, this product does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may not meet the technical requirements of the directive.

Should this evaluation kit not meet the specifications indicated in the EVM User's Guide, the kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies TI from all claims arising from the handling or use of the goods. Please be aware that the products received may not be regulatory compliant or agency certified (FCC, UL, CE, etc.). Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the user **is not exclusive.**

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the EVM User's Guide and, specifically, the EVM Warnings and Restrictions notice in the EVM User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact the TI application engineer.

Persons handling the product must have electronics training and observe good laboratory practice standards.

No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which such TI products or services might be or are used.

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the input voltage range of 7.5Vp-p and the output voltage range of 7.5Vp-p.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 50°C. The EVM is designed to operate properly with certain components above 50°C as long as the input and output ranges are maintained. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright • 2002, Texas Instruments Incorporated

## **Read This First**

#### About This Manual

This document provides information pertinent to the setup and operation of the PGA4311 evaluation module. This includes hardware configuration, as well as software installation. For a more detailed description of the PGA4311 4-channel volume control product, the user is referred to the Related Documentation from Texas Instruments section of this manual.

#### How to Use This Manual

This manual is divided into three chapters. Chapters 1 and 2 provide information relevant to the hardware setup and configuration for the evaluation module. A complete schematic is also provided at the end of Chapter 2. Chapter 3 focuses on the installation and usage of the PC-based software used to control the PGA4311 for evaluation purposes.

For a more detailed topical breakdown and quick reference, please refer to the Contents, Figures, and Tables sections located just prior to Chapter 1 in this manual.

#### Related Documentation From Texas Instruments

Data Sheets Literature Number

PGA4311 Data Sheet SBOS230 PGA2310-EVM SBOU012

#### If You Need Assistance

If you have questions about this or other Texas Instruments data converter evaluation modules, feel free to e-mail the data converter application team at <a href="mailto:dataconvapps@list.ti.com">dataconvapps@list.ti.com</a>. Include the product name in the subject heading.

#### FCC Warning

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **Trademarks**

Windows is a registered trademark of Microsoft Corporation.

## **Contents**

| Read This First                                      | ii  |

|------------------------------------------------------|-----|

| About This Manual                                    |     |

| How To Use This Manual                               |     |

| Related Documentation From Texas Instruments         |     |

| If You Need Assistance                               |     |

| FCC Warning                                          |     |

| Trademarks                                           |     |

| Contents                                             | iv  |

| Figures                                              |     |

| Tables                                               |     |

| Operating Conditions and Block Diagram               |     |

| 1.1 Recommended Operating Conditions                 |     |

| 1.2 EVM Block Diagram                                | 1-2 |

| Hardware Guide                                       | 2-1 |

| 2.1 Power Supplies                                   | 2-2 |

| 2.2 PC Parallel Port Interface                       | 2-2 |

| 2.3 DATA IN and DATA OUT Headers                     | 2-2 |

| 2.4 Analog Input and Output Connectors               | 2-2 |

| 2.5 Registor Loop-Back Jumper                        | 2-3 |

| 2.6 Schematic                                        |     |

| Software Guide                                       | 3-1 |

| 3.1 System Requirements                              | 3-2 |

| 3.2 Installation Procedure                           |     |

| 3.3 Getting Started: The Main Panel                  | 3-2 |

| 3.4 Determining and Setting the Printer Port Address | 3-3 |

| 3.5 Programming the PGA4311: The DUT Panels          | 3-3 |

| 3.6 Gain Controls                                    | 3-4 |

| 3.7 Mode Controls                                    | 3-4 |

| 3.8 Register Loop-Back Controls                      | 3-4 |

| 3.9 Ramp Function Controls                           | 3-4 |

## **Figures**

| Figure 1. | EVM Block Diagram                       | 1-2    |

|-----------|-----------------------------------------|--------|

| Figure 2. | EVM Schematic                           |        |

| Figure 3. | The Main Panel                          |        |

| Figure 4. | The DUT1 Control Panel                  |        |

| Figure 5. | The DUT2 Control Panel                  |        |

|           |                                         |        |

|           |                                         | Tables |

|           |                                         |        |

| Table 1.  | Requirements for Three-Supply Operation | 2-2    |

| Table 2.  | Requirements for Two-Supply Operation   |        |

|           |                                         |        |

### Chapter 1

## **Operating Conditions and Block Diagram**

This chapter provides a brief listing of the reccommended operating conditions for the PGA4311 evaluation module. A simplified functional block diagram is also provided for reference when reading through Chapter 2.

| Торіс                            | Page |

|----------------------------------|------|

| Recommended Operating Conditions | 1-2  |

| PGA4311-EVM Block Diagram        | 1-2  |

#### 1.1 Recommended Operating Conditions

| Analog Supplies                     |              |

|-------------------------------------|--------------|

| VA+                                 | +5.0V DC     |

| VA                                  | 5.0V DC      |

| Digital Supply                      |              |

| VD+                                 | +5.0V DC     |

| Ambient Temperature                 | 0°C to +40°C |

| Input Voltage, AIN1 through AIN4    | 7.5Vp-p max  |

| Output Voltage, AOUT1 through AOUT4 | 7.5Vp-p max  |

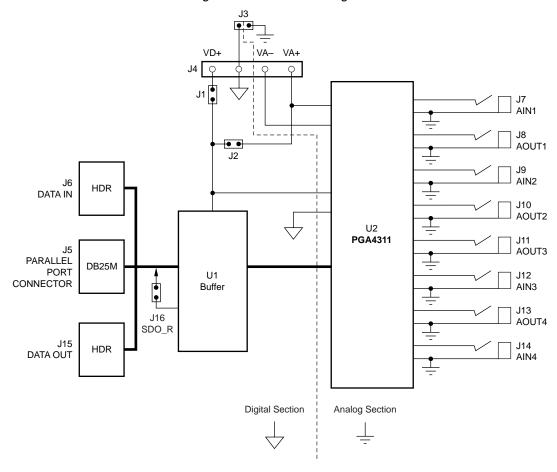

### 1.2 PGA4311-EVM Block Diagram

Figure 1. EVM Block Diagram.

## Chapter 2

## **Hardware Guide**

This chapter provides hardware setup and configuration information for the PGA4311 evaluation module. A complete schematic is also provided at the end of this chapter.

| Горіс                              | Page |

|------------------------------------|------|

| Power Supplies                     |      |

| PC Parallel Port Interface         | 2-2  |

| DATA IN and DATA OUT Headers       | 2-2  |

| Analog Input and Output Connectors | 2-2  |

| Registor Loop-Back Jumper          | 2-3  |

| Schematic                          | 2-4  |

|                                    |      |

#### 2.1 Power Supplies

The PGA4311-EVM includes a power supply connector, labeled J4 on the circuit board. Four locking terminals are provided for the analog power supplies (VA+ and VA-), a digital power supply (VD+), and a common ground (GND). There are two configuration modes for the power supplies: Three-Supply operation and Two-Supply operation.

In the case of Three-Supply operation, jumper J1 is installed while jumper J2 is an open circuit. Separate supplies are required for VD+, VA+, and VA-. The supplies share a common ground connection at the GND terminal. Table 1 shows the supply configuration details.

Table 1. Requirements for Three-Supply Operation.

| Supply<br>Designator | Recommended<br>Supply Voltage | Supply<br>Voltage Range |

|----------------------|-------------------------------|-------------------------|

| VD+                  | +5V                           | +4.5V to +5.5V          |

| VA+                  | +5V                           | +4.5V to +5.5V          |

| VA-                  | –5V                           | −4.5V to −5.5V          |

NOTE: Install jumper at J1. Remove jumper from J2 (open circuit).

In the case of Two-Supply operation, jumpers are installed at both J1 and J2. The J2 jumper connects the VA+ terminal to the VD+ terminal, with VA+ providing both the positive analog and digital supplies. Separate supplies are required for VA+ and VA-. The supplies share a common ground connection at the GND terminal. Table 2 shows the supply configuration details.

Table 2. Requirements for Two-Supply Operation.

| Supply     | Recommeded     | Supply         |

|------------|----------------|----------------|

| Designator | Supply Voltage | Voltage Range  |

| VA+        | +5V            | +4.5V to +5.5V |

| VA-        | -5V            | -4.5V to -5.5V |

NOTE: Jumpers J1 and J2 need to be installed.

#### 2.2 PC Parallel Port Interface

The evaluation module includes a DB-25 connector, labeled J5, which is used to interface the PGA4311-EVM with a PC parallel (printer) port. The evaluation module software utilizes the parallel port to communicate with the PGA4311's serial interface. An interface cable is supplied as part of the evaluation module package.

#### 2.3 DATA IN and DATA OUT Headers

Two 14-pin headers are included on the evaluation module. They are labeled DATA IN and DATA OUT. The DATA IN header provides an alternative connection for host communications with the PGA4311's serial interface. It also provides a means for interfacing to another PGA4311-EVM when using a daisy-chain configuration. The DATA OUT header is used for connection to the DATA IN header of another PGA4311-EVM when implementing a daisy-chain configuration.

#### 2.4 Analog Input and Output Connectors

The evaluation module includes RCA jacks for connection to waveform generators, signal analyzers, and commercial audio equipment. The input jacks are labeled AIN1 through AIN4, while the output jacks are labeled AOUT1 through AOUT4. The analog inputs and outputs are unbalanced (referenced to ground). The analog input or output swing at these terminals must not exceed 7.5Vpp when powered from ±5V analog power supplies.

#### 2.5 Register Loop-Back Jumper

The evaluation module contains a loop-back jumper, labeled SDO\_R. The purpose of this jumper is to allow read back of the gain register values. This is helpful when diagnosing problems with the PC parallel port interface or host controller communications.

The serial interface is basically a 32 bit serial IN, serial OUT shift register. The SDI pin is the input, while SDO is the output. As 32 bits of new data are shifted into the PGA4311, the previously programmed 32-bits are being shifted out. This allows the user to read back the values to determine if the device is being programmed correctly. It also allows multiple PGA4311 devices to be cascaded, or daisy-chained, to form a 32 • N-bit long shift register, where N is the number of devices included in the chain. This arrangement allows a 3-wire interface to program multiple PGA4311 devices connected in a daisy-chain fashion.

#### 2.6 Schematic

Figure 2. EVM Schematic. ERROR SUN DO NO DO ACK

BUSY

P EMPT

SELECT

A FEED MUTE SCLK \*\*\*\* SDI (N + 1) SCLK CS ZCEN 0 0 8 SDI (N) 0 0 10 cs RB SDI (1) 12 ZCEN 9 G2 GND SN74HC54IN 8 7 8 8 1 2 2 1 ₩ S S VD 20 0.01μF | \*\*\*\*\*\*\*\*\*\* 11 12 13 14 15 16 17 18 TP7

OZCEN

OSDI

OSCLK

OMUTE AIN1 4 ₽ 0 GND ş ×<sub>A</sub> SI SP YP PGA4311PA DUT\_N R1 100kΩ 4 \_C<sub>3</sub> \_10µF C<sub>12</sub> to DUT pin 17 and DUT pin 23. Guard AIN pins with adjacent AGND pins. J3 is a jumper wire. POĘ ₽ 172 o₽ 4 AOUT2 A A

2-4

### Chapter 3

## **Software Guide**

This chapter provides information regarding evaluation software installation and application. Software control panel operation is described in detail, with graphics of each panel providing a visual reference.

Note: The PGA4311-EVM utilizes the applications software created for the PGA2310-EVM. Where needed, differences in operation between the PGA4311-EVM and PGA2311-EVM will be explained in more detail.

| Topic                                            | Page |

|--------------------------------------------------|------|

| System Requirements                              | 3-2  |

| Installation Procedure                           | 3-2  |

| Getting Started: The Main Panel                  | 3-2  |

| Determining and Setting the Printer Port Address | 3-3  |

| Programming the PGA4311: The DUT Panels          | 3-3  |

| Gain Controls                                    | 3-4  |

| Mode Controls                                    | 3-4  |

| Register Loop-Back Controls                      | 3-4  |

| Ramp Function Controls                           | 3-4  |

|                                                  |      |

#### 3.1 System Requirements

The supplied software will operate on personal computers designed for use with Windows 95 and 98. A CD-ROM drive is required for installation of program files and access to support documents. Approximately 4MB of hard disk space is required for installation.

#### 3.2 Installation Procedure

The following procedure assumes familiarity with navigating the Windows desktop to find folders and files located on mounted volumes. Should you need assistance with this, please consult the Windows Help system.

Step 1: Insert the accompanying CD into your CD-ROM drive.

<u>Step 2</u>: Locate the **PGA2310-EVM** folder on the CD, using either My Computer or Windows Explorer.

<u>Step 3</u>: Double-click the **PGA2310-EVM** folder icon, and then locate the **Package** folder. Double-click on the **Package** folder icon to open the folder. Locate the file named **Setup.exe**. Double-click the **Setup.exe** icon to start the installation process. Follow the on-screen instructions to complete the installation procedure.

#### 3.3 Getting Started: The Main Panel

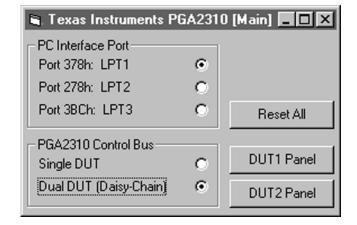

The setup program installs a Texas Instruments folder in the Programs folder of the Start menu. Within the Texas Instruments folder is the PGA2310 EVM program. Selecting this program will startup the applications software.

Once the program is started, the Main panel will be displayed, as shown in Figure 3. The Main panel allows the user to select the parallel (or printer) port address, and either Single or Dual DUT operation. The 'Reset All' button will revert all settings to their startup defaults. Pressing the DUT1 Panel and DUT2 Panel buttons will open panels containing the PGA4311 control objects, as shown in Figures 4 and 5.

Figure 3. The Main Panel.

#### 3.4 Determining and Setting the Printer Port Address

The parallel port address for your PC can be found by going to the Start menu and selecting the Control Panel item in the Settings menu. When the Control Panels window opens, find the System icon and double click it. From the System window, select the Device Manager tab by clicking on it once. Scroll down the list of devices until you see the Ports entry. Double click on the Ports entry to list the PC ports. One of the ports should be a Printer Port. Double click on the Printer Port entry to open the Printer Port window. From the Printer Port window, select the Resources tab by clicking on it once. The Input/Output Range is displayed (ex/ 0378 - 037F). Write down the starting number in the range (ex/ 0378), and go to the Main panel of the evaluation module program and select the port address that matches this number.

#### 3.5 Programming the PGA4311: The DUT Panels

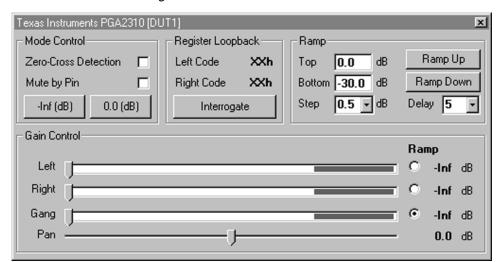

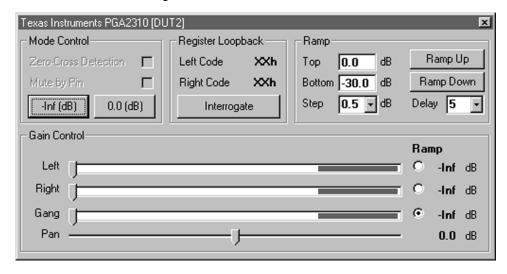

All controls for the PGA4311 are contained within the DUT1 and DUT2 control panels, as shown in Figures 4 and 5. This section describes the functions contained within these panels.

Figure 4. The DUT1 Control Panel.

#### 3.6 Gain Controls

The Gain Controls occupy the bottom half of each DUT panel. There are three gain sliders, including one each for left and right channel, and a Gang slider for controlling both channels simultaneously. The DUT1 panel controls Channels 1 and 2 of the PGA4311, with Channel 2 corresponding to the right channel, and Channel 1 corresponding to the left channel. The DUT2 panel controls Channels 3 and 4 of the PGA4311, with Channel 4 corresponding to the right channel, and Channel 3 corresponding to the left channel.

When the PGA4311 first powers up, all channels will reset to maximum attenuation (or mute). The software also defaults to maximum attenuation at startup (shown as –Inf to the right of the sliders). A display to the right of each slider displays the currently selected gain setting.

The Ramp radio buttons to the right of each slider are used to select the gain slider to be automated when using the Ramp controls in the upper right-hand corner of the DUT panel.

The Pan slider functions as a Balance control, simultaneously gaining one channel while attenuating the other. It's behaves just like the balance control on your home or car stereo system.

#### 3.7 Mode Controls

The Mode control section resides in the upper left-hand corner of each DUT panel. Only the mode controls in the DUT1 control panel are enabled. Several functions are accessible from this section. The Zero-Cross Detection checkbox is used to enable and disable the zero crossing detector circuit inside the PGA4311 device. The default setting is zero crossing detection disabled.

The Mute by Pin checkbox is used to enable or disable the MUTE pin function of the PGA4311. When MUTE is LOW, the PGA4311 sets both left and right channel attenuation to maximum (or mute). The default setting is mute disabled.

Two buttons allow the user to quickly set the gain of both left and right channels to either 0dB or –Inf dB (or mute). The –Inf dB button differs from the Mute by Pin checkbox in that it programs maximum attenuation for both left and right channels using the PGA4311's gain control registers, as opposed to using the MUTE pin.

#### 3.8 Register Loop-Back Controls

With the SDO\_R jumper installed, the user can test the function of the PGA4311 serial interface by using the Register Loop-Back control available in each DUT panel. Simply press the Interrogate button to read back the values being programmed for each channel. This function is included primarily for diagnostics, to ensure that the PC parallel port and the PGA4311 are communicating properly.

#### 3.9 Ramp Function Controls

The Ramp controls allow automation of the gain settings for the PGA4311. The user enters the top and bottom points for the ramp, along with the desired step size and delay between steps. The ramp may be generated from bottom to top (Ramp Up) or from top to bottom (Ramp Down) for the given range. The ramp step size may be set from 0.5dB to 3.0dB in 0.5dB increments. The ramp step delay may be set using relative delay settings of 0, 1, 2, 5, 10, 20, or 50.

The channel selection for the automated ramp is selected using the radio buttons located to the right of the gain sliders in the Gain Control section of each DUT panel.