# **DEM-OPA-DSN-EVM User's Guide**

#### **ABSTRACT**

The DEM-OPA-DSN-EVM is a demonstration fixture that helps designers evaluate the operation and performance of TI's high speed, wide bandwidth operational amplifiers. This unpopulated PC board is compatible with dual channel amplifier products offered in the 10-pin SON (DSN) package. The board is designed to accommodate multiple amplifier configurations to allow for maximum flexibility and ease of use.

## **Table of Contents**

| 1 Features                                         |   |

|----------------------------------------------------|---|

| 2 Power Connections                                | 2 |

| 2.1 Split-Supply Operation                         |   |

| 2.2 Single Supply Operation                        |   |

| 3 Input and Output Connections                     |   |

| 4 Schematic                                        |   |

| 5 Layout                                           |   |

|                                                    |   |

| List of Figures                                    |   |

| Figure 4-1. DEM-OPA-DSN-EVM Schematic              |   |

| Figure 5-1. DEM-OPA-DSN-EVM Top Layers             |   |

| Figure 5-2. DEM-OPA-DSN-EVM Ground Layer (Layer 2) |   |

| Figure 5-3. DEM-OPA-DSN-EVM Power Layer (Layer 3)  |   |

| Figure 5-4. DEM-OPA-DSN-EVM Bottom Layers          | Δ |

# **List of Tables**

#### **Trademarks**

All trademarks are the property of their respective owners.

Features Vivil Com

#### 1 Features

- Configurable for single or split-supply operation

- Includes optional termination resistors on inputs and outputs for easy use with  $50-\Omega$  test equipment

- Feedback network components for inverting and non-inverting configurations

- · Standard SMA footprints for input and output signal connections

- High speed optimized layout to reduce parasitic effects

#### **2 Power Connections**

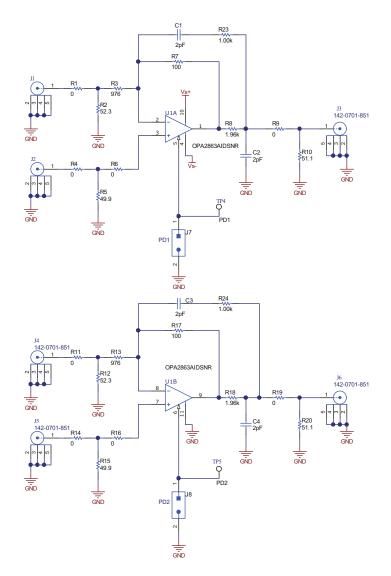

The DEM-OPA-DSN-EVM is equipped with test point connectors for easy connection of power. The positive supply input is red and is labeled V+. The negative supply input is yellow and is labeled V-. The ground is black and is labeled GND.

#### 2.1 Split-Supply Operation

To operate as split supply, apply the positive-supply voltage to V+, negative-supply voltage to V-, and the ground reference from supply to GND.

# 2.2 Single Supply Operation

To operate as single supply, connect both the V– connector and the GND connector to ground and apply the positive-supply voltage to V+. Inputs and outputs must be biased per the specifications listed in the data sheet for proper operation.

# 3 Input and Output Connections

The DEM-OPA-DSN-EVM is equipped with footprints for SMA connectors for connection of signal generators and analysis equipment. For best results, the input and output to the EVM should be terminated to  $50-\Omega$  impedances and signals must be routed to and from the EVM with cables having  $50-\Omega$  characteristic impedance. INA+ (J2) and INB+ (J5) include termination resistors R5 and R15 respectively for non-inverting configurations. For inverting configurations an resistor network (R1, R2, and R3 for amplifier A; R11, R12, and R13 for amplifier B) is included to match the input impedance while maintaining a desired gain resistor value. OUTA (J3) and OUTB (J6) are the output connectors for amplifiers A and B respectively. A resistor network (R8, R9, and R10 for amplifier A; R18, R19, and R20 for amplifier B) at the output of the amplifiers can be used to convert the signal to  $50-\Omega$  single-ended source while providing a larger total load to the amplifier when terminated with  $50-\Omega$  load at J3 and J6.

www.ti.com Schematic

# 4 Schematic

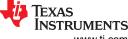

Figure 4-1 shows an example non-inverting configuration for the DEM-OPA-DSN-EVM using the OPA2863A. For details on configuring a specific amplifier for use with the evaluation module, please refer to the selected device's data sheet.

Figure 4-1. DEM-OPA-DSN-EVM Schematic

Layout www.ti.com

# 5 Layout

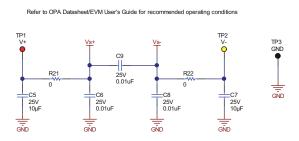

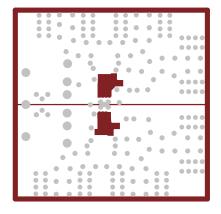

Figure 5-1 through Figure 5-4 show the respective PCB layers from top to bottom.

Figure 5-1. DEM-OPA-DSN-EVM Top Layers

Figure 5-2. DEM-OPA-DSN-EVM Ground Layer (Layer 2)

Figure 5-3. DEM-OPA-DSN-EVM Power Layer (Layer 3)

Figure 5-4. DEM-OPA-DSN-EVM Bottom Layers

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated