# User's Guide TPS7A13EVM-057 Evaluation Module

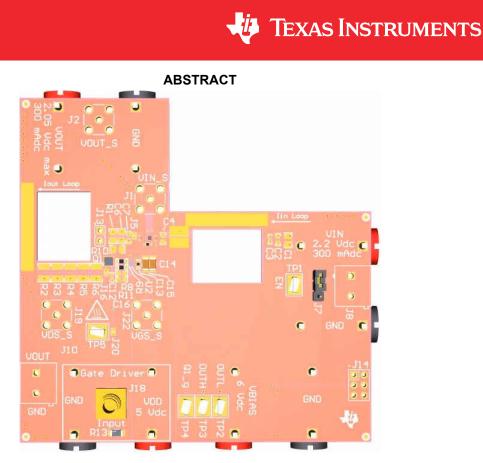

Figure 1-1. TPS7A13EVM-057 Evaluation Module

This user's guide describes the operational use of the TPS7A13EVM-057 evaluation module (EVM) as a reference design for engineering demonstration and evaluation of the TPS7A13 low-dropout linear regulator (LDO). Included in this user's guide are setup and operating instructions, thermal and layout guidelines, a printed-circuit board (PCB) layout, a schematic diagram, and a bill of materials (BOM).

Throughout this document, the terms *evaluation board*, *evaluation module*, and *EVM* are synonymous with the TPS7A13EVM-057.

# **Table of Contents**

| 1 Trademarks                                                    | 2  |

|-----------------------------------------------------------------|----|

| 2 Introduction                                                  |    |

| 3 Setup                                                         |    |

| 3.1 LDO Input/Output Connector Descriptions                     |    |

| 3.2 Optional Load Transient Input/Output Connector Descriptions | 3  |

| 3.3 TPS7A13 LDO Operation                                       | 5  |

| 3.4 Optional Load Transient Circuit Operation                   |    |

| 4 Board Layout                                                  | 9  |

| 5 TPS7A13 EVM Schematic                                         | 11 |

| 6 Bill of Materials                                             | 12 |

# **List of Figures**

| Figure 1-1. TPS7A13EVM-057 Evaluation Module                                | <mark>1</mark> |

|-----------------------------------------------------------------------------|----------------|

| Figure 3-1. TPS7A13EVM-057 Turn On                                          | 5              |

| Figure 3-2. TPS7A13EVM-057 With Current Probes Attached                     | 6              |

| Figure 3-3. TPS7A13EVM-057 Load Transient Results: 1-mA to 300-mA Load Step | <b>7</b>       |

| Figure 3-4. TPS7A13EVM-057 Load Transient Results: 300-mA to 1-mA Load Step | <mark>8</mark> |

| Figure 4-1. Top Assembly Layer and Silk Screen                              | 9              |

| Figure 4-2. Top Layer Routing                                               | 9              |

| Figure 4-3. Layer 2                                                         |                |

| Figure 4-4. Layer 3                                                         |                |

| Figure 4-5. Bottom Layer Routing                                            | 10             |

| Figure 4-6. Bottom Assembly Layer and Silk Screen                           |                |

| Figure 5-1. Schematic                                                       | 11             |

|                                                                             |                |

# 1 Trademarks

LeCroy<sup>™</sup> is a trademark of Teledyne LeCroy. Kapton<sup>®</sup> is a registered trademark of DuPont.

All trademarks are the property of their respective owners.

# 2 Introduction

The Texas Instruments' TPS7A13EVM-057 evaluation module (EVM) helps designers evaluate the operation and performance of the TPS7A13 LDO voltage regulator. As shown in Table 2-1, the TPS7A13EVM-057 contains one TPS7A13 LDO voltage regulator in the DSBGA package. An optional load transient circuit is also included to assist the user with high-speed load transient testing. An input current loop is included that allows fast measurements of the input current.

| Table 2-1. Device Information |                  |                |             |  |  |

|-------------------------------|------------------|----------------|-------------|--|--|

| EVM ORDERABLE NUMBER          | V <sub>OUT</sub> | PART NAME      | PACKAGE     |  |  |

| TPS7A13EVM-057                | 0.9 V            | TPS7A1309PYCKR | 6-pin DSBGA |  |  |

# 3 Setup

This section describes the jumpers and connectors on the EVM, and how to properly connect, set up, and use the TPS7A13EVM-057. Section 3.1 and Section 3.3 describe the test setup and operation for the TPS7A13 LDO. Section 3.2 and Section 3.4 describe the test setup and operation of the optional load transient circuit.

# 3.1 LDO Input/Output Connector Descriptions

# 3.1.1 VIN and GND

VIN and GND are the connection terminals for the input supply. The VIN terminal is the positive connection, and the GND terminal is the negative (that is, ground) connection.

## 3.1.2 BIAS and GND

BIAS and GND are the connection terminals for the input supply. The BIAS terminal is the positive connection, and the GND terminal is the negative (that is, ground) connection.

## 3.1.3 VOUT and GND

VOUT and GND are the connection terminals for the output load. The VOUT terminal is the positive connection, and the GND terminal is the negative (that is, ground) connection.

# 3.1.4 EN

EN is a 3-pin header used to enable or disable the TPS7A13.

The center pin of the 3-pin header is tied to the TPS7A13 EN input. When the 2-pin shunt is placed across the top two pins of the header, VIN is shorted to EN, and the TPS7A13 is enabled. When the 2-pin shunt is placed across the bottom two pins of the header, GND is shorted to EN, and the TPS7A13 is disabled.

When driving the EN terminal with an off-board supply or signal generator, the applied voltage must be kept between 0 V and 5.5 V.

# 3.2 Optional Load Transient Input/Output Connector Descriptions

# 3.2.1 VDD and GND

VDD and GND are the connection terminals for the input supply of the load transient circuit. The VDD terminal is the positive connection, and the GND terminal is the negative (that is, ground) connection.

# 3.2.2 J13

J13 is an optional connection for the user to make measurements or apply loads to the output of the LDO.

# 3.2.3 J15

J15 is an optional connection to insert a damping circuit across the load transient MOSFET drain to source voltage.

## 3.2.4 J16

J16 is an optional connection to insert capacitance or additional load across the drain to source of the load transient MOSFET.

#### Setup

# 3.2.5 J18

J18 is the connection for the function generator to drive the gate driver device. J18 is terminated by the 50- $\Omega$  resistor, R13.

# 3.2.6 J19

J19 is a high-frequency kelvin connection that allows accurate measurements of the load transient MOSFET drain to source voltage.

# 3.2.7 J22

J22 is a high-frequency kelvin connection that allows accurate measurements of the load transient MOSFET gate to source voltage.

# 3.2.8 TP2, TP3, and TP4

TP2, TP3, and TP4 allow the user to measure the gate drive resistances R8 and R9 when power is turned off to the EVM.

## 3.2.9 TP5

TP5 is the enable pin to enable the gate driver device. Tie this pin to GND to enable the gate driver.

# 3.3 TPS7A13 LDO Operation

The TPS7A13EVM-057 evaluation module contains the TPS7A13 LDO with input, bias, and output capacitors installed. These four components provide the minimum required solution size, as illustrated by the white boxes in Figure 3-2. Additional pads are available to test the LDO with additional input and output capacitors beyond what is already installed on the EVM. The TPS7A13 LDO can be enabled or disabled by using the J7 3-pin header.

- 1. Place a 2-pin shunt across the header to tie VIN to EN to enable the device.

- 2. Place a 2-pin shunt across the header to tie GND to EN to disable the device.

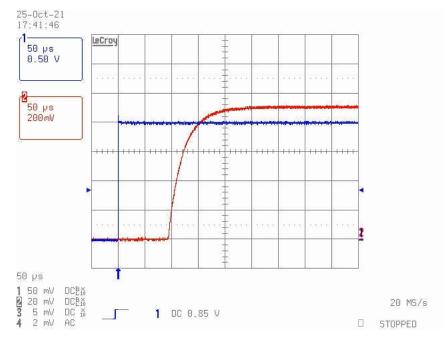

Alternatively, by connecting an external function generator to TP1 (EN) and a nearby GND post (J11), the user can enable or disable the TPS7A13 LDO after VIN is applied. Figure 3-1 shows the result of the TPS7A13EVM-057 during turn on. The blue trace is the enable voltage, and the red trace is the output voltage.

Figure 3-1. TPS7A13EVM-057 Turn On

If desired, a current probe can be inserted in the EVM as shown in Figure 3-2 to measure the input and output current. The slots were sized to fit most current probes, such as the LeCroy<sup>™</sup> AP015 or CP031 current probes.

Figure 3-2. TPS7A13EVM-057 With Current Probes Attached

The user has two options for providing a DC load on the output of the TPS7A13. J10 can be used to place a DC load that flows through the current sense path on the output of the LDO. Alternatively, the J4 (VOUT) and J12 (GND) banana connectors can be used for external measurements and loading; however, the IOUT loop does not sense current flowing through these connectors. In cases where very fast transient tests are performed, ringing may be observed on VIN or VOUT as a result of the parasitic inductance within the PCB of the EVM. A strip of wire placed on the exposed copper in the current path can reduce this ringing. Select the correct size of additional wire to fill the volume of the current probe. For most current probes, a 10 AWG wire can be used.

## WARNING

The sensors of some current probes are tied to GND and cannot come into contact with energized conductors. See the user manual of your current probe for details. If your current probe has this limitation, use a thin strip of electrical or Kapton<sup>®</sup> tape to isolate the current sense path from the current probe.

Optional kelvin sense points are provided using the SMA connectors J1 (VIN) and J2 (VOUT).

# 3.4 Optional Load Transient Circuit Operation

The TPS7A13EVM-057 evaluation module contains an optional high-performance load transient circuit to allow efficient testing of the TPS7A13 LDO load transient performance. To use the optional load transient circuit, install the correct components in accordance with the application. Modify the input and output capacitance connected to the TPS7A13 LDO to match the expected operating conditions. Determine the desired peak current to test, and modify the parallel resistor combination of R2, R3, R4, R5, and R6 as shown:

$$I_{Peak} = \frac{V_{OUT}}{R_2 \| R_3 \| R_4 \| R_5 \| R_6}$$

(1)

6

| R8      | R9      | Rise/Fall Time |

|---------|---------|----------------|

| 107 kΩ  | 86.6 kΩ | 9.6 µs         |

| 59 kΩ   | 43.2 kΩ | 4.8 μs         |

| 36.5 kΩ | 21.5 kΩ | 2.4 µs         |

| 19.1 kΩ | 10.7 kΩ | 1.2 µs         |

| 9.31 kΩ | 5.23 kΩ | 600 ns         |

| 4.53 kΩ | 2.55 kΩ | 300 ns         |

| 2.15 kΩ | 1.24 kΩ | 150 ns         |

| 402 Ω   | 267 Ω   | 30 ns          |

| Table 3-1 | Suggested | Ramn | Rate | <b>Resistor Values</b> |

|-----------|-----------|------|------|------------------------|

|           | Juggesteu | namp | Nate | Nesision values        |

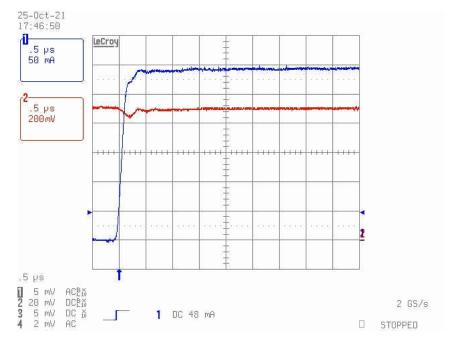

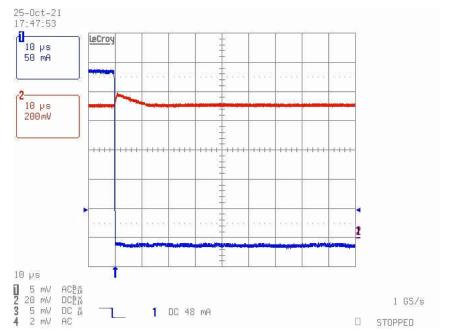

After the EVM is modified (if needed), connect a power supply to banana connectors J17 (VDD) and J21 (GND) with a 5-V DC supply and a 1-A DC current limit. As illustrated in Figure 3-3 and Figure 3-4, the TPS7A13 transient response is very fast and the output voltage recovers in well under 1 ms after the initial load transient. Therefore, use a load transient pulse duration limit of 1 ms to prevent excessive heating of the pulsed resistors (R2, R3, R4, R5, and R6). Configure a function generator for the  $50-\Omega$  output, in a 0-V DC to 5-V DC square pulse. If necessary, burst mode can be configured in the function generator for repetitive, low duty cycle, load transient testing.

A 2.49-k $\Omega$  resistor is installed on the EVM at R8, and a 2-k $\Omega$  resistor is installed on the EVM at R9. These resistors provide approximately 1 A/µs slew rate from 0 mA to 300 mA. Figure 3-3 and Figure 3-4 provide example test data with R8 = 2.49 k $\Omega$  and R9 = 2 k $\Omega$ . The red trace is the output voltage and the blue trace is the output current. J10 provides 1 mA of DC load current and R2, R3, R4, R5, and R6 provide 299 mA of pulsed load. The resulting test data shows a 1-mA to 300-mA load step on VOUT of the LDO, with only a 1-µF capacitor on the output of the LDO.

Figure 3-3. TPS7A13EVM-057 Load Transient Results: 1-mA to 300-mA Load Step

7

Figure 3-4. TPS7A13EVM-057 Load Transient Results: 300-mA to 1-mA Load Step

# 4 Board Layout

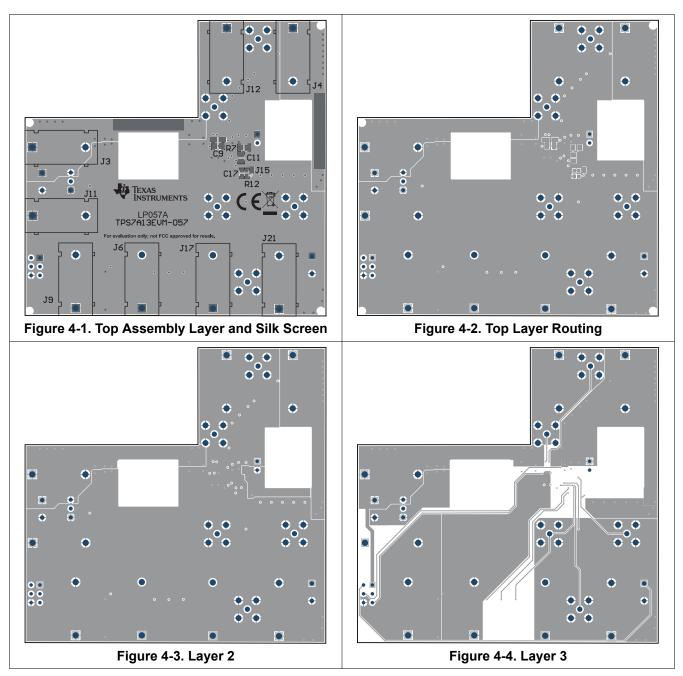

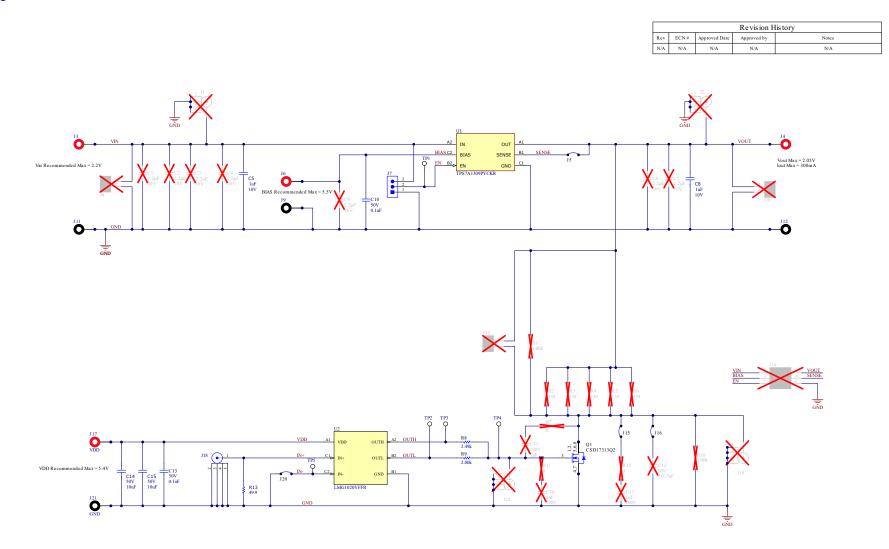

Figure 4-1 through Figure 4-6 show the board layout for the TPS7A13EVM-057 PCB.

The TPS7A13EVM-057 dissipates power, which may cause some components to experience an increase in temperature. The TPS7A13 LDO, LMG1020YFFR gate driver, and pulsed resistors R2, R3, R4, R5, and R6 are most at risk of raising to a high junction temperature during normal operation.

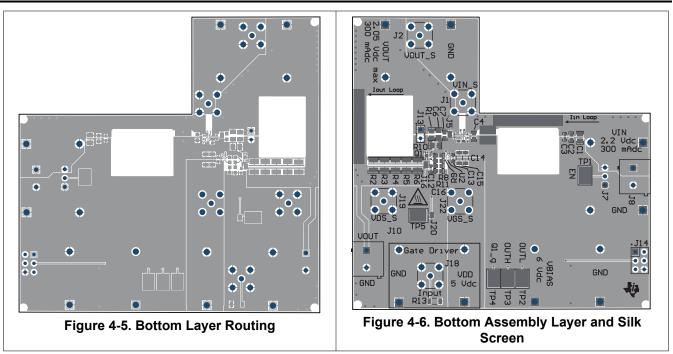

# 5 TPS7A13 EVM Schematic

Figure 5-1 shows a schematic for the TPS7A13EVM-057.

Figure 5-1. Schematic

# 6 Bill of Materials

Table 6-1 shows the bill of materials for the TPS7A13EVM-057.

| Designator                      | Quantity | Value | Description                                                                     | PackageReference               | PartNumber              | Manufacturer             | Alternate<br>PartNumber | Alternate<br>Manufacturer |

|---------------------------------|----------|-------|---------------------------------------------------------------------------------|--------------------------------|-------------------------|--------------------------|-------------------------|---------------------------|

| !PCB1                           | 1        |       | Printed Circuit Board                                                           |                                | LP057                   | Any                      |                         |                           |

| C5, C8                          | 2        | 1µF   | 1µF ±10% 10V Ceramic Capacitor X7R<br>0402 (1005 Metric)                        | 402                            | GMC04X7R105K10<br>NT    | Cal-Chip Electronics     |                         |                           |

| C10, C13                        | 2        | 0.1uF | CAP, CERM, 0.1 uF, 50 V, +/- 10%, X7R, 0402                                     | 402                            | C1005X7R1H104K0<br>50BB | TDK                      |                         |                           |

| C14, C15                        | 2        | 10µF  | 10 µF ±10% 50V Ceramic Capacitor X7R<br>1206 (3216 Metric)                      | 1206                           | GMC31X7R106K50<br>NT    | Cal-Chip Electronics     |                         |                           |

| FID1, FID2, FID3,<br>FID4, FID8 | 5        |       | Fiducial mark. There is nothing to buy or mount.                                | N/A                            | N/A                     | N/A                      |                         |                           |

| J3, J4, J6, J17                 | 4        |       | Standard Banana Jack, insulated, 10A, red                                       | 571-0500                       | 571-0500                | DEM Manufacturing        |                         |                           |

| J5, J15, J16, J20               | 4        |       | Jumper, SMT                                                                     | shorting jumper,<br>SMT        | JMP-36-30X40SMT         | Any                      |                         |                           |

| J7                              | 1        |       | Header, 2.54 mm, 3x1, Gold, TH                                                  | Header, 2.54mm,<br>3x1, TH     | 61300311121             | Wurth Elektronik         |                         |                           |

| J9, J11, J12, J21               | 4        |       | Standard Banana Jack, insulated, 10A, black                                     | 571-0100                       | 571-0100                | DEM Manufacturing        |                         |                           |

| J18                             | 1        |       | SMA Straight Jack, Gold, 50 Ohm, TH                                             | SMA Straight Jack,<br>TH       | 901-144-8RFX            | Amphenol RF              |                         |                           |

| Q1                              | 1        | 30V   | MOSFET, N-CH, 30 V, 5 A, DQK0006C<br>(WSON-6)                                   | DQK0006C                       | CSD17313Q2              | Texas Instruments        |                         | None                      |

| R8                              | 1        | 2.49k | RES, 2.49 k, 1%, 0.1 W, 0603                                                    | 603                            | RC0603FR-072K49<br>L    | Yageo                    |                         |                           |

| R9                              | 1        | 2.00k | RES, 2.00 k, 1%, 0.1 W, 0603                                                    | 603                            | RC0603FR-072KL          | Yageo                    |                         |                           |

| R13                             | 1        | 49.9  | Res Thick Film 1206 49.9 Ohm 1% 1/4W<br>±100ppm/°C Molded SMD SMD Paper<br>T/R  | 1206                           | RMCF1206FT49R9          | Stackpole<br>Electronics |                         |                           |

| SH-J1                           | 1        | 1x2   | Shunt, 100mil, Gold plated, Black                                               | Shunt                          | SNT-100-BK-G            | Samtec                   | 969102-0000-DA          | 3M                        |

| TP1, TP2, TP3,<br>TP4, TP5      | 5        |       | Test Point, Compact, SMT                                                        | Testpoint_Keystone<br>_Compact | 5016                    | Keystone                 |                         |                           |

| U1                              | 1        |       | 300-mA, Low VIN, Low VOUT, Ultra-Low<br>Dropout Regulator                       | DSBGA6                         | TPS7A1309PYCKR          | Texas Instruments        |                         |                           |

| U2                              | 1        |       | 5V, 7A/5A Low Side GaN Driver<br>With 60MHz/1ns Speed, YFF0006AEAE<br>(DSBGA-6) | YFF0006AEAE                    | LMG1020YFFR             | Texas Instruments        | LMG1020YFFT             | Texas Instruments         |

| C1, C6, C9                      | 0        | 2.2uF | CAP, CERM, 2.2 uF, 50 V, +/- 20%, X7R, 0805                                     | 805                            | C2012X7R1H225M<br>125AC | ТDК                      |                         |                           |

| C2, C4, C7                      | 0        | 2.2uF | CAP, CERM, 2.2 uF, 10 V, +/- 10%, X7R, 0603                                     | 603                            | C1608X7R1A225K0<br>80AC | ТDК                      |                         |                           |

| Designator         | Quantity | Value   | Description                                         | PackageReference                                   | PartNumber              | Manufacturer                   | Alternate<br>PartNumber | Alternate<br>Manufacturer |

|--------------------|----------|---------|-----------------------------------------------------|----------------------------------------------------|-------------------------|--------------------------------|-------------------------|---------------------------|

| C3                 | 0        | 2.2uF   | CAP, CERM, 2.2 uF, 10 V, +/- 10%, X7S, 0402         | 402                                                | C1005X7S1A225K0<br>50BC | TDK                            |                         |                           |

| C11                | 0        | 1pF     | CAP, CERM, 1 pF, 100 V, +/- 5%, C0G/<br>NP0, 0805   | 805                                                | GQM2195C2A1R0<br>CB01D  | MuRata                         |                         |                           |

| C12                | 0        | 0.015uF | CAP, CERM, 0.015 uF, 50 V, +/- 10%,<br>X7R, 0402    | 402                                                | GRM155R71H153K<br>A12D  | MuRata                         |                         |                           |

| C16, C17           | 0        | 1000pF  | CAP, CERM, 1000 pF, 100 V, +/- 5%,<br>X7R, 0603     | 603                                                | 06031C102JAT2A          | AVX                            |                         |                           |

| FID5, FID6, FID7   | 0        |         | Fiducial mark. There is nothing to buy or mount.    | N/A                                                | N/A                     | N/A                            |                         |                           |

| J1, J2, J19, J22   | 0        |         | SMA Straight Jack, Gold, 50 Ohm, TH                 | SMA Straight Jack,<br>TH                           | 901-144-8RFX            | Amphenol RF                    |                         |                           |

| J8, J10            | 0        |         | Terminal Block, 5 mm, 2x1, Tin, TH                  | Terminal Block, 5<br>mm, 2x1, TH                   | 691 101 710 002         | Wurth Elektronik               |                         |                           |

| J13                | 0        |         | Header, 100mil, 2x1, Gold, TH                       | Sullins 100mil, 1x2,<br>230 mil above<br>insulator | PBC02SAAN               | Sullins Connector<br>Solutions |                         |                           |

| J14                | 0        |         | Header, 100mil, 3x2, Gold, TH                       | 3x2 Header                                         | TSW-103-07-G-D          | Samtec                         |                         |                           |

| R1, R10            | 0        | 1.00k   | RES, 1.00 k, 1%, 0.125 W, AEC-Q200<br>Grade 0, 0805 | 805                                                | ERJ-6ENF1001V           | Panasonic                      |                         |                           |

| R2, R3, R4, R5, R6 | 0        | 154     | RES, 154, 1%, 0.5 W, 1210                           | 1210                                               | RC1210FR-07154R<br>L    | Yageo                          |                         |                           |

| R7                 | 0        | 0       | RES, 0, 5%, 0.125 W, AEC-Q200 Grade 0, 0805         | 805                                                | ERJ-6GEY0R00V           | Panasonic                      |                         |                           |

| R11, R12           | 0        | 0       | RES, 0, 1%, 0.1 W, AEC-Q200 Grade 0, 0603           | 603                                                | RMCF0603ZT0R00          | Stackpole<br>Electronics Inc   |                         |                           |

|                    |          |         |                                                     |                                                    |                         |                                |                         |                           |

## Table 6-1. Bill of Materials (continued)

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated