# User's Guide ISOW7741 Quad-Channel Digital Isolator With Integrated DC-DC Converter Evaluation Module

# **TEXAS INSTRUMENTS**

#### ABSTRACT

This user's guide describes the ISOW7741 quad-channel digital isolator with integrated DC-DC converter evaluation module (EVM). This EVM lets designers evaluate device performance for fast development and analysis of isolated systems. The EVM supports evaluation of any of the quad-channel device variants of ISOW77xx family in a 20-pin WB SOIC package (DFM-20).

#### CAUTION

This evaluation module is made available for isolator parameter performance evaluation only and is not intended for isolation voltage testing. To prevent damage to the EVM, any voltage applied as a supply or digital input/output must be maintained within the 0-V to 5.5-V recommended operating range.

## **Table of Contents**

| 1 Introduction                                                                                    | 2 |

|---------------------------------------------------------------------------------------------------|---|

| 2 Overview                                                                                        | 2 |

| 3 Pin Configuration of the ISOW7741 Quad-Channel Digital Isolator with Integrated DC-DC Converter | 3 |

| 4 EVM Setup and Operation                                                                         |   |

| 5 EVM Schematics                                                                                  |   |

| 6 PCB layout and 3D diagram                                                                       | 6 |

| 7 Bill of Materials                                                                               |   |

|                                                                                                   |   |

### **List of Figures**

| Figure 3-1. ISOW7741 Quad-Channel Digital Isolator with Integrated DC-DC Converter Pin Configuration | 3 |

|------------------------------------------------------------------------------------------------------|---|

| Figure 4-1. Typical EVM test setup                                                                   |   |

| Figure 5-1. ISOW7741DFMEVM Schematic                                                                 |   |

| Figure 6-1. ISOW7741DFMEVM PCB layout - top layer                                                    | 6 |

| Figure 6-2. ISOW7741DFMEVM PCB layout - bottom layer                                                 |   |

| Figure 6-3. ISOW7741DFMEVM PCB 3D daigram                                                            | 7 |

|                                                                                                      |   |

# List of Tables

| Table 4-1. Resistor configurations | 4              |

|------------------------------------|----------------|

| Table 7-1. Bill of Materials       | <mark>8</mark> |

#### Trademarks

All trademarks are the property of their respective owners.

# **1** Introduction

This user's guide describes EVM operation with respect to the ISOW7741 quad-channel digital isolator with integrated DC-DC converters. However, the EVM may be reconfigured for evaluation of any of quad-channel device variants of ISOW77xx family in a 20-pin WB SOIC package (DFM-20). This guide also describes the EVM BoM, EVM schematic, EVM PCB layout, and typical laboratory setup.

## 2 Overview

The ISOW7741 device is a galvanically-isolated quad- channel digital isolator with an integrated high-efficiency, low emissions power converter. The integrated DC-DC converter provides up to 500 mW of isolated power, eliminating the need for a separate isolated power supply in space-constrained isolated designs. The high-efficiency of the power converter allows for operation at a wide operating ambient temperature range of -40°C to +125°C. This device provides improved emissions performance, allowing for simplified board design and has provisions for ferrite beads to further attenuate emissions. The ISOW7741 has been designed with enhanced protection features in mind, including soft-start to limit inrush current, over-voltage and under-voltage lock out, fault detection on the EN\_DC DC pin, overload and short-circuit protection, and thermal shutdown.

The ISOW7741 device provides high electromagnetic immunity while isolating CMOS or LVCMOS digital I/Os. The signal-isolation channel has a logic input and output buffer separated by a double capacitive silicon dioxide (SiO2) insulation barrier, whereas, power isolation uses on-chip transformers separated by thin film polymer as insulating material. The ISOW7741 can operate from a single supply voltage of 3 V to 5.5 V by connecting VIO and VDD together on PCB. If lower logic levels are required, these devices support 1.71 V to 5.5 V logic supply (VIO) that can be independent from the power converter supply (VDD) of 3 V to 5.5 V. VISOIN and VISOOUT needs to be connected on board with either a ferrite bead or fed through a LDO.

The EVM enables a user to evaluate ISOW7741 device thoroughly before incorporating the device into their design. To facilitate the EVM to be powered from various power sources including regulated power supplies, standard DC adaptors and batteries, EVM includes two adjustable output LDOs (LM317M) that are connected to VIO and VDD pins of ISOW7741. This allows the LDO inputs to be connected to a wider range of supply voltages and the optimum voltage for normal operation of the EVM is between 9V to 12V. The EVM also includes an on-board oscillator (LTC6908-1) that can be connected to the inputs of ISOW7741 through  $0\Omega$  resistors. The oscillator helps to provide a quick test signal to verify device operation. The EVM can be configured to operate in various power supply voltages and test configurations the details of which are provided in following sections.

The EVM can be used to verify many of ISOW7741 datasheet parameters like input threshold voltages, current consumption and others. Some of the datasheet specifications require a different test setup configuration than the ISOW7741DFMEVM and hence, they cannot be verified from the EVM as is. The example parameters include maximum datarate, propagation delay and other timing specifications.

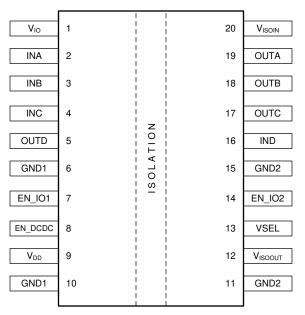

#### 3 Pin Configuration of the ISOW7741 Quad-Channel Digital Isolator with Integrated DC-DC Converter

Figure 3-1 shows the ISOW7741 Quad-Channel Digital Isolator with Integrated DC-DC Converter pin configuration.

Figure 3-1. ISOW7741 Quad-Channel Digital Isolator with Integrated DC-DC Converter Pin Configuration

## 4 EVM Setup and Operation

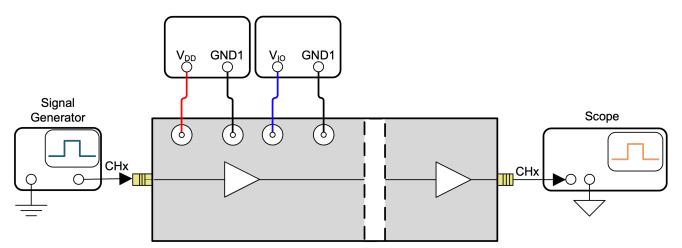

This section describes the typical setup and operation of the EVM for device evaluation. Figure 4-1 shows a typical test configuration for operating the ISOW7741DFMEVM using two power supplies.

Figure 4-1. Typical EVM test setup

ISOW7741DFMEVM has many DNP resistors which can be populated or unpopulated to setup the EVM to desired operating test conditions. Table 4-1 lists and describes all the possible test configurations that can be acheived by populating various resistors.

| Resistor           | Description                                                                                                                                                                                                                                                                 |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R1                 | It connects LDOs U1, U2 inputs together allowing only one power supply to be used instead of two power supplies.                                                                                                                                                            |  |  |  |

| R2, R5, R7, R10    | Sets LDO U2 output voltage to 5V, 3.3V, 2.5V or 1.8V, respectively. Only one of the four resistors needs t populated.                                                                                                                                                       |  |  |  |

| R6, R9             | Sets LDO U1 output voltage to 5V or 3.3V, respectively. Only one of the two resistors needs to be populated.                                                                                                                                                                |  |  |  |

| R11, R3, R17       | Populating R11 bypasses LDO U1 allowing VDD to be powered directly from external power supply. When R11 is populated, R3 and R17 need to be unpopulated to disconnect the LDO. When LDO is not bypassed the recommended input voltage to LDO should be between 9V and 12V.  |  |  |  |

| R15, R4, R18       | Populating R15 bypasses LDO U2 allowing VIO to be powered directly from external power supply. When R15 is populated, R4 and R18 need to be unpopulated to disconnect the LDO. When LDO is not bypassed, the recommended input voltage to LDO should be between 9V and 12V. |  |  |  |

| R13, R14, R16      | These resistors allow one input signal connection to multiple input channels.                                                                                                                                                                                               |  |  |  |

| R23                | It connects oscillator U3 output signal to U4 inputs allowing EVM to be tested using a test signal without needing any external test signal input.                                                                                                                          |  |  |  |

| R24, R25           | Populating only R24 sets U3 output signal frequency to 2.5 MHz (5 Mbps) and populating both R24 & R25 sets the frequency to 5 MHz (10 Mbps).                                                                                                                                |  |  |  |

| R26, R42           | Populating R26 enabled DC-DC converter of ISOW7741 and populating R42 disables it. Only one of the two resistors needs to be populated.                                                                                                                                     |  |  |  |

| R35, R37, R38      | These resistors allow one output signal connection to multiple input channels.                                                                                                                                                                                              |  |  |  |

| R40, R41           | Populating R40 sets VISOOUT to 5V and populating R41 sets it to 3.3V. Only one of the two resistors needs to be populated.                                                                                                                                                  |  |  |  |

| R33, R34, R36, R39 | One or more of these resistors can be populated to facilate external load to VISOOUT.                                                                                                                                                                                       |  |  |  |

|                    |                                                                                                                                                                                                                                                                             |  |  |  |

#### Table 4-1. Resistor configurations

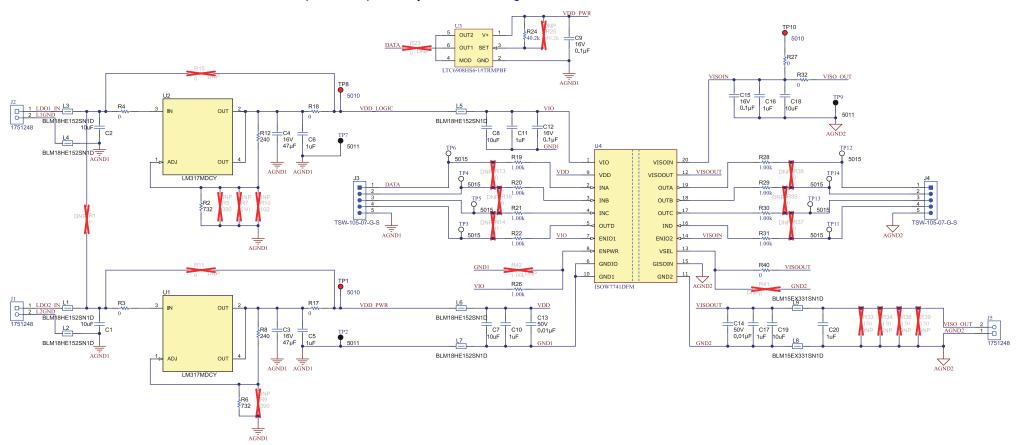

### **5 EVM Schematics**

The ISOW7741DFMEVM is designed to accommodate any of the ISOW774x quad-channel devices in a 20-pin WB SOIC package (DFM-20). To evaluate any of the ISOW774x quad-channel devices in a 20-pin WB SOIC package (DFM-20), replace ISOW7741 with the device of interest on the ISOW7741DFMEVM board. No other component requires any modification. Figure 5-1 shows the ISOW7741DFMEVM schematic.

Figure 5-1. ISOW7741DFMEVM Schematic

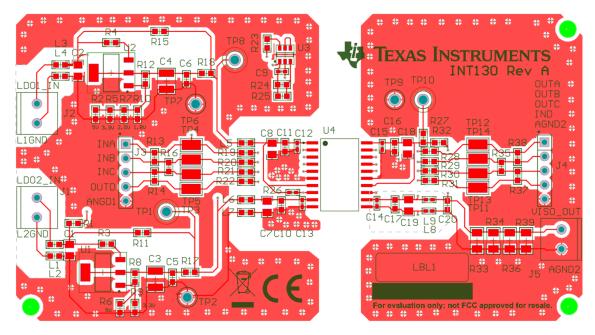

## 6 PCB layout and 3D diagram

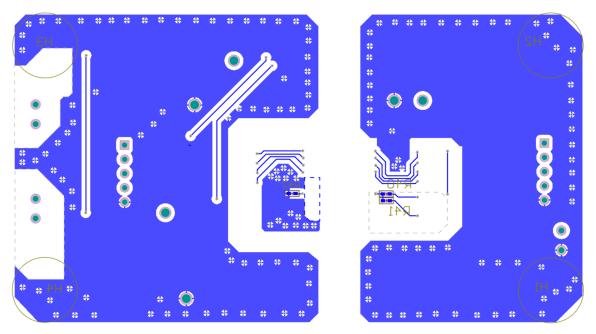

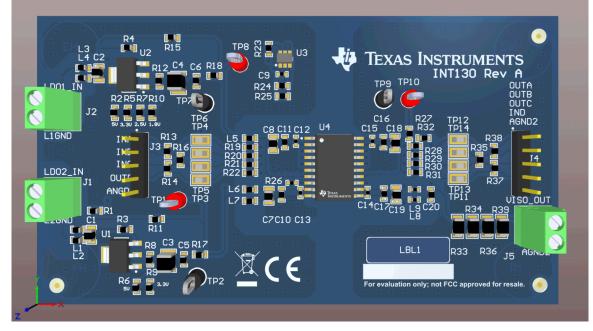

Figure 6-1 and Figure 6-2 show the printed-circuit board (PCB) layout top and bottom layers, respectively, and Figure 6-3 shows a 3D diagram of the PCB indicating how a finished board looks like.

Figure 6-1. ISOW7741DFMEVM PCB layout - top layer

Figure 6-2. ISOW7741DFMEVM PCB layout - bottom layer

Figure 6-3. ISOW7741DFMEVM PCB 3D daigram

## 7 Bill of Materials

Table 7-1 lists the bill of materials (BOM) for this EVM.

| Table 7-1. Bill of Materials | Table | 7-1. | Bill | of | Materia | ls |

|------------------------------|-------|------|------|----|---------|----|

|------------------------------|-------|------|------|----|---------|----|

| ltem | Designator                                       | Description                                                                                  | Manufacturer                  | PartNumber          |

|------|--------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------|---------------------|

| 1    | C1, C2, C7, C8,<br>C18, C19                      | CAP, CERM, 10 uF, 35 V, +/- 10%, X5R, 0805                                                   | MuRata                        | GRM21BR6YA106KE43L  |

| 2    | C3, C4                                           | CAP, CERM, 47 µF, 16 V,+/- 10%, X5R, 1210                                                    | Samsung Electro-<br>Mechanics | CL32A476KOJNNNE     |

| 3    | C5, C6, C10, C11,<br>C16, C17, C20               | CAP, CERM, 1 uF, 50 V, +/- 10%, X5R, 0603                                                    | Samsung Electro-<br>Mechanics | CL10A105KA8NNNC     |

| 4    | C9, C12, C15                                     | CAP, CERM, 0.1 µF, 16 V,+/- 10%, X7R, 0402                                                   | Walsin                        | CL05B104KO5NNNC     |

| 5    | C13, C14                                         | CAP, CERM, 0.01 µF, 50 V,+/- 10%, X7R, 0402                                                  | Walsin                        | 0402B103K500CT      |

| 6    | H1, H2, H3, H4                                   | Bumpon, Hemisphere, 0.44 X 0.20, Clear                                                       | 3M                            | SJ-5303 (CLEAR)     |

| 7    | J1, J2, J5                                       | Conn Term Block, 2POS, 3.5mm, TH                                                             | Phoenix Contact               | 1751248             |

| 8    | J3, J4                                           | Header, 100mil, 5x1, Gold, TH                                                                | Samtec                        | TSW-105-07-G-S      |

| 9    | L1, L2, L3, L4, L5,<br>L6, L7                    | Ferrite Bead, 1500 ohm @ 100 MHz, 0.5 A, 0603                                                | MuRata                        | BLM18HE152SN1D      |

| 10   | L8, L9                                           | Ferrite Bead, 330 ohm @ 100 MHz, 1.1 A, 0402                                                 | MuRata                        | BLM15EX331SN1D      |

| 11   | LBL1                                             | Thermal Transfer Printable Labels, 0.650" W x Brady<br>0.200" H - 10,000 per roll            |                               | THT-14-423-10       |

| 12   | R2, R6                                           | RES, 732, 1%, 0.1 W, 0603                                                                    | Yageo                         | RC0603FR-07732RL    |

| 13   | R3, R4, R17, R18,<br>R27, R32                    | RES, 0, 5%, 0.1 W, 0603                                                                      | Yageo                         | RC0603JR-070RL      |

| 14   | R8, R12                                          | RES, 240, 1%, 0.1 W, 0603                                                                    | Yageo                         | RC0603FR-07240RL    |

| 15   | R19, R20, R21,<br>R22, R28, R29,<br>R30, R31     | RES, 1.00 k, 1%, 0.1 W, 0603                                                                 | Yageo                         | RC0603FR-071KL      |

| 16   | R24                                              | RES, 40.2 k, 1%, 0.1 W, 0603                                                                 | Yageo                         | RC0603FR-0740K2L    |

| 17   | R26                                              | RES, 1.00 k, 1%, 0.0625 W, 0402                                                              | Yageo America                 | RC0402FR-071KL      |

| 18   | R40                                              | RES, 0, 5%, 0.063 W, 0402                                                                    | Yageo America                 | RC0402JR-070RL      |

| 19   | TP1, TP8, TP10                                   | Test Point, Red, Through Hole, RoHS, Bulk                                                    | Keystone                      | 5010                |

| 20   | TP2, TP7, TP9                                    | Test Point, Multipurpose, Black, TH Keystone                                                 |                               | 5011                |

| 21   | TP3, TP4, TP5,<br>TP6, TP11, TP12,<br>TP13, TP14 | Test Point, Miniature, SMT                                                                   | Keystone                      | 5015                |

| 22   | U1, U2                                           | 3/4 Pin 500mA Adjustable Positive Voltage<br>Regulator, DCY0004A (SOT-223-4)                 | Texas Instruments             | LM317MDCY           |

| 23   | U3                                               | Resistor Set SOT-23 Oscillator, 2.7 to 5.5 V, 6-pin<br>SOT23 (S6-6), -40 to 85 degC, Pb-Free | Linear Technology             | LTC6908HS6-1#TRMPBF |

| 24   | U4                                               | ISOW7741DFM                                                                                  | Texas Instruments             | ISOW7741DFM         |

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated